5_RISC技术

RISC设计原则及基本技术

RISC设计原则及基本技术CISC的特点:指令系统庞⼤,指令功能复杂,指令寻址⽅式多,指令格式多绝⼤多数指令须要多个机器周期完毕各种指令都能够訪问存储器採⽤微程序控制有专⽤寄存器,少量难以⽤优化编译技术⽣成⾼效的⽬标代码程序RISC特点:⼤多数指令在单周期内完毕LOAD/STORE结构硬布线控制逻辑降低指令和寻址⽅式的种类固定的指令格式注重编译的优化(三地址指令格式、较多的寄存器、对称的指令格式)*我觉得RISC与CISC的不同之处在于指令精简、寻址⽅式降低以及注重编译优化,这要得益于⼆⼋法则(CISC中,⼤约20%的指令占领了80%的处理机时间。

其余80%指令使⽤频度仅仅占20%的处理机执⾏时间)。

RISC⽐CISC快3倍左右。

主要取决于CPI(每条指令执⾏的平均周期数)。

在RISC中CPI近乎1。

RISC的设计原则:使⽤频度⾮常⾼的指令⼤⼤降低寻址⽅式全部指令在⼀个机器周期内完毕扩⼤通⽤寄存器个数採⽤硬联控制实现通过精简指令和优化设计编译程序,以简单有效的⽅式⽀持⾼级语⾔RISC结构採⽤的基本技术:在逻辑上採⽤硬联实现和微程序固件实现相结合的技术在CPU中设置数量较⼤的寄存器组,并採⽤重叠寄存器窗体的技术指令的运⾏採⽤流⽔和延迟转移技术採⽤优化编译技术。

优化寄存器的分配和使⽤RISC的不⾜:指令少。

加重汇编程序猿的负担浮点运算和虚拟存储器⽀持不⾜编译程序难写对于不⾜的最后⼀条,我感到疑惑——RISC提供直接⽀持⾼级语⾔的能⼒,应当是简化了编译程序的设计。

为什么还要说编译程序难写?希望知道的朋友们留下评论:)VLIW(超长指令字):是⼀种显式指令级并⾏指令系统⼀条VLIW指令含有多个同样或不同的操作字段(每⼀个操作字段的功能相当于⼀般处理机中的⼀条指令)每⼀个操作字段可以分别独⽴地控制各⾃的功能部件同⼀时候执⾏⼆维程序结构指令级并⾏度⾼应⽤VLIW的有Intel和HP合制的安腾(Intanium)处理机。

riscv相关政策

riscv相关政策RISC-V (Reduced Instruction Set Computer - V) 是一种开源指令集架构(ISA),它具有良好的灵活性、可扩展性和可定制性,逐渐成为全球范围内的热门技术。

众多国家和地区已经制定出了一系列与 RISC-V 相关的政策,以促进其发展和应用。

以下是相关的参考内容,介绍了几个主要国家和地区的 RISC-V 政策和措施。

1. 中国中国政府高度重视 RISC-V 技术的发展,并积极推动其在内地的推广和应用。

2019年,中国软件行业协会发布了《关于推动RISC-V市场应用的建议》的指导意见,提出了培育和扶持核心技术、研发和生态环境、推动关键应用和示范项目等多项具体措施。

同时,中国还设立了专门的研究机构和实验室,加强与 RISC-V 相关的研发和创新,同时鼓励各级政府和企事业单位采用 RISC-V 技术。

2. 美国美国政府也在积极推动 RISC-V 的发展并制定一系列政策支持措施。

例如,美国国防部于2019年宣布成立了联合协议,旨在推动 RISC-V 的发展和部署,以提高国防领域的信息安全和计算能力。

另外,美国国家科学基金会(NSF)还资助了许多与 RISC-V 相关的研究项目,并提供经费支持和技术资源。

3. 欧盟欧盟也在积极关注 RISC-V 技术的发展,并通过政策和计划来支持其推广和应用。

例如,欧洲计算机和系统工程协会(EUROPEAN DIGITAL SME ALLIANCE)发起了名为“RISC-V Euro”的倡议,旨在促进 RISC-V 在欧洲的发展,并加强欧洲与其他地区的合作。

此外,欧盟还通过不同的项目和计划提供资金支持,以发展和推广 RISC-V 相关的研究、开发和示范项目。

4. 日本日本政府也非常关注 RISC-V 的发展,并采取了一系列政策来推动其应用。

例如,经济产业省于2019年发布了《关于RISC-V等通用处理器的应用拓展的调查研究报告》,提出了鼓励采用 RISC-V 技术的相关政策建议。

RISC技术

RISC技术相信大家在日常电脑使用或CPU的广告介绍中时常听到见到“RISC”这个词,什么Pentium Ⅱ/Pro采用先进RISC技术……K6采用RISC86结构,从而……总之大凡稍高档点的中央处理器都称采用RISC技术,那么RISC究竟是什么东西呢?如果你是电脑初学爱好者,并想从事电脑的开发、学习,那你应认真读一读,因为它是计算机技术中一个相当重要的环节。

首先,要了解RISC技术就该从计算机的指令谈起,我们都知道计算机的工作就是取指令、执行指令,一条指令一般给出的是操作码和地址码,这是基本的结构,然而指令又涉及以下几个问题。

首先指令字长有多少位,是定字长还是变字长;其次,操作码结构需几位,位数是定量还是浮动量;再次,地址的结构和寻址方式如何。

这种种因素使计算机指令产生了“简单指令”和“复杂指令”之分。

70年代以前的计算机均用传统的CISC指令结构,即完全采用复杂指令来支持高级语言、应用程序和操作系统。

这种PC不但成本高且效率较低,速度受限,后来人们发现机器执行的指令中8 5%左右的都是简单指令,复杂指令甚少,因此开始研制精简指令系统计算机(RISC)。

自从Intel的Pentium问世以来(92年末),RISC技术更是得到了广泛的应用,并开始渗透到小、中、大型机领域,可谓发展前景一片光明。

下面具体谈谈RISC技术。

CPU执行运算速度受三个因素的影响:(1)程序中指令数I;(2)每条指令执行所用周期数CPI;(3)周期时间T。

这三者又有:程序执行时间=I*CPI*T,因此,从这个等式可看出减小其中任一个都可提高CPU的速度,因此RISC技术就从这三方面下手,对I、CPI、T进行优化改良,其措施如下:1、采用多级指令流水线结构采用流水线技术可使每一时刻都有多条指令重叠执行,以减小CPI的值,使CP U不浪费空周期。

实例:Pentium Ⅱ/Pro/Celeron可同时发出执行五条指令,AMD -K6/K6-2可同时发出六条指令。

ASIC、NP、X86、RISC、DSP 、ARM、单片机几种常见技术介绍

RISC微处理器不仅精简了指令系统,采用超标量和超流水线结构;它们的指令数目只有几十条,却大大增强了并行处理能力。如:1987年Sun

Microsystem公司推出的SPARC芯片就是一种超标量结构的RISC处理器。而SGI公司推出的MIPS处理器则采用超流水线结构,这些RISC处理器在构建并行精简指令系统多处理机中起着核心的作用。

(2)程序和数据空间分开,可以同时访问指令和数据;

(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;

(4)具有低开销或无开销循环及跳转的硬件支持;

(5)快速的中断处理和硬件I/O支持;

● 分级存储器组织: NP存储器一般包含多种不同性能的存储结构,对数据进行分类存储以适应不同的应用目的。

● 高速I/O接口:

NP具有丰富的高速I/O接口,包括物理链路接口、交换接口、存储器接口、PCI总线接口等。通过内部高速总线连接在一起,提供很强的硬件并行处理能力。

现代ASIC常包含整个32-bit处理器,类似ROM、RAM、EEPROM、Flash的存储单元和其他模块.

这样的ASIC常被称为SoC(片上系统)。

FPGA是ASIC的近亲,一般通过原理图、VHDL对数字系统建模,运用EDA软件仿真、综合,生成基于一些标准库的网络表,配置到芯片即可使用。它与ASIC的区别是用户不需要介入芯片的布局布线和工艺问题,而且可以随时改变其逻辑功能,使用灵活。

针对滤波、相关、矩阵运算等需要大量乘和累加运算的特点,DSP的算术单元的乘法器和加法器,可以在一个时钟周期内完成相乘、累加两个运算。近年出现的某些DSP如ADSP2106X、DSP96000系列DSP可以同时进行乘、加、减运算,大大加快了FFT的蝶形运算速度。

计算机组成原理复习题及答案

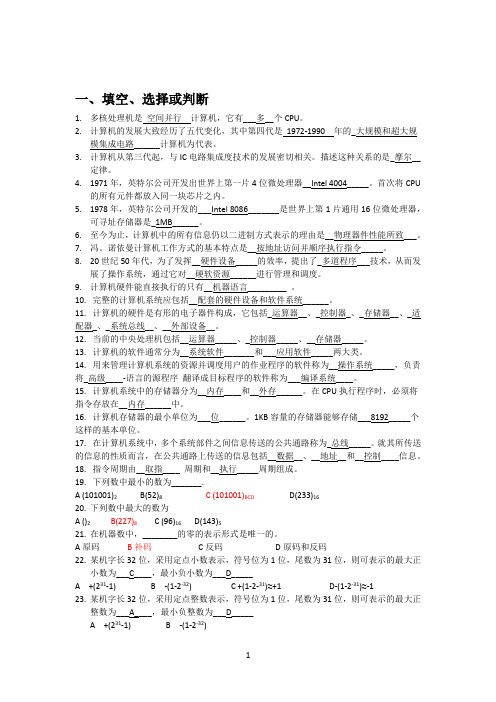

一、填空、选择或判断1.多核处理机是空间并行计算机,它有___多__个CPU。

2.计算机的发展大致经历了五代变化,其中第四代是1972-1990 年的_大规模和超大规模集成电路______计算机为代表。

3.计算机从第三代起,与IC电路集成度技术的发展密切相关。

描述这种关系的是_摩尔__定律。

4.1971年,英特尔公司开发出世界上第一片4位微处理器__Intel 4004_____。

首次将CPU的所有元件都放入同一块芯片之内。

5.1978年,英特尔公司开发的___Intel 8086_______是世界上第1片通用16位微处理器,可寻址存储器是_1MB______。

6.至今为止,计算机中的所有信息仍以二进制方式表示的理由是__物理器件性能所致___。

7.冯。

诺依曼计算机工作方式的基本特点是__按地址访问并顺序执行指令_____。

8.20世纪50年代,为了发挥__硬件设备_____的效率,提出了_多道程序___技术,从而发展了操作系统,通过它对__硬软资源______进行管理和调度。

9.计算机硬件能直接执行的只有__机器语言_________ 。

10.完整的计算机系统应包括__配套的硬件设备和软件系统______。

11.计算机的硬件是有形的电子器件构成,它包括_运算器__、_控制器_、_存储器__、_适配器_、_系统总线__、__外部设备__。

12.当前的中央处理机包括__运算器_____、_控制器_____、__存储器_____。

13.计算机的软件通常分为__系统软件_______和___应用软件_____两大类。

14.用来管理计算机系统的资源并调度用户的作业程序的软件称为__操作系统_____,负责将_高级____-语言的源程序翻译成目标程序的软件称为___编译系统____。

15.计算机系统中的存储器分为__内存____和__外存______。

在CPU执行程序时,必须将指令存放在__内存______中。

大学计算机基础缩写词

大学计算机基础缩写词1.ALU:Arithmetic Logic Unit算术逻辑单元2.CPU:Central Processing Unit中央处理单元3.CISC技术:ComplexInstructionSetComputer复杂指令系统计算机4.RISC技术:ReducedInstructionSetComputer精减指令系统计算机5.RAM:Random Access Memory6.BIOS:Basic Input/output system7.CMOS:complementary metal-oxide semiconductor互补金属氧化物半导体8.SDRAM:Synchronous DRAM同步动态随机存储器9.DDR:Dual Date Rate10.SDRAM:双倍速率11.掩膜ROM:Masked ROM12.PROM:Programmable ROM可编程PROM13.EPROM:Erasable PROM可擦除PROM14.ROM:Read Only Memory15.VLSI:Very Large Scale Integration,超大规模集成电路16.EISA:Extended Industry Standard Architecture17.ISA:Industrial Standard Architecture总线18.VESA:Video Electronics Standards Association即视频电子标准协会总线19.PCI:peripheral component interconnect总线20.AGP :Accelerated Graphics Port总线B:Universal Serial Bus总线22.DBMS:Database Management System数据库管理系统23.IDE:Integrated Drive Electronics电子集成驱动器24.SCSI硬盘:Small Computer System Interface小型计算机系统接口25.RAID:Redundant Array of Independent Disks独立磁盘冗余阵列26.SSD:Solid States Disk固态存储器27.BCD码:Binary Coded Decimal,用二进制代码表示的十进制数28.PCB:Process Control Block进程控制块29.DMA:Direct Memory Access直接存取方式30.FAT:File Allocation Table文件分配表31.DBP:Dos Boot Record操作系统引导记录区32.BPB:BIOS Parameter Block,BIOS参数块33.NTFS:New Technology File System34.MBR:Master Boot Record主引导记录35.DPT:Disk Partition Table硬盘分区表36.GUI:Graphics User Interface图形用户界面37.Windows NT:NT,New Technology38.PCM:Pulse Coded Modulation脉冲编码调制39.DRM:Digital Rights Management数字版权管理40.MIDI:Musical Instrument Digital Interface41.RGB:Red、Green、Blue42.CMYK:Cyan、Magenta、Yellow、blacK43.HSB:Hue、Saturation、Brightness色相、饱和度、明度44.GIF:Graphics Interchange Format45.JPEG:Joint Photographic Experts Group46.MPEG:Moving picture experts group47.TIFF:Tagged Image File Format48.PNG:Portable Network Graphic可移植的网络图像49.AVI:Audio Video Interleaved,音频视频交叉存取格式50.ADSL:Asymmetrical Digital Subscriber Line非对称数字用户环路51.ARP :Address Resolution Protocol 地址解析协议52.ATM :Asynchronous Time division multiplexing异步传输模式53.BBS:Bulletin Board System电子公告栏54.CDMA:Code Division Multiple Access码分多址接入技术55.CERNET:China Education and Research Network中国教育和科研网56.CGWNET:China Great Wall Network中国长城网57.ChinaGBN:China Gold Bridge Network中国金桥信息网58.CIETNET:China International Economy Trade Network中国国际经济贸易互联网59.CMNET:China Mobile Network中国移动互联网CNET:China NetCom Network中国网通公用互联网61.CSTNET :China Science and Technique NetWork中国科技网62.CSS :Cascading Style Sheets层叠样式表63.DDN:Digital Data Network数字数据网64.DHCP:Dynamic Host Configuration Protocol动态主机配置协议65.DNS:Domain Name System域名解析系统66.DWDM:Dense Wavelength Division Multiplexing密集波分复用67.FDDI:Fiber Distributed Data Interface光纤分布式数据接口68.FTP :File Transfer Protocol文件传输协议69.GPRS:General Packer Radio Service通用无线分组业务70.GPS:Global Position System全球定位系统71.HTML:Hypertext Markup Language超文本标记语言72.HTTP:Hypertext Transfer Protocol超文本传输协议73.ICMP:Internet Control Message Protocol因特网控制报文协议74.IGMP:Internet Group Management Protocol因特网组管理协议75.IMAP:Internet Mail Access Protocol Internet邮件访问协议76.IP:Internet Protocol 网际协议77.IPX/SPX:Internetwork Packet eXchange/Sequences Packet NETW ARE eXchange客户端/服务器的协议群78.ISDN:Integrated Services Digital Network综合业务数字网N:Local Area Network局域网80.MAC:Medium Access Control媒体接入控制81.MAN :Metropolitan Area Network城域网82.MIME:Multipurpose Internet Mail Extensions多用途Internet函件扩展标准BEUI:NetBIOS Extended User Interface NetBios增强用户接口84.OSI/RM:Open Systems Interconnection Reference Model开放系统互联基本参考模型85.POP :Post Office Protocol邮局协议86.PPP:Point to Point Protocol点对点协议87.RARP:Reverse Address Resolution Protocol逆地址解析协议88.RSS:Really Simple Syndication描述和同步网站内容的格式89.SMTP :Simple Mail Transfer Protocol简单邮件传送协议90.SNMP:Simple Network ManagementProtocol简单网络管理协议91.TCP:Transmission Control Protocol传输控制协议92.UDP:User Datagram Protocol用户数据报协议93.UNINET:China Unicom Network中国联通互联网94.URL:Uniform Resource Locator统一资源定位器95.WAN:Wide Area Network广域网96.WWW: World Wide Web万维网。

计算机系统结构自考题模拟9_真题(含答案与解析)-交互

计算机系统结构自考题模拟9(总分100, 做题时间90分钟)第Ⅰ部分选择题一、单项选择题(在每小题列出的四个备选项中只有一个是符合题目要求的)1.下列选项中不属于计算机系统的设计方法的是______SSS_SINGLE_SELA 由上往下B 从左向右C 由下往上D 从中间开始分值: 1答案:B[考点] 计算机系统的设计方法[解析] 计算机系统的设计方法有由上往下、由下往上和从中间开始。

2.在早期冯·诺依曼计算机特征中,机器以哪项为中心______SSS_SINGLE_SELA 存储器B 输入输出设备C 运算器D 控制器分值: 1答案:C[考点] 冯·诺依曼计算机的概念[解析] 在早期冯·诺依曼计算机特征中,机器以运算器为中心。

3.下面哪个页面替换算法实际上是不能够实现的______SSS_SINGLE_SELA 随机页面替换算法B 先进先出替换算法C 最久没有使用算法D 最优替换算法分值: 1答案:D[考点] 页面替换算法[解析] 最优替换算法是理想上的算法,实际上是不可能实现的。

但其可以作为一个考量标准,来评价其他算法的好坏。

4.为了提高流水线的最大吞吐率,首先要找出______SSS_SINGLE_SELA 瓶颈B 任务数C 结果数D 以上三个都不是分值: 1答案:A[考点] 标量流水线的主要性能[解析] 为了提高流水线的最大吞吐率,首先要找出瓶颈,然后没法消除此瓶颈。

5.下列选项不属于开发并行的途径的是______SSS_SINGLE_SELA 资源重复B 资源共享C 分布式处理系统D 时间重叠分值: 1答案:C[考点] 并行性开发环境[解析] 开发并行性的途径有时间重叠、资源重复和资源共享等。

6.在对Cache写操作时,以下关于写回法描述不正确的是______SSS_SINGLE_SELA 需要设置修改位B 需要少量缓冲器C 不需要缓冲器D 没有直达法可靠分值: 1答案:C[考点] Cache存储器的性能[解析] 写回法需要少量缓冲器,用于暂存将要写回的块,使之不必等待替换块写回主存后才开始进行Cache存取。

微机原理与接口技术+第四版+钱晓捷主编+课后习题答案

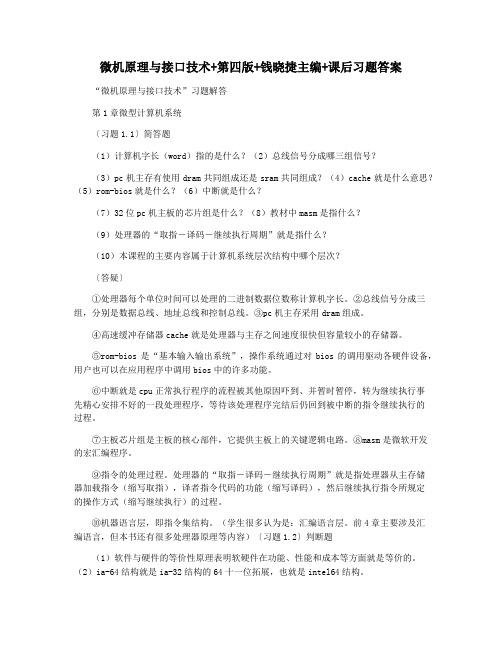

微机原理与接口技术+第四版+钱晓捷主编+课后习题答案“微机原理与接口技术”习题解答第1章微型计算机系统〔习题1.1〕简答题(1)计算机字长(word)指的是什么?(2)总线信号分成哪三组信号?(3)pc机主存有使用dram共同组成还是sram共同组成?(4)cache就是什么意思?(5)rom-bios就是什么?(6)中断就是什么?(7)32位pc机主板的芯片组是什么?(8)教材中masm是指什么?(9)处理器的“取指-译码-继续执行周期”就是指什么?(10)本课程的主要内容属于计算机系统层次结构中哪个层次?〔答疑〕①处理器每个单位时间可以处理的二进制数据位数称计算机字长。

②总线信号分成三组,分别是数据总线、地址总线和控制总线。

③pc机主存采用dram组成。

④高速缓冲存储器cache就是处理器与主存之间速度很快但容量较小的存储器。

⑤rom-bios是“基本输入输出系统”,操作系统通过对bios的调用驱动各硬件设备,用户也可以在应用程序中调用bios中的许多功能。

⑥中断就是cpu正常执行程序的流程被其他原因吓到、并暂时暂停,转为继续执行事先精心安排不好的一段处理程序,等待该处理程序完结后仍回到被中断的指令继续执行的过程。

⑦主板芯片组是主板的核心部件,它提供主板上的关键逻辑电路。

⑧masm是微软开发的宏汇编程序。

⑨指令的处理过程。

处理器的“取指―译码―继续执行周期”就是指处理器从主存储器加载指令(缩写取指),译者指令代码的功能(缩写译码),然后继续执行指令所规定的操作方式(缩写继续执行)的过程。

⑩机器语言层,即指令集结构。

(学生很多认为是:汇编语言层。

前4章主要涉及汇编语言,但本书还有很多处理器原理等内容)〔习题1.2〕判断题(1)软件与硬件的等价性原理表明软硬件在功能、性能和成本等方面就是等价的。

(2)ia-64结构就是ia-32结构的64十一位拓展,也就是intel64结构。

(3)8086的数据总线为16位,也就是说8086的数据总线的个数、或说条数、位数是16。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(3) 总线控制部件 指令Cache可同时发 送两条指令, 一条发 (4) 存储管理部件 送到RISC核心, 另一 (5) 浮点控制部件 条发送到浮点部件. (6) 浮点加法及乘法部件 (7) 三维图形处理部件 (8) RISC核心

结论: 整体性能有较大提高 RISC处理器的出现

说明: 复杂指令功能由软件实现与提高速度相矛盾? - 复杂指令使用频率较低; - 去掉微程序, 采用硬件控制, 提高了速度 - 简单指令有利于流水线执行 - 简化电路节省了芯片面积, 利于增加Cache容量

二、RISC处理器特征描述

1. 简单固定的指令格式

表现形式 控制依据

操作应在什么时间进行并完成

操作什么时刻进行(定时) 信息流动的起点与终点

门电路的开和关信号、打入脉冲等。 执行的指令和机器的状态

指令功能分解结合时序完成上述控制

— 组合逻辑设计 指令功能分解成微操作-结合时序信号- 逻辑表达式综合并化简-逻辑电路实现 例:

(1) 执行指令: ADD R1, R2 硬件模型

① ld.l 0(r14), r15

完成 (0 +r14)r15; 间接寻址

② ld.l 8(r14), r15 ③ ld.l r13(r14), r15

变址寻址 r0≡0, 直接寻址

④ ld.l 64(r0), r15

r0恒为0, 与执行的操作无关。作用如: subu r5, r4 r0; 产生比较指令 提供直接寻址 通过逻辑运算, 为某个寄存器赋0值 可以体现精简指令的特点。

(一) RISC核心

1. 功能 指令读入、数据存取、以及除浮点运算外的其 它指令操作

2. 指令格式 32位定长指令; 指令中 操作码、源操作数、目标操作数 字段位 置固定 (使指令译码与取源操作数可以并行)。 3. 寄存器 32个32位寄存器 r31 ~ r0 存放操作数、运算结果、间址和变址等地址量

RISC微处理器技术

RISC技术概述

一、起源

CISC — Complex Instruction Set Computer RISC — Reduced Instruction Set Computer 指令集:控制器设计的基础

计算机工作过程:

各种信息在受控状态下的流动过程。 受控的体现:

时间的控制 时机的控制 方向的控制

F D E1 E2 E3 W

如何实现一条整数指令和一条浮点指令的并发?

汇编编程:应用设计者 高级语言:编译程序

二、i860指令系统例

两大类: 整数指令

整数和浮点数的存取指令 算术及逻辑运算指令 转移指令 整数寄存器与浮点寄存器间的数据传送指令

浮点指令

浮点数据加、减、比较等 浮点数乘、倒数、平方根等

在RISC结构中 条件转移指令, 预测错误。 转移指令 无条件转移指令; 无条件转移指令:

ADD MOV1

流水线情况:

F D E W E W E W E W F D F D F D

MOV2

JMP NT2 NT1: SUB ..... NT2: AND

阻塞三个周期

AND

解决措施:

(1) 硬件自动冻结流水线周期 (2) 延迟转移技术

可由硬件实现也可由

软件实现

i860采用通过系统软件的

指令重调度。

转移指令可能引起流水线阻

塞, 这种情况称为控制相关 (也称为指令相关)。

对条件转移指令: 采用分支预测或指令重调度 i860采用指令重调度

引发流水线阻塞的另一因素 数据相关 即: 当前指令等待前面指令的执行结果。

ADD AX, BX INC AX MOV CX, DX ... ADD AX, BX MOV CX, DX INC AX ...

(如指令: ADC [变址寻址], 立即数 ;复杂指令)

软件中的简单指令约占总运行时间的20%, 复

杂指令约占总运行时间的80%;

造成控制电路复杂的主要原因是由于复杂指

令的存在;

— 结论及试验

从指令集中去掉复杂指令, 复杂指令功能由软 件实现. 可简化电路设计, 去掉微程序, 采用硬 连控制方法, 提高处理器速度。

4. 指令流水线 RISC核心采用4级指令流水线。 取指 译码 执行 写结果

5. 存取式体系结构 访存指令:Load/Store

* 流水线情况分析

前述的可能造成流水线阻塞的原因: 指令太长, 一个周期未能取出全部指令码; 指令功能复杂, 一个执行周期不能完成; 无条件转移指令; 条件转移指令, 预测错误。

解决方法:硬件自动冻结周期或指令重调度 i860采用指令重调度

资源冲突 资源冲突的典型情况:对存储器的访问 如下图的指令流水线:

F D E W E W F D

F D

如果该阶段出现访存(如 ld/St指令), 则与第三条 指令的取指操作冲突。

E W

E W

F D

若访存, 与第四条指

令的的取指操作冲突。

(一) 整数指令

1. 整数的存取 (1) 取数指令 ld.x isrc1(isrc2), idest 其中: isrc2和idest为r31~r0之一 ; isrc1为16为立即数或r31~r0之一 ; 完成: (isrc1+isrc2) idest .b 取8位数据 指令后缀: .x .s 取16位数据 .l 取32位数据 取数指令例:

; 锁存器1的打入脉冲 ; R2内容输出到内部总线 ; 锁存器2的打入脉冲 ; 相加结果打入R1

根据 取指(FET) — 译码(DE) — 执行(EXE)

FET

DE

EXE

T1 T2 T3 T4

.....

+R1EN = +ADD· EXE· T1 +Lat1 = +ADD· EXE· T1 +R2EN = +ADD· EXE· T2 +Lat2 = +ADD· EXE· T2 +R1CLK = +ADD· EXE· T4

四个寄存器可在逻辑上构成一个128位寄存器;

3. 浮点部件与RISC核心的并行 (1) 单指令模式 (SIM)

RISC核心与浮点部件按程序中指令流的顺序执 行。一次发出一条指令(整数指令或浮点指令)。 指令串行发出,但整数指令和浮点指令的执行 过程在时间上是可以重叠的。

(2) 双指令模式 (DIM)

(T1表示在上升沿, T1表示在下降沿)

(节拍T3等待加法器 完成加法操作)

综合简化后逻辑实现:

微命令序列

微命令发生器

(各种门电路构成)

运行状态

指 令 译 码

…...

时序

优点: 硬件实现, 速度快 缺点: 设计过程及电路复杂; 修改困难; 更新换代困难;

— 微程序设计

指令功能分解成微操作-微操作编码-存入微 程序ROM-微命令译码结合时序-完成功能 微指令 微地址 微地址 译码器

(2) 存数指令 st.x isrc1, const(isrc2) 完成: isrc1 ( const+tisrc2)

其中: isrc1和isrc2为寄存器, const为16位立即数

例: st.l r1, 64(r2); r1( 64+r2)

2. 浮点数的存取

(1) 取数 fld.y isrc1(isrc2), fdest 完成: (isrc1+isrc2) fdest isrc1为16为立即数或整数寄存器; isrc2为整数寄存器; fdest为浮点寄存器。

利用指令64位的双端口指令Cache, 同时发出 两条指令。一条整数指令 一条浮点指令

RISC核心 浮点部件

整数Ins1 F D E W

浮点Ins1 F D E1 E2 E3 W

注: 浮点运算至少需要 三个执行周期

整数Ins2

浮点Ins2 整数Ins3 浮点Ins3

F D E W

F D E1 E2 E3 W F D E W

指令Cache和数据Cache分离, 使取指和取数 相互独立, 如Pentium和i860均采用该结构。 或者: 同一Cache, 指令端口和数据端口分离, 可同时访问两个不同端口。

(二) 浮点部件

1. 组成 浮点控制器 浮点加法器 浮点乘法器 2. 寄存器 f31~f0 32个32位浮点寄存器

两个寄存器可在逻辑上构成一个64位寄存器;

.q 128位数据传送

例: fld.d 0(r3), f20 ; 64位数f20:f21 fld.q 0(r3), f20 ; 128位数f20:f21:22:f23

优点: 设计过程及电路相对简单; 采用微程序设 修改和更新换代更容易。 计的另一原因: 处理器与存储 缺点: 微命令实现, 速度较慢 器速度的矛盾

传统处理器设计的难题:

速度、复杂性、设计周期等矛盾

— 对指令系统进行的研究, 统计表明: 软件中大部分指令为简单指令(约80%), 复杂 指令只占少数 (约20%);

优化后的指令顺序: ADD R1, R2, R3 MUL R6, R7, R0 ADD R3, R4, R5 MUL R0, R8, R9

②指令顺序调整结合变量重命名

由于四条指令均与R3有关,仅通过调整顺 序难以优化。因此重新命名一个变量R0。

Intel 860处理器 (i860) 一、i860的组成

指令长度固定

指令长度无需译码, 简化了译码电路并节省了 长度译码时间; 指令长度设定为总线宽度, 保证取指令码一 个总线周期完成, 避免了多周期取操作数并行;

指令意义简单: 功能单一, 简化硬件逻辑

2. 减少寻址方式和指令数量 作为简化硬件逻辑的措施之一。 3. 流水线(或超级流水线) 尽量只使在单周期执行完成; RISC的设计思想更利于指令按流水线方式的 运行。