VHDL硬件描述语言(2.1)

VHDL硬件描述语言

b. 类型参数说明 必须放在端口说明前面,用于指定参数。 c. 端口说明格式 PORT( 端口名{,端口名}: 方向 端口名{,端口名}: 方向 数据类型名; 数据类型名);

其中, 方向—— IN OUT INOUT BUFFER LINKAGE 输入 输出 双向 输出 不指定方向

注意: * OUT 结构选体中不能再用; * BUFFER 结构选体中能再用。

5

二、VHDL程序的基本结构

* 一个完整的VHDL语言程序通常包含: 实体、 结构体、库、包集合和配置五个部分 a. 实体(Entity) ——用于描述所设计系统或单元的外部接口信号; b. 结构体(Architecture) —— 用于描述所设计系统或单元内部的结构和行为。

6

c. 库(Librrary) —— 用于存放已经编译的实体、结构体、包集合和配置。 库可由用户生成或由ASIC芯片制造商提供,以便于 在设计中为大家所共享; d. 包集合(Package) —— 用于存放各设计模块都能共享的数据类型、常数和子 程序等; e. 配置(Configuration) —— 用于从库中选取所需单元来组成系统设计的不同版本; 这个部分有时可以没有。

实体

结构体

a b

&

y

16

3.库

—— 库(Library)是经编译后的数据的集合,它存放包 集合定义、实体定义、结构体定义和配置定义。 a. 在VHDL语言中,库的说明总是放在设计单元的最前面, 书写格式为: LIBRARY 库名 ; 注意:

- 在设计时可以直接使用库中的数据。 - 设计者可以共享已经编译过的设计结果。 - 库和库之间是独立的,不能互相嵌套。

12

i 结构描述: 描述该设计单元的硬件结构。主要用配置指定语句及元 件例化语句描述元件的类型及元件的互连关系。 ii 行为描述: 描述该设计单元的功能,主要用函数,过程和进程语句, 以算法形式描述数据的变换和传送。 iii 数据流方式/RTL描述: 以类似于寄存器传输级(RTL)的方式描述数据的传输 和变换,主要用并行信号赋值语句,显式表示该设计单 元的行为, 隐式表示了该设计单元的结构。

硬件描述语言VHDL基本概念

信号模式表示端口的数据流向,有以下五 种:IN(流入实体)、OUT(流出实体)、 INOUT(双向端口)、BUFFER(带有反馈的 输出端口,该端口只能有1个驱动源)和 LINKAG(无特定方向)。

20世纪70年代末至80年代初,美国国防部提出了 VHSIC(Very High Speed Integrated Circuit)计划, 其目标是为了开发新一代集成电路。

为了配合这一计划,1983年美国国防部与TI公司、 IBM公司和Intermerics公司联合签约,开发VHSIC HDL,即VHDL。在1985年开发小组发布了最后版本 VHDL V7.2,同时开始着手标准化工作,到1987年12月, VHDL经过多次修改后,被IEEE接受为第一个标准HDL, 即IEEE Std 1076-1987。

目前公布的最新VHDL标准版本是

IEEE Std 1076-2008。

2.2 1位全加器的描述实例

1位全加器有3个输入端a、b、c_in和 2个输出端sum、c_out。

它是由2个半加器和1个或门构成。

a

sum

b

全加器

a

temp_sum

sum

U1

U2

b 半加器

半加器 temp_c2

c_in

c_out c_in

1个设计实体由1个实体声明和若干个结构 体组成。实体声明是设计实体的接口部分,它 表示设计实体对外部的特征信息;结构体是设 计实体的实现方案描述。

1个设计实体中的若干个结构体,分别代表 同一实体声明的不同实现方案。

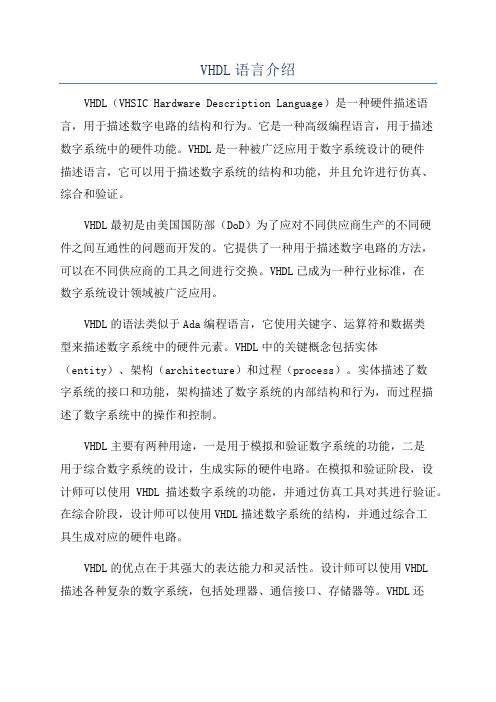

VHDL语言介绍

VHDL语言介绍VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述数字电路的结构和行为。

它是一种高级编程语言,用于描述数字系统中的硬件功能。

VHDL是一种被广泛应用于数字系统设计的硬件描述语言,它可以用于描述数字系统的结构和功能,并且允许进行仿真、综合和验证。

VHDL最初是由美国国防部(DoD)为了应对不同供应商生产的不同硬件之间互通性的问题而开发的。

它提供了一种用于描述数字电路的方法,可以在不同供应商的工具之间进行交换。

VHDL已成为一种行业标准,在数字系统设计领域被广泛应用。

VHDL的语法类似于Ada编程语言,它使用关键字、运算符和数据类型来描述数字系统中的硬件元素。

VHDL中的关键概念包括实体(entity)、架构(architecture)和过程(process)。

实体描述了数字系统的接口和功能,架构描述了数字系统的内部结构和行为,而过程描述了数字系统中的操作和控制。

VHDL主要有两种用途,一是用于模拟和验证数字系统的功能,二是用于综合数字系统的设计,生成实际的硬件电路。

在模拟和验证阶段,设计师可以使用VHDL描述数字系统的功能,并通过仿真工具对其进行验证。

在综合阶段,设计师可以使用VHDL描述数字系统的结构,并通过综合工具生成对应的硬件电路。

VHDL的优点在于其强大的表达能力和灵活性。

设计师可以使用VHDL描述各种复杂的数字系统,包括处理器、通信接口、存储器等。

VHDL还提供了丰富的数据类型和运算符,使设计师可以轻松地描述数字系统中的各种操作。

除了描述数字系统的结构和行为,VHDL还提供了丰富的标准库和模块化编程的方法。

设计师可以使用标准库中提供的各种功能模块来加速开发过程,并且可以将自己设计的模块封装成库以便重复使用。

VHDL还支持面向对象的设计方法,设计师可以使用面向对象的技术来组织和管理复杂的数字系统。

通过使用面向对象的方法,设计师可以将数字系统分解成多个模块,每个模块都有自己的接口和功能,并且可以通过继承和复用来简化设计过程。

VHDL硬件描述语言与数字逻辑电路设计(第五版)侯伯亨章 (2)

第2章 数字系统的算法描述

2.乘法器 乘法器可实现的算法很多。2个4位数乘法的运算过程如表 2-1所示。

第2章 数字系统的算法描述

表中有一个9位寄存器,低4位存放乘数。如果乘数的最低 位(寄存器的最低位)为“1”,则将被乘数加到寄存器的b4~ b7位上;如果为“0”,则不作加法,然后向右移一位。再重 复上述过程,直至将乘数全部移出9位寄存器为止(此例中要移 4位)。将这种算法的运算过程用算法流程图来描述,如图27(a)所示,与该算法流程图对应的硬件电路框图如图2-7(b)所 示。

第2章 数字系统的算法描述

2.2 状态机及算法状态机图描述

众所周知,数字系统由控制单元和处理单元两大部分组成。 控制单元在统一的同步时钟控制下,严格按照一定的时间关系 输出控制信号;处理单元一步一步地完成整个数字系统的操作。 这种工作过程用算法流程图是无法正确描述的。 面介绍一种用于描述控制器工作过程的方法,即算法状态机图 (Algorithmic State Machine Flowchart,ASM图)描述方法。

说明该工作框所对应的硬件操作内容及对应的输出信号。

图2-2 工作框

第2章 数字系统的算法描述

(a) 工作框;(b) 对应的逻辑电路 图2-3 工作框与硬件之间的对应关系

第2章 数字系统的算法描述

通常算法流程图与硬件功能有极好的对应关系。也就是说, 一个工作框的功能应该很容易地映射成为一个较基本的逻辑电 路。图2-3(a)描述两个二进制数a和b相加,其结果为输出c的 工作框;图2-3(b)则是实现该工作框功能的逻辑电路。在设计 数字系统时,如用算法流程图描述其功能,则总要经历由粗至 细逐步细化的过程。所以,在数字系统描述的初期,一个工作 框的功能不一定完全能用一个逻辑电路来实现。但是,随着描 述的逐步细化,设计者应考虑每一个工作框的可实现性,只有 这样,算法流程图最后才能被综合成逻辑电路。

VHDL硬件描述语言.

非法的名称

ill__egle、_illegle、illegle_、2bad、ill

egle、ill/egle

特殊的名称

\74LS04\、\vhdl\、\VHDL\

信号模式 每个端口信号都必须规定信号模式; 信号模式规定信号流动的方向; in out 输入端口 输出端口

inout

buffer

双向端口

VHDL硬件描述语言 Very high speed integration circuits HDL

起源: 1985年,美国国防部提出计划; 1987年成为IEEE1076标准; 1993年进一步修订完善; 是目前标准化程度最高,适应性最广的 HDL语言;

VHDL硬件描述语言 Very high speed integration circuits HDL

简单的实体 entity entity-name is port (signal-name : mode signal-type; …… signal-name : mode signal-type); end entity-name;

比较复杂的实体

ENTITY 实体名 IS

GENERIC语句;

PORT语句;

(BEGIN

决断语句、过程调用、进程说明等)

END 实体名;

VHDL的实体: entity 要点:

实体以 entity

实体名

is

开始;

以end 实体名; 结束; 实体的主要内容为端口(port)说明, 其中主要包括: 实体名、信号名、信号模式、信号类型

实体名称和信号名称 每个实体在设计中对应一个电路模块,

s : in std_logic;

y : out std_logic);

利用VHDL实现(2,1,2)卷积码编码

专业课程设计报告题目:利用VHDL实现(2,1,2)卷积码编码姓名:专业:通信工程班级学号:同组人:指导教师:南昌航空大学信息工程学院20 17 年6 月27 日专业课程设计任务书2016-2017学年第 2 学期第 17 周- 19 周摘要在现代数字通信中,为降低数据传输的误码率,提高通信质量及其可靠性,常在通信中采用纠错编码技术。

其中卷积码就是一种具有较强纠错能力的纠错码。

由于Vitebrbi译码算法比较容易实现,卷积码得到了广泛应用。

本课题简明地介绍了用EDA技术实现卷积码编码器的实现。

卷积码纠错性能常常优于分组码,是一种性能优越的信道编码。

由于码字之间的相关性,其编码器要利用移位寄存器来存储状态。

随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。

卷积码作为通信系统中重要的编码方式,以其良好的编码性能,合理的译码方式,被广泛应用。

本文在阐述卷积码编码器基本工作原理的基础上,给出了(2,1,2)卷积编码器的VHDL设计,在QuartusⅡ环境下进行了波形功能仿真,并下载到EP1C6T144C8N芯片上进行验证,最终实现输入四位序列,编码输出八位通过指示灯显示。

关键词:卷积码QuartusⅡEP1C6T144C8N目录:摘要 (4)目录: (5)第一章系统设计要求 (6)1.1系统设计要求 (6)第二章系统组成与工作原理 (6)2.1系统组成 (6)2.2编码器设计原理 (6)2.2.1结构图法描述编码器 (7)2.2.2(2,1,2)卷积码的状态转移图 (8)第三章编码器设计方案与对比选择 (9)第四章 VHDL语言实现及仿真调试 (10)4.1编码器电路设计 (10)4.2VHDL描述编码器 (11)4.2调试 (12)第五章 FPGA编程下载 (15)第六章实验心得 (16)参考文献 (17)第一章系统设计要求1.1系统设计要求1.设计一个(2,1,2)卷积码编码器。

2.在FPGA上用VHDL硬件描述语言实现上述编码器和译码器。

硬件描述语言

上一页 下一页 返回

architecture

inhabit_arch of inhibit is 一结构体定义 begin z<='1' when x='1' and y='0' else '0'; end;

下面请看演示

上一页 下一页 返回

5.1 VHDL概述

(2)VHDL的并发性 计算机软件程序一般按书写的顺序依次执行, 而VHDL却具有并发性。VHDL的并发性体现在 两个方面,首先在使用VHDL进行数字电路设计 时存在并发性,即VHDL支持设计分解,可使被 分解的各个子部分的设计并行完成。一个模型 的设计主要由3部分组成:元件库部分—USE说 明区:实体部分—确立模型与环境的接口;结 构体部分—描述元件的行为或功能,为模型生 成测试向量,并捕获模型输出信号状态以供分 上一页 下一页 返回 析。

5.2 VHDL的程序结构

【例5-2】一个与门电路的VHDL程序 library ieee; use ieee.std_logic_1164.all; 一 打开需要用到的库 entity inhibit is 一实体(端口)说明 port( x,y:in std_logic; z:out std_logic); end inhibit;

上一页 下一页 返回

5.1 VHDL概述

VHDL是为数字电路的建模和模拟

(simulation)而制定的,是一种面向模拟、 针对硬件的语言。它的语法中有许多方面 均考虑到模拟与硬件的因素,包括VHDL的 硬件相关结构、并发特征和混合级描述以 及混合级模拟。

5.1 VHDL概述

(1)VHDL中的硬件相关结构 VHDL具有许多与数字电路结构直接相关的 概念,其中最主要的是元件(component), 它是数字硬件结构—"黑盒"或"模块"的抽 象。VHDL中的元件由实体和结构体两部分 共同描述完成。

第2章 VHDL语言基础

End 实体名;

端口名

端口模式

数据类型

(2)ENTITY

端口模式(MODE)有以下几种类型: IN ;OUT;INOUT ;BUFFER 端口模式可用下图说明:(黑框代表一个设计或模块)

IN

OUT

BUFFER

INOUT

二输入与门电路设计范例

Library std; Use std.standard.all;

(4)CONFIGURATION定义区

定义格式: Configuration 配置名 of 实体名 is for 选用的结构体名 end for; end configuration 配置名 ;

二输入与门电路设计范例

a c

b电Leabharlann 真值表abc

0

0

0

1

0

0

0

1

0

1

1

1

二输入与门电路设计范例

Architecture Na of and2 is

‘1’; 符号<=为信号直接赋值符。

End Na;

--结构体Na

Architecture Nb of and2 is

Begin

c <= a and b;

--and 为逻辑与操作

End Nb; --结构体Nb

Library ieee; Use ieee.std_logic_1164.all;

Entity half_adder is Port( x,y : in std_logic;sum,carry : out hlf_adder); End half_adder;

(4)CONFIGURATION定义区

一个完整VHDL电路设计必须有一个实体 和对应的结构体,即实体和结构体对构成一个 完整的VHDL设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

例1: …… L2: loop a:=a+1; exit L2 when a >10; end loop L2; ……

26

2)for … loop 语句 ) [标号]:for 循环变量 in 离散范围 顺序处理语句; end loop [标号]; loop

特点: ①循环变量是 loop 内部自动声明的局部量,仅 在 loop 内可见;不需要指定其变化方式。 ②离散范围必须是可计算的整数范围: 整数表达式 to 整数表达式 整数表达式 downto 整数表达式

15

例:用case 语句描述四选一电路

16

例:case 语句的误用 signal value : integer range 0 to 15 ; signal out_1 : bit ; case value is -- 缺少 when条件语句 end case ; case value is -- 分支条件不包含2到15 when 0 => out_1 <= ‘1’ ; when 1 => out_1 <=‘0’ ; end case ; case value is -- 在5到10上发生重叠 when 0 to 10 => out_1 <= ‘1’ ; when 5 to 15 => out_1 <= ‘0’ ; end case ;

18

BEGIN PROCESS( A ) BEGIN CASE A(3 DOWNTO 0) IS WHEN "0000" => LED7S <= "0111111" ; -- X"3F"'0 WHEN "0001" => LED7S <= "0000110" ; -- X"06"'1 WHEN "0010" => LED7S <= "1011011" ; -- X"5B"'2 WHEN "0011" => LED7S <= "1001111" ; -- X"4F"'3 WHEN "0100" => LED7S <= "1100110" ; -- X"66"'4 WHEN "0101" => LED7S <= "1101101" ; -- X"6D"'5

27

例:用 for … loop 语句描述的8位奇校验电路

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY P_CHECK IS PORT (a:IN STD_LOGIC_VECTOR(7 DOWNTO 0); Y:OUT STD_LOGIC); END P_CHECK; ARCHITECTURE ART OF P_CHECK IS BEGIN PROCESS(A) variable TMP:STD_LOGIC; BEGIN TMP:='1';

9

if_then_elsif 语句中隐含了优先级别的判断, 最先出现的条件优先级最高,可用于设计具有优 先级的电路。如8-3优先级编码器。 library ieee; use ieee.std_logic_1164.all; entity coder is port(input: in std_logic_vector(7 downto 0); output: out std_logic_vector(2 downto 0)); end coder;

20

例2:2输入的与门电路描述

library ieee; use ieee.std_logic_1164.all; entity and22j is port(a:in std_logic; b:in std_logic; y:out std_logic); end and22j; architecture behave of and22j is begin p1:process(a,b)

5.3 VHDL顺序语句(Sequential) 顺序语句( 顺序语句 )

ENTITY

ARCHITECTURE Process Process ports

Sequential Process Combinational Process

ports

component

硬件执行:并发执行(VHDL本质) 仿真执行:顺序执行、并发执行 分为两大类:顺序(Sequential)描述语句 并发(Concurrent)描述语句

11

elsif input(3)=‘0’ then output<=“100”; elsif input(2)=‘0’ then output<=“101”; elsif input(1)=‘0’ then output<=“110”’; else output<=“111”; end if; end process; end art;

5.3.1 转向控制语句 转向控制语句

转向控制语句通过条件控制开关决定是否执 行一条或几条语句,或重得执行一条或几条语句, 或跳过一条或几条语句。 分为五种: if 语句、case 语句、 loop 语句、next 语句、 exit 语句

3

1、 if 语句 、

if 语句执行一序列的语句,其次序依赖于一 个或多个条件的值。 1)if 语句的门闩控制 ) if 条件 then 顺序处理语句; end if ; 例: if (ena = ‘1’) then q <= d; end if; 综合后生成锁存器(latch)

17

例1:七段数码管驱动电路(电子时钟的 :七段数码管驱动电路(电子时钟的DISP) ) LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; ENTITY segment7 IS PORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0) ; LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ) ; END ; ARCHITECTURE one OF segment7 IS

19

Байду номын сангаас

WHEN "0110" => LED7S <= "1111101" ; -- X"7D"'6 WHEN "0111" => LED7S <= "0000111" ; -- X"07"'7 WHEN "1000" => LED7S <= "1111111" ; -- X"7F"'8 WHEN "1001" => LED7S <= "1101111" ; -- X"6F"'9 --WHEN "1010" => LED7S <= "1110111" ; -- X"77"'10 --WHEN "1011" => LED7S <= "1111100" ; -- X"7C"'11 --WHEN "1100" => LED7S <= "0111001" ; -- X"39"'12 --WHEN "1101" => LED7S <= "1011110" ; -- X"5E"'13 --WHEN "1110" => LED7S <= "1111001" ; -- X"79"'14 --WHEN "1111" => LED7S <= "1110001" ; -- X"71"'15 WHEN OTHERS => NULL ; END CASE ; END PROCESS ; END ;

21

variable comb:std_logic_vector(1 downto 0); begin comb:=a & b; case comb is when "00"=>y<='0'; when "01"=>y<='0'; when "10"=>y<='0'; when "11"=>y<='1'; when others=>y<='X'; end case; end process p1; end behave;

22

寄存器传输级 描述形式

例3:2输入的与门电路描述

library ieee; use ieee.std_logic_1164.all; entity and22 is port(a:in std_logic; b:in std_logic; y:out std_logic); end and22; architecture behave of and22 is begin y<=a and b;

4

条件改为时钟沿,则生成 D触发器:

5

2)if 语句的二选择控制 ) 格式: if 条件 then 顺序处理语句; else 顺序处理语句; end if ; 用条件来选择两条不同程序执行的路径。