VerilogHDL1-2(语法)

第04讲 Verilog-HDL语法——第2部分 语法要点

` timescale

`timescale 说明延时单位及延时精度

格式:`timescale <time_unit> / <time_precision> 如:`timescale 1 ns / 100 ps

`timescale必须在模块之前出现 `timescale 1 ns / 100 ps // All time units are in multiples of 1 nanosecond module MUX2_1 (out, a, b, sel); output out; input a, b, sel; wire sel_;

12 'H83a 8'b1100_ 0001 64'hff01 9'O17 32'bz01x 3’b1010_ 1101 6.3 32e- 4 4.1E3 unsized decimal (zero-extended to 32 bits) unsized hexadecimal (zero- extended to 32 bits) 8-bit binary 64-bit hexadecimal (zero- extended to 64 bits) 9-bit octal Z-extended to 32 bits 3-bit number, truncated to 3’b101 decimal notation scientific notation for 0.0032 scientific notation for 4100

hex

oct

dec

bin

ACSII

string

time

strength module

转义符

\t \n \\ \” %% \<1-3 digit octal number>

[工学]西安电子科技大学verilog教程1-2

![[工学]西安电子科技大学verilog教程1-2](https://img.taocdn.com/s3/m/7e9aa877240c844768eaeea1.png)

西安电子科技大学

雷达信号处理国防科技重点实验室

2. 数字信号处理

数字信处理系统往往要进行一些复杂的数字运算和数据处理, 并且又有实时响应的要求,他们通常是由高速专用数字逻辑系统或专 用数字信号处理器所构成,电路是相当复杂的。因此只有在高速大规 模集成电路设计制造技术进步的基础上,才有可能实现真正有意义的 实时数字信号处理系统。对实时数字信号处理系统的要求不断提高, 也推动了高速大规模集成电路设计制造技术的进步。现代专用集成电 路的设计是借助于电子电路设计自动化(EDA)工具完成的。学习和 掌握硬件描述语言(HDL)是使用电子电路设计自动化工具的基础。

• 由传统的观点出发,可以从三个不同的方面来研究计算,即从数 学、科学和工程的不同角度;由比较现代的观点出发,可以从四 个主要的方面来研究计算,即从算法和数据结构、编程语言、体 系结构、软件和硬件设计方法学。

• 一个复杂的数字系统设计往往是从算法到由硬线连接的门级逻辑 结构,再映射到硅片的逐步实现的过程。

&Moorby,刘明业等译。

西安电子科技大学

雷达信号处理国防科技重点实验室

课时及考试安排

授课时数:30课时 上机时数;14课时 考试时数:90分钟 成绩计算:大作业*40%+考试*60%

西安电子科技大学

雷达信号处理国防科技重点实验室

课程内容安排

第一部分 初级篇

第一章. 概述及设计工具介绍 第二章. Verilog HDL的基本知识 第三章. Verilog HDL基本概念 第四章. 常用Verilog语法之一 第五章.常用Verilog语法之二 第六章.常用Verilog语法之三 第七章.常用Verilog语法之四 第八章.常用Verilog语法之五

常用VerilogHDL 语法总结

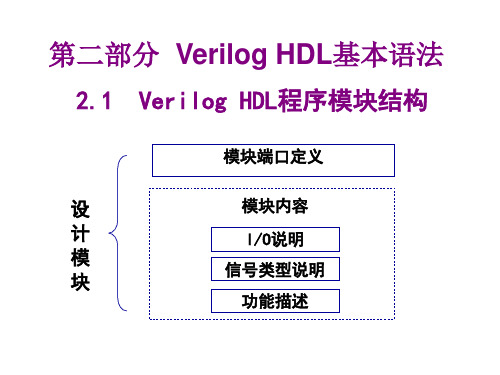

常用VerilogHDL 语法总结1 模块(1)端口定义:声明模块的输入输出口。

引用模块时端口的两种连接方法。

(2)模块内容:I/O说明(输入输出)、内部信号说明(和端口有关的变量说明)、功能定义(定义逻辑功能的三种方式:assign 声明语句;实例元件;always 块)。

(3)理解要点:整体语句并发执行,always块内顺序执行。

2 常量(1)数字:整数及三种表达方式x和z值负数:减号的位置下划线:位置和作用(2)参数:parameter符号常量,常用于定义延迟时间(使用#)和变量宽度。

3 变量(1)wire:表示易assign指定的组合逻辑信号;默认值;任何方程式的输入或assign语句及实例元件的输出;定义格式。

(2)reg:表示always块中指定的信号,代表触发器;寄存器数据类型(触发器存储值),默认值为x;定义格式。

(3)memory:reg的数组;描述RAM、ROM、reg文件;单元索引;一个n为寄存器和n个一位数组的区别。

4 运算符与表达式(1)算术运算符:五种(2)位运算符:五种(3)逻辑运算符:三种(4)关系运算符:四种(3种不同的返回值)(5)等式运算符:四种(6)移位运算符:两种(移位补零)(7)位拼接运算符:{},常用于某些控制信号位;重复与嵌套使用(8)缩减运算符:类似于逻辑运算符,结果为一位二进制数(9)运算符优先级5 语句(1)赋值语句阻塞赋值:b<=a;块结束后完成赋值,b的值不是立即改变的,较为常用;非阻塞赋值:b=a;赋值语句执行后块才结束,b的值马上改变,在沿触发的always块中使用可能引起错误后果。

(2)块语句顺序块begin-end:顺序执行,最后语句执行完流程跳出语句块;并行块fork-join:同时执行,时间最长语句执行完或disable语句执行时跳出程序块;块名的作用;起始时间和结束时间(3)条件语句If-else语句:三种形式;if表达式判断;分号;复合语句;表达式简写;if语句嵌套;if与else的配对。

了解VerilogHDL语法规则吗,看完这篇就知道了

了解VerilogHDL语法规则吗,看完这篇就知道了本节介绍Verilog HDL语法规则,包括文字规则、数据对象及运算符的使用等。

Verilog HDL文字规则1.关键词与标识符关键词是Verilog HDL中预先定义的单词,它们在程序中有特别的使用目的。

已经被用作关键词的单词不可以在程序中另作他用,见表3-1。

不同版本的Verilog HDL硬件描述语言中定义的关键词数目略有变化,Verilog 1995的关键词有97个,Verilog 2001共102个。

标识符是用户编程时给对象定义的名称,对象包括:常量、变量、模块、寄存器、端口、连线、示例和beginend块等元素。

定义标识符时应遵循如下规则:只能由26个大小写英文字母、数字和下划线组成。

标识符的第一个字符必须是英文字母或下划线。

字符中的英文字母区分大小写。

【例3-7】判断下面标识符是否合法。

2.注释与C语言一样,硬件描述语言中的注释也不会被编译。

在Verilog HDL中有两种形式的注释方式:采用/* */,多用于多行注释。

采用//,用于单行注释。

【例3-8】注释举例。

在实际使用中,很多公司的编程规范明确表明,注释行中不提倡采用第一种/**/的注释方式,不允许使用中文注释。

3.常数的表示在Verilog HDL中,常数用来表示在程序中不随意变化的量,常数分为整数、实数及字符串三大类型。

(1)整数型常数是数字电路中最常用到的类型,在Verilog HDL中有两种表示方法:简单的十进制格式,例如-50、6等。

基数格式,其表达方式一般如下:〈位宽〉是十进制数值表示的常数化成二进制时对应的宽度,〈进制符号〉用进制符号b或B(二进制)、o或O(八进制)、d或D(十进制)、h或H(十六进制)表示常数的进制格式,即二进制、八进制、十进制、十六进制这4种进制表示。

数字的位宽可以默认,如果没有定义长度,数的长度由具体机器系统决定(至少是32位)。

【例3-9】常数表示方法举例。

VerilogHDL语法基础

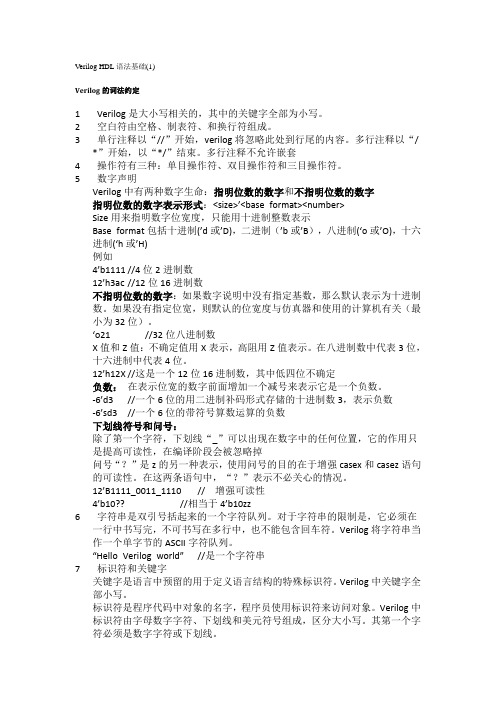

Verilog HDL语法基础(1)Verilog的词法约定1Verilog是大小写相关的,其中的关键字全部为小写。

2空白符由空格、制表符、和换行符组成。

3单行注释以“//”开始,verilog将忽略此处到行尾的内容。

多行注释以“/ *”开始,以“*/”结束。

多行注释不允许嵌套4操作符有三种:单目操作符、双目操作符和三目操作符。

5数字声明Verilog中有两种数字生命:指明位数的数字和不指明位数的数字指明位数的数字表示形式:<size>’<base format><number>Size用来指明数字位宽度,只能用十进制整数表示Base format包括十进制(’d或’D),二进制(’b或’B),八进制(‘o或’O),十六进制(‘h或’H)例如4’b1111 //4位2进制数12’h3ac //12位16进制数不指明位数的数字:如果数字说明中没有指定基数,那么默认表示为十进制数。

如果没有指定位宽,则默认的位宽度与仿真器和使用的计算机有关(最小为32位)。

‘o21//32位八进制数X值和Z值:不确定值用X表示,高阻用Z值表示。

在八进制数中代表3位,十六进制中代表4位。

12’h12X //这是一个12位16进制数,其中低四位不确定负数:在表示位宽的数字前面增加一个减号来表示它是一个负数。

-6’d3//一个6位的用二进制补码形式存储的十进制数3,表示负数-6’sd3//一个6位的带符号算数运算的负数下划线符号和问号:除了第一个字符,下划线“_”可以出现在数字中的任何位置,它的作用只是提高可读性,在编译阶段会被忽略掉问号“?”是z的另一种表示,使用问号的目的在于增强casex和casez语句的可读性。

在这两条语句中,“?”表示不必关心的情况。

12’B1111_0011_1110// 增强可读性4’b10??//相当于4’b10zz6字符串是双引号括起来的一个字符队列。

对于字符串的限制是,它必须在一行中书写完,不可书写在多行中,也不能包含回车符。

VerilogHDL基本语法

c a b

源程序如下

1

&

&

&

out

module example_2_3 out,a,b,c ;

input

a,b,c;

output out;

assign out = a b:c;

endmodule

ห้องสมุดไป่ตู้

9. 位并接操作符 Concatenation operators 并接操作符为:{} 并接操作符的使用格式: {操作数1的某些位,操作数2的某些位,…,操作数n的某 些位};

⑤ 可以用/*……*/或//……对Verilog HDL程序的任 何部分作注释。

一个完整的源程序都应当加上需要的注释,以 加强程序的可读性。

2.2 Verilog HDL的词法

2.2.1 空白符和注释

Verilog HDL的空白符包括空格、tab符号、换行 和换页。

空白符如果不是出现在字符串中,编译源程序时 将被忽略。

input

端口1,端口2,端口3,…;

output

端口1,端口2,端口3,…;

例如

input

ina,inb,cin;

output

sum,cont;

2. 信号类型声明

信号类型声明用来说明设计电路的功能描述中,所用的 信号的数据类型以及函数声明。

信号的数据类型主要有连线 wire 、寄存器 reg 、整型 integer 、实型 real 和时间 time 等类型。

8. 条件操作符 Conditional operators 条件操作符为: :

条件操作符的操作数有3个,其使用格式为 操作数 = 条件 表达式1:表达式2;

即当条件为真 条件结果值为1 时,操作数 = 表达 式1;为假 条件结果值为0 时,操作数 = 表达式2。

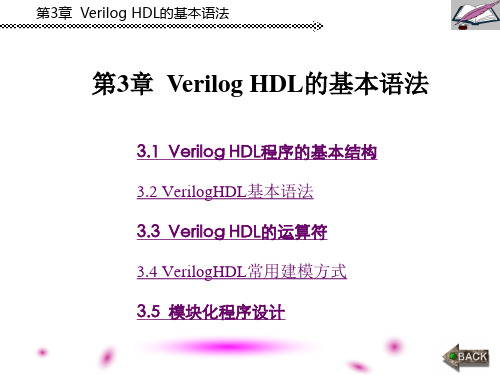

第3章 Verilog HDL的基本语法

3.1.1 VerilogHDL设计风格 1.VerilogHDL功能描述方式

VerilogHDL可综合硬件逻辑电路的功能描述通常有三种 方式:结构描述方式、数据流描述方式和行为描述方式。

(1)结构描述方式也称为门级描述方式,是通过调用 VerilogHDL语言预定义的基础元件(也称为原语,即 Primitive), 比如逻辑门元件,并定义各元件间的连接关系来构建电路。 这种方式构建的电路模型综合和执行效率高,但描述效率低, 难于设计复杂数字系统。

第3章 Verilog HDL的基本语法

2.端口说明 端口说明用于说明端口列表中每个端口的位宽和输入/ 输出方向。输入/输出方向可用input、output或inout进行说明。 input输入端口说明格式为input[msb1:lsb1]端口名11,端口名 12,…;、 input[msb2:lsb2]端口名21,端口名22,…; output输出端口说明格式为 output[msb1:lsb1]端口名11,端口名12,…; output[msb2:lsb2]端口名21,端口名22,…; inout双向端口说明格式为 inout[msb1:lsb1]端口名11,端口名12,…; inout[msb2:lsb2]端口名21,端口名22,…;

第3章 Verilog HDL的基本语法

5.并行执行 作为电路建模语言,在学习 VerilogHDL时必须注意的是, 模块中的实例化语句、连续赋值语句与过程块之间是并行执 行的。这是 VerilogHDL与一般高级语言最为不同的地方。 若 Verilog模块用到了多个实例引用语句,或者多个 assign语句,或者多个always块,或者将这些语句混合使用,那 么它们的书写顺序是任意的,因为它们对仿真程序和综合程 序的执行来说是并行的。也就是说,当它们被综合器综合成 实际电路时,会形成不同的电路块,当输入信号变化时,这些电 路块在满足延时的条件下同时动作,是并行执行的。 但是,需要明确的是,always块内部的高级抽象描述语句 是按顺序执行的。因为“if…else…”这样的语句若不按顺序 执行,其功能就没有任何意义。

VerilogHDL基本语法解析

125//表示十进制数125

X和Z表示位数的特殊性:

input

端口1,端口2,端口3,…;

output

端口1,端口2,端口3,…;

例如

input

ina,inb,cin;

output

sum,cont;

2. 信号类型声明

信号类型声明用来说明设计电路的功能描述中,所用的 信号的数据类型以及函数声明。

信号的数据类型主要有连线(wire)、寄存器(reg)、 整型(integer)、实型(real)和时间(time)等类型。

always @(posedge clk) //时钟上升沿,每次上升沿, 执行always语句

begin

if (clr)

out <=8'b0;

else if (load) out <= data;

else

out <= out+8'b1;

end

assign cout = &out & cin; //”&out”-与缩减运算式

注释分为行注释和块注释两种方式。行注释用 符号//(两个斜杠)开始,注释到本行结束。块注 释用/*开始,用*/结束。块注释可以跨越多行,但 它们不能嵌套。

2.2.2 常数

Verilog HDL的常数包括数字、未知X和高阻Z三 种。数字可以用二进制、十进制、八进制和十六进制 等4种不同数制来表示,完整的数字格式为

//模块端口定义 input ina,inb,cin; output sum,cout;//I/O声明 assign {cout,sum} = ina+inb+cin;

//功能描述语句 endmodule //endmodule后不加分号

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

c

5、模块的结构

内部信号说明:在模块内用到的和与端口有关的wire 和 reg 变量的声 明。 如: reg [width-1 : 0] R变量1,R变量2 。。。。; wire [width-1 : 0] W变量1,W变量2 。。。。;

module sample( q, a, clk ); input [3:0] a; input clk; output [3:0] q; wire reg wire …... endmodule a, clk; // 默认,可以省略 q; // 输出端口类型定义 c; // 模块内信号线的定义

Verilog HDL模块的基本概念

Verilog HDL程序是由模块构成的。每个模块的内容都 是嵌在module和endmodule两个语句之间。每个模块实 现特定的功能。 模块是可以进行层次嵌套的。可以将大型的块分割成不 同的小模块来实现特定的功能,最后通过顶层模块调用 子模块来实现整体功能。 每个模块要进行端口定义,并说明输入输出口,然后对模 块的功能进行行为逻辑描述。 Verilog HDL区分大小写。也就是说大小写不同的标识 符是不同的。此外,Verilog HDL是自由格式的,即结 构可以跨越多行编写,也可以在一行内编写。空白(新 行、制表符和空格)没有特殊意义。 除了endmodule语句外,每个语句和数据定义的最后必须 有分号。 可以用/*.....*/和//.......对Verilog HDL程序的任何部分 作注释。

module <模块名> (<输入、输出端口列表>) /*端口描述*/ output <输出端口列表>; input <输入端口列表>; /*内部信号声明*/ wire //nets型变量,通常缺省 reg //register变量 integer /*逻辑功能定义*/ /*任务或函数*/ task或 function /*使用assign语句定义逻辑功能*/ assign <结果信号名>=<表达式>; /*使用always块描述逻辑功能*/ always @(<敏感信号表达式>) begin //过程赋值 //条件语句 //循环语句 //task,function 调用 end /*元件例化*/ <module_name模块名><instance_name例化元件名>(<port_list端口列表>); endmodule

2、Verilog HDL模块的基本概念

/*一个名为adder的三位加法器的例子*/

module adder ( count,sum,a,b,cin ); //模块定义开始

input [2:0] a,b; input cin; output count; output [2:0] sum;

//输入信号定义 //输入信号定义 //输出信号定义 //输出信号定义

模块的结构

时延: Verilog HDL模型中的所有时延都根据时间单位定义。

Assign #2 Sum = A ^ B; //# 2指2个时间单位。 使用编译指令将时间单位与物理时间相关联。编译器指令 需在模块描述前定义

` timescale 1ns /100ps 此语句说明时延时间单位为1ns并且时间精度为100ps (时间 精度是指所有的时延必须被限定在0.1ns内)。 如果此编译器指令所在的模块包含上面的连续赋值语句, #2 代表2ns。

Verilog HDL模块的基本概念

/*一个模块调用(例化)的例子*/

module trist1(out,in,enable); output out; input in, enable; mytri tr由mytri模块定义的实例元件tri_inst endmodule module mytri(out,in,enable); output out; input in, enable; assign out = enable? in : 'bz; endmodule

Verilog HDL硬件描述 语言

Hardware Description Language(HDL)

第一部分

语法

1.Verilog HDL程序结构:

Verilog HDL程序模块包括模块名、输入输出端口说明、内 部信号说明、逻辑功能定义等几个部分,内容都是嵌在module和 endmodule两个关键字之间 。程序模板如下:

assign {count,sum} = a + b + cin; //模块功能描述 endmodule //模块定义结束

Verilog HDL模块的基本概念

/*一个名为compare的比较器例子*/

module compare ( equal,a,b ); output equal; //声明输出信号equal input [1:0] a,b; //声明输入信号a,b /*如果a、b 两个输入信号相等,输出为1,否则为0*/ assign equal=(a==b)?1:0; endmodule

模块的结构

模块的功能定义可以用采用下面的4种方式描述:

1) 数据流方式; 2) 行为方式; 3) 结构方式; 4) 混合描述方式。

模块的结构

数据流描述方式:

用连续赋值语句“assign” ,只能描述组合逻辑。

连续赋值语句的语法为: assign [delay] LHS_net = RHS_ expression

2-4解码器电路

连续赋值语句是并发执行的,也就是说各语句的执行顺序与其 在描述中出现的顺序无关。

模块的结构

行为描述方式:

•

用类似软件程序中的各种运算符,直接表示输入输出信号之间的关系的 描述方法称为行为描述。

无论右边的操作数何时发生变化, 右边表达式都重新计算, 并且在指定的时延后赋给左边线网变量。 如果没有定义时延值, 缺省时延为0。

模块的结构

`timescale 1ns/ 1ns module Decoder2x4 (A, B, EN, Z); input A, B, EN; output [ 3:0] Z; wire Abar, Bbar; assign #1 Abar = ~ A; assign #1 Bbar = ~ B; assign #2 Z[0] = ~ (Abar & Bbar & EN) ; assign #2 Z[1] = ~ (Abar & B & EN) ; assign #2 Z[2] = ~ (A & Bbar & EN) ; assign #2 Z[3] = ~ (A & B & EN) ; endmodule

模块组成

模块开始 模块名称

module block(a,b,c,d); input a,b; 输入端口 output c,d; 输出端口

assign c = a | b; assign d = a & b; endmodule

模块结束

block

a

b

逻辑功能

c d

输出端口

1. 端口定义 模块的端口声明了模块的I/O口,其格式如下: module 模块名(端口1,端口2,端口3……); 2. 输入输出端口说明 输入输出端口说明格式如下: 输入端口:input 端口1,端口2……端口n; 输出端口:output 端口1,端口2……端口n; 双向端口:inout 端口1,端口2……端口n; 3. 内部信号说明 定义各变量或常量的类型,其格式为: wire 数据名1,数据名2,数据名3……; reg 数据名1,数据名2,数据名3……; //位宽说明

模块的端口定义: 模块的端口声明了模块的输入输出口。其格式如下: module 模块名(端口1,端口2,端口3,………); 如:module sample ( q, a, b, sel, clk, resetn ) ;

模块的结构

I/O说明:对输入输出端口的属性进行定义,包括端口的方向、 信号位宽等。 定义端子方向有如下语句: input(输入端口) output(输出端口) 高 低 位 位 inout(双向端口) 定义信号位宽: 信号类型 [MSB:LSB] 信号名 如:input [11:0] address; output [ 0:7] data; I/O说明也可写在端口声明语句里,Verilog 2001支持下面的描 述方式。 module adder_16 (output reg [15:0] sum,output reg cout, input wire cin, input wire [15:0] a, b);

3、模块的结构

“模块”(block)是Verilog的基本设计单元。 一个模块是由两部分组成的,一部分描述接口,另一部分描述逻辑功能,即 定义输入是如何影响输出的。 module block (a,b,c,d); input a,b; output c,d; assign c= a | b ; assign d= a & b; endmodule

4、编写Verilog HDL模块的练习

请在下面的空格中填入适当的符号 使其成为右图的Verilog 模块 :

module block1(a, b, —, —, — ); input —, —, —; —— d, — ; assign d = a | ( b & ~c) ; assign e = ( b & ~c ); _______

Module <模块名> (<输入、输出端口列表>) /*端口描述*/ output <输出端口列表>; input <输入端口列表>; /*端口和内部信号声明*/ wire //nets型变量,通常缺省 reg //register变量 integer /*逻辑功能定义*/ /*任务或函数*/ task或 function /*使用assign语句定义逻辑功能*/