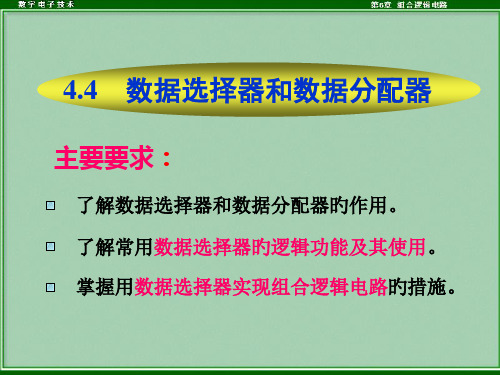

数据选择器与分配器

第十八讲 数据选择器与分配器

组合逻辑电路

CC14539 数据选择器 1 真值表

输 入 输出 1ST A1 A0 1D3 1D2 1D1 1D0 1Y 使能端低电平有效 1 ×× × × × × 0 0 0 0 × × × 0 0 1D0 0 0 0 × × × 1 1 1ST = 1 时,禁止数据 选择器工作,输出 1Y = 0。 0 0 1 × × 0 × 0 1D 0 0 1 × × 1 ×1 1 0 1 0 × 0 × ×0 1D2 1ST = 0 时,数据选择 0 1 0 × 1 × ×1 器工作。输出哪一路数据 0 1 1 0 × × ×0 1D 由地址码 A1 A0 决定。 0 1 1 1 × × ×1 3

一路输入

D

Y0 Y Y11= D Y2 Y3

多路输出

地址码输入

A1 0

A0 1

EXIT

组合逻辑电路

二、数据选择器的逻辑功能及其使用

1.

8 选 1 数据选择器 CT74LS151

Y ST Y 互补输出端 8 路数据输入端

使能端,低 电平有效

地址信号 输入端

ST A2 CT74LS151 A1 A0 D0D1 D2 D3 D4 D5 D6 D7

0 1 Y = A2A1A0D0 + A20 1A0D1 + A Y = A2A1A0D0 + A2A1A0D1 + 1 0 A2A1A0D2+ A20 1A0D3+ A A2A1A0D2+ A2A1A0D3+ 0 A2A1A0D4+ A20 1A0D5+ A A2A1A0D4+ A2A1A0D5+ 0 A2A1A0D6+ A20 1A0D7 A A2A1A0D6+ A2A1A0D7

3.5 数据分配器与数据选择器-数字电子技术基础(第3版)-林涛-清华大学出版社

A1

An-1

数

据 选

F

择

器

EN

2 电路工作原理分析

EN

D0 D1 D2 D3 A0

A1

电路基本结构为与或形式

& >1 Y=EN Dimi

Y

功能表

输入

输出

EN A1 A0

Y

1XX

0

00 0

D0

00 1

D1

01 0

D2

01 1

D3

3 集成电路数据选择器 1) 74LS151

D0

八选一

D7

数据 Y

选择器 W

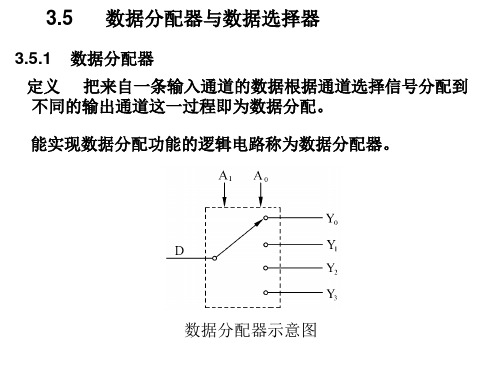

3.5 数据分配器与数据选择器

3.5.1 数据分配器 定义 把来自一条输入通道的数据根据通道选择信号分配到 不同的输出通道这一过程即为数据分配。 能实现数据分配功能的逻辑电路称为数据分配器。

数据分配器示意图

数据分配器可以直接用译码器来实现,例如:

A0

A0

Y0

Z0

A1

A1

Y1

Z1

A2

A2

Y2

Z2

74LS138 Y3

形式为可控最小项之和

只有适当选取Di的值为1或0,即可实现最小项表达式

方法

真值表法 比较系数法 卡诺图法

例 1 用八选一数据选择器实现 L X Y Z

XY Z

00 0 00 1 01 0 01 1 10 0 10 1 11 0 11 1

L Di

00 11 11 00 11 00 00 11

0 D0

Z3

1S1Y4来自Z4Y5Z5D

S2

Y6

Z6

S3

Y7

Z7

Zi Yi S1S2S3mi Dmi

数据分配器和数据选择器-

MSI双四选一数据选择器74LS153

图2-19 74LS153的逻辑符号和引脚排列图

ҧ

控制输入端低电平有效。

13

Y ( A1 , A0 ) S (m0 D0 m1D1 m2 D2 m3 D3 )

四选一数据选择器的功能表

表2-10

输入

输出

ത A1 A0

Y

0

0

0

0

1

D0

D1

解:假设三变量为A、B、C,表决结果为F,则真值表如表

2-12所示。

A B C

F

0

0

0

0

1

1

1

1

0

0

0

1

0

1

1

1

表2-12

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

例2-6的真值表

20

则

F ( A, B, C ) m3 m5 m6 m7

在八选一电路中,将A、B、C从A2、A1、A0

输入,令

D3 = D5 =D6 =D7 =1

1

0

电路0

1

0

电路1

1

0

电路7

A2 A1 A0

6

思考:数据可以从S1或3 输入吗?

7

第2章 加法器与密码锁(MSI组合逻辑电路)

2.3 数据选择器

2.3.1 数据选择器的工作原理

2.3.2 八选一数据选择器74LS151

2.3.3 数据选择器实现组合逻辑函数

2.3 数据选择器(Mux)

在多路数据传送过程中,能够根据需要将其中任意一路挑

数据选择器与数据分配器

L ABC ABC AB

图4-32 例4-8的逻辑电路图

1.3 数据分配器

数据 输入端

数 据

输

出

端

选择端

图4-33 数据分配器示意图

1.3 数据分配器

D

数据 分配器

Y0 Y1

Y2

Y3

A1 A0

表4-17 1路-4路数据分配器真值表

1

0

D7

inst MULTIPLEXER

GN

D7

D6

D5

D4

D3

WN

D2

Y

D1

D0

C

B

A

ቤተ መጻሕፍቲ ባይዱ74151

(a) 8选1数据选择器74LS151

inst MULTIPLEXER

2C3

2C2

2C1

2C0

2GN

1C3

2Y

1C2

1Y

1C1

1C0

1GN

B

A

74153

(b) 双4选1选择器74LS153

出

W

1

D0 D1 D2 D3 D4 D5 D6 D7

数字电子技术

数据选择器与数据分配器

1.1 数据选择器

数

据

数据输出端

输

入

端

选择端 图4-27 2n选一数据选择器示意图

1.1 数据选择器

D0

四选一

D1

数据

Y

D2

选择器

D3

A1 A0

图4-28 四选一数据选择器逻辑符号

表4-15 四选一数据选择器真值表

数据选择和分配器

输 S 1 0 0 0 0 D × D0 D1 D2 D3

入 A1 × 0 0 1 1 A0 × 0 1 0 1

输 出 Y 0 D0 D1 D2 D3

1S

A1 1D3 1D2 1D1 1D0 1Y GND

选通控制端S为低电平有效, 时芯片被选中, 选通控制端 为低电平有效,即S=0时芯片被选中, 为低电平有效 时芯片被选中 处于工作状态; 时芯片被禁止, 处于工作状态;S=1时芯片被禁止,Y≡0。 时芯片被禁止 。

L = A B C + A BC + AB

1 3个变量,选用4 选1数据选择器。

1

确定数据选择器

2

选用74LS153 选用

2 74LS153有两个 地址变量。确定地址量A1=A、A0=B 、

3

(1)公式法 )

函数的标准与或表达式:

3

L = A B C + A BC + AB = m0C + m1C + m2 ⋅ 0 + m3 ⋅ 1

数据输出端

地址 信号 输入 端

输入数据端

使能端,输入 使能端 输入 低电平有效

选 数 据 选 择 器 的 真 值 表

4 1

Y = ( A1 A 0 D0 + A1 A0 D2 + A1 A 0 D3 + A1 A0 D3 ) ST

当 ST =1时,输出 =0,数据选择器不工作。 时 输出Y= ,数据选择器不工作。 当 ST =0时,数据选择器工作。其输出为 时 数据选择器工作。

A0 1

1路-4路数据分配器 路 路数据分配器

输 入 数 据 真值表

D

输 A1 0 0 1 1

入 A0 0 1 0 1 Y0 D 0 0 0

数据选择器与数据分配器

资料范本本资料为word版本,可以直接编辑和打印,感谢您的下载数据选择器与数据分配器地点:__________________时间:__________________说明:本资料适用于约定双方经过谈判,协商而共同承认,共同遵守的责任与义务,仅供参考,文档可直接下载或修改,不需要的部分可直接删除,使用时请详细阅读内容3.3 数据选择器与数据分配器本次重点内容:1、数据选择器的电路原理与功能。

2、用数据选择器实现函数。

3、数字分配器的电路和功能教学过程3.3.1 数据选择器在多路数据传输过程中,经常需要将其中一路信号挑选出来进行传输,这就需要用到数据选择器。

在数据选择器中,通常用地址输入信号来完成挑选数据的任务。

如一个4选1的数据选择器,应有两个地址输入端,它共有22=4种不同的组合,每一种组合可选择对应的一路输入数据输出。

同理,对一个8选1的数据选择器,应有3个地址输入端。

其余类推。

而多路数据分配器的功能正好和数据选择器的相反,它是根据地址码的不同,将一路数据分配到相应的一个输出端上输出。

根据地址码的要求,从多路输入信号中选择其中一路输出的电路,称为数据选择器。

其功能相当于一个受控波段开关。

多路输入信号:N个。

输出:1个。

地址码:n位。

应满足2n≥N。

(一)、4选1数据选择器1、逻辑电路:D3、D2、D1、D0为数据输入端,A1、A0为地址信号输入端,Y为数据输出端,为使能端,又称选通端,输入低电平有效。

2、真值表:4选取1数据选择器的真值表。

3.由真值表可写出输出逻辑函数式(二)8选1数据选择器MSI器件TTL 8:选1数据选择器CT74LS1511.逻辑功能示意图:D7、D6、D5、D4、D3、D2、D1、D0为数据输入端,A2、A1、A0为地址信号输入端。

Y和为互补输出端,为使能端,又称选通端,输入低电平有效。

2.数据选择器CT74LS151的真值表3.输出逻辑函数:(三)用数据选择器实现组合逻辑函数实现原理:数据选择器是一个逻辑函数的最小项输出器:而任何一个n位变量的逻辑函数都可变换为最小项之和的标准式,Ki的取值为0或1,所以,用数据选择器可很方便地实现逻辑函数。

数据选择和分配器

S1 — 数据输入(D)

Y 0 ~ Y 7 — 数据输出( D)

S2 、S3 — 使能控制端

S2 S3 0时, 实现数据分配器的功能 。

S3 — 数据输入(D) Y 0 ~ Y 7 — 数据输出( D) S1 、S2 — 使能控制端 S1 1 , S 2 0时 , 实现数据分配器的功能 。

四、用数据选择器实现组合逻辑函数

1ST = 1 时,禁止数据

0 0

00××× 00×××

0 1

0 1

1D0

选择器工作,输出 1Y = 0。

0 0

01×× 01××

0 1

× ×

0 1

1D1

1ST = 0 时,数据选择 器工作。输出哪一路数据 由地址码 A1 A0 决定。

0 1 0 × 0 × ×0 0 1 0 × 1 × × 1 1D2 0 1 1 0 × × ×0 0 1 1 1 × × × 1 1D3

数据输出

数据

输入 D

1 路-4 路 数据分配器

选择控制

A1 A0

真

A1 A0 Y0 Y1 Y2 Y3

0 0 D0 0 0

值 0 1 0 D0 0

表 1 0 0 0D 0

1 1 0 0 0D

Y0 D A1 A0

函

Y1 D A1 A0

数

Y2 D A1 A0 Y3 D A1 A0

式

Y0 Y1 Y2 Y3

1 C1

1 D2 D3

令 A1 = A, A0 = B 则 D0 = 0 D1 =D2 = C D3 = 1

(4)画连线图(略)

用数据选择器实现函数 Z m 3,4,5,6,7,8,9,10,12,14

[解] (1) n = k-1 = 4-1 = 3 用 8 选 1 数据选择器 74LS151

数字电子技术电路组合逻辑电路数据选择器、分配器

数据输出 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

S1 — 数据输入(D)

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

74LS138

A0 A1 A2 STB STC STA

S2 — 数据输入(D)

A0 A1 A2 地址码

S3 S2 S1

数据输入 (任选一路)

用 MSI 实现组合逻辑函数

3. 4. 1 用数据选择器实现组合逻辑函数 一、基本原理和步骤 1. 原理:选择器输出为标准与或式,含地址变量的

选择控制

1 路-4 路 数据分配器

A1

A0

Y0

函

Y1

数

Y2

式

Y3

Y0

Y1

Y2

Y3

&&&&

真

00

D0 0 0

值

表

01

0 D0 0

10

0 0Hale Waihona Puke 0110 0 0D

D

1

1

逻辑图

A1

A1

二、集成数据分配器 用 3 线-8 线译码器可实现 1 路-8 路数据分配器

二、集成数据分配器

用 3 线-8 线译码器可实现 1 路-8 路数据分配器

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

74LS138

A0 A1 A2 STB STC STA

A0 A1 A2

S3 S2 S1

…

任何一个函数都可以 写成最小项之和的形式

2. 基本步骤 (1) 选择集成二进制译码器 (2) 写函数的标准与非-与非式 (3) 确认变量和输入关系 (4) 画连线图 二、应用举例 [例] 用集成译码器实现函数 [解] (1) 三个输入变量,选 3 线 – 8 线译码器 74LS138

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

D7

禁止 Y2 使能 禁止

D7

74151 (4)

A2 A1 A0 EN

…D

74151 (3)

0

A2 A1 A0 EN

D7

…D

74151 (2)

0

A2 A1 A0 EN

74151 (1) … DA A A

0 2 1

0

EN

D31 …D24

S4 D23 …D16

16 15 14 13 12 11 10 9

74LS151

1 2 3 4 5 6 7 8

功 能 示 意 图பைடு நூலகம்

Y

D 07 0 1 2 3 4 5 6

17 Y D 0 1 2 3 4 5 6

禁止 MUX 使能

……

D7 D0 A2 A1 A0 S 1 ╳ ╳ 0 1 0 ╳ 1 1 0 0

D3 D2 D1 D0 Y Y S 地

S3 D15 …D8

S2 D7 … D0

S1

1 0

0 1

1/2 74LS139

0 1 S A4 A3 0 1 1 1 0 1 1 0

0 1

A2 A1 A0

07

四片 8 选 1(74151)

32 选 1 数据选择器

方法 1:真值表(使用 74LS139 双 2 线 - 4 线译码器)

A4 0 0 1 1

四路 8 位 并行数据

四片8选1 四路 1 位 串行数据 一片4选1

一路 1 位 串行数据

3. 4. 2 数据分配器 ( Data Demultiplexer ) 将 1 路输入数据,根据需要分别传送到 m 个输出端 一、1 路-4 路数据分配器

数据输出 数据 输入

D

1 路-4 路 数据分配器 A1 0 1 0 1 D 0 0 0 A0 0 D 0 0 0 0 D 0 0 0 0 D

Y 0 Y 1 当A S 1 时 ,选择器被禁止 A — 地址端 2 0 当S 0 时 ,选择器被选中(使能) D D — 数据输入端

7 0

S — 选通控制端

Y D A2数据输出端 A1 A0 D1 A2 A1 A0 D7 A2 A1 A0 Y 、 Y 0—

0 1 0 1

D0 D1 D2 D3

据

D3

据

A1

A0

0 1 0 1 选择控制信号

3. 函数式

Y D0 A1 A0 D1 A1 A0 D2 A1 A0 D3 A1 A0

一、4 选 1 数据选择器

3. 函数式

Y D0 A1 A0 D1 A1 A0 D2 A1 A0 D3 A1 A0

A3 译码器输出(1) (2) (3) (4) 输出信号 工 禁 禁 禁 D0 ~ D7 0 Y0 0 D8 ~ D15 禁 工 禁 禁 1 Y1 0 D16 ~ D23 禁 禁 工 禁 0 Y2 0 D24 ~ D31 1 Y3 0 禁 禁 禁 工

方法 2:74LS153 双 4 选 1 数据选择器(电路略)

地址码

S3 S2 S1

数据输入 (任选一路)

Y 0 ~ Y 7 — 数据输出(D ) S1 、 S 2 — 使能控制端

S1 1 , S 2 0 时 , 实现数据分配器的功能 。

3. 4 数据选择器和分配器

发送

并行传送 接收

数 据 传 输 方 式

0 1 1 0

0 1 1 0

0 1 1 0

在发送端和接收端不需要 0 串行传送 数据 并-串 或 串-并 转换装置, 1 但每位数据各占一条传输线,当 1 传送数据位数增多时,成本较高, 0 且很难实现。 串-并转换:数据分配器

并-串转换:数据选择器

m0 D0 m1 D1 m2 D2 m3 D3

4. 逻辑图

&

Y = D3 0 1 2

1 ≥1

0 A1 1 1 A0 0

1 1

D0 D1 D2 D3

二、集成数据选择器 1. 8 选 1 数据选择器 74151 74LS151 74251 74LS251

引 脚 排 列 图

VCC D4 D5 D6 D7 A0 A1 A2

数据输出

S1 — 数据输入(D)

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

Y 0 ~ Y 7 — 数据输出(D )

S2 、 S 3 — 使能控制端 S 2 S 3 0时 , 实现数据分配器的功能。

S2 — 数据输入(D)

74LS138

A0 A1 A2 STB STC STA A0 A1 A2

Y0 Y1 Y2 Y3

D A1 A0 D A1 A0 D A1 A0 D A1 A0

函 数 式 Y1 Y2

&

选择控制

Y0

&

Y3

&

真 值 表

A1 A0 Y0 Y1 Y2 Y3

0 0 1 1

&

D

1 1

逻辑图

A1

A1

二、集成数据分配器 用 3 线-8 线译码器可实现 1 路-8 路数据分配器

3. 4. 1 数据选择器 ( Data Selector )

能够从多路数据输入中选择一路作为输出的电路 一、4 选 1 数据选择器 1. 工作原理 输 D0 输 D3 2. 真值表 4选 1 0 出 1 2 Y 入 D1 D2 数 数据选择器 数 D A A Y

1 0

D0 D1 D2 D3

0 0 1 1

2. 集成数据选择器的扩展

D D80 D D15 7 D8 D15 Y2 0 Y 高位 使能 74151 (2) 禁止

D7 … D0 A2 A1 A0 EN … S D8 D15 1 D7 … …

Y

≥1

两片 8 选 1(74151) 16 选 1数据选择器

D7 Y1 D0 0 Y 使能 禁止 74151 (1) 低位

D0 A2 A1 A0 EN S

D7

D0

1 0

A3

A2

A1

A0

07

32 选 1 数据选择器 四片 8 选 1(74151) 方法 1: 74LS139 双 2 线 - 4 线译码器

Y

&

禁止 Y3 禁止 使能

D …D

7 0

0 D D D D D D D 16 8 0 24 15 7 23 31