Transparent resistive random access memory (T-RRAM) based on Gd2O3 film

阻变存储器概述

阻变存储器概述阻变存储器(Resistive Random Access Memory, RRAM)是一种基于非电荷存储机制的新型存储技术。

RRAM的上下电极之间是能够发生电阻转变的阻变层材料。

在外加偏压的作用下,器件的电阻会在高低阻态之间发生转换从而实现“0”和“1”的存储。

在二进制存储中,一般将低阻态代表“1”,高阻态代表“0”。

器件从高阻变化为低阻的过程称为Set,从低阻变为高阻的过程称为Reset。

Set过程中,一般需要限制通过器件的最大电流,以避免器件完全损坏。

虽然阻变存储器的研究自2000年后才兴起,但薄膜的阻变现象早在1967年就由英国Standard Telecommunication Laboratories的J. G. Simmons等人发现[1]。

1971年,美国加州大学伯克利分校的华裔教授Leon Chua就在理论上预言了除了电阻、电容、电感之外的第四种基本器件——忆阻器(Memristor)的存在[2]。

在2008年的Nature杂志上,惠普公司报道已成功制备出忆阻器原型器件并提出了相应的物理模型。

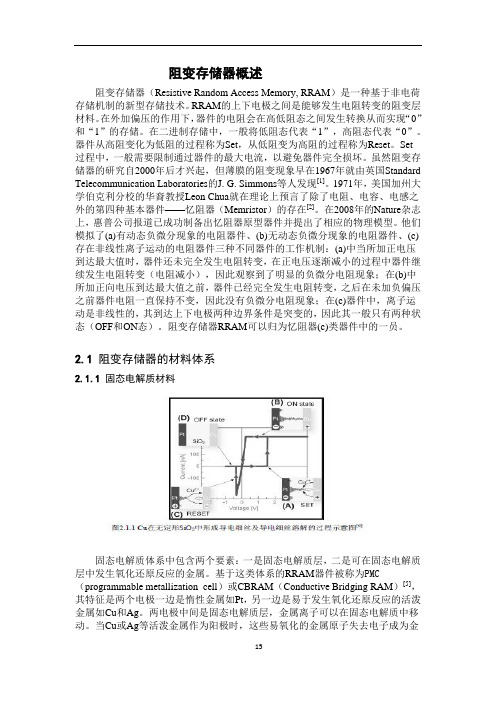

他们模拟了(a)有动态负微分现象的电阻器件、(b)无动态负微分现象的电阻器件、(c)存在非线性离子运动的电阻器件三种不同器件的工作机制:(a)中当所加正电压到达最大值时,器件还未完全发生电阻转变,在正电压逐渐减小的过程中器件继续发生电阻转变(电阻减小),因此观察到了明显的负微分电阻现象;在(b)中所加正向电压到达最大值之前,器件已经完全发生电阻转变,之后在未加负偏压之前器件电阻一直保持不变,因此没有负微分电阻现象;在(c)器件中,离子运动是非线性的,其到达上下电极两种边界条件是突变的,因此其一般只有两种状态(OFF和ON态)。

阻变存储器RRAM可以归为忆阻器(c)类器件中的一员。

2.1 阻变存储器的材料体系2.1.1 固态电解质材料固态电解质体系中包含两个要素:一是固态电解质层,二是可在固态电解质层中发生氧化还原反应的金属。

rram原理

RRAM基本原理RRAM(Resistive Random-Access Memory)是一种新型的非挥发性存储器技术,它具有高密度、低功耗和快速读写等优势,被视为下一代存储器的候选技术之一。

RRAM的工作原理基于一种称为电阻变化的效应,通过控制材料中的电阻状态来实现数据的存储和读取。

RRAM的结构RRAM的基本结构由两个电极和介质层组成,介质层中包含了具有电阻变化特性的材料。

其中,一个电极称为顶电极(top electrode),另一个电极称为底电极(bottom electrode)。

介质层通常是一种氧化物,如氧化铌(Nb2O5),氧化锆(ZrO2)或氧化钛(TiO2)等。

RRAM的工作原理RRAM的工作原理可以分为两个步骤:写入(programming)和读取(readout)。

写入(programming)在写入操作中,通过施加一个较高的电压,使得介质层中的电子受到电场的影响而迁移到顶电极,这样就改变了介质层的电阻状态。

具体来说,当施加一个较高的正电压时,电子会从底电极流向顶电极,形成一个导电通道,导致介质层的电阻减小,这种状态被称为“低电阻态”(LRS,Low Resistance State)。

相反,当施加一个较高的负电压时,电子会从顶电极流向底电极,导致导电通道断开,介质层的电阻增加,这种状态被称为“高电阻态”(HRS,High Resistance State)。

读取(readout)在读取操作中,通过施加一个较低的电压,测量介质层的电阻状态,以确定存储的数据。

具体来说,当施加一个较低的电压时,如果介质层处于LRS状态,电流会通过导电通道,导致读取电流较大;如果介质层处于HRS状态,导电通道断开,读取电流较小。

通过测量读取电流的大小,就可以确定介质层的电阻状态,进而读取存储的数据。

RRAM的工作机制RRAM的电阻变化效应可以归因于介质层中的离子迁移和电子迁移。

离子迁移在写入操作中,施加的电压会导致介质层中的离子发生迁移。

阻变式存储器存储机理

内注入大量电子 [ 11 ]. 同时体内一般要有以下两种状

况 [ 13 ] :材料中的陷阱是正电性的 (空态时呈正电性 ,

吸引一个电子时不带电 ) ,或者材料中存在大量的

施主或受主中心.

图 4 施主效应的 P - F效应 [ 8 ] ( Ed 为施主能级的深度 ,Δ< 为 势垒降 )

图 3 A l/A lq3 /A l/A lq3 /A l0 为真空介电常数 , K为相对

介电常数. 如果不考虑温度的影响 ,上式可定性看作

如下关系 :

ln ( I /V ) ~ V1 /2.

(2)

P - F效应是一种体效应 ,产生这种效应的前提

就是 :在界面处形成非阻挡接触 ,或者即使界面处是

阻挡接触 ,但是势垒很薄 ,可以通过隧穿的方式向体

应 ( electrode2lim ited)将阻变机理分成两大类 [8 ] ,其 穿的方式穿过局域态到达正电极 ,此时 SiO 薄膜处

中体效应是指发生在体内的电阻转变现象 ,相应的 于低阻态. 而在能带弯曲的 Ⅰ区 ,由于陷阱能级的差

机理包含 S - V ( Simmons - Verderber) 理论 , P - F 异 ,导致了隧穿难度的加大 ,因此有少量电子驻留在

阻变式存储器的读写机制是 : 采用简单的结

构 ,如 1D 1R (一只二极管和一个阻变器 )或 1 T1R (一只晶体管和一个阻变器 ) ,如图 1 所示 ,利用高

2. 1 体效应 ( bulk2lim ited) 2. 1. 1 S - V 理论

电压改变材料的阻值的大小 ,即擦 /写要存储的信 息 ,然后用一个适当的小电压读取存储的信息.

2. 1. 2 P - F效应

P - F效应或者称为场助热电离效应 ( field2as2

交叉杆结构忆阻器件的研究进展

交叉杆结构忆阻器件的研究进展敬秦媛;程海峰;刘东青;张朝阳【摘要】忆阻器被认为是除电容器、电感器、电阻器之外的第四种无源器件,具有器件结构简单、操作速度快、功耗小等优点,是具有电阻记忆特性的非易失性的电阻元件.而交叉杆结构忆阻器件作为忆阻器的一种结构,由于其较之其他结构的忆阻器具有结构简单、集成度高、容错性和并行性优良等特性,受到了外界广泛的关注及研究.文章综述了近年来交叉杆忆阻器的兴起和发展现状,阐述了以交叉杆结构为基础的各类忆阻器的制备及应用.%Memristor is considered to be a fourth passive device other than capacitors,inductors and resistors.It has the advantages of simple device structure,fast operation speed and low power consumption.It is nonvolatile with resistive memory characteristic of the original resistance.The cross-bar structure as a memristor,because of its simple structure,high integration level,high error tolerance and excellent parallel characteristics,receives the outside world wide attention and research.In this paper,the rise and development of the cross-bar resistive switching memory devices in recent years is reviewed,and the preparation and application of various memristors based on cross-bar structure is described.【期刊名称】《电子元件与材料》【年(卷),期】2017(036)006【总页数】6页(P8-13)【关键词】交叉杆;忆阻器;综述;记忆;柔性;并行性【作者】敬秦媛;程海峰;刘东青;张朝阳【作者单位】国防科技大学新型陶瓷纤维及其复合材料重点实验室,湖南长沙410073;国防科技大学新型陶瓷纤维及其复合材料重点实验室,湖南长沙410073;国防科技大学新型陶瓷纤维及其复合材料重点实验室,湖南长沙410073;国防科技大学新型陶瓷纤维及其复合材料重点实验室,湖南长沙410073【正文语种】中文【中图分类】TN602忆阻器是一个有关磁通和电荷的非线性双终端的无源电子器件。

26个盖亚记忆体介绍大全

26个盖亚记忆体介绍大全盖亚记忆体是一种先进的记忆体技术,具有高速、高密度、低功耗等优点,被广泛应用于计算机、智能手机、平板电脑等电子产品中。

在下面,我将为您介绍26种不同类型的盖亚记忆体,希望能帮助您更全面地了解这一领域。

1. DRAM(Dynamic Random Access Memory):动态随机存取存储器,是一种常见的盖亚记忆体,用于临时存储数据和程序。

2. SRAM(Static Random Access Memory):静态随机存取存储器,速度快、功耗低,常用于高性能的计算机系统中。

3. SDRAM(Synchronous Dynamic Random Access Memory):同步动态随机存取存储器,具有高速度和高带宽,被广泛用于个人电脑和服务器中。

4. DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory):双倍数据速率同步动态随机存取存储器,是一种速度更快的内存类型,用于提高数据传输效率。

5. DDR2 SDRAM:双倍数据速率2同步动态随机存取存储器,相比DDR SDRAM有更高的频率和更大的带宽。

6. DDR3 SDRAM:双倍数据速率3同步动态随机存取存储器,继续提高数据传输速度和功耗效率。

7. DDR4 SDRAM:双倍数据速率4同步动态随机存取存储器,采用更先进的技术,具有更高的频率和更低的功耗。

8. DDR5 SDRAM:双倍数据速率5同步动态随机存取存储器,是目前最新一代的内存标准,具有更高的带宽和更低的延迟。

9. LPDDR(Low Power Double Data Rate):低功耗双倍数据速率存储器,用于移动设备和嵌入式系统,具有低功耗和高性能的特点。

10. MRAM(Magnetoresistive Random Access Memory):磁电阻随机存取存储器,采用磁性存储单元,具有非常快的读写速度和较长的数据保存时间。

计算机英语缩写表计算机英语缩写查询表

缩写意义与完整形式单元10b11b 11b 11b 11b 6b 3D3G 三维(Three Dimensional)第3代(Third-Generation)3GPP 4G 第三代合作伙伴计划(3rd Generation Partnership Project) 第4代(Fourth-Generation) 5G 第5代(Fifth-Generation)ACID ACLs ADT AGI 原子性,一致性,隔离,耐久性(Atomicity,Consistency,Isolation,Durability )访问控制列表(Access Control Lists )11a 4b 抽象数据类型(abstract data type )通用人工智能(Artificial General Intelligence)异步JavaScript 与可扩展标记语言(Asynchronous JavaScript and XML) 算术逻辑单元;运算器(Arithmetic and Logic Unit )弱人工智能(Artificial Narrow Intelligence) 13a 12a 1a AJAX ALU ANI 13a 13b 4b ANNs API 人工神经网络(Artificial Neural Networks)应用编程接口(Application Programming Interface )增强现实(Augmented Reality)AR 10b 8aARPA ARPANET ASCIIASI (美国国防部)高级研究计划署(Advanced Research Projects Agency )阿帕网,美国国防部高级研究计划署计算机网(Advanced Research Projects Agency Network )8a 美国信息交换标准码(American Standard Code for Information Interchange )超人工智能(Artificial Super Intelligence) 自动语音识别(Automatic Speech Recognition) 边界网关协议(Border Gateway Protocol )基本输入输出系统(Basic Input Output System )位图文件(BitMap Picture )10a13a 13b 9a ASR BGP BIOS BMP CAN CD 1a 10a 8a 园区网(Campus Area Network )光盘(Compact Disc )3a CERN CPU 欧洲粒子物理研究所(European Laboratory for Particle Physics )中央处理器(Central Processing Unit )9b 1a dApps DBMS DNA DoS 分布式应用程序(distributed applications )数据库管理系统(database management system )脱氧核糖核酸(deoxyribonucleic acid) 14b 6a 15b 11a 1b 拒绝访问(Denial of Service )DRAM DSL 动态随机存储器(Dynamic Random Access Memory )数字用户线(Digital Subscriber Line )8a EEPROM电可擦除只读存储器(Electrically Erasable Programmable Read Only Memory )1bEGP EMI EPROMER 外部网关协议(Exterior Gateway Protocol )9a 电磁干扰(Electromagnetic Interference )可擦可编程只读存储器(Erasable Programmable Read Only Memory )实体—关系(Entity Relationship )1b 1b2b 13b 4b 9a FAQs FIFO FTP 常见问题(Frequently Asked Questions) 先进先出(First In First Out )文件传输协议(File Transfer Protocol )GB 吉字节(GigaByte )1b 11b 11b 13a 1b 10b 7a Gbps Ghz 每秒千兆位(gigabits per second) 千兆赫(Gigahertz)GPS HDD HDMI HTML HTTP ICMP ID 全球定位系统(Global Position System) 硬盘驱动器(Hard Disk Drive )高清多媒体接口(High Definition Multimedia Interface) 超文本链接标示语言(HyperText Markup Language )超文本传输协议(HyperText Transfer Protocol )网间控制报文协议(Internet Control Messages Protocol )身份(Identification,Identity )9a 8a 4a IDE 集成驱动器电子电路(Integrated Drive Electronics )集成开发环境(Integrated Development Environment )国际电工技术委员会(International Electrotechnical Commission )(美国)电气电子工程师学会(Institute for Electrical and Electronic Engineers )因特网工程任务组(Internet Engineering Task Force )内部网关协议(Interior Gateway Protocol )物联网(Internet of Things)1b 2a IDE IEC 8b8a IEEE IETF IGP 9b 9a IoT 15a 9a IRC 因特网在线聊天系统(Internet Relay Chat )索引顺序存取法(Index Sequence Access Method )国际标准化组织(International Organization for Standardization )因特网服务提供商(Internet Service Provider )信息技术(Information Technology)ISAM ISO 6b 8b 8a ISP IT 15a 6b 9b 8a JDBC JIT 联合式数据库互接(Join Database Connectivity )即时编译技术,运行时编译执行的技术(Just-In-Time )局域网,本地网(Local Area Network )LAN LIFO LTE 后进先出(Last In First Out )4b 11b 8a 长期演进技术(Long-Term Evolution) MAC MAN媒体访问控制(Media Access Control )城域网(Metropolitan Area Network )8aMbps MDA MHz MIMD MIME MIMO MIT 每秒兆位(Megabits per second)11b2b11b1a 模型驱动体系(Model Driven Architecture)兆赫(Megahertz)多指令多数据(Multiple Instruction Multiple Data)多用途互联网邮件扩展(Multipurpose Internet Mail Extensions)多输入多输出(Multiple Input,Multiple Output)(美国)麻省理工学院(Massachusetts Institute of Technology)磁阻抗随机存储器(Magnetoresistive Random Access Memory)网卡(Network Interface Card)5b11b9b1b8aMRAM NICNLP自然语言处理(Natural Language Processing)纳米(Nanometer)13b 1b 5b 6b 11b 2b 7anmNOP无操作(NoOperation)ODBC OFDM OOAD OOP 开放式数据库互接(Open Database Connectivity)正交频分复用(Orthogonal Frequency-Division Multiplexing)面向对象分析与设计(Object Oriented Analysis and Design)面向对象编程(Object Oriented Programming)操作系统(Operating System)OS3aOSI开放式系统互连(Open System Interconnect)个人网络(Personal Area Network)8aPAN8aPCA主成分分析(Principal Component Analysis)外部设备扩展接口(Peripheral Component Interconnect)周边元件扩展接口(Peripheral Component interconnect)个人计算机存储卡国际协会(Personal Computer Memory Card International Association)个人数字助理(Personal Digital Assistant)超级文本预处理语言(Hypertext Preprocessor)点对点协议(Point-To-Point Protocol)13b 1b 8b 8b 3aPCIPCIPCMCIAPDAPHP2b9a PPPPROM RAM RDBMS REPL RF 可编程序的只读存储器(Programmable Read Only Memory)随机存取存储器(Random Access Memory)关系数据库管理系统(Relational DBMS)读取—求值—输出循环(read–eval–print loop)无线电频率(Radio Frequency)1b1a6b5b11b8b1aRF射频,无线电频率(Radio Frequency)ROM RTC 只读存储器(Read-Only Memory)实时通信技术(Real-Time Communication)串行高级技术附件(Serial Advanced Technology Attachment)11b1b7bSATASDLC软件开发生命周期(Software Development Life Cycle)SGML SIMD SLIPSMTP SQL 标准通用标记语言(Standard Generalized Markup Language )单指令多数据(Single Instruction Multiple Data )串行线路接口协议(Serial Line Internet Protocol )简单邮件传输协议(Simple Mail Transfer Protocol )结构化查询语言(Structured Query Language )静态随机存储器(Static Random Access Memory )固态驱动器(Solid State Drive )9b 1a 9a9a 6a SRAM SSD 1b 1b 7b 13b 13b 8a SSL 安全套接字协议(Secure Sockets Layer ) 奇异值分解(Singular Value Decomposition) 支持向量机(Support Vector Machine) SVD SVM TCP 传输控制协议(Transfer Control Protocol )用户数据报协议(User Datagram Protocol )统一建模语言(Unified Modeling Language )统一资源标识符(Uniform Resource Identifier )统一资源定位符(Uniform Resource Locator )通用串行总线(Universal Serial Bus )UDP UML URI 9a 2b 9a URL USB 9a 8a VGA VR 视频图形阵列(Video Graphics Arrays )虚拟现实(Virtual Reality)10a 10b 9b 8a W3C WANWLAN WWW万维网协会(World Wide Web Consortium )广域网(Wide Area Network )无线局域网(Wireless Local Area Network )万维网(World Wide Web )8b 8a。

DRAM的发展

DRAM的发展1. 简介动态随机存取存储器(Dynamic Random Access Memory,简称DRAM)是一种常见的计算机内存技术,用于存储数据和指令。

它的发展至关重要,因为它直接影响着计算机的性能和速度。

本文将详细介绍DRAM的发展历程、技术特点和未来发展趋势。

2. 发展历程DRAM的发展可以追溯到上世纪60年代。

早期的DRAM采用了基于电容的存储单元,每个存储单元由一个电容和一个开关构成。

然而,由于电容会逐渐失去电荷,需要不断刷新,这导致了存储器的速度较慢。

随着技术的进步,DRAM逐渐演变为现代的存储器技术。

3. 技术特点(1)存储单元:现代DRAM的存储单元通常由一个电容和一个晶体管构成。

电容用于存储数据位,而晶体管则用于读取和写入数据。

这种结构使得DRAM具有高集成度和较低的成本。

(2)刷新机制:DRAM的存储单元需要定期刷新以保持数据的稳定性。

刷新操作会占用一定的时间,这会降低DRAM的响应速度。

为了解决这个问题,出现了自刷新技术,可以在不干扰其他操作的情况下刷新存储单元。

(3)存储密度:DRAM具有较高的存储密度,可以在较小的面积内存储更多的数据。

这使得DRAM成为计算机内存的首选技术之一。

(4)读写速度:DRAM的读写速度较快,可以满足计算机对大量数据的快速访问需求。

然而,由于存储单元需要刷新,DRAM的访问速度仍然比不上静态随机存取存储器(SRAM)。

4. 未来发展趋势(1)高带宽需求:随着计算机应用的不断发展,对内存带宽的需求也越来越高。

为了满足这一需求,DRAM的发展方向之一是提高数据传输速率和带宽。

(2)低功耗设计:随着移动设备的普及,低功耗成为了DRAM发展的重要方向。

研究人员正在开发新的DRAM技术,以降低功耗并延长电池寿命。

(3)新型存储技术:除了传统的DRAM技术,研究人员还在探索新型存储技术,如相变存储器(Phase Change Memory,PCM)和阻变存储器(Resistive Random Access Memory,ReRAM)。

存储器概述

存储器概述1.1 引言存储器是一种用于存储数据的记忆器件,被广泛地应用于数码产品、电脑、移动通信等各种领域,其最基本的结构是存储二进制信息“0”和“1”的存储单元。

根据掉电后存储数据能否继续保持,半导体存储器又可以分为挥发性存储器和非挥发性存储器两大类。

目前的挥发性存储器市场,以动态随机存储器(Dynamic Random Access Memory,简称DRAM)和静态随机存储器(Static Random Access Memory,简称SRAM)为代表。

DRAM是通过对电容的充、放电来实现数据的擦写,其最典型的应用在各种内存芯片上,主要应用于PC、手机、电视、GPS等领域。

由于其存储单元为1T1C结构,所以DRAM易于实现高密度存储。

但是,由于在数据写入电容后存在电荷泄露,DRAM需要通过不断刷新才能保持数据,因此其功耗比较大。

相对DRAM而言,SRAM具有存取速度快的优势,因此SRAM主要应用在高速低功耗场合,如移动通信网络、手机、计算机缓存等等。

但是SRAM的存储单元为6T结构,所占单元面积较大,因此其存储密度比较低。

随着便携式电子设备的不断普及,非挥发存储器在整个存储器市场上的份额也越来越大。

据统计,2005年人均拥有的存储容量为10G,而在不久的将来这个数字将达到400G。

自上世纪90年代以来,市场上主流的非挥发存储器技术是基于电荷存储机制的“闪存”(Flash)存储器件。

Flash是基于1967年Bell实验室的S. M. Sze和D. Kahng提出的浮栅结构非挥发性存储器发展而来的[1],如图1.1.1(a) 所示,其基本结构包括衬底、隧穿氧化层、浮栅、控制氧化层和控制栅极。

浮栅型Flash存储的存储机理如图1.1.1(b)所示,在外界适当电激励情形下,电子可以被注入和释放出浮栅存储层,从而实现数据的擦写。

当电子被注入到浮栅中并被浮栅俘获时,器件的阈值电压会增大;而当电子被从浮栅上释放出来时,器件的阈值电压会减小。

晶圆基底芯片 逻辑 存储

晶圆基底芯片逻辑存储1.引言1.1 概述概述晶圆基底芯片、逻辑芯片和存储芯片是现代电子产品中不可或缺的核心组件。

它们作为集成电路的重要组成部分,承载着不同的功能和任务。

晶圆基底芯片是一种用于制造集成电路的基础材料。

它通常采用硅晶圆作为基板,通过一系列的工艺步骤,在其表面上制造各种不同的电子元件。

晶圆基底芯片在整个电子行业中具有举足轻重的地位,因为几乎所有的电子产品都离不开它们。

逻辑芯片是一种能够通过逻辑操作进行数据处理和计算的集成电路。

它由大量的逻辑门电路组成,通过连接和控制这些逻辑门,实现对数据的存储、处理和传输。

逻辑芯片的功能多样,可以用于实现不同的电子设备,如计算机、手机、智能家居等。

存储芯片是一种用于数据存储和读取的集成电路。

它可以记录和保存各种类型的数据,如文档、照片、视频等。

存储芯片的技术不断进步,从最早的EPROM、FLASH,到如今的SSD、SD卡等,存储容量和读写速度大大提高,满足了人们对数据存储的日益增长的需求。

本文将从定义、特点、应用领域、功能和发展趋势等多个方面,详细介绍晶圆基底芯片、逻辑芯片和存储芯片的相关知识。

通过对这些核心组件的了解,读者将更好地理解和认识现代电子产品的内部工作原理,以及背后的科技发展趋势。

1.2文章结构文章结构:本文共分为引言、正文和结论三个部分。

具体结构如下:1. 引言部分(Introduction)1.1 概述(Overview)在本部分中,将介绍晶圆基底芯片、逻辑芯片和存储芯片的概念,并简要说明它们在现代科技领域的重要性。

1.2 文章结构(Article Structure)本文将按照以下结构展开讨论晶圆基底芯片、逻辑芯片和存储芯片的相关内容。

1.3 目的(Purpose)在本部分中,将明确本文的目的和意义,以及阐述对晶圆基底芯片、逻辑芯片和存储芯片发展的展望。

2. 正文部分(Main Body)2.1 晶圆基底芯片(Wafer Substrate Chips)2.1.1 定义和特点(Definition and Characteristics)在本部分中,将详细解释晶圆基底芯片的定义和特点,包括其在集成电路制造中的作用和重要性。

新型高密度1S1R结构阻变存储器件概述

新型高密度1S1R 结构阻变存储器件概述随着现代半导体工艺的技术进步,Flash 存储器开始遇到技术瓶颈,新型 存储器应运而生。

与其他儿种新型的非易失性存储器相比,阻变存储器(RRAM 或ReRAM )因其具有结构简单、访问速度快等优势,成为下一代非易失性存储 器的有力竞争者之一。

基于阻变存储器的交义阵列是阻变存储器实现高密度存储最简单、最有效的 方法。

而仅山阻变存储单元构成的交义阵列山于漏电通道而存在误读现象。

为了 解决误读现象,通常需要在每个存储单元上串联一个选择器构成1S1R 结构。

对 山阻变存储单元和选择器构成的1S1R 结构的研究进展进行综述分析是一项有意 义的工作,因此本论文主要对1S1R 结构的阻变存储器件的研究进展进行概述。

关键词:阻变存储器,交义阵列,选择器,1S1R错误!未定义书签。

错误!未定义书签。

第一章绪论 (1)1.1阻变存储器 (1)1. 1. 1 RRAM 基本结构 ........................................... 1 1. 1.2 RRAM 技术回顾 ............................................ 1 1.2交叉阵列汇中的串扰问题 .......................................... 3 1.3本论文的研究意义及内容 (3)1. 3. 1研究意义 (3)中文摘要.... 英文摘要1.3.2研究内容 (3)第二章RRAM的集成选择器的集成方式 (5)2.1有源阵列 (5)2.2无源阵列 (5)第三章RRAM的集成选择器的类型 (6)3. 1 1T1R (6)3.2 1D1R (6)3.3 1S1R (8)3. 4back to back 结构 (10)3.5具有自整流特性的1R结构 (11)第四章1S1R结构阻变存储器件研究进展 (13)第五章总结与展望 (14)5. 1论文总结 (14)5.2未来工作展望 (14)第一章绪论1.1阻变存储器1. 1. 1 RRAM基本结构阻变存储器(Resistive Random Access Memoiy, RRAM)和相变存储器的原理有点相似,在电激励条件下,利用薄膜材料,薄膜电阻在高阻态和低阻态间相互转换,这样子就能实现数据存储["I。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Transparent resistive random access memory (T-RRAM) based on Gd 2O 3 film and its resistiveswitching characteristicsKou-Chen Liu 1,*, Wen-Hsien Tzeng 2, Kow-Ming Chang 2, Yi-Chun Chan 1, Chun-Chih Kuo 1, and Chun-Wen Cheng 11Institute of Electro-Optical Engineering, Chang Gung University, Tao-Yuan, 33302, Taiwan, R.O.C 2Institute of Electronics, Department of Electronics Engineering, National Chiao Tung University, HsinChu, 30010, Taiwan,R.O.CAbstract- A transparent resistive random access memory (T-RRAM) based on ITO/Gd 2O 3/ITO capacitor structure is successful y fabricated on Gl ass substrate by pul se l aser deposition (PLD) at room temperature. Under bipo l ar operation, the ITO/Gd 2O 3/ITO device exhibits reliable and stab le resistive switching behaviors for more than 200 switching cyc es and ow operation vo tage of -2V/+2V. Furthermore, our device demonstrates nonpol ar resistive switching characteristic which exhibits high potential to be applied for the next generation nonvolatile memory.I. I NTRODUCTIONResistive random access memory (RRAM) attracts muchattention in recent years owning to advantag es of simple structure, hig h density, low power consumption, etc. Many transition metal oxide (TMO) were proposed to demonstrate the resistive switching (RS) behavior, such as NiO[1], TiO 2[2], and Cu 2O[3], however, the switching mechanism of RRAM is still on debate. TMO material exhibits excellent merits of simple composition and high functionality and compatibility to integ rate with CMOS technolog y, even TMO film integ rated with transparent conducting oxide (TCO) has reported several months ag o. It’s called T-RRAM which shows not only RS behavior but also highly transparency to UV light proposed by Park et al.[4] at the first time. Furthermore, by integrating with transparent electronic components, a total see-throu g hembedded electronic device could put into realization.However, since the switching mechanism of the RS behavior is still needed further investig ation, it’s essential to discuss on other TMO material to have a better understanding for the sake of stable RS of T-RRAM. In this study, we investig ated the resistive switching characteristics of T-RRAM based on ITO/Gd 2O 3/ITO capacitor structure. After forming process, both unipolar and bipolar RS behavior could be observed on our T-RRAM device. Bipolar RS properties show more reliable and stable switchin characteristics of RRAM behavior. Endurance, retention, *Contacting Author: Kou-Chen Liu is with Institute of Electro-Optical Engineering, Chang Gung University, Tao-Yuan, 33302, Taiwan, R.O.C (phone:+886-3-2118800; fax: +886-3-2118507; email:jacobliu@.tw ) fabrication process condition of Gd 2O 3 film and electrical conduction behavior of fresh, HRS and LRS are also discussed here.II. E XPERIMENTSGlass substrate was prepared and used in this experiments. Before the main structure deposition, the g lass surface is cleaned by DI water, and then followed acetone solution for 10 min. Then, ITO bottom electrode was deposited by dc sputterin system. 10 min pre-sputterin under workin pressure of 30 mTorr is experimented and then ITO film with thickness of 1000A was deposited in Ar gas of 15 sccm. Metal oxide Gd2O3 was deposited by pulse laser deposition (PLD) at 25ć under oxyg en partial pressure of 10 mTorr for 10 min. This room temperature (RT) fabrication process provides advantag es such as low thermal budg et and easy compatible with back-end fabrication process. Then top electrode ITO with the same process condition of bottom electrode was deposited by dc sputtering system with a shadow mask. Electrical characteristics was measured by HP 4156C under different measurement temperature from 25ć to 85ć. Current flow from top side electrode ITO to bottom side ITO was defined as positive sweep.III. R ESULTS AND DISCUSSION The typical unipolar and bipolar RS characteristics of our ITO/Gd 2O 3/ITO capacitor structure in dc sweep mode are shown in Fig. 1 and Fig. 2, respectively. Forming process was needed in the beginning for all our samples to activate our T-RRAM device with certain current compliance of 1 mA. Both unipolar and bipolar RS characteristics could be observed in our samples irrespectively of the operation polarity, i.e. nonpolar RS properties. Though unipolar RS behavior is more applicable for integ rated current desig n to have smaller cell size and hi her device density, however, the electricalcharacteristics of unipolar RS is less stable than bipolar RS in this samples. Only 15 times of switching cycles with unstable RS characteristic and larg e voltag e dispersion is observed shown in Fig. 1. Bipolar switching characteristics of our T-RRAM device switches to ON (OFF) state by neg ative (positive) bias is shown in Fig. 2. Excellent and reliable RS978-1-4244-3544-9/10/$25.00 ©2010 IEEEcharacteristic of more than 200 switching cycles are observed. Low operation voltage of only -2V/+2V is needed to operate our T-RRAM device. During a continuously automatic dc sweeping bias, our device could switch to ON or OFF state with low voltag e dispersion among the 200 switching cycles shown in Fig. 3. A larg e voltag e operation window of 1V is observed and there is no voltag e overlap in our T-RRAM device. Endurance of our device is shown in Fig. 4. Among the 200 switching cycles, there has a large high to low resistance ratio of about 5. The negative operated dc sweep on HRS curve was translated to positive side on both voltag e and current values, and then the electrical conduction behavior of HRS and LRS are fitted and shown in Fig. 5. The conduction mechanismin the LRS is dominated by Ohmic conduction with a slope of approximately 1. The conduction behavior in the HRS is Ohmic conduction at low voltag e (I͉V), and space-charg e limited current (SCLC) (I͉V2) at high voltage. A transparent T-RRAM based on ITO/Gd2O3/ITO structure was fabricated and investigated here. Excellent and reliable bipolar switching characteristics with low operation voltag e of -2V/+2V, no voltag e overlap, and more than 200 switching cycles are observed. Furthermore, our T-RRAM demonstrates nonpolar switching behavior which exhibits high potential to be applied for next generation nonvolatile memory.R EFERENCES[1] I.G. Baek, M.S. Lee, S. Seo, M.J. Lee, D.H. Seo, D.–S. Suh, J.C. Park,S.O. Park, H.S. Kim, I.K. Yoo, U.-In. Chung, J.T. Moon, “Hig hly Scalable Non-volatile Resistive Memory using Simple Binary Oxide Driven by Asymmetric Unipolar Voltag e Pulses,” IEDM Tech. Dig.(2004) pp.587[2] B.J. Choi, D.S. Jeong, S.K. Kim, C. Rohde, S. Choi, J.H. Oh, H.J. Kim,C.S. Hwang, K.Szot, R. Waser, B. Reicheng erg, S. Tiedke, “Resistiveswitchin mechanism of TiO2 thin films rown by atomic-layer deposition,” J. Appl. Phys. 98 (2005) 033715[3] A. Chen, S. Haddad, Y.-C. Wu, T.-N. Fang, Z. Lan, S. Avanzino, S.Pang rle, M. Buynoski, M. Rathor, W. Cai, N. Tripsas, C. Bill, M.VanBuskirk, and M. Tag uchi, “Non-Volatile Resistive Switching for Advanced Memory Applications,” IEDM Tech. Dig. (2005) pp.746[4] J.W. Seo, J.-W. Park, K.S. Lim, J.-H. Yang, and S.J. and Kang,“Transparent resistive random access memory and its characteristics for nonvolatile resistive switching,” Appl. Phys. Lett, 93, 223505 (2008)Fig. 1. The typical unipolar resistive switching characteristicsFig. 2. The typical bipolar resistive switching characteristics of Fig. 3. Operation voltag e distribution of the ITO/ Gd O/ITO Fig. 4. The resistance values of HRS and LRS versus the number Fig. 5. The conduction behavior of LRS is mainly dominated by。