清华大学微电子所-陈弘毅教授PPT(1-7章)_部分2

数电课件 第一章_清华

又如:(209.04)10= 2×102 +0×101+9×100+0×10-1+4 ×10-2

2、二进制 数码为:0、1;基数是2。 运算规律:逢二进一,即:1+1=10。 二进制数的权展开式: 如:(101.01)2= 1×22 +0×21+1×20+0×2-1+1 ×2 -2 =(5.25) 10

序

课程介绍 1. 课程的性质

言

2. 教学目标 3. 课程研究内容 4. 课程特点与学习方法 5. 教材和参考书 6. 对大家共同的要求

1.课程性质

《数字电子技术基础》课程是电子、电气、信息、计

算机、自动化类专业具入门性质的重要专业基础课。

2.教学目标

获得适应信息时代的数字电子技术方面的基本理论、

基本知识和基本技能。培养分析和解决实际问题的能力,

(4)片上系统(SoC):有些PLD集成度很高,足 以满足设计一般数字系统的需要,这样就可以由 设计人员自行编程将一个数字系统集成在一片 PLD上,做成“片上系统”,而不必去请厂家做 专用集成电路了。 (5)可编程片上系统(SoPC):是可编程的片上 系统。用可编程逻辑技术把整个系统放到一块芯 片上,具有灵活的设计方法,可裁剪、可扩充、 可升级,并具备软硬件在系统可编程的功能。 (6)在系统可编程器件(isp):编程不需要专门 的编程器,在计算机上就可以完成。

• 摩尔定律 :1965年时任仙童公司电子工程师 的戈顿· 摩尔在应邀为《电子学》杂志35周年 专刊写的文章中指出,芯片中的晶体管和电 阻器的数量每年会翻番。1968年与他人共同 创办了大名鼎鼎的芯片制造厂商Intel公司任 副总裁 。 1975年,摩尔在给IEEE学术年会 的论文中修正了摩尔定律,他认为,每隔24 个月,晶体管的数量将翻番。现在大家普遍 认同的是“集成电路芯片上所集成的电路的 数目,每隔18个月就翻一番”。

微电子学概论 ppt课件

自1968年开始,硅技术为代表的信息技术领域的学术 论文超过了以钢铁技术为代表的机械领域的学术论文

PPT课件

PPT课件

PPT课件

11个国家集成电路人才 培养基地

一. 微电子技术与半导体集成电路

微电子学- 信息科学的基础 研究在固体(半导体)材料上构成的微小型化电路、子系统及系统 的电子学分支,研究芯片级微电路系统的科学。研究电子或离子在 固体材料中的运动规律及其应用,并实现信号处理。

PPT课件

课程内容及学时安排 2学分 32学时

第一章 概论 (多媒体)

3 学时

第二章 集成器件物理基础(部分多媒体)

12学时

第三章 集成电路制造工艺 (多媒体)

7 学时

第四章 集成电路设计(多媒体)

4 学时

第五章 微电子系统设计 (多媒体)

2 学时

第六章 集成电路C A D技术(计算机辅助设计) 4 学时

PPT课件

除了自身对国民经济的巨大贡献之外

PPT课件

采用交流传动改造后,电力机车可节电20%-30% 内燃机车可节油12%-14%

全国一半以上中等城市的自来水公司,在管网自动 检测和生产调度中使用计算机控制,可使自来水流 失率降低50%

PPT课件

PPT课件

PPT课件

人类社会的材料(主要) 宽禁带半导体材料(GaAs)

微电子学概论

PPT课件

教学目的

了解微电子学发展历史及在科学技术、国民经济、国家安全

的重要战略作用。

对微电子技术发展过程中的一些基本规律、发展前景的展望

和进行预测;对充分反映微电子技术领域的最新成果、体现前 沿性和时代性等进行了解。

在半导体物理基础上,对半导体器件基础、大规模集成电路

清华大学电工技术电子技术1PPT课件

i

u R =ui

阻

const

伏电-工安电子技特术 性

2.电感 L:单位电流产生的磁链

(单位:H, mH, H)

i u

磁通

L = N

i

线圈 匝数

04.12.2020

电工电子技术

电感中电流、电压的关系

+

u

i

–

e=Nd=Ldi

dt dt

e+

–

L = N

u = e = L di dt

i

当 i = I (直流) 时, di = 0

若 P 0 输出功率(起电源作用)

电源的功率可能为正(吸收功率) ,也可能为负(输出功率)

04.12.2020

电工电子技术

电源的功率

aI

+

U

b

-

P = UI

电压电流正方向一致

aI

+

U

b

-

P = –UI

电压电流正方向不一致

04.12.2020

电工电子技术

含源网络的功率

I

+

U

-

含源 网络

P = UI

04.12.2020

电工电子技术

规定正方向的情况下欧姆定律的写法

I

a

I与U的方向一致

U

R

b

U = IR

I

a

U b

04.12.2020

I与U的方向相反

R

U = – IR

电工电子技术

规定正方向的情况下电功率的写法

功率的概念:设电路任意两点间的电压为 U ,流入此

部分电路的电流为 I, 则这部分电路消耗的功率为:

【课件】Verilog教程清华微电所精编版

VERILOG HDL的设计流程

自顶向下(Top-Down)设计 一个系统由总设计师先进行系统描述

(Spec),将系统划分为若干模块,编写 模块模型(一般为行为级),仿真验证后, 再把这些模块分配给下一层的设计师, 由他们完成模块的具体设计,而总设计 师负责各模块的接口定义

VERILOG教程(1)

清华大学微电子学研究所 2003年9月

提纲

Verilog概述 Verilog程序的基本结构 Verilog上机环境及工具

Verilog概述 Verilog程序的基本结构 Verilog上机环境及工具

VERILOG概述

什么是Verilog HDL? Verilog HDL(Hardware Discription Language)是一种硬件描述语言,用于从 算法级、门级到开关级的多种抽象设计 层次的数字系统建模。

VERILOG HDL与 C语言

虽然Verilog的某些语法与C语言接近,但存在 本质上的区别

Verilog是一种硬件语言,最终是为了产生实际的硬 件电路或对硬件电路进行仿真

C语言是一种软件语言,是控制硬件来实现某些功 能

利用Verilog编程时,要时刻记得Verilog是硬件语 言,要时刻将Verilog与硬件电路对应起来

数据流方式 行为方式 结构方式 上述方式的混合

模块

简单的例子(数据流方式) module HalfAdder(A, B, Sum, Carry);

input A, B; output Sum, Carry;

assign #2 Sum=A^B; assign #5 Carry=A&B; endmodule

清华大学VLSI7.ppt

2020/11/2

18

§4 现场可编程门阵列(FPGA)

现场可编程门阵列(Field Programmable Gate Array)是一种可编程器件,它是近 几年迅速发展起来的,用于ASIC设计的 一种新方法。FPGA提供了用户可编程 和自己制造的能力,极大地缩短了设计 和制造时间。

2020/11/2

14

• 标准单元模式的优点:

(1)比门阵列更加灵活的布图方式。

(2)可以解决布通率问题,达到100%布 通率。

(3)“标准单元”预先存在单元库中,可 以提高布图效率。

(4)标准单元设计模式,由于其自动化程 度高、设计周期短、设计效率高。十分 适用于ASIC的设计,是目前应用最广泛 的设计方法之一。

2020/11/2

15

• 标准单元的改进

随着集成电路工艺的发展,标准单元布图 方式也在不断的改进,由于增加了布线 层数(3~7层)和采用“跨单元布线” (over-cell routing)技术,可允许出现不 等高的单元,而单元引线端的位置也可 以任意,不一定要在单元的上下边界上, 这样有利于提高芯片的利用率。由此造 成布线通道的不规则性,给自动布线算 法带来了一定难度。

2020/11/2

13

• 标准单元布图方法

在布图时,从单元库中调出标准单元按

行排列,行与行之间留有布线通道,同 行或相邻行的单元相连可通过单元行的 上、下通道完成。隔行单元之间的垂直 方向互连则必须借用事先预留在“标准 单元”内部的走线道(feed-through)或 在两单元间设置的“走线道单元” (feed-through cell)或“空单元” (empty cell)来完成连成。

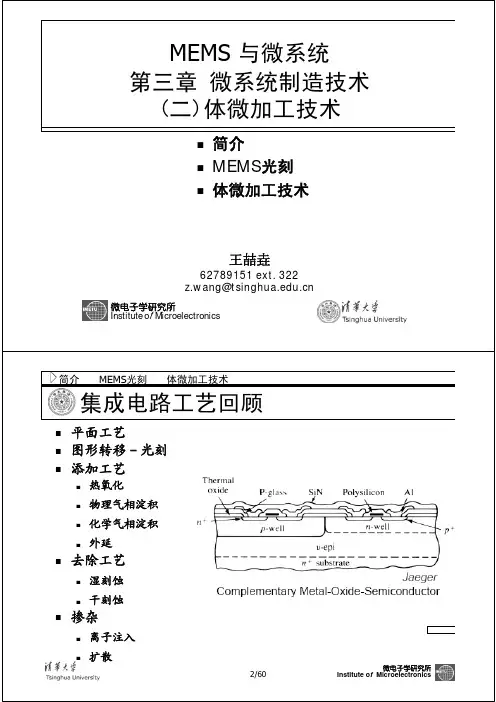

清华大学MEMS课程讲义

3/60微电子学研究所Institute o f Microelectronics电镀(Electroplating)7/60微电子学研究所Institute o f Microelectronics MEMS光刻体微加工技术)各向同性湿法刻蚀与刻蚀剂成分比例有关23/60微电子学研究所Institute o f Microelectronics MEMS光刻体微加工技术Question:What will happen in KOH etching?微电子学研究所刻蚀侧壁与底面垂直不能实现任意开口形状保护方法机械夹具/黑胶/浮片各向异性湿法刻蚀37/60微电子学研究所Institute o f Microelectronics39/60微电子学研究所Institute o f Microelectronics 简介MEMS光刻体微加工技术43/60微电子学研究所Institute o f Microelectronics简介MEMS光刻体微加工技术物理刻蚀利用粒子的能量进行轰击优缺点微电子学研究所Institute o f Microelectronics 电子、离子、中性基团、分子微电子学研究所Institute o f Microelectronics微电子学研究所Institute o f Microelectronics等离子体硅微电子学研究所Institute o f Microelectronicsm/min55/60微电子学研究所Institute o f MicroelectronicsMEMS光刻体微加工技术低温DRIE特性↓↓↓↓等离子体硅片源59/60微电子学研究所Institute o f Microelectronics1B1A’2B 1B’1A 2B’2A’2Ax-轴y-轴z-轴3轴加速C M O S 集成63/60微电子学研究所Institute o f MicroelectronicsMEMS光刻体微加工技术作业100:98:1. 画出刻蚀40秒, 100秒和600秒后的窗口截面图说明厚胶光刻中曝光衍射和散射、分辨率下降、以及曝光剂量不够的解决。

清华大学MEMS课程讲义

压阻系数:单位应力引起的相对电阻率变化量

14/46

微电子学研究所 Institute of Microelectronics

简介

敏感机理

压力传感器

加速度传感器

微陀螺

其他传感器

压阻效应

单晶硅的电阻率相对变化量

0 0 ⎤ ⎡ T1 ⎤ ⎡ d1 ⎤ ⎡ Δρ1 ⎤ ⎡π 11 π 12 π 12 0 ⎢d ⎥ ⎢ Δρ ⎥ ⎢π ⎢ ⎥ 0 0 ⎥ ⎢ 2⎥ ⎢ 2 ⎥ ⎢ 12 π 22 π 12 0 ⎥ ⎢T2 ⎥ ⎢ d3 ⎥ 1 ⎢ Δρ3 ⎥ ⎢π 12 π 12 π 11 0 0 0 ⎥ ⎢T3 ⎥ ⎢ ⎥= ⎢ ⎥=⎢ ⎥⎢ ⎥ d ρ 0 0 0 π 0 0 Δ ρ 4 4 44 0 ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢T4 ⎥ ⎢d ⎥ ⎢ Δρ ⎥ ⎢ 0 0 0 0 π 44 0 ⎥ ⎢T5 ⎥ ⎢ 5⎥ ⎢ 5⎥ ⎢ ⎥⎢ ⎥ d ρ 0 0 0 0 0 π Δ ⎢ ⎢ ⎥ ⎢ ⎥ 44 ⎥ ⎦⎢ ⎣ 6⎦ ⎣ 6⎦ ⎣ ⎣T6 ⎥ ⎦

简介

敏感机理

压力传感器

加速度传感器

微陀螺

其他传感器

传感器的分类

根据敏感器件

电容传感器 谐振传感器 压阻传感器 压电传感器 隧道传感器 机械(力学) 热 电 磁 辐射 化学传感器

7/46

微电子学研究所 Institute of Microelectronics

根据输入量

其他传感器

压阻效应

平面应力的压阻变化

T3 = T4 = T5 = 0

′ − ρ0 ΔR ρ11 ′ T1′ + π 12 ′ T2′ + π 16 ′ T6′ = π l Tl + π tTt + π sTs = = π 11 R0 ρ0

模拟电子技术基础清华大学全套完整版PPT课件

电路中有40亿个晶体管。有科学家预测,集成度还将按10倍

/6年的速度增长,到2015或2020年达到饱和。

学习电子技术方面的课程需时刻关注电子技术的发展!

华成英 hchya@

值得纪念的几位科学家!

第一只晶体管的发明者

(by John Bardeen , William Schockley and Walter Brattain

近似分析要“合理”。 抓主要矛盾和矛盾的主要方面。 电子电路归根结底是电路。不同条件下构造不同模型。

2. 实践性

常用电子仪器的使用方法 电子电路的测试方法 故障的判断与排除方法 EDA软件的应用方法

华成英 hchya@

五、如何学习这门课程

1. 掌握基本概念、基本电路和基本分析方法

子的浓度及其梯度均有变化,也有电荷的积累和释放

的过程,其等效电容称为扩散电容Cd。

结电容: Cj Cb Cd

结电容不是常量!若PN结外加电压频率高到一定程 度,则失去单向导电性!

清华大学 华成英 hchya@

华成英 hchya@

问题

物质因浓度差而产生的运动称为扩散运动。 气体、液体、固体均有之。

P区空穴 浓度远高 于N区。

N区自由电 子浓度远高

于P区。

扩散运动

扩散运动使靠近接触面P区的空穴浓度降低、靠近接 触面N区的自由电子浓度降低,产生内电场。

华成英 hchya@

PN 结的形成

由于扩散运动使P区与N区的交界面缺少多数载流子,形成 内电场,从而阻止扩散运动的进行。内电场使空穴从N区向P区、 自由电子从P区向N 区运动。

以及将所学知识用于本专业的能力。

注重培养系统的观念、工程的观念、科技进 步的观念和创新意识,学习科学的思维方法。提 倡快乐学习!

清华大学模电版华成英课件第七章

清华大学 华成英 hchya@

§6.2 负反馈放大电路的方框图 及放大倍数的估算

2. 若在第三级的 射极加旁路电容, 则反馈的性质有何 变化?

3. 若在第三级的射极加旁路电容,且在输出端和输入 端跨接一电阻,则反馈的性质有何变化?

分立元件放大电路中的净输入量和输出电流

• 在判断分立元件反馈放大电路的反馈极性时,净输入 电压常指输入级晶体管的b-e(e-b)间或场效应管g-s (s-g)间的电位差,净输入电流常指输入级晶体管的 基极电流(射极电流)或场效应管的栅极(源极)电 流。

描述放大电路和反馈网络在输入端的连接方式, 即输入量、反馈量、净输入量的叠加关系。

+ _

负反馈

Ui Ui' Uf --串联负反馈 Ii Ii' If --并联负反馈

3. 四种反馈组态:注意量纲

电压串联负反馈 电压并联负反馈

电流串联负反馈

为什么在并

联负反馈电路 中不加恒压源 信号?

反馈电流

净输入电流减小,引入了负反馈

iR2

uN uO R2

反馈量

净输入电流 增大,引入 了正反馈

在判断集成运放构成的反馈放大电路的反馈极性时,净 输入电压指的是集成运放两个输入端的电位差,净输入电 流指的是同相输入端或反相输入端的电流。

4. 电压反馈和电流反馈的判断

令输出电压为0,若反馈量随之为0,则为电压反馈; 若反馈量依然存在,则为电流反馈。

《清华大学VLSI》PPT课件

100000000

1000000

10000000

100000 58%/Yr. Complexity

10000 growth rate

第五节 存储器 (Memory) 1. 只读存储器(ROM):(EPROM,EEPROM) 2. 随机存储器(RAM):(动态随机存储器DRAM, 静态随机存储器SRAM)

第六节 交通灯

以上内容由于在《数子逻辑》课中已详细讨论过,所以 本课不作详细介绍了。

2021/4/26

23

Giga-Scale System-On-A-Chip

• Design Complexity C1 x C2

2021/4/26

27

Logic Transistors/Chip(K) Transistors/Staff-Month

Productivity Gap

Chip Capacity and Designer Productivity

10000000

应用硬应用硬软件协同设计方法实现软件协同设计方法实现socsoc的嵌入式系统的嵌入式系统vlsicadvlsicad系统组成系统组成系统描述综合验证分析模拟物理布图提取测试诊断计划研究的计划研究的edaeda技术技术测试与诊断原则

第四章 逻辑设计技术

2021/4/26

1

第一节 MOS管的串、并联特性

设:标准反相器的导电因子为βn=βp, 逻辑门:βn1=βn2=β’n βp1=βp2=β’p

Vdd

Tp

Vi

V0

Tn

2021/4/26

Vss 7

(1)a,b=1,1时,下拉管的等效导电因子:βeffn=β’n/2

(2)a,b=0,0时,上拉管的等效导电因子:βeffp=2β’p

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2011-3-20

清华大学微电子学研究所 陈弘毅

31

三 流水线与并行处理(续)

– 并行处理用于降功耗

• 对 L级并行处理系统

2011-3-20

清华大学微电子学研究所 陈弘毅

42

四 重定时(续)

• 小结:重定时

– 在不改变系统的输入输出特性的前提下,改变电路延迟元件 的配置 – 重定时的重要性质

– 重定时技术

• 不改变环路中的总延迟数 • 不改变DFG的迭代边界T • 割集重定时

– 在割集的各反向边增减相同的延迟数 – k倍降速 (k-slow)技术

» 子图 1中节点取0 » 子图 2中节点取k

1 0

0

• 一般割集的重定时

1

0

• 节点重定时:非常有用

– 割集围绕节点 – 右下图例: r(1)=0, r(2)=1, r(3)=0, r(4)=0

2011-3-20

1 0

0

割集围绕节点的重定时 37

清华大学微电子学研究所 陈弘毅

四 重定时(续)

• 前馈割集重定时:流水线(无环路)系统,属割集重定时的特殊情况

• 可见:展开 并行处理

– 应用

• 发掘算法潜在的并发性,采用并行处理来降低迭代(采样)周期,(对 环路来说)向迭代边界T逼进 • 得到位/字级并行架构,位串行位并行或字串行、字串行字并行 • 展开 =环路展开(Loop Unrolling),应用于汇编编程、编译理论

2011-3-20 清华大学微电子学研究所 陈弘毅 45

清华大学微电子学研究所 陈弘毅 36

四 重定时(续)

• 重定时技术

– 割集重定时:在割集的各反向边增减相同的延迟数

• 规则

– 重定时值r(V)

– 所有路径权重wr(p)0 – 在所有某向边增加 k个延迟数 – 在所有反向边减去 k个延迟数 – 右上图例:r(1)=0, r(2)=1, r(3)=0, r(4)=1

2011-3-20 清华大学微电子学研究所 陈弘毅 35

四 重定时(续)

• 关于重定时的一般化方法:定义、性质和求解

– 定义

• 重定时:将一个电路G映射到一个重定时电路Gr ,即 G Gr • 重定时值:每个节点V的重定时值r(V) 用来表征G Gr的重定时解 • 重定时方程:用来确定节点U到V的边UV(e)重定时后的权重

– 充放电电容不变,但是总负载电容增加L倍 – 关键路径不变,但是每个时钟周期处理L个样点 – 为保持原来的采样速率,L级并行处理系统的时钟周期增加为 LTseq (Tseq是原始时序电路的传播延时)。这意味着负载电容充 放电时间长L倍(即 LTseq),则电源电压可以减低到V0 – 利用原始系统与并行处理系统传播延时的公式

五 展开(续)

• 展开的算法

– 符号

• x:表示对x向下取整,即取小于或等于x的最大整数 • x:表示对x向上取整,即取大于或等于x的最小整数 • a% b(或 amodb):表示a除以b的余数,其中a和b是整数

• 节点 U:有 J个具有相同功能的节点Ui (i=0, 1, …, J-1) • 边:有 J条相应的边 即: J阶展开后的DFG总是包含了相当于原始DFG的 J倍 数量的节点和边

2011-3-20

清华大学微电子学研究所 陈弘毅

44

五 展开(续)

– 展开特点

• 上例变换后的两个公式描述的连续迭代是原式的一个二阶展开(2unfolding)版本 • 在 J阶展开系统中,每个延迟元件是J倍降速(J-slow)的

– 如果输入到一个延迟单元的信号是x(kJ+m),则该延迟单元的输出是 x((k-1)J+m)=x(kJ+m-J)

2011-3-20 清华大学微电子学研究所 陈弘毅 29

三 流水线与并行处理(续)

• 功耗降低因子Βιβλιοθήκη 的求法– 利用原始系统与流水线系统传播延时的公式

– 根据:Tseq = Tpip,有

• 流水线系统的功耗为

2011-3-20

清华大学微电子学研究所 陈弘毅

30

三 流水线与并行处理(续)

• 例1:简单数据通路

– 流水线用于降功耗:仅做宏观估计

• 原始时序系统(如 FIR滤波器)中的功耗

• 对 M级流水线系统

– 关键路径减少为原始的 1/M (fs可以提高M倍 ) – 在单个时钟周期要充放电的负载电容也减少为原始的1/M (但是总负载 电容不变 ) – 时钟速度 fs保持不变前提下降低功耗:在相同时间 Ts内,只需对原始电 容的 1/M部分充放电,意味着电源电压V0可以降低到V0 (0< <1),即 功耗降低 2倍。称功耗降低因子

– J阶展开DFG的节点与边

– 构建一个 J阶展开DFG

• 对原始 DFG中的每个节点U,画J个节点U0, U1, …, UJ-1 • 对在原始 DFG中的每个延迟为w的边UV,画延迟为 wunf(i)=(i+w)/J的 J个边UiV(i+w)%J (i=0, 1, …, J-1)

2011-3-20 清华大学微电子学研究所 陈弘毅 46

– 由不等式组画出约束图,用最短路径求出所有节点重定时值解r

2011-3-20 清华大学微电子学研究所 陈弘毅 43

五 展开

• 引言

– 展开 (Unfolding):是一种转换技术,它产生一个新的程序来 描述原有程序的多次迭代,J称展开因子,表示迭代次(阶 ) 数

• 例子:对DSP程序y(n)=ay(n-9)+ x(n)进行2阶展开 y(2k)=ay(2k-9)+ x(2k)= ay((2(k-5)+1)+ x(2k) y(2k+1)=ay(2k-8)+ x(2k+1)= ay((2(k-4)+0)+ x(2k+1)

2011-3-20 清华大学微电子学研究所 陈弘毅 33

三 流水线与并行处理(续)

– 流水线与并行处理结合降功耗

• 流水线与并行处理结合可以更有效降功耗

– 流水线减少在一个时钟内的充/放电电容 – 并行处理增加对原始电容充/放电时钟周期 – 并行流水系统传播延时 – 求解 的方程

• 功耗降低因子的求法

• 一般的重定时流程(略)

– 给出重定时目标:例如时钟周期c – 计算最小延迟路径权重 W(U, V)和最长路径的计算时间D(U, V):可直接 从 DFG求出 – 由约束条件列出不等式组

» 可行性约束(权重非负 ):对 UV来说,要求 r(U)-r(V) w(e) » 关键路径约束 (权重非负):对(U, V)之 D(U, V) c时,要求插入延迟,即r(U)r(V) W(U, V)-1

– 前馈割集的边都是同向的,则都加个 k延迟,无反向边 – 右图 4阶 FIR滤波器可以在割集 的两个同向边都加一个延迟

• k倍降速(k-slow)后的割集重定时

– 用 kD取代 D:如下图右,k=2

» » » » 是 Tclk不变的降速 隔 1时钟输入1样点,奇数时钟插入空操作 硬件利用率50% 时钟周期不变,Tclk=2 u.t. ,迭代周期加倍,Titer=4 u.t.

– 重定时前后的权重(即延迟数):分别为 w和wr – G中所有节点按重定时值r(U)、 r(V)、。。。进行重定时 – G Gr的重定时解满足重定时方程

– 重定时性质:可由重定时方程导出

– 重定时流程(略)

2011-3-20

• 对于重定时的路径p= V0 V1 … Vk,其权重由下式计算 wr(p) = w(p)+r(Vk)-r(V0) 只与路径起始、终止节点的重定时值相关 • 重定时不改变环路中的总延迟数:因为环路之Vk=V0 • 重定时不改变DFG的迭代边界T:T=TL/wL ,因为环路的运行时间 和延迟数都不变化 • 所有节点重定时值r(V)都增加常数值j, 重定时映射G Gr不变

加

乘a

–2阶展开图中的边

» 无延迟边 AC 、 C B 、 D C都展开为连接相应节点的两条边 » 延迟 9D(w=9)的边 CD展开为两条边:延迟4D(wunf=(0+9)/2=4)的 边 C0 D1(D(0+9)%2= 1)和延迟 5D(wunf= (1+9)/2=5) C1 D0(D(1+9)%2= 0) 当 w<J时,展开原始DFG中延迟为w的边,相当于在J阶展开DFG中 生成了 J-w条无延迟的边和 w条延迟为1的边

• 例 3:前述简单数据通路,见下页图

– 2级并行+2级流水:L= M= 2 – 设 Vt=0.45V; V0=5V – 根据计算:=0.4 – 考虑多路器和锁存器影响:Ctotal=2.35C – 电源可降为2V 功耗为原始的19%

2011-3-20 清华大学微电子学研究所 陈弘毅 34

四 重定时

• 割集重定时可以多次使用,以便取得优化的性能

2011-3-20 清华大学微电子学研究所 陈弘毅 40

四 重定时(续)

2011-3-20

清华大学微电子学研究所 陈弘毅

41

四 重定时(续)

例子:递归滤波器,下图, G Gr

• • • • 已知重定时值为:r(1)=0, r(2)=1, r(3)=0, r(4)=0 wr (2 1)=w (2 1)+r(1)-r(2)=0 wr (3 2)=w (3 2)+r(2)-r(3)=1 wr (4 2)=w (4 2)+r(2)-r(4)=1

三 流水线与并行处理(续)

• 流水线与并行处理用于降低功耗

– 流水线与并行处理的优点:提高速度、降低功耗 – CMOS电路的两个简化了的公式