实验五 地址译码电路与IO接口

接口实验整理

一、I/O译码端口实验一、实验目的掌握I/O地址译码电路的工作原理。

二、实验原理和内容实验电路如图1-1所示,其中74LS74为D触发器,可直接使用实验台上数字电路实验区的D触发器,74LS138为地址译码器。

译码输出端Y0~Y7在实验台上“I/O地址“输出端引出,每个输出端包含8个地址,Y0:280H~287H,Y1:288H~28FH,……当CPU执行I/O 指令且地址在280H~2BFH范围内,译码器选中,必有一根译码线输出负脉冲。

例如:执行下面两条指令MOV DX,2A0HOUT DX,AL(或IN AL,DX)Y4输出一个负脉冲,执行下面两条指令MOV DX,2A8HOUT DX,AL(或IN AL,DX)Y5输出一个负脉冲。

图1-1利用这个负脉冲控制L7闪烁发光(亮、灭、亮、灭、……),时间间隔通过软件延时实现。

三、编程提示1、实验电路中D触发器CLK端输入脉冲时,上升沿使Q端输出高电平L7发光,CD端加低电平L7灭。

;*******************************;;* I/O地址译码*;;*******************************;outport1 equ 2a0houtport2 equ 2a8hcode segmentassume cs:codestart:mov dx,outport1out dx,alcall delay ;调延时子程序mov dx,outport2out dx,alcall delay ;调延时子程序mov ah,1int 16hje startmov ah,4chint 21hdelay proc near ;延时子程序mov bx,200lll: mov cx,0ll: loop lldec bxjne lllretdelay endpcode endsend start二、中断一、实验目的1、掌握PC机中断处理系统的基本原理。

接口实验报告

接口实验报告一、实验目的掌握I/O地址译码电路的工作原理。

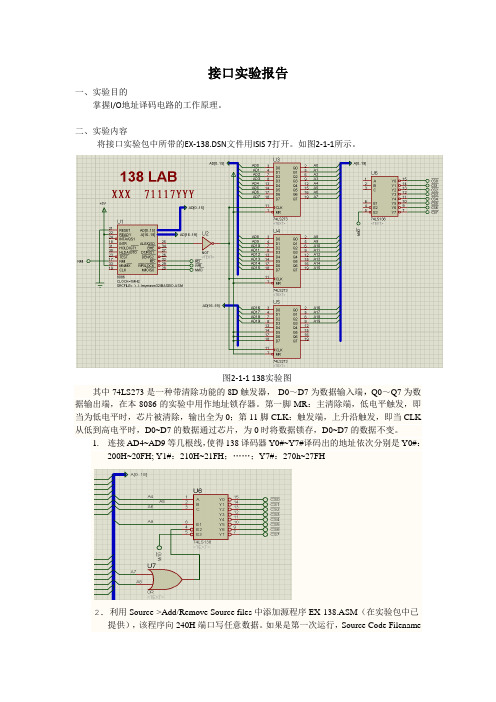

二、实验内容将接口实验包中所带的EX-138.DSN文件用ISIS 7打开。

如图2-1-1所示。

图2-1-1 138实验图其中74LS273是一种带清除功能的8D触发器,D0~D7为数据输入端,Q0~Q7为数据输出端,在本8086的实验中用作地址锁存器。

第一脚MR:主清除端,低电平触发,即当为低电平时,芯片被清除,输出全为0;第11脚CLK:触发端,上升沿触发,即当CLK 从低到高电平时,D0~D7的数据通过芯片,为0时将数据锁存,D0~D7的数据不变。

1.连接AD4~AD9等几根线,使得138译码器Y0#~Y7#译码出的地址依次分别是Y0#:200H~20FH; Y1#:210H~21FH;……;Y7#:270h~27FH2.利用Source->Add/Remove Source files中添加源程序EX-138.ASM(在实验包中已提供),该程序向240H端口写任意数据。

如果是第一次运行,Source Code Filename这一项选New来调入源程序。

如图2-1-2所示图2-1-2 添加源程序3.在Source菜单下点击“Build All”,汇编源代码(全部编译);执行程序,查看Y0~Y7中是否Y4#脚输出为有效(管脚出的有颜色的小方块为红色是高电平,蓝色为低电平),如图2-1-3所示。

图2-1-3 输出结果4.改变程序中的输出地址,使得Y0#, Y1#,Y6#,Y7#分别有效。

.8086.MODEL SMALL.stack.dataaddress word 260h //使Y6#有效,Y1#有效为210h,Y7#有效为270h,Y0#有效为200h.codestart:mov ax,@datamov ds,axmov dx,addressmov al,0out dx,aljmp $END start5.改变A9~A3的接线方法,从而得到Y0;388H~38FH;Y1:398H~39FH; ……;Y7:3F8H~3FFH。

IO接口数据传送及地址译码技术

Image 的数据 (输出寄存器)

状态寄存器——保存状态信息,CPU可从状态 口读取当前状态;

控制寄存器——用来保存CPU写入的控制字。

任何接口电路均包括如下基本功能:

No 1. 作为微型机与外设间传递数据的中间缓冲站; Image 2.正确寻址与微机交换数据的外设 ;

No (2) 模拟量

Image 非电量信息

传感器

电量

信号 处理

A/D CPU

No (3) 开关量 两个状态的量 (可以用0、1表示) Image 例如电机的启与停,开关的合与开等。

2. 状态信息 (STATUS)

No 反映当前外设工作状态的信息,例如:

输入时,输入设备是否准备好? (READY)

(256个) FFH

... ...

M空间

原则:M与I/O分开编址、互不干扰——M 与I/O地址不重叠

优点:M空间不受I/O空间影响;有专用 I/O指令(程序清晰);I/O指令短, 执行速度快

缺点:I/O指令种类有限,I/O空间不易 扩展

(64KB) FFFFH

Image 输出时,输出设备是否空闲?(BUSY)

3. 控制信息 (CONTROL)

CPU通过接口输出用以控制外设工。

AB

1 DATA

CPU

DB

I/O 接口

2

STATUS

I/O 设备

CB

CONTROL

3

CPU 与外设之间的接口信息

6.2 I/O 端口及其寻址方式

可寻址256个端口。

No 采用间接寻址,则其指令格式为: 输入指令:IN AL,DX 输出指令:OUT DX,AL

Image 这种间接寻址方式的端口地址为两个字节长,

I-O译码实验

I/O译码实验

实验目的: 掌握I/O端口的译码方法

实验设备: 数字逻辑实验箱

2

实验内容

已知并行接口芯片8255A有4个端口,片选信号 CS 为低电平有效。 试用组合逻辑电路实现一个译码电路,使该芯片的4个端口地址为 218H~21BH。

已知数/模转换芯片0832的端口地址为228H~22FH,片选信号CS为 低电平有效。试用集成器件74LS138实现。

3

实验步骤及说明

根据实验要求设计电路 根据设计电路进行连线,可利用实验箱上的开关控

制输入地址,并用发光二极管观测实验结果

4

微型计算机

微机原理与接口技术实验指导书(2 译码电路、简单并口、8253实验)

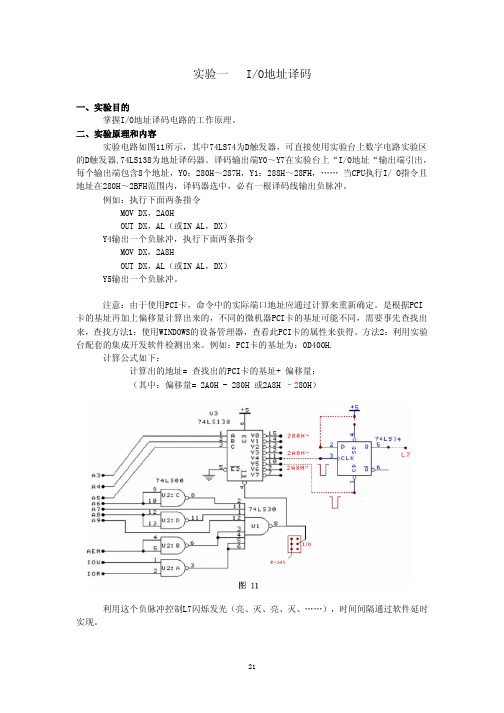

实验一 I/O地址译码一、实验目的掌握I/O地址译码电路的工作原理。

二、实验原理和内容实验电路如图11所示,其中74LS74为D触发器,可直接使用实验台上数字电路实验区的D触发器,74LS138为地址译码器。

译码输出端Y0~Y7在实验台上“I/O地址“输出端引出,每个输出端包含8个地址,Y0:280H~287H,Y1:288H~28FH,……当CPU执行I/ O指令且地址在280H~2BFH范围内,译码器选中,必有一根译码线输出负脉冲。

例如:执行下面两条指令MOV DX,2A0HOUT DX,AL(或IN AL,DX)Y4输出一个负脉冲,执行下面两条指令MOV DX,2A8HOUT DX,AL(或IN AL,DX)Y5输出一个负脉冲。

注意:由于使用PCI卡,命令中的实际端口地址应通过计算来重新确定。

是根据PCI 卡的基址再加上偏移量计算出来的,不同的微机器PCI卡的基址可能不同,需要事先查找出来,查找方法1:使用WINDOWS的设备管理器,查看此PCI卡的属性来获得。

方法2:利用实验台配套的集成开发软件检测出来。

例如:PCI卡的基址为:0D400H.计算公式如下:计算出的地址= 查找出的PCI卡的基址+ 偏移量;(其中:偏移量= 2A0H - 280H 或2A8H –280H)利用这个负脉冲控制L7闪烁发光(亮、灭、亮、灭、……),时间间隔通过软件延时实现。

三、编程提示1、实验电路中D触发器CLK端输入脉冲时,上升沿使Q端输出高电平L7发光,CD端加低电平L7灭。

2、由于TPC卡使用PCI总线,所以分配的IO地址每台微机可能都不同,编程时需要了解当前的微机使用那段IO地址并进行设置,获取方法前面已经介绍。

3、参考程序:ioport equ 0d400h-0280houtport1 equ ioport+2a0houtport2 equ ioport+2a8hstart:mov dx,outport1out dx,alcall delay ;调延时子程序mov dx,outport2out dx,alcall delay ;调延时子程序mov ah,1int 16hje startmov ah,4chint 21hdelay proc near ;延时子程序mov bx,2000lll: mov cx,0ll: loop lldec bxjne lllretdelay endp实验程序应有信息提示,按什么键开始,按什么键退出程序等控制功能。

微机原理-地址译码实验-实验报告

地址译码实验实验目的:理解并掌握MCS-51的数据总线和地址总线原理,外部数据空间及外部地址空间的访问,并对指令时序进行观测和计算。

实验内容:1.利用A0-A15,/WR 、/RD和74LS138设计译码电路。

并用MOVX指令,产生地址为2005H的外部数据空间地址选通信号(需要读、写信号参与译码电路控制端)。

2.用示波器分别观测选通脉冲ALE、读写信号/WR 、/RD、译码电路输出并测量宽度,画出MOVX指令周期时序图。

3.实验原理:1.MCS-51地址总线特点:1)地址线A0~A15 (16位)2)P2口提供高8位地址A8~A153)P0口经地址锁存器提供低8位地址A0~A7 。

4)片外存储器可寻址范围达64KB(即=65536个字节)5)传送地址6)单向2.数据总线和地址总线通过锁存器分离开来,经过锁存器的为地址总线。

3.多片外部数据存储器的扩展方法:1)线选法:单根高位地址线直接接在存储器的/CE端。

连接简单,不必附加电路,但不能提供全部64K地址空间且扩展地址不连续,且有地址重叠区。

2)译码法:附加译码电路,能提供全部64K地址空间且扩展地址连续。

4.访问片外扩展RAM指令所需时钟计算公式:MOV @DPTRwrite(写操作):5*N+2read(读操作):5*N+1实验流程图:实验代码:ORG 0000HLJMP MAINORG 0100H MAIN: MOV DPTR,#2005HMOVX A,@DPTRMOVX @DPTR,ASJMP MAINEND示波器波形WR使能时:ALE和WRALE和Y1RD使能时:ALE和RDALE和Y1WR使能时的ALE、Y1、WR、RD波形汇总(RD使能时Y1和RD几乎相同):有写操作,导致ALE触发了2次。

io地址译码实验

接口技术课程教案课程编号:182182YB总学时:51 周学时:3适用年级专业(学科类):07电信职本开课时间:2009-2010 学年第二学期使用教材:微型计算机接口技术授课教师姓名:孔世明实验1IO地址译码教具、教学素材准备:实验箱,多媒体教学方法:网络讲授与实作教学时数:2一、实验目的掌握I/O地址译码电路的工作原理。

二、实验原理和内容实验电路如图(1)所示,其中74LS74为D触发器,可直接使用实验台上数字电路实验区的D触发器,74LS138为地址译码器。

译码输出端Y0~Y7在实验台上“I/O地址“输出端引出,每个输出端包含8个地址,Y0:280H~287H,Y1:288H~28FH,……当CPU执行I/O 指令且地址在280H~2BFH范围内,译码器选中,必有一根译码线输出负脉冲。

例如:执行下面两条指令MOV DX,2A0HOUT DX,AL(或IN AL,DX)Y4输出一个负脉冲,执行下面两条指令MOV DX,2A8HOUT DX,AL(或IN AL,DX)Y5输出一个负脉冲。

MOV DX,2A0HOUT DX,AL(或IN AL,DX)Y4输出一个负脉冲,执行下面两条指令MOV DX,2A8HOUT DX,AL(或IN AL,DX)Y5输出一个负脉冲。

利用这个负脉冲控制L7闪烁发光(亮、灭、亮、灭、……),时间间隔通过软件延时实现D触发器特征函数三、编程提示实验电路中D触发器CLK端输入脉冲时,上升沿使Q端输出高电平L7发光,CD端加低电平L7灭。

;*******************************;;* I/O地址译码*;;*******************************;ioport equ 0cc00h-0280houtport1 equ ioport+2a0houtport2 equ ioport+2a8hcode segmentassume cs:codestart:mov dx,outport1out dx,alcall delay ;调延时子程序mov dx,outport2out dx,alcall delay ;调延时子程序mov ah,1int 16hje startmov ah,4chint 21hdelay proc near ;延时子程序mov bx,2000lll: mov cx,0ll: loop lldec bxjne lllretdelay endpcode endsend start几点约定:1、实验电路介绍中凡不加“利用通用插座”说明的均为实验台上已固定电路。

IO端口地址译码PPT课件

同步通信卡1

3A0H~3AFH

同步通信卡2

380H~38FH

单显MDA

3B0H~3BFH

彩显CGA

3D0H~3DFH

彩显EGA/VGA

3C0H~3CFH

硬驱控制卡

1F0H~1FFH

软驱控制卡

3F0H~3F7H

PC网卡

360H~36FH

.

本章7首页

5.2.3 I/O端口地址译码

1. I/O地址译码电路工作原理及作用

.

本章12首页

本章要点

端口的概念 端口的地址编址方式及其特点 I/O端口地址选用的原则 掌握I/O端口地址译码电路的工作原理 I/O端口地址译码电路的设计与分析

.

本章13首页

片间选择:高位地址+控制信号

译码电路

片选信号

高位地址、 低位地址的划分

片内端口选择:低位地址直接与接口芯片地址线相连

.

本章8首页

5.2.3 I/O端口地址译码(续)

3. I/O端口地址译码电路设计

A9

地址范围:n根地址线未参与译码,译出地址含2n个 1)固定式端口地址译码 门电路译码法——单个地址或地址范围

微机原理与接口

(第5章)

信息工程学院 电子信息工程教研室

.

1

5.2 I/O端口地址译码技术

主要内容

5.2.1 I/O端口及其编址方式 5.2.2 I/O端口地址分配 5.2.3 I/O端口地址译码

.

2

5.2.1 I/O端口及其编址方式

1. I/O端口和I/O操作

1)I/O端口

端口(port):是接口电路中能被CPU直接访问的寄存器。

C

Y0

实验一 IO地址译码报告

实验一I/O地址译码一、实验目的掌握I/O地址译码电路的工作原理。

二、实验原理和内容实验电路如图1-1所示,图中线路两端有节点的信号线需要用户用实验导线连接起来,其中74LS74为D触发器,可直接使用实验台上部系统板上的D触发器。

74LS138为地址译码器。

译码输出端Y0-Y7在实验台中间系统板上引出,每个输出端包含8个地址,即:Y0:280H~287H;Y4:2A0H~2A7H;Y1:288H~28FH; Y5:2A8H~2AFH;Y2:290H~297H; Y6:2B0H~2B7H;Y3:298H~29FH; Y7:2B8H~2BFH;图1-1 I/O地址译码电路图当CPU执行I/O指令且地址在280H~2BFH范围内,译码器选中,必有一根译码线输出负脉冲。

例如:执行下面两条指令,对应的译码输出脚输出一个负脉冲。

MOV DX, PORT1OUT DX, AL(或IN AL, DX)执行下面两条指令,对应的译码输出脚输出一个负脉冲。

MOV DX, PORT2OUT DX, AL(或IN AL, DX)利用这个负脉冲控制发光二极管L0闪烁发光(灭亮循环),时间间隔通过软件延时实现。

注意:命令中的端口地址PORT1、PORT2是根据DVCC卡的I/O基址再加上偏移量计算出来的,不同的微机DVCC卡的I/O 基址可能不同,需要事先查找出来。

计算公式如下:PORT1=查找出的DVCC卡的I/O基址+偏移量其中:偏移量=Y0~Y7中所选定的任意一个译码地址值-280H。

下面的程序用到L4,即2A0H。

假设DVCC卡的I/O基地址=0C400H,经计算PORT1=0C420H。

三、编程提示1.实验电路中D触发器的CLK端输入脉冲时,上升沿使Q端输出高电平,L0发光,CLK端加低电平L0灭。

2.由于DVCC卡使用PCI总线,所以分配的IO地址每台微机可能都不用,编程时需要了解当前的微机使用那段IO地址并进行处理。

实验五 编码译码器

实验五译码器(编码译码显示电路)一、实验目的1、掌握中规模集成译码器的逻辑功能和使用方法。

2、掌握数码管的原理和使用。

二、实验原理译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同的译码器。

译码器可分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

1、变量译码器(又称2进制译码器),用以表示输入变量的状态,如2线一4线、3线一8线和4线一16线译码器。

若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。

而每一个输出所代表的函数对应于n个输入变量的最小项。

以3线一8线译码器74LS138为例进行分析,图1中的(a)、(b)分别为其逻辑图及引脚排列,其中A0、A1、A2为地址输入端,Y0~Y7为译码输出端,S1、S2、S3为使能端。

表1为74LS138功能表:123信号(全为1)输出。

当S1=0,S2+S3=X时(X为任意,0、1均可),或S1=X,S2+S3=l时,译码器被禁止,所有输出同时为1。

二进制译码器实际上也是负脉冲输出的脉冲分配器。

若利用使能端中的一个输入端输入数据信息,器件就成为一个数据分配器(又称多路分配器),如图2所示。

若在S1输入端输入数据信息,S2=S3=0,地址码所对应的输出是S1数据信息的反码;若从S2端输入数据信息,令S1=1、S3=0,地址码所对应的输出就是S2端数据信息的原码。

若数据信息是时钟脉冲,则数据分配器便成为时钟脉冲分配器。

根据输入地址的不同组合译出唯一地址,故可用作地址译码器。

接成多路分配器,可将一个信号源的数据信息传输到不同的地点。

二进制译码器还能方便地实现逻辑函数,如图3所示,实现的逻辑函数是:Z=CB+ABCA+A CBA+CB利用使能端能方便地将两个3/8译码器组合成一个4/16译码器,如图4所示:2、数码显示译码器a、七段发光二极管(LED)数码管LED数码管是目前最常用的数字显示器,图5的(a)、(b)分别为共阴管和共阳数码管的电路,右侧图为共阴共阳两种不同形式的引出脚功能图。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电工电子实验中心

实验报告

课程名称:计算机硬件技术基础

实验名称:地址译码电路与I/O接口姓名:学号:

评定成绩:审阅教师:

实验时间:2017.05.16

南京航空航天大学

1) 学习 3-8 译码器在接口电路中的应用。

2) 掌握地址译码电路的一般设计方法。

3) 理解输入输出接口的基本原理。

二、实验任务

用 74LS138 译码器设计地址译码电路,其 Y7 作为基本输入/输出单元的片选信号。

参考实验电路如图 3-1-1 所示,功能及流程如下:

1) 读入74LS245 输入的八位数据,在74LS574 上输出,用八位LED

显示开关状态。

2) 当有键按下,且读入的数字量为 1, 则八位 LED 从右向左依次循点

亮,否则重读数字量。

3) 再有键按下,且读入的数字量为 2, 则八位 LED 交替亮,否则重读

数字量。

4) 再有键按下返回。

图3-1-1 地址译码设计实验电原理框图

四、实验代码

IOY0 EQU 3000H ;片选IOY0对应的端口始地址Y7 EQU IOY0+0E0H ;译码电路输出Y7对应的端口地址DATA SEGMENT

NUM DB 01H

DATA ENDS

STACK1 SEGMENT STACK

DW 256 DUP(?)

STACK1 ENDS

CODE SEGMENT

ASSUME CS:CODE,DS:DATA

START: MOV DX, Y7 ;读入开关量

IN AL, DX

OUT DX, AL

MOV AH, 1 ;判断是否有按键按下

INT 16H

JZ START ;无按键则跳回继续循环,有则退出

L1: MOV DX,Y7

IN AL,DX ;读入开关量, 判断是否为1

CMP AL,1

JNE L1

L2: MOV DX,Y7

MOV AL,NUM

OUT DX,AL ;八位LED从右向左依次循点亮

ROL AL,1

MOV NUM,AL

CALL DELAY

MOV DL,0FFH

MOV AH, 6 ;判断是否有按键按下

INT 21H

JZ L2 ;无按键则跳回继续循环,有则退出L3: MOV DX,Y7

IN AL,DX ; 读入开关量, 判断是否为2

CMP AL,2

JNE L3

MOV NUM,55H

L4: MOV DX,Y7

MOV AL,NUM

OUT DX,AL ;八位LED交替亮

NOT AL

MOV NUM,AL

CALL DELAY

MOV DL,0FFH

MOV AH, 6 ;判断是否有按键按下

INT 21H

JZ L4 ;无按键则跳回继续循环,有则退出

MOV AX, 4C00H ;结束程序退出

INT 21H

DELAY PROC

MOV BX,3FFH

DELAY1:MOV CX,0FFFFH

LOOP $ ;延时子程序

DEC BX

JNZ DELAY1

RET

DELAY ENDP

CODE ENDS

END START

五、实验的运行数据及分析

电路实现以下功能:

1) 读入 74LS245 输入的八位数据,在 74LS574 上输出,用八位 LED 显示开关状态。

2) 当有键按下,且读入的数字量为 1, 则八位 LED 从右向左依次循点亮,否则重读数字量。

3) 再有键按下,且读入的数字量为 2, 则八位 LED 交替亮,否则重读数字量。

4) 再有键按下返回。

六、实验讨论及心得体会

实验的过程中了解了试验箱的用法,也对PIT++软件的使用有所掌握。

通过对实验现象的分析,对数字电子技术中学过的74LS138的工作原理有了更深的理解。

学习了3-8 译码器在接口电路中的应用,掌握地址译码电路的一般设计方法,加深理解了输入输出接口的基本原理。