数字电子技术第六章习题课【精选】

《数字电子技术 》课件第6章

图6.3 SRAM存储元

2. DRAM存储元 静态MOS管组成的存储元中管子数目较多, 不利于提 高集成度。 为了克服这些缺点, 人们利用大规模集成工艺, 研制出了动态DRAM。 DRAM存储信息的原理基于MOS管 栅极电容的电荷存储效应。 由于漏电流的存在, 电容上存储的信息不能长久保持, 因而必须定期给电容补 充电荷, 以免存储的信息丢失, 这种操作称为再生或刷新。

图6.5 随机读/写存储器位扩展方式

2. 字扩展方式 字扩展的方法是将地址线、 输出线对应连接, CS分别与译码器的输出端连接。 图6.6所示为4片256×8 RAM扩展为1024 ×8 RAM, 需要有10根地址输入线。

图6.6 随机读/写存储器字扩展方式

然而每片集成电路上的地址输入端只有8位(A0~A7), 给出的地址范围全部是0~255, 无法区分4片中同样的地址 单元。 因此增加了两位地址代码A8、A9, 使地址代码增加 到10位, 才得到1024地址。 图6.6中通过2线-4线译码器选 择每片RAM的片选端CS, 当CS=0时, 该片被选中工作, 当 CS=1时, 该片RAM不工作, 从而实现了4片RAM轮流选通 工作。

3. 可擦除可编程只读存储器 可擦除可编程只读存储器(EPROM)不仅可以编程, 而且 写入的信息可以擦除, 从而再编入新的信息, 即可多次编 程。 因此熔丝结构、 二极管结构不能作为EPROM的编程单 元, 而应采用浮栅型MOS管。 编程时, 给写入“0”信息的 MOS管的浮栅充电; 若要擦除信息, 则以紫外光照射使浮 栅上所积累的电荷消失。

地址译码电路实现地址的选择。 在大容量的存储器中, 通常采用双译码结构, 即将输入地址分为行地址和列地址 两部分, 分别由行地址译码电路、 列地址译码电路译码。 行地址译码电路、 列地址译码电路的输出作为存储矩阵的 行地址选择线、 列地址选择线, 由它们共同确定欲选择的 地址单元。 地址单元的个数N与二进制地址码的位数 n满足关系式N=2n。 图6.2是一个1024×4位的RAM实例。

数字电子技术第6章习题及解答2

第6章习题解答1. 电路如图6-1所示,试分析其功能。

(1)写出驱动方程、次态方程和输出方程;(2)列出状态表,并画出状态图和时序波形。

图6-1 题1图z解 (1)根据图6-1写出驱动方程'1'21Q Q D =, 12Q D =将其代入D 触发器的特性方程,得每一触发器的状态方程'1'21*1Q Q D Q ==12*2Q D Q ==输出方程为 CP Q z ⋅=2(2)由状态方程可列出状态表如表6-1所示。

按表00,可作出时序波形图如图6-2(b )所示。

图6-2 题1状态图和波形图CP Q 2Q 1z(a )(b )2. 时序电路如图6-3所示。

(1)写出该电路的状态方程、输出方程;(2)列出状态表,画出状态图。

图6-3 题2图解 (1)驱动方程 x K J ==11 122xQ K J ==将其代入JK 触发器的特性方程,的状态方程21'21*21'1*1)'('Q xQ Q xQ Q Q x xQ Q +=+=输出方程 21Q xQ z =(2)假定一个现态,代入状态方程,得出对应的次态和输出状态,列表表示即得状态表,如表6-2所示。

由此算出状态图,如图6-4所示。

表6-2 题2状态表图6-4 题2的状态图3. 某计数器的输出波形如图6-5所示,试确定该计数器是模几计数器,并画出状态图。

图6-5 题3图CP Q A Q B QC解 由波形图画出状态图,Q C 为高位,Q A 为最低位。

010000001100011101Q C Q B Q A故该波形显示的计数器的计数模为六。

4. 分析如图6-6所示的同步时序电路。

图6-6 题4图解 (1)有题图得到各级触发器的驱动方程为⎪⎪⎩⎪⎪⎨⎧====34231242'3'11)'(Q D Q D Q D Q Q Q Q D(2)列出状态方程为⎪⎪⎩⎪⎪⎨⎧========34*423*312*242'3'11*1)'(Q D Q Q D Q Q D Q Q Q Q Q D Q由驱动方程和状态方程可以确定,该电路是移位寄存器型时序电路,其电路的状态转移决定于第一级的驱动信号。

《数字电子技术基础》第六章习题答案

第六章存储器和可编程器件6.1 填空1、按构成材料的不同,存储器可分为磁芯和半导体存储器两种。

磁芯存储器利用 正负剩磁 来存储数据;而半导体存储器利用 器件的开关状态 来存储数据。

两者相比,前者一般容量较 大 ;而后者具有速度 快 的特点。

2、半导体存储器按功能分有 ROM 和 RAM 两种。

3、ROM 主要由 地址译码器 和 存储矩阵 两部分组成。

按照工作方式的不同进行分类,ROM 可分为 固定内容的ROM 、 PROM 和 EPROM 三种。

4、某EPROM 有8数据线,13位地址线,则其存储容量为 213×8 。

5、PLA 一般由 与ROM 、 或ROM 和 反馈逻辑网络 三部分组成。

6.2 D 0A 0D 1m(3,6,9,12,15)D 210D 3m(0,5,9,13)==∑=⋅=∑⎧⎨⎪⎪⎪⎩⎪⎪⎪ 6.3地址译码器A1A0D3 D2 D1 D0B1B0m 0m 156.4 1。

F Q Q Q Q Q Q Q F Q Q Q Q Q Q Q Q Q F Q Q 110212102210210210310=⋅+⋅+⋅=⋅⋅+⋅+⋅⋅=⋅⎧⎨⎪⎪⎩⎪⎪2、CP F1F2F36.5A AB BC C i-1i-1S i C i6.6 用PLA 实现BCD8421码十进制加法计数器和相应的显示译码电路。

D 1Q1Q1D2 Q2 Q2D3 Q3Q3D4Q4Q49 87654 3210a b c d e f ga b cdef g。

数字电子技术第6章 时序逻辑电路

RD—异步置0端(低电平有效) 1 DIR—右移串行输入 1 DIL—左移串行输入 S0、S1—控制端 1 D0D1 D2 D3—并行输入

《数字电子技术》多媒体课件

山东轻工业学院

4、扩展:两片74LS194A扩展一片8位双向移位寄存器

《数字电子技术》多媒体课件

山东轻工业学院

例6.3.1的电路 (P276) 74LS194功能 S1S0=00,保持 S1S0=01,右移 S1S0=10,左移 S1S0=11,并入

(5)状态转换图

《数字电子技术》多媒体课件

山东轻工业学院

小结

1、时序逻辑电路的特点、组成、分类及描述方法; 2、同步时序逻辑电路的分析方法; 课堂讨论: 6.1,6.4

《数字电子技术》多媒体课件

山东轻工业学院

6.3 若干常用的时序逻辑电路

寄存器和移位寄存器 时序 逻辑电路 计数器 顺序脉冲发生器 序列信号发生器

移位寄存器不仅具有存储功能,且还有移位功能。 可实现串、并行数据转换,数值运算以及数据处理。 所谓“移位”,就是将寄存器所存各位数据,在每个移 位脉冲的作用下,向左或向右移动一位。

2、类型: 根据移位方向,分成三种:

左移 寄存器 (a) 右移 寄存器 (b) 双向 移位 寄存器 (c)

《数字电子技术》多媒体课件

学习要求 :

* *

自学掌握

1. 掌握寄存器和移位寄存器的概念并会使用; 2. 掌握计数器概念,熟练掌握中规模集成计数器74161 和74160的功能,熟练掌握用160及161设计任意进制计 数器的方法。

《数字电子技术》多媒体课件

山东轻工业学院

6.3.1寄存器和移位寄存器

一、寄存器

寄存器是计算机的主要部件之一, 它用来暂时存放数据或指令。

《数字电子技术基础》2版习题答案 6章习题解答

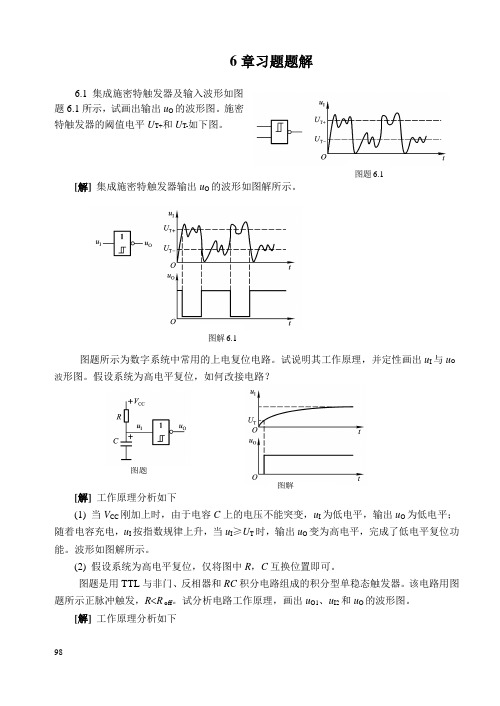

6章习题题解6.1 集成施密特触发器及输入波形如图题6.1所示,试画出输出u O的波形图。

施密特触发器的阈值电平U T+和U T-如下图。

图题6.1 [解]集成施密特触发器输出u O的波形如图解所示。

图解6.1图题所示为数字系统中常用的上电复位电路。

试说明其工作原理,并定性画出u I与u O 波形图。

假设系统为高电平复位,如何改接电路?图题图解[解] 工作原理分析如下(1) 当V CC刚加上时,由于电容C上的电压不能突变,u I为低电平,输出u O为低电平;随着电容充电,u I按指数规律上升,当u I≥U T时,输出u O变为高电平,完成了低电平复位功能。

波形如图解所示。

(2) 假设系统为高电平复位,仅将图中R,C互换位置即可。

图题是用TTL与非门、反相器和RC积分电路组成的积分型单稳态触发器。

该电路用图题所示正脉冲触发,R R off。

试分析电路工作原理,画出u O1、u I2和u O的波形图。

[解]工作原理分析如下9899触发信号未到来时,u I 为低电平,输出u O 为高电平;正触发脉冲到来时,u O1翻为低电平,此时由于u I2仍为高电平,输出u O 为高电平不变,电容通过R 放电,当u I2下降到U T 时〔u I 仍为高电平〕,输出u O 翻为高电平,暂稳态过程结束。

u O1、u I2和u O 的波形见图解。

6.4 集成单稳态触发器74121组成的延时电路如图题6.4所示,要求 (1)计算输出脉宽的调节范围; (2)电位器旁所串电阻有何作用?[解] (1) 输出脉宽:W ext ext W 0.70.7()t R C R R ==+,分别代入R W =0和22k Ω计算,可得t W的调节范围为:W 3.6mS 19mS t ≤≤。

(2) 电阻R 起保护作用。

假设无R ,当电位器调到零时,假设输出由低变高,那么电容C 瞬间相当于短路,V CC 将直接加于内部门电路输出而导致电路损坏。

6.5 集成单稳态触发器74121组成电路如图题6.5所示,要求(1)计算u O1、u O2的输出脉冲宽度;(2)假设u I 如图中所示,试画出输出u O1、u O2的波形图。

数字电子技术基础课-阎石_第五版第五、六章期末复习题

第五章-第六章习题习题一1、由与非门组成的基本SR锁存器,输入端分别为S、R为使锁存器处于“置1”状态,其S、R端应为。

(A)SR=00 (B)SR=01 (C)SR=10 (D)SR=112、有一个T触发器,在T=1 时,加上时钟脉冲,则触发器。

(A)保持原态(B)置0 (C)置1 (D)翻转3、假设JK触发器的现态Q n=0,要求Q n+1=0,则应使。

(A)J=×,K=0 (B)J=0,K=×(C)J=1,K=×(D)J=K=1 4、电路如图5.1所示。

实现Q n +1 = Q n的电路是。

(A)(B)(C)(D)图5.15、米里型时序逻辑电路的输出是。

(A)只与输入有关(B)只与电路当前状态有关(C)与输入和电路当前状态均有关(D)与输入和电路当前状态均无关6、穆尔型时序逻辑电路的输出是。

(A)只与输入有关(B)只与电路当前状态有关(C)与输入和电路当前状态均有关(D)与输入和电路当前状态均无关7、用n个触发器组成计数器,其最大计数模为。

(A)n (B)2n (C)n2(D)2n8、四位移位寄存器,现态为1100,经左移一位后其次态为。

(A)0011 或1011 (B)1000或1001 (C)1011 或1110 (D)0011 或11119、下列电路中,不属于时序逻辑电路的是。

(A)计数器(B)全加器(C)寄存器(D)分频器10、一个5 位的二进制加计数器,由00000 状态开始,经过75个时钟脉冲后,此计数器的状态为:(A)01011 (B)01100 (C)01010 (D)00111 11、图5.2所示为某时序电路的时序图,由此可知该时序电路具有的功能。

(A)十进制计数器(B)九进制计数器(C)四进制计数器(D)八进制计数器图5.2习题二5-1填空题(1)组合逻辑电路任何时刻的输出信号,与该时刻的输入信号;与电路原来所处的状态;时序逻辑电路任何时刻的输出信号,与该时刻的输入信号;与信号作用前电路原来所处的状态。

数字电子技术第6章自测练习及习题解答

自测练习(6.1)1.4位寄存器需要()个触发器组成。

2.图6-1中,在CP()时刻,输入数据被存储在寄存器中,其存储时间为()。

3.在图6-4中,右移操作表示数据从()(FF0,FF3)移向(FF0,FF3)。

SHIFT LOAD为()电平时,寄存器执行并行数据输入操作;4.在图6-7中,当/5.74LS194的5种工作模式分别为()。

6.74LS194中,清零操作为()(同步,异步)方式,它与控制信号S1、S1()(有关,无关)。

7.74LS194中,需要()个脉冲可并行输入4位数据。

8.74LS194使用()(上边沿,下边沿)触发。

9.为了将一个字节数据串行移位到移位寄存器中,必须要()个时钟脉冲。

10.一组数据10110101串行移位(首先输入最右边的位)到一个8位并行输出移位寄存器中,其初始状态为11100100,在两个时钟脉冲之后,该寄存器中的数据为:(a)01011110 (b)10110101 (c)01111001 (d)001011011.42.上升沿,1个CP周期3.FF0,FF34.低5.异步清零,右移,左移,保持,并行置数6.异步,无关7.18.上边沿9.810.(c)01111001自测练习(6.2)1.为了构成64进制计数器,需要()个触发器。

2.2n进制计数器也称为()位二进制计数器。

3.1位二进制计数器的电路为()。

4.使用4个触发器进行级联而构成二进制计数器时,可以对从0到()的二进制数进行计数。

5.如题5图中,()为4进制加法计数器;()为4进制减法计数器。

Q0 Array Q1CP题5图(a )题5图(b )6.一个模7的计数器有( )个计数状态,它所需要的最小触发器个数为( )。

7.计数器的模是( )。

(a )触发器的个数(b )计数状态的最大可能个数(b )实际计数状态的个数 8.4位二进制计数器的最大模是( )。

(a )16 (b )32 (c )4 (d )89.模13计数器的开始计数状态为0000,则它的最后计数状态是( )。

数字电路第6章习题答案

6.2 试作出101序列检测器得状态图,该同步电路由一根输入线X ,一根输出线Z ,对应与输入序列的101的最后一个“1”,输出Z=1。

其余情况下输出为“0”。

(1) 101序列可以重叠,例如:X :010101101 Z :000101001 (2) 101序列不可以重叠,如:X :010******* Z :0001000010 解:1)S 0:起始状态,或收到101序列后重新开始检测。

S 1:收到序列起始位“1”。

S 2:收到序列前2位“10”。

10101…X/Z0/01/0X/Z11…100…2)10101…X/Z0/0X/Z11…100…6.3对下列原始状态表进行化简:(a)解:1)列隐含表:A B CDC B ×A B CD C B ×AD BC ××(a)(b)2)进行关联比较 所有的等价类为:AD ,BC 。

最大等价类为:AD ,BC ,重新命名为a,b 。

3)列最小化状态表为:a/1b/0bb/0a/0aX=1X=0N(t)/Z(t)S(t)(b)N (t )/Z (t )S (t )X=0 X=1A B/0 H/0B E/0 C/1C D/0 F/0D G/0 A/1E A/0 H/0F E/1 B/1G C/0 F/0H G/1 D/1解:1)画隐含表:2)进行关联比较:AC,BD,EG ,HF,之间互为等价隐含条件,所以分别等价。

重新命名为: a, b, e, h 3)列最小化状态表:N (t )/Z (t ) S (t )X=0 X=1a b/0 h/0b e/0 a/1 e a/0 h/0 h e/1 b/1试分析题图6.6电路,画出状态转移图并说明有无自启动性。

解:激励方程:J1=K1=1;J2=Q1n⎯Q3n,K2=Q1nJ2=Q1n Q2n,K2=Q1n状态方程:Q1n+1=⎯Q1n·CP↓Q2n+1=[Q1n⎯Q3n⎯Q2n+⎯Q1n Q2n]·CP↓Q3n+1=[Q1n Q2n⎯Q3n+⎯Q1n Q3n]·CP↓状态转移表:序号Q3Q2Q10 1 2 3 4 5 000 001 010 011 100 101偏离状态110Æ111111Æ000状态转移图状态转移图:Q3Q2Q1偏离态能够进入有效循环,因此该电路具有自启动性。

数电第六章答案全部

P6-19 解:由状态图作出状态转移表如表解 6-19 所示,由状态转移表可作出各触发器的次态卡 诺图和输出函数卡诺图如图解 6-19 所示。由图解 6-19 求得各触发器的状态方程和输出函 数,最后求得各触发器的激励函数:

n 1 Q2 Q1 Q0 Q 2 ,

Q1n 1 Q 2 Q0 Q1 Q2 Q1 Q0 Q 2 Q1 Q 0 Q 2 Q0 Q1 Q2 Q0 Q1 , Q0n 1 Q 2 Q 0 Q2 Q1 Q0 ,

3. 试用 JK 触发器和 D 触发器分别构成下列电路: (1) 四位二拍接收数据寄存器; (2) 四位单拍接收数据寄存器。 解: (1) 由 JK 触发器构成的四位二拍接收数据寄存器如图解 6-12(a)所示,由 D 触发器构成的四位二拍接收数据寄存器如图解 6-12(b)所示。

(2) 由 JK 触发器构成的四位单拍接收数据寄存器如图解 6-12(c) , (d)所示, 由 D 触发器构成的四位单拍接收数据寄存器如图解 6-12(e)所示。

J 2 Q1 Q0 , K2 1,

J 1 Q 2 Q0 , K 1 Q2 Q0 ,

J0 Q2 K 0 Q2 Q1

Z Q2 Q11 Q 0

20.设计一个时序逻辑电路,该时序电路的工作波形图由图 P6-20 给出。

图 P6-20 解:该时序电路可视为一个三输出的脉冲分配器,工作波形的周期为八拍,可以先用八进 制计数器产生 8 个状态作为组合电路的输入, 然后通过组合电路产生三路输出, 其电路结 构框图如图解 6-20 所示,组合电路的真值表如表解 6-20 所示。 (设计数器的输出为:

S1 为接收到一个 1 的状态;

S 2 为在收到 1 后接收到一个 0 的状态; S 3 为在顺序收到 10 后接收到一个 1 的状态;

数字电子技术 第六章习题答案

第六章 习题解答6.1. 分析题图P6.1所示电路的功能,列出功能表。

解:图P6.1所示电路的功能表如表6.1所示。

将功能表中各变量数值关系的逻辑函数用对应的“卡诺图”如图6.1所示。

RS 具有约束条件RS =0,触发器的逻辑表达式为⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,根据这一逻辑表达式,P6.1逻辑电路具有基本RS 触发器的逻辑功能,约束条件是SR=0。

6.2同步RS 触发器与基本RS 触发器的主要区别是什么?解:同步RS 触发器与基本RS 触发器的主要区别是基本RS 触发器的RS 输入信号不论任何时刻都是有效的,只要RS 输入的状态组合发生变化,输出Q 的状态跟随发生变化;而同步同步RS 触发器的RS 输入信号只要在CP 时钟脉冲信号有效时段内起作用,只有在这一时段内,输出Q 的状态才跟随RS 输入的状态组合变化而发生变化。

1& & 1QR图 P6.1QR S Q nQ n+1功 能 1 1 1 1 0 1 不用 不用 不允许11 0 0 0 1 0 0 01=+n Q 置0 0 0 1 1 0 1 1 1 11=+n Q 置10 00 00 10 1n n Q Q =+1 保持6.3如图P6.3 (a)所示电路的初始状态为Q =1,R 、S 端和CP 端的信号如图P6.3(b )所示,画出该同步RS 触发器相应的Q 和Q 端的波形。

解:根据图P6.3 (a)所示电路结构,其功能为同步RS 触发器,电路的特性方程为:⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,若R=S=1,在CP 时钟脉冲信号为“1”的时段内,触发器的两个输出端的状态均输出“1”,此种情况下,若CP 时钟脉冲信号从“1”状态,跳变为“0”的输入状态,则触发器的两个输出状态为不确定状态。

根据特性方程以及电路的初始状态,作出电路的输出端时序图如图6.3所示。

6.4 主从RS 触发器输入信号的波形如图P6.4(a )、(b )所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Q3Q2 Q1Q0

Q3Q 2Q1Q 0

LD

RCO 74161

ET EP

RD

D3 D2 D1 D 0 CP

1 11

Q

3

Q

2

10

0000 0011

1111 1100

∧

1 计数脉冲

0100 0111 1011 1000

电子与信息工程学院

7

电子教研室

第6章、时序逻辑电路

题6.3 分析图示时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方 程,画出电路的状态转换图,说明电路能否自启动。

此电路工作过程如下: 设0000为初始状态,则D3D2D1D0=0011,LD=0, 这意味着在第一个脉冲作用下,要置数,使 Q3Q2Q1Q0=0011;当Q3Q2Q1Q0=0011时,则LD=1,这 意味着在第二个脉冲作用下,要计数,而置数无 效,使Q3Q2Q1Q0=0100;……就这样逐次分析各个 状态,并画出对应的状态转换图,如图所示。可

时,输出Z=1。当X=1时,按照减1规律从11→10→01→00→11循环变

化。所以该电路是一个可控的四进制计数器,其中Z是进位信号输出

端。

电子与信息工程学院

4

电子教研室

第6章、时序逻辑电路

例2.异步时序逻辑电路分析:分析图示电路。 解:1.驱动方程:

2.各触发器的状态方程:

电子与信息工程学院

5

电子教研室

Q0

=1 ┌ 1J C1 ┌ 1K FF0

X 1

CP

输出方程: Z Q1nQ0n 2.列出状态表如表所示。

X S

0

Q1n

Q0n

Q1n+1

Q0n+1

Z

0

0

0

1

0

0

1

1

0

0

1

0

1

1

0

1

1

0

0

1

1

Q1n+1

Q0n+1

Z

1

1

0

0

0

0

0

1

0

1

0

1

电子与信息工程学院

3

电子教研室

3.画出状态图及波形图如图所示。

《数字电子技术基础》习题课 教学课件

辽宁工业大学

电子与信息工程学院 电子信息工程教研室

第6章、时序逻辑电路

一、本章内容:时序逻辑电路的结构和特点;时序逻辑电路的分 析方法;寄存器的工作原理及应用;同步计数器和异步计数器的工 作原理;集成计数器构成任意进制计数器;时序逻辑电路的设计方 法。

二、本章要求: 1.掌握时序逻辑电路的分析方法和设计方法。 2.熟悉寄存器的工作原理、逻辑功能。 3.了解二进制、十进制计数器的工作原理、逻辑功能。 4.熟悉常用中规模集成计数器的结构特点及逻辑功能,能熟练应 用集成计数器构成任意进制计数器。

状态方程:

Q n1 1

AQ2n

Qn1 2

AQ1nQ2n

A(Q2n

Q1n )

输出方程: Y AQ1Q2

状态转换图,如下图所示。

电路的逻辑功能是:判断A是否连续 输入四个和四个以上“1”信号,是则 Y=1,否则Y=0。

电子与信息工程学院

9

电子教研室

第6章、时序逻辑电路

题6.11 分析图示计数器电路,说明这是多少进制的计数器。

电子与信息工程学院

2

电子教研室

第6章、时序逻辑电路

例1.同步时序电路分析:试分析如下电路的逻辑功能。

解:1.写出各逻辑方程: 驱动方程:J0=K0=1,J1=K1= X Q0n

Q1 Z&

将驱动方程代入JK触发器的特性方程

1J ┌

C1

┌ 1K

得次态方程: Q0n1 Q0n

FF1

Q1n1 (X Q0n )Q1n (X Q0n )Q1n (X Q0n ) Q1n

解 1.驱动方程:J1 K1 Q3

J 2 K 2 Q1 J 3 Q1Q2,K3 Q3

2.状态方程:

Q n1 1

Q3nQ1n

Q3nQ1n

Q3n

Q1n

Q n1 2

Q1n Q2n

Q1nQ2n

Q2n

Q1n

Q3n1 Q3n0 X/Z

CP

0/0

X

00

01

1/0

Q0

0/1 1/0 1/0 0/0

Q1

1/1

11

10

Z

0/0

4.逻辑功能分析

由状态图可以很清楚地看出电路状态转换规律及相应输入、输出关

系:该电路一共有4个状态00、01、10、11。当X=0时,按照加1规律

从00→01→10→11→00循环变化,并每当转换为11状态(最大数)

电子与信息工程学院

6

电子教研室

第6章、时序逻辑电路

例3. 试分析图示电路,画出它的状态图,说明它是几进制计数器。

解:74161是异步清零、同步置数,模16计数器 。其中RD是异步清零端,LD是同步预置数控制端, 两者均是低电平有效,D3、D2、D1、D0是预置数据 输入端,EP和ET是计数使能端,计数时EP、ET均 应置于高电平,RCO是进位输出端,CP是计数脉冲 输入端。EP=ET=1,保证正常计数,RD=1说明清零 无效,D3D2D1D0=Q3Q211,Q1控制LD。

3.画出状态图及波形图如图所示。

4.逻辑功能分析

此电路是一个模5异步计数器。从波形图中表面上看 与同步计数器相同,实际上各触发器并不是同时翻转 的。例如来第二个时钟脉冲CP的下降沿,触发器0先 由1→0,然后由于Q0的下跳变使触发器1由0→1;第 四个时钟脉冲CP的下降沿,使触发器0先由1→0,亦 是由于Q0的下降沿使触发器1由1→0。

解 M=1时为六进制计数器,M=0时为八进制计数器。

电子与信息工程学院

12

电子教研室

第6章、时序逻辑电路

题6.14试用4位同步二进制计数器74LS161接成十三进制计数器,标出输入、 输出端。可以附加必要的门电路。

解 可用多种方法实现十三进制计数器,根据功能表,现给出两种典型用法,它们 均为十三进制加法计数器。如图 (a)、(b)所示。

解 电路为七进制计数器。计数顺序是3-9循环。

电子与信息工程学院

10

电子教研室

第6章、时序逻辑电路

题6.12分析图示计数器电路,画出电路的状态转换图,说明这是多少进制的计数器。 解 这是一个十进制计数器。计数顺序是0-9循环。

电子与信息工程学院

11

电子教研室

第6章、时序逻辑电路

题6.13 试分析图示的计数器在M=1和M=0时各为几进制。

3.可得状态转换图

4.电路的逻辑功能:是一 个五进制计数器,计数顺 序是从0到4循环。

电子与信息工程学院

8

电子教研室

第6章、时序逻辑电路

题6.5 试分析图示时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程, 画出电路的状态转换图。A为输入逻辑变量。

解 驱动方程: D1 AQ2 D2 AQ1Q 2