Embedded2-ARM核

ARM嵌入式系统基础教程第二版课后习题答案

第1章嵌入式系统概述(1)举出3个本书中未提到的嵌入式系统的例子。

答:键盘、鼠标、扫描仪。

(2)什么叫嵌入式系统?答:嵌入到对象体系中的专用计算机应用系统。

(3)什么叫嵌入式处理器?嵌入式处理器分为哪几类?答:嵌入式处理器是为完成特殊的应用而设计的特殊目的的处理器。

分为3类:1.注重尺寸、能耗和价格;2.关注性能;3.关注全部4个需求——性能、尺寸、能耗和价格。

(4)什么是嵌入式操作系统?为何要使用嵌入式操作系统?答:嵌入式操作系统是操作系统的一种类型,是在传统操作系统的基础上加入符合嵌入式系统要求的元素发展而来的。

原因:1.提高了系统的可靠性;2.提高了开发效率,缩短了开发周期。

3.充分发挥了32位CPU的多任务潜力。

第2章 ARM7体系结构1.基础知识(1)ARM7TDMI中的T、D、M、I的含义是什么?答:T:高密度16位Thumb指令集扩展;D:支持片上调试;M:64位乘法指令;I:Embedded ICE硬件仿真功能模块。

(2)ARM7TDMI采用几级流水线?使用何种存储器编址方式?答:3级;冯·诺依曼结构。

(3)ARM处理器模式和ARM处理器状态有何区别?答:ARM处理器模式体现在不同寄存器的使用上;ARM处理器状态体现在不同指令的使用上。

(4)分别列举ARM的处理器模式和状态?答:ARM的处理器模式:用户模式、系统模式、管理模式、中止模式、未定义模式、中断模式、快速模式;ARM的处理器状态:ARM状态、Thumb状态。

(5)PC和LR分别使用哪个寄存器?答:PC:R15;LR:R14。

(6)R13寄存器的通用功能是什么?答:堆栈指针SP。

(7)CPSR寄存器中哪些位用来定义处理器状态?答:位31~28:N、Z、C、V,条件代码标志位;27~8:保留位;7~0:I、F、T、M4~0,控制标志位。

(8)描述一下如何禁止IRQ和FIQ的中断。

答:当控制位I置位时,IRQ中断被禁止,否则允许IRQ中断使能;当控制位F置位时,FIQ 中断被禁止,否则允许FIQ中断使能。

ARM处理器内核介绍

52v07 ARM普通处理器内核

TM

23

23

2.6 ARM片上总线

AMBA-Advanced Microcontroller Bus Architecture(先进 的微控制器总线体系结构)

AMBA总线定义3种规范

TM

测试芯片 ARM10200E

2

2

IP核、软核、硬核、固核

IP(Intellectual Property)就是常说的知识产权。IP定义为 用于ASIC、ASSP和PLD等当中,并且是预先设计好的电路模块。

IP核模块有行为(Behavior)、结构(Structure)和物理( Physical)三级不同程度的设计,对应描述功能行为的不同分 为三类,即软核(Soft IP Core)、完成结构描述的固核 ( Firm IP Core)和基于物理描述并经过工艺验证的硬核( Hard IP Core)。

52v07 ARM普通处理器内核

TM

18

18

ARM9TDMI 数据通道 (2)

结果 DINFWD

MU 逻辑

B 寄存器 Bank Imm BDATA 移位器

A

乘法器

ALU

PSR

ADATA

锁存

锁存

MU逻辑单元包含有:多路复用器,乘法器和桶形移位器

52v07 ARM普通处理器内核

TM

19

19

ARM9TDMI流水线的变化

52v07 ARM普通处理器内核

TM

16

16

ARM9TDMI

iarforarm怎么安装?IARforARM8.22破解版安装激活图文详细教程

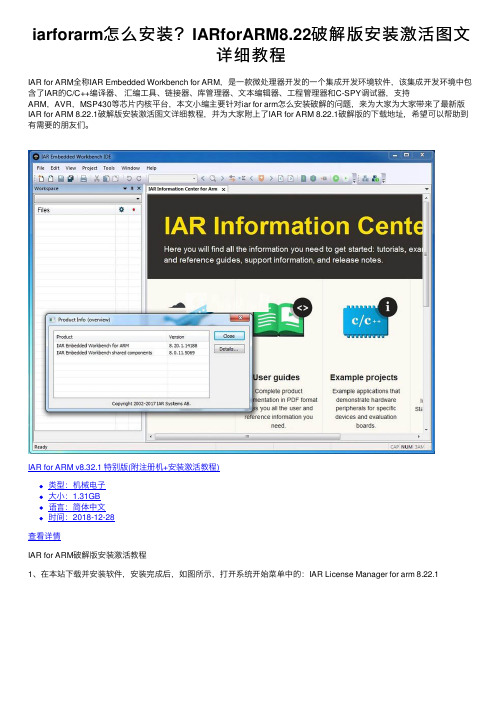

iarforarm怎么安装?IARforARM8.22破解版安装激活图⽂详细教程IAR for ARM全称IAR Embedded Workbench for ARM,是⼀款微处理器开发的⼀个集成开发环境软件,该集成开发环境中包含了IAR的C/C++编译器、汇编⼯具、链接器、库管理器、⽂本编辑器、⼯程管理器和C-SPY调试器,⽀持ARM,AVR,MSP430等芯⽚内核平台,本⽂⼩编主要针对iar for arm怎么安装破解的问题,来为⼤家为⼤家带来了最新版IAR for ARM 8.22.1破解版安装激活图⽂详细教程,并为⼤家附上了IAR for ARM 8.22.1破解版的下载地址,希望可以帮助到有需要的朋友们。

IAR for ARM v8.32.1 特别版(附注册机+安装激活教程)类型:机械电⼦⼤⼩:1.31GB语⾔:简体中⽂时间:2018-12-28查看详情IAR for ARM破解版安装激活教程1、在本站下载并安装软件,安装完成后,如图所⽰,打开系统开始菜单中的:IAR License Manager for arm 8.22.12、会弹出如图所⽰的软件注册界⾯,选择第⼀项拥有许可证号码3、在安装包中找到Keygen.rar注册机解压,如图所⽰,得到License Generator.exe注册⽣成⼯具,双击License Generator.exe运⾏选择no,点下⼀步4、点击generate⽣成按钮,⽣成注册码1126-004-558-16125、将⽣成的注册码复制到软件注册界⾯,选择断⽹,(我们整个激活是离线激活,所以⼀定要断⽹)点击下⼀步6、出现如下弹窗,点击是,选择离线激活7、如图所⽰,继续选择第⼀项,离线激活,点下⼀步8、该许可证是否应该锁定在硬件加密狗上,我们选择no,点下⼀步9、如图所⽰,浏览到桌⾯,选择到⽂件ActivationInfo.txt,然后点下⼀步10、会在桌⾯⽣成⼀个ActivationInfo.txt⽂本,如图所⽰11、回到注册机,点browse按钮选择已⽣成在桌⾯的ActivationInfo.txt⽂件:C:\Users\dpg\Desktop\ActivationInfo.txt,12、再点Activate license,⽣成破解⽂件ActivationResponse.txt13、回到软件注册界⾯,点下⼀步14、浏览到刚⽣成的机会⽂件ActivationResponse.txt,点下⼀步15、以上操作完成后,软件已经完美破解l16、运⾏快捷⽅式IAR Embedded Workbench.exe,默认英⽂,点ok17、软件正常运⾏,所有功能都可以免费使⽤了。

ARM架构——精选推荐

ARM架构(过去称作进阶精简指令集机器(Advanced RISC Machine),更早称作Acorn RISC Machine)是一个32位元精简指令集(RISC)中央处理器(processor)架构,其广泛地使用在许多嵌入式系统(embedded)设计。

由于节能的特点,ARM处理器非常适用于行动通讯领域,符合其主要设计目标为低耗电的特性。

在今日,A R M家族占了所有32位元嵌入式处理器75%的比例[1],使它成为占全世界最多数的32位元架构之一。

A R M处理器可以在很多消费性电子产品上看到,从可携式装置(P D A、移动电话、多媒体播放器、掌上型电玩,和计算机)到电脑周边设备(硬盘、桌上型路由器)甚至在导弹的弹载计算机等军用设施中都有他的存在。

在此家族中衍伸的重要产品还包括M a r v e l l的X S c a l e架构和德州仪器的O M A P系列。

编辑本段历史A R M的设计是A c o r n电脑公司(A c o r n C o m p u t e r s L t d)于1983年开始的开发计划。

这个团队由R o g e r W i l s o n和S t e v e F u r b e r带领,着手开发一种新架构,类似进阶的M O S T e c h n o l o g y 6502处理器。

A c o r n有一大堆建构在6502架构上的电脑,因此能设计出一颗类似的芯片即意味着对公司有很大的优势。

团队在1985年时开发出A R M1S a m p l e版,而首颗"真正"的产能型A R M2于次年量产。

A R M2具有32位的数据总线、26位的寻址空间,并提供64M b y t e的寻址范围与16个32-b i t的暂存器。

这些暂存器其中有一颗做为(w o r d大小)程式计数器,其前面6b i t s和后面2b i t s用来保存处理器状态标记(P r o c e s s o r S t a t u s F l a g s)。

基于Qt/Embedded的ARM—Linux应用程序研究

3 ・ 3

维普资讯

基于 Q E bde A M—I u m edd的 R . x应用程序研 究 i n

可以对源 码 进 行 修 改 和 剪 裁 以适 应 自己特 定 的应 用 , 以 出现 了很 多 种 面 向嵌 入 式 应 用 的 Lnx 有 所 iu, R]nxU Lnx 还 有 目前 可 以支持 面 向 A M 核 的 1ju , C i , L u R Lnx操 作 系 统 A i x A M i x支 持 多种 iu M R Ln 。 R Ln u u

A M 芯片, R 带有大部分通用设备的驱动, 比如键盘、

鼠标 、S U B接 口等 , 开发者 只需专注 于开发 自己系统 特定 驱 动 , 即可使 整 个 系统正 常运行 , 大缩短 了开 大 发周 期 , 降低 了开发 的复杂度 。 3 Q/ m edd进 行应 用开发 的流 程 tE bde

线和 串口线相连, 最终在 主机上把应用程序编译成 A M格 式的二进制文件通过 网线或 串口传输到 目 R

标板 上运行 。 主机 与 目标 板 的连接 图如 图 2所 示。 开发环境 构 建 所 需 软 件 开 发 包 有 :nx内核 , lu i

l u 一2 4 2 一e s i x . . 1 l 一1—4—3 t ; R 交 叉 编 译 n m . rA a M

收 稿 日期 "06—0 —2 20 6 5

可从 网上下载。把这些软件包解压安装 , 在安装 时,

应配置两套开发环境, 一种是 A M 体系的, R 另一种 是 X 6体 系的 , 通过设 置 cngr 的参数 完成 。 8 这 of u i e后

作者简介 : 李佳林(90 6一)男 , 18 . , 在读硕士研究生 ; 主要研究方 向: 微机控制技术与应用。

基于嵌入式ARM的SD卡的读写要点

摘要SD卡(Secure Digital Memory Card)中文翻译为安全数码卡,是一种基于半导体快闪记忆器的新一代记忆设备,它被广泛地于便携式装置上使用,例如数码相机、个人数码助理(PDA)和多媒体播放器等。

本实训的作品是利用基于ARM Cotex-M3内核的嵌入式处理器STM32自带的SDIO硬件接口来驱动SD卡,并结合文件系统 FATFS R0.07C来完成一个基于嵌入式ARM的SD卡读写的作品,现实向SD 卡写入一个txt文件,并读取SD卡的文件目标并通过串口打印到PC机显示。

关键词:嵌入式;ARM;STM32;SD卡;文件系统AbstractSD Card (Secure Digital Memory Card) Chinese translation for Secure Digital Card, it is a kind of based on semiconductor flash Memory of a new generation of Memory device, it is widely used in portable devices, such as Digital cameras, personal Digital assistant (PDA) and multimedia player, etc. This training work is based on ARM Cotex - M3 kernel embedded processor STM32 own SDIO hardware interface to drive the SD card, and combined with the file system FATFS R0.07 C to complete a based on embedded ARM of the SD card, speaking, reading and writing work, reality to SD card to a TXT file, and read SD card file goals and through the serial port print to PC display.Key words:embedded;ARM;STM32; SD Card; File system目录1 前言 (1)1.1ARM应用背景 (1)1.2研究内容 (2)1.3研究成果 (3)2 STM32处理器概述 (3)2.1STM32简介 (3)2.1.1 STM32F103VET6的参数 (4)2.2内部资源 (6)2.3C ORTEX-M3内核简介 (6)2.4STM32SDIO简介 (7)2.4.1 SDIO简介 (7)2.4.2 SDIO功能特性 (8)3 SDIO的原理及实现方法 (8)3.1原理 (9)3.2SDIO适配器 (10)3.3SDIO卡识别过程 (11)3.4SDIO写数据块 (12)3.5SDIO读数据块 (13)4 FATFS文件系统 (13)4.1F A T FS文件系统简介 (13)4.2F A T FS文件系统移植 (14)4.2.1移植前工作 (14)4.2.2开始移植 (14)5 测试及结果 (15)5.1JTAG仿真器介绍 (16)5.2现象及结果 (16)6 结论 (18)致谢 (19)参考文献 (20)1 前言1.1 ARM应用背景如今,学习一种处理器的就有许多ARM内核的处理器可供使用,现在社会已步入嵌入式学习阶段。

Qt_Embedded触摸屏的智能家居无线传输系统设计

Qt/Embedded触摸屏的智能家居无线传输系统设计①李新春徐英华(辽宁工程技术大学电子信息与工程学院辽宁葫芦岛 125105)摘要:设计了一个基于Qt/Embedded触摸屏的智能家居控制平台,并通过zigbee组网的方式,实现家居的智能化控制。

首先,智能家居的界面用Qt/Embedded设计,然后,界面被移植到以ARM9为微处理器的控制平台上,并实现界面的触摸屏功能;最后,通过串口驱动将设计的具有触摸屏功能的界面与zigbee组网的协议连接起来,实现对智能家居控制的无线传输。

关键词:Qt/Embedded;ARM;zigbee;触摸屏;GUIDesign of Intelligence Home Wireless Transmission System Based on Qt / Embedded of Touch Screen LI Xin-Chun, XU Ying-Hua (Department of Electronic Information and Engineering, Liaoning EngineeringTechnology University, Huludao 125105, China)Abstract:This paper designs the intelligence home control platform based on Qt/Embedded of touch screen, realizing the intelligence control of home by way of zigbee networking. Interface designer of intelligence home usesQt/Embedded. At the same time, interface will be transplanted to the control platform for microprocessor ofARM9, and achieve the touch-screen features of interface. Finally, the paper connects the interface of atouch-screen features with zigbee networking through the serial port driver, to realize wireless transmissionabout the intelligence home.Keywords: Qt/Embedded; ARM; zigbee; touch screen; GUI1 引言随着生活质量的提高,家居智能化已经成为当今时代的一种主流。

arm体系结构过程调用标准

ARM体系结构支持多种过程调用标准(Calling Convention),这些调用标准定义了函数如何传递参数、如何管理和清理栈、以及如何返回结果等。

以下是一些常见的ARM过程调用标准:1. ARM Procedure Call Standard (AAPCS):AAPCS是ARM架构的官方过程调用标准,它被广泛用于ARM和Thumb 指令集。

参数传递:根据参数的类型和数量,参数可能通过寄存器或堆栈传递。

通常,前四个整数或指针参数通过R0-R3寄存器传递,第六个和第七个浮点参数通过S0-S1寄存器传递。

返回值:对于小的整数和指针,返回值通常在R0寄存器中;对于较大的整数和浮点数,可能需要使用多个寄存器(如R0-R1或S0-S1)。

调用者负责清理堆栈上的参数。

函数的返回地址保存在链接寄存器LR中。

2. ARM EABI (Embedded Application Binary Interface):ARM EABI是针对嵌入式系统的应用程序二进制接口,它包括了一套过程调用规则。

参数传递和返回值处理与AAPCS相似,但可能有一些特定于嵌入式环境的优化和差异。

3. ARM Linux Calling Convention:在Linux环境下,ARM遵循AAPCS,但在某些情况下可能会有一些特定的调整以适应Linux内核和用户空间程序的需求。

例如,在内核模式下,可能会使用不同的寄存器来保存上下文信息。

4. Thumb Procedure Call Standard (THUMB-PCS):THUMB-PCS是针对Thumb指令集的过程调用标准,它与AAPCS类似,但在某些细节上有所不同,以适应Thumb指令集的特点。

参数传递和返回值处理方式与AAPCS基本一致。

不同编译器和操作系统可能会对这些标准进行一些微调或扩展,所以在实际使用时,应参考相应的编译器文档和系统规范来确保代码的正确性和兼容性。

Arm简答题

Arm简答题9.ARM920T体系结构支持哪两种方法存储字数据?答:大端模式和小端模式,大端模式高地址存的是数据的低位,低地址存存的是数据的高位。

小端模式高地址存的是数据的高位,6.哈佛体系结构和冯诺依曼体系结构有何不同。

答:哈佛体系结构有两套地址总线和数据总线是分开的,冯诺依曼体系结构是复用的。

2.ARM9采用了几级流水线工作方式,简要说明。

答:五级流水线工作方式,1.取指2.指令译码3.执行4.数据存储访问5.写寄存器1.什么是嵌入式系统?其特点有些什么?答:嵌入式系统是“以应用为中心、以计算机技术为基础、软件硬件可裁剪、功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

”特点:1)是专用的计算机系统,用于特定的任务;2)资源较少,可以裁减;3) 功耗低,体积小,集成度高,成本低; 4)使用实时操作系统;5) 可靠性要求更高,具有系统测试和可靠性评估体系;6)运行环境差异大7)大部分程序固化在ROM中;8) 较长的生命周期;9)嵌入式微处理器通常包含专用调试电路3、什么叫嵌入式处理器?嵌入式处理器分为哪几类?嵌入式处理器是为完成特殊的应用而设计的特殊目的的处理器。

嵌入式微处理器(Embedded Microprocessor Unit, EMPU)嵌入式微控制器(Microcontroller Unit, MCU)嵌入式DSP 处理器(Embedded Digital Signal Processor, EDSP)嵌入式片上系统(System On Chip)4、什么是嵌入式操作系统?为何要使用嵌入式操作系统?是一段在嵌入式系统启动后首先执行的背景程序,首先,嵌入式实时操作系统提高了系统的可靠性。

其次,提高了开发效率,缩短了开发周期。

再次,嵌入式实时操作系统充分发挥了32 位CPU 的多任务潜力。

4、分别列举ARM的处理器模式和状态。

状态:ARM 状态32 位,这种状态下执行的是字方式的ARM 指令Thumb 状态16 位,这种状态下执行半字方式的Thumb 指令模式:用户模式、快中断模式、中断模式、管理模式、中止模式、未定义模式和系统模式。

嵌入式系统——精选推荐

嵌⼊式系统第⼀章⼀、嵌⼊式系统的定义:从技术⾓度定义:以应⽤为中⼼,以计算机技术为基础,软硬件可裁剪,适应应⽤系统对功能、可靠性、成本、体积、功耗等严格要求的专⽤计算机系统,是将应⽤程序、操作系统和计算机硬件集成在⼀起的系统。

⼆、常见的嵌⼊式操作系统:1.WindowsEmbedded2.VxWorks3.µC/OS4.QNX5.嵌⼊式Linux6.安卓系统三、嵌⼊式系统的特点:专⽤型强体积⼩型化实时性好可裁剪性好可靠性⾼功耗低不可垄断性四、嵌⼊式处理器有两个体系结构,特点,优缺点冯诺依曼体系结构和哈弗体系结构冯诺依曼:程序和数据共享⼀个存储空间;程序指令存储地址和数据存储地址指向⼀个存储器的不同物理位置;采⽤单⼀的地址及数据总线;程序指令和数据宽度相同。

处理器在执⾏指令时,必须从存储器中取出指令解码,再取操作数执⾏运算,在⾼速运算的时候,容易在传输通道上出现瓶颈效应。

哈弗:程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独⽴的存储器,每个存储器独⽴编址、独⽴访问。

与两个存储器相对应的是系统中的4套总线:程序的数据总线和地址总线,数据的数据总线和地址总线。

这种分离的程序总线和数据总线可允许在⼀个机器周期内同时获取指令字和操作数,从⽽提⾼了执⾏速度,⼜由于程序和数据存储器在两个分开的物理空间中,因⽽取值和执⾏能够完全重叠,提⾼了运算速度。

五、嵌⼊式微处理器的分类(P10)嵌⼊式微处理器根据功能、结构、性能运算特点和使⽤⽅法等多⽅⾯的综合因素可以粗略分成嵌⼊式微控制器(MCU)、嵌⼊式微处理器(MPU)、数字信号处理器(DSP))、CPLD/FPGA、⽚上系统(SOC)等5类。

SOC往往是在FPGA上实现的。

六、嵌⼊式微处理器如何选型(P13)1.技术指标2.熟悉原则3.成本原则4.⽀持⼯具原则5,整体原则第⼆章⼀、RISC(精简指令集)特点:1.⼤的、统⼀的寄存器⽂件2.装载/保存结构,数据处理操作只针对寄存器的内容,⽽不是直接对存储器进⾏操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2 ARM技术概述(续)ARM技术概述ARM体系结构ARM技术基础ARM核介绍L.J.Zhu, Automation Dept., SJTUARM系列内核ARM处理器内核及内核扩展 ARM7系列核ARM9和ARM9E系列核ARM10E系列核ARM11处理器核ARM Cortex TM系列其他ARM核L.J.Zhu, Automation Dept., SJTUARM处理器内核归类固化宏单元(硬核)Licensed at layout levelDelivered as GDSⅡCannot be changed by licensee如:ARM710T,ARM920T等可合成内核(软核)Delivered as RTLConfigured and sysnthesized by licenseeFunctionality cannot be changed如:ARM7TDMI-S,ARM926EJ-S等L.J.Zhu, Automation Dept., SJTUARM处理器内核简称ARM核,目前ARM公司共推出了七个ARM版本(V1~V7),其变化主要体现在内核结构的变化和内核的扩展处理器核=ALU+CU+R+内部总线 ALU:算术逻辑部件(Arithmetic Logic Unit) CU:控制部件(Control Unit)R:寄存器组(Registers)内部总线L.J.Zhu, Automation Dept., SJTU冯·诺依曼3级流水线的ARM核ALUCURegisters内部总线L.J.Zhu, Automation Dept., SJTU哈佛5级流水线的ARM核增加I-cache 和D-cache,取指与存取数据分开增加数据写回通路和寄存器FetchDecodeExecuteMemoryWriteL.J.Zhu, Automation Dept., SJTU内核扩展内核的扩展主要是增加ARM核外围的组件,以改善ARM性能主要有3种硬件扩展:Cache和紧耦合存储器TCM存储管理协处理器接口L.J.Zhu, Automation Dept., SJTU带Cache的冯·诺依曼结构ARM核 数据、指令放在同一Cache,只有一套地址、数据总线(如ARM710T)L.J.Zhu, Automation Dept., SJTUL.J.Zhu, Automation Dept., SJTU 紧耦合存储器(TCM)位于存储器物理地址的映射中,是一段始终有效的连续快速SRAM区域,比Cache有较高的稳定性数据、指令放在不同TCM ,有两套地址、数据总线(如ARM920T )带TCM 的哈佛结构ARM 核带TCM和Cache的哈佛结构ARM核 数据、指令放在不同Cache和TCM,有两套地址、数据总线。

带TCM,取指、数据操作稳定性高(如ARM946E-S)L.J.Zhu, Automation Dept., SJTU内核扩展—存储管理ARM内核的3种不同存储管理类型 无存储管理、无存储保护有限的存储保护MPU对每个存储区域提供专门的访问权限,但没有复杂的存储映射全面保护的存储管理单元MMUMMU提供精细的存储控制,包括:虚拟地址与物理地址的转换及访问权限控制L.J.Zhu, Automation Dept., SJTU内核扩展—协处理器协处理器可以附属于ARM内核,通过扩展指令集和提供配置寄存器来扩展内核功能例如,ARM内核使用协处理器CP15的寄存器来控制Cache、TCM和存储管理 ARM体系支持16个协处理器和三类ARM协处理器指令L.J.Zhu, Automation Dept., SJTUARM系列内核ARM处理器内核及归类 ARM7系列核ARM9和ARM9E系列核 ARM10E系列核ARM11处理器核ARM Cortex TM系列其他ARM核L.J.Zhu, Automation Dept., SJTUL.J.Zhu, Automation Dept., SJTUARM7系列处理器性能特征无无有有MMU无8KARM7EJ有有有有无无无ARM720T 无无有有无无无ARM7TDMI-S 无无有有无无无ARM7TDMI JazelleDSP Thumb AHB 总线接口存储器管理紧密耦合存储器Cache 大小(指令/数据)ARM7系列核ARM7TDMI核ARM V4T 冯.诺依曼架构3级流水线结构,CPI约1.966MHz,极低的功耗T-支持16位Thumb指令集D-支持片上调试M-支持64位乘法I-带Embedded ICE-RT逻辑,支持片上断点和调试点主要应用领域:工业控制、Internet 设备、网络和调制解调器设备、移动电话等L.J.Zhu, Automation Dept., SJTUL.J.Zhu, Automation Dept., SJTUARM7TDMI 方框图ARM7TDMI处理器内核L.J.Zhu, Automation Dept., SJTUARM7TDMI 核外部接口ARM7TDMI内核数据总线地址总线控制信号时钟与定时中断协处理器接口存储器接口总线控制调试接口电源存储器接口ARM7TDMI采用冯.诺依曼架构,没有专门的MMU,采用直接地址方式访问存储器存储器接口信号包括4大类时钟和时钟控制信号:MCLK, ECLK, nWAIT, nRESET等地址类信号:A[31:0], nRW等存储器请求信号:nMREQ和SEQ数据时序信号:D[31:0], DIN[31:0], DOUT[31:0]等L.J.Zhu, Automation Dept., SJTU存储器总线周期类型ARM7TDMI可执行4 种类型存储器总线周期 非顺序周期(N周期)内核请求一个数据传送地址与前一周期地址不相关 顺序周期(S周期)内核请求一个数据传送地址与前一周期地址相同或者比前一周期地址大一个字或半个字内部周期(I周期)内核执行内部功能,不访问存储器协处理器寄存器传送周期(C周期)内核使用总线与协处理器通信,但不请求存储器动作L.J.Zhu, Automation Dept., SJTUL.J.Zhu, Automation Dept., SJTU存储器总线周期类型ARM7TDMI 存储器总线周期类型由存储器请求信号决定协处理器寄存器传送周期(C 周期)11内部周期(I 周期)01顺序周期(S 周期)10非顺序周期(N 周期)00总线周期类型SEQ nMREQ调试结构调试主机协议转换器(硬件仿真器)目标板主机运行ARM开发调试工具软件(一般为PC机)协议转换器接收主机命令并与目标板通信(最常用JTAG仿真器)系统板,包括ARM主处理器逻辑和调试逻辑(EmbeddedICE、TAP控制器、扫描链等)L.J.Zhu, Automation Dept., SJTUJTAG接口JTAG(Joint Test Action Group)IEEE 1149.1标准将集成电路固定在PCB上,通过芯片上的JTAG 边界扫描测试直接控制ARM的内部总线、I/O口等信息JTAG的边界扫描测试(BST)规范规定了一个测试访问口TAP (Test Access Port)和边界扫描结构,提供了访问和控制芯片内部仿真(ICE)模块的方法L.J.Zhu, Automation Dept., SJTUJTAG标准工作原理边界扫描基本思想在靠近芯片的输入输出管脚上增加一个移位寄存器单元,称边界扫描寄存器,将这些边界扫描寄存器单元相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain) 当芯片处于调试状态时,边界扫描寄存器将芯片和外围的输入输出隔离,实现对芯片输入输出信号的观察和控制在正常运行状态下,边界扫描寄存器对芯片透明L.J.Zhu, Automation Dept., SJTUJTAG标准工作原理TAP(TEST ACCESS PORT)JTAG测试访问端口,通过TAP 可以访问芯片提供的所有数据寄存器和指令寄存器对TAP 的控制通过TAP控制器完成包括5个信号接口:TCK(Test Clock Input):测试时钟TMS(Test Mode Selection Input):控制TAP状态机转换(TAP控制器共有16 种状态)TDI(Test Data Input):JTAG指令和数据的输入线TDO(Test Data Output):JTAG指令和数据输出线n TRST(Test Reset Input):测试复位L.J.Zhu, Automation Dept., SJTUL.J.Zhu, Automation Dept., SJTUARM7TDMI 调试接口ARM7TDMI 实现典型的ARM 调试结构通过JTAG接口控制和操作扫描链含一组寄存器和比较器,用以产生调试异常、设置断点和观察点长113 位, 可以访问内核的外围电路, 包括数据总线长33 位,扫描链0 的子集.可以更快的插入指令或数据到内核长38 位,专门用来访问EmbeddedICE 内部寄存器协处理器接口时钟和时钟控制信号CLK、CLKEN、nRESET流水线跟随信号CPnI:ARM通知协处理器当前为协处理器指令 CPA和CPB:协处理器指示是否接受这一指令OPC:指示存储器访问是取指令还是取数据,协处理器流水线跟随器使用它来跟踪ARM指令的执行握手信号WDATA[31:0]、RDATA[31:0]等L.J.Zhu, Automation Dept., SJTUARM系列内核ARM处理器内核及归类 ARM7系列核ARM9和ARM9E系列核 ARM10E系列核ARM11处理器核ARM Cortex TM系列其他ARM核L.J.Zhu, Automation Dept., SJTUL.J.Zhu, Automation Dept., SJTUARM9系列处理器性能特征无无有有MMU无4K/4KARM940T无无有有MMU 无8K/8K ARM922T 无无有有MMU 无16K/16K ARM920T JazelleDSP Thumb AHB 总线接口存储器管理紧密耦合存储器Cache 大小(指令/数据)ARM9系列核ARM9处理器系列特点ARM V4T 哈佛架构,支持指令快存I-Cache和数据快存D-Cache5级流水线结构,CPI约1.5,200MHz支持32 位ARM 指令集和16 位Thumb 指令集支持32 位的高速AMBA总线接口全性能的MMU,支持Windows CE、Linux等多种主流嵌入式操作系统主要应用领域:无线设备、仪器仪表、机顶盒、高端打印机、数字照相机和数字摄像机等L.J.Zhu, Automation Dept., SJTUARM920T内部结构ARM920T的AMBA总线L.J.Zhu, Automation Dept., SJTUARM9E 系列处理器性能特征无有有有无有无ARM966E-S无有有有MMU 有4~1MB/4~1MB ARM946E-S 有有有双AHB MMU 有4~128K/4~128K ARM926EJ-SJazelleDSP Thumb AHB 总线接口存储器管理紧密耦合存储器Cache 大小(指令/数据)ARM9E 系列核ARM9E处理器系列特点ARM V5 哈佛架构,支持指令Cache和数据Cache 5 级整数流水线,指令执行效率更高主频最高可达300MIPS支持DSP 指令集,适合需高速数字信号处理的场合 支持32 位ARM 指令集和16 位Thumb 指令集支持32 位的高速AMBA总线接口支持VFP9 浮点处理协处理器全性能的MMU,支持WinCE、Linux等操作系统 主要应用领域:下一代无线设备、数字消费品、成像设备、工业控制、存储设备和网络设备等L.J.Zhu, Automation Dept., SJTUARM系列内核ARM处理器内核及归类 ARM7系列核ARM9和ARM9E系列核 ARM10E系列核ARM11处理器核ARM Cortex TM系列其他ARM核L.J.Zhu, Automation Dept., SJTUL.J.Zhu, Automation Dept., SJTUARM10E 系列处理器性能特征有有有双AHBMMU+MMU有可变ARM1026EJ-S无有有双AHB MMU 无16K/16K ARM1022E 无有有双AHB MMU 无32K/32K ARM1020E JazelleDSP Thumb AHB 总线接口存储器管理紧密耦合存储器Cache 大小(指令/数据)ARM10E 系列核ARM10E处理器系列特点ARM V5TE架构,支持指令Cache和数据Cache6级流水线结构,指令执行效率更高,CPI约1.3主频最高可达400MIPS支持DSP 指令集,适合需高速数字信号处理的场合 支持32 位ARM 指令集和16 位Thumb 指令集支持32 位的高速AMBA总线接口支持VFP10 浮点处理协处理器全性能的MMU,支持WinCE、Linux等操作系统 内嵌并行读/写操作部件,静态转移预测逻辑主要应用领域:下一代无线设备、数字消费品、成像设备、工业控制、通信和信息系统等L.J.Zhu, Automation Dept., SJTUARM系列内核ARM处理器内核及归类 ARM7系列核ARM9和ARM9E系列核 ARM10E系列核ARM11处理器核ARM Cortex TM系列其他ARM核L.J.Zhu, Automation Dept., SJTUL.J.Zhu, Automation Dept., SJTUARM11系列处理器性能特征有有SIMD有有有4个64位AHBMMU有4~64K/ 4~64KARM1136JF-无有有4个64位AHB MMU有4~64K/ 4~64K ARM1136J-S 浮点运算Jazelle DSP AHB 总线接口存储器管理紧密耦合存储器Cache 大小(指令/数据)ARM11系列核ARM11处理器系列特点ARM V6架构多媒体性能、实时性能、非ARM处理器的移植性 8级流水线结构静态和动态转移预测逻辑快速反应中断模式内挂4-64K I-Cache和D-Cache4个主存储器口Jazelle技术支持8-bit的Java字节码L.J.Zhu, Automation Dept., SJTUARM系列内核ARM处理器内核及归类 ARM7系列核ARM9和ARM9E系列核 ARM10E系列核ARM11处理器核ARM Cortex TM系列其他ARM核L.J.Zhu, Automation Dept., SJTUARM Cortex系列ARM CortexARMv7架构,包含三个系列:A系列:用于高性能的“开放应用平台”(越来越接近电脑)——Cortex-A8 R系列:用于高端的带有实时要求的嵌入式系统(快、实时)——Cortex-R4 M系列:用于深度嵌入的、单片机风格的系统(低成本、低功耗、极速中断反应)——Cortex-M3L.J.Zhu, Automation Dept., SJTUCortex-M3内核ARMv7-M 哈佛架构3级流水线+分支预测两种工作模式:线程和处理器两个访问等级:特权级和用户级存储器映射系统,可寻址空间4GB支持非对齐数据访问方式和位带bit-banding技术支持Thumb / Thumb-2用于微控制器,汽车车身系统,工业控制系统和无线网络等对功耗和成本敏感的嵌入式应用领域L.J.Zhu, Automation Dept., SJTUL.J.Zhu, Automation Dept., SJTUARM7TDMI-S 和Cortex-M3比较ARM系列内核ARM处理器内核及归类 ARM7系列核ARM9和ARM9E系列核 ARM10E系列核ARM11处理器核ARM Cortex TM系列其他ARM核L.J.Zhu, Automation Dept., SJTUL.J.Zhu, Automation Dept., SJTU基于ARM 的Intel 处理器无有有N/AMMU无32K/32KXScale无无无N/A MMU 无16K/8K Strong ARM JazelleDSP Thumb AHB 总线接口存储器管理紧密耦合存储器Cache 大小(指令/数据)核StrongARM处理器特点ARM V4 哈佛架构16K指令Cache与16K数据Cache5级流水线结构内核时钟160-200MHz8数据项的写缓冲器改进的高速乘法器低功耗的伪静态操作不支持Thumb指令集,不支持Multi-ICE调试 使用系统控制协处理器,无外部协处理器接口L.J.Zhu, Automation Dept., SJTUIntel XScale处理器特点ARM V5TE体系架构7-8级超级流水线结构带统计转移预测逻辑32K指令和数据Caches,2K的数据Minicache支持16位Thumb指令和DSP扩充完整的32位协处理器接口调试和性能监控内核时钟速度可配置100-733MHz主要领域:超低功率与高性能的组合,适用于广泛的互联网接入设备L.J.Zhu, Automation Dept., SJTU小结ARM体系结构的技术特征和版本的发展演变 Thumb技术的特点、作用和实现ARM处理器的工作模式、寄存器组、异常处理、存储管理机制、流水线技术等ARM调试接口、AMBA总线结构ARM核的特点ARM7TDMI、ARM920T、…L.J.Zhu, Automation Dept., SJTU。