六十进制计数器

六十进制的运算法则

一、六进制加法六进制加法遵循以下规则:1. 当两个数相加时,从最低位开始逐位相加。

2. 如果相加的结果大于等于6,则向前一位进位,并从6中减去进位值。

3. 当所有位相加完成后,如果最高位有进位,则将其加到结果的最高位。

例如,计算六进制数 234 + 5:```234+ 05------244```从最低位开始,4 + 5 = 9,大于等于6,进位1,并将4留在该位。

然后,3 + 0 + 1(进位)= 4,2 + 0 = 2。

所以,234 + 5 = 244。

二、六进制减法六进制减法遵循以下规则:1. 当两个数相减时,从最低位开始逐位相减。

2. 如果被减数的某一位小于减数的对应位,则向前一位借位。

3. 借位后,被减数的该位加上6,再进行相减。

例如,计算六进制数 534 - 234:```534- 234------300```从最低位开始,4 - 4 = 0,3 - 3 = 0,5 - 2 = 3。

所以,534 - 234 = 300。

三、六进制乘法六进制乘法遵循以下规则:1. 将乘数和被乘数的每一位相乘。

2. 如果相乘的结果大于等于6,则向前一位进位,并从6中减去进位值。

3. 将乘积的各位数按照相应的位数进行排列。

例如,计算六进制数234 × 5:```234× 5------1170```从最低位开始,4 × 5 = 20,进位2,并将0留在该位。

然后,3 × 5 + 2(进位)= 17,进位1,并将7留在该位。

接着,2 × 5 + 1(进位)= 11,进位1,并将1留在该位。

最后,将进位1加到最高位,得到1170。

所以,234 × 5 = 1170。

四、六进制除法六进制除法遵循以下规则:1. 将被除数和除数的每一位进行除法运算。

2. 如果被除数的某一位小于除数的对应位,则向前一位借位。

3. 借位后,被除数的该位加上6,再进行除法运算。

电子技术实训项目(数字电子)

数字电子技术项目实训目录项目实训一集成逻辑门电路逻辑功能的测试项目实训二组合逻辑电路的设计与测试项目实训三译码器的使用项目实训四编码译码及数显电路项目实训五数据选择器项目实训六触发器项目实训七集成计数器及应用项目实训八 555时基电路项目实训一集成逻辑门电路逻辑功能的测试一、项目实训目的1.熟悉数字电路实验台的结构、基本功能和使用方法。

2.掌握常用与门、与非门、或门的逻辑功能、测试方法及使用方法。

二、项目实训器材1.数字电路实验台2.元器件: 74LS00 74LS08 74LS32 各一块导线若干三、项目实训说明1.数字电路实验台提供5 V的直流电源供用户使用。

2.连接导线时,最好先测量导线的好坏,为了便于区别,最好用不同颜色导线区分电源和地线,一般用红色导线接电源,用黑色导线接地。

3.实验台“16位逻辑电平输出”模块,由16个开关组成,开关往上拨时,对应的输出插孔输出高电平“1”,开关往下拨时,输出低电平“0”。

4.实验台“16位逻辑电平输输入”模块,提供16位逻辑电平LED显示器,可用于测试门电路逻辑电平的高低,LED亮表示“1”,灭表示“0”。

四、项目实训内容和步骤(1).74LS00(与非)74LS08(与门)74LS32(或门)管脚排列:(2)测试74LS00、74LS08、74LS32的逻辑功能将集成块正确插入实验台的面板上,注意识别1脚位置,查管脚图,分清集成块的输入和输出端以及接地、电源端。

按下表要求输入高、低电平信号,测出相应的输出逻辑电平。

五、项目实训报告要求1.整理实验结果,填入相应表格中,并写出逻辑表达式。

2.小结实验心得体会。

项目实训二组合逻辑电路的设计与测试一、项目实训目的掌握组合逻辑电路的分析设计、测试方法。

二、项目实训器材1.数字电路实验台2.元器件: 74LS00 74LS20 各一块导线若干三、项目实训说明设计一个三人表决电路,当多数人同意时,则表决通过,逻辑1(灯亮)表示同意通过,逻辑0(灯灭),表示不同意。

生活中60进制的例子

生活中60进制的例子

六十进制在生活中主要用作纪录时间、角度和地理座标。

六十进制是以60为底数的进位制,源于公元前三千年至公元前两千年的苏美人,后传至巴比伦,流传至今仍用作纪录时间、角度和地理座标。

其他文明也有使用六十进制,如西新几内亚的Ekagi 族。

数字60共有12个正因数,分别为1、2、3、4、5、6、10、12、15、20、30和60,其中2、3和5是质数。

六十进制的优点是:由于拥有较多因数,六十进制的数可被较多数整除,使得许多分数在该进制下是有限小数;换言之,可以分拆成多种不同的时间长度,例如一小时可以被看作2个30分钟、3个20分钟、4个15分钟等。

60也是可同时被1至6整除的最小的数字。

但是,六十进制的乘法表将包含60×60共3600项,远远高于十进制的乘法表,记忆更加困难,因此在实际使用中六十进制未必更高效。

60进制简述

六十进制

六十进制是以60为基数的进位制,源于公元前3世纪的古闪族,后传至巴比伦,流传至今仍用作纪录时间、角度和地理座标。

其他文明也有使用六十进制,如西新几内亚的Ekagi族。

数字60有12个因子,即1、2、3、4、5、6、10、12、15、20、30和60,其中2、3和5是质数。

由于拥有较多因子,六十进制的数可被较多数整除;换言之,可以分拆成多种不同的时间长度,例如一小时可以被看作2个30分钟、3个20分钟、4个15分钟等。

60也是可同时被1至6整除的最小的数字。

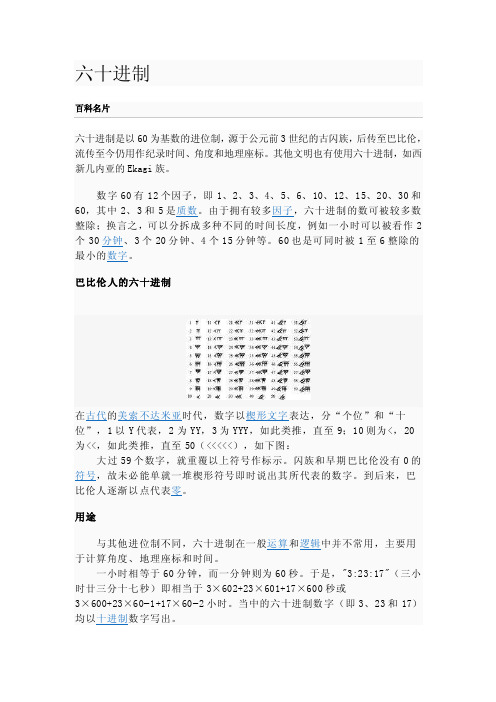

巴比伦人的六十进制

在古代的美索不达米亚时代,数字以楔形文字表达,分“个位”和“十位”,1以Y代表,2为YY,3为YYY,如此类推,直至9;10则为<,20

为<<,如此类推,直至50(<<<<<),如下图:

大过59个数字,就重覆以上符号作标示。

闪族和早期巴比伦没有0的符号,故未必能单就一堆楔形符号即时说出其所代表的数字。

到后来,巴比伦人逐渐以点代表零。

用途

与其他进位制不同,六十进制在一般运算和逻辑中并不常用,主要用于计算角度、地理座标和时间。

一小时相等于60分钟,而一分钟则为60秒。

于是,"3:23:17"(三小时廿三分十七秒)即相当于3×602+23×601+17×600秒或

3×600+23×60−1+17×60−2小时。

当中的六十进制数字(即3、23和17)均以十进制数字写出。

74ls160十进制计数器原理

74ls160十进制计数器原理

74LS160十进制计数器原理74LS160是一种常用的十进制计数器,它能够实现0至9的循环计数。

它的原理基于二进制计数和锁存器的结合。

该计数器由四个D触发器组成,每个触发器都能存储一个二进制位。

在计数过程中,每当一个触发器的输出从低电平变为高电平时,它会向高位触发器传递一个脉冲信号。

这样,当最低位的触发器计数到9时,它会向高位触发器传递一个脉冲信号,使得高位触发器加1,而最低位触发器归零。

为了实现循环计数,74LS160还包含一个复位功能。

当外部信号复位输入为低电平时,所有触发器的输出都会被清零,计数器重新从0开始计数。

除了计数功能,74LS160还具有一个使能输入。

当使能输入为低电平时,计数器将会被禁用,不再进行计数。

这个功能可以用于控制计数器的启动和停止。

总结起来,74LS160十进制计数器通过二进制计数和锁存器的结合,实现了0至9的循环计数。

它具有复位和使能功能,可以灵活控制计数器的启动和停止。

这使得它在很多应用中都有广泛的使用,如时钟、计时器、频率分析等。

74ls160十进制计数器原理(一)

74ls160十进制计数器原理(一)介绍74ls160是一种常见的数字计数器芯片,主要用于计数和分频电路的设计中。

本文将深入解析74ls160的原理,以及如何使用它来进行计数。

什么是74ls160?74ls160是一种4位二进制/十进制计数器,可以通过外部时钟信号进行计数。

它有一个复位输入端,可以将计数器复位到0。

74ls160内部结构74ls160由两个主要的部分构成:•计数器•码型选择器计数器计数器由四个D触发器(D Flip-flop)级联构成,可以实现二进制和十进制两种计数模式。

在二进制计数模式下,计数器会从0000(十进制0)开始计数,一直累加到1111(十进制15),然后重新从0000开始。

而在十进制计数模式下,计数器会从0000(十进制0)开始计数,然后依次递增到0001(十进制1)、0010(十进制2)、0011(十进制3)…依次递增到1001(十进制9),然后重新从0000(十进制0)开始。

码型选择器码型选择器可以控制计数器以二进制或十进制模式进行计数。

它包含两个输入端:•BCD位(P/Q)•M段其中,P/Q位用于选择十进制计数还是二进制计数模式,M段则用于选择计数器是否可以计数到16。

如果M段输入高电平,则计数器可以从0000计数到1111;如果M段输入低电平,则计数器只能计数到1001。

如何使用74ls160进行计数74ls160可以通过一个外部时钟信号进行计数,这个时钟信号可以来自外部的振荡器或信号源。

每当时钟信号上升沿到达计数器时,计数器会自动加1,并输出当前的计数值。

此外,74ls160还有一个复位输入端,可以将计数器复位为指定的值。

复位信号需要在时钟信号之前达到才能生效。

在典型的应用中,复位信号通常由一个按钮或拨动开关提供。

结论74ls160作为一种通用的计数器芯片,可以适用于多种应用场景:例如频率计、脉冲计、时钟分频等等。

当然,在使用时需要根据具体的需求选择不同的工作模式和参数配置。

基于CPLD的数字时钟设计

CPLD课程学习报告 学生姓名:熊军 同组者姓名:黄辉 CPLD的全称是 Complex Programmable Logic Device (即复杂可编程器件),但本次试验所使用的器件并不是CPLD而是FPGA,FPGA的全称是Field Programmable Gate Array

(即现场可编程门阵列)。FPGA与CPLD有很多相似点,它们都是可编程数字逻辑器件,都在时序逻辑电路和组合逻辑电路中有很强的优势。它们的区别在于,FPGA的容量大、速度慢且不可预测、掉电信息丢失,二CPLD容量小、速度快且有很好的可预测性、掉电信息不丢失。CAD的全称是 Computer Aided Design(即计算机辅助设计)。 本实验所用到的软件是MAX+PLUS II,本次试验目的是做一个数字时钟。该数字时钟包含五个主模块,它们分别是数字时钟模块、闹钟模块、跑表模块、模式选择模块和音乐模块。。完成的功能如下:1、数字时钟,时、分、秒六位数码管显示(标准时间23点59分59秒),具有小时、分钟加减调时调分的校准功能,整点报时:55,56,57,58,59低音响,正点高音,间断振铃(嘟--嘟--嘟--嘟--嘟--嘀);2,、定时闹钟,可在00:00到23:59之间由用户设定任一时间,到时报警,定时闹钟花样,前10s一般振铃,其后13秒较急促,再其后17秒急促,最后20秒特急促振铃。并可随时关断;3、跑表,最大计时99分59秒999毫秒。独立的跑表功能,不影响数字钟正常工作。另外附加一段音乐,可随时控制播放和停止,不影响其他任何功能,音乐的内容是《两只蝴蝶》。系统原理图如下:

系统共有九个输入管脚,41个输出管脚,输出管脚中包括一个蜂鸣器,八个数码管,八个LED发光二极管。图中的D触发器的作用是为了使跑表具有后台功能。下面依次介绍这五个模块。

一、 数字时钟模块 数字时钟模块包含四个部分,它们分别是六十进制计数器、二十四进制计数器、分频器和整点报时控制器。它们的原理图如下,程序见附录。 六十进制计时器和二十四进制计数器的思想一样,都是利用时钟沿计数,并将计数值输出,不同的是计数器模(即计数上限值)。六十进制计数器的模式60,二十四进制计数器的模是24。它们都包含clk、reset、en、sub、qh、ql、carry七组引脚,其中只有qh和ql的宽度是四位,其它全为一位。clk 是时钟输入端,上升沿有效;reset 是异步复位端,高电平有效;en 是使能端,低电平有效,高电平计数保持;sub 是减计数,高电平有效;qh、ql分别是计数器的十位和个位,高电平有效;carry 是进位端,正脉冲有效。 将两个六十进制计数器和一个二十四进制计数器依次串联起来,用1Hz的时钟驱动,就组成了简单的数字时钟。同时为了实现调时功能,将调时信号和时钟信号做异或运算后的信号作时钟信号。这里之所以使用与异或门,是因为无论调时信号的状态如何,都不会封锁正常的时钟线号,只是电平相反,时钟超前或滞后半个时钟周期,这是异或门的优点。而与门和或门就不行,低电平封锁与门,高电平封锁或门。 分频器是将50MHz的时钟信号分频成clk1、clk2、clk3 三种频率的方波,它们的频率分别是500Hz、1500Hz、1Hz。500Hz对应的音调是 嘟,1500Hz对应的音调是 嘀,1Hz的信号就作时钟驱动信号。 整点报时控制器是在59分55、56、57、58、59秒从beep引脚送出clk1,整点时从beep引脚送出clk2 。但是为了使每秒之间的响声是间断的,我们将 clk1 和 clk2 分别与clk3 相与后再送入整点报时控制器,从而使beep 发出 嘟-嘟-嘟-嘟-嘟-嘀 的声音。

60进制的计算方法

60进制的计算方法嘿,咱就说说60 进制的计算方法呗。

这60 进制啊,跟咱平常老用的十进制不太一样。

十进制就是满十进一,这60 进制呢,是满六十进一。

咱先说说加法咋算。

比如说咱要算25 加38,在60 进制下哈。

先个位相加,5 加8 等于13,可这60 进制下不能写成13 啊,得把13 分成10 和3,10 就是一个六十,得往十位进一。

然后十位上 2 加 3 再加上进的一,就是6。

所以25 加38 在60 进制下就是63。

减法呢,也有点不一样。

比如说48 减27。

个位上8 减7 等于1。

十位上4 减2 等于2。

所以结果就是21。

可要是不够减咋办呢?比如说35 减48。

个位上 5 减8 不够减啊,这时候就得从十位借一,借来的一在60 进制下就是六十。

个位上就变成了65 减8,等于57。

十位上借走了一,就变成 2 了,2 减 4 也不够减啊,再从更高位借一,咱这先不考虑更高位哈,就当借不来了。

反正这结果就是算不出来了。

咱就知道不够减的时候得从高位借一,借的一在60 进制下是六十。

乘法呢,也有点麻烦。

比如说35 乘以24。

先算 5 乘以 4 等于20,在60 进制下就是20。

再算30 乘以 4 等于120,加上刚才个位进的20,就是140,140 在60 进制下就是220。

然后算 5 乘以20 等于100,在60 进制下就是40。

再算30 乘以20 等于600,加上刚才十位进的40,就是640,640 在60 进制下就是40。

最后把两次结果加起来,220 加上40,就是260。

咱举个例子哈。

俺们村有个老李头,他以前当过船员,那船上的航海钟就是用60 进制的。

有一回他跟别人讲这60 进制咋算。

他说有一回他们在海上航行,要算时间。

比如说从早上八点过了五个小时是几点。

在60 进制下,8 加5 等于13,这就是下午一点。

老李头就这么一讲,大家就明白这60 进制咋算了。

这60 进制啊,虽然不太好算,但是在一些特定的地方还挺有用哩。

60进制的法则的六个步骤

60进制的法则的六个步骤嗨,宝子们!今天咱们来唠唠60进制法则的六个步骤哦。

那啥是60进制呢?就像咱们看时间,60秒是1分钟,60分钟是1小时,这就是60进制在生活中的体现啦。

第一步呀,得先确定一个基础单位。

比如说在时间里,秒就是个基础单位呢。

这个基础单位就像是盖房子的第一块砖,特别重要。

要是没有这个明确的基础,后面的事儿可就乱套喽。

第二步,就是要确定60这个倍数关系。

为啥是60呢?这可有不少说法。

有人说60这个数啊,它的因数特别多,1、2、3、4、5、6、10、12、15、20、30、60都是它的因数呢。

这样在计算和划分的时候就超级方便。

第三步,开始按照60进制进行分组。

就像把60个小物件归成一组,这一组就相当于高一级的单位啦。

比如说60个秒就组成了1分钟这个新的单位。

这一步就像是把散沙聚成了小沙包呢。

第四步,在不同级别的单位之间进行转换。

这就有点像变魔术啦。

从秒转换到分钟,再从分钟转换到小时。

这一步要很熟练才行,不然就容易迷糊。

就像有时候咱们算时间,从几点几分几秒换算成总共多少秒,再换算回去,要是不熟练就会算错呢。

第五步,运用60进制进行计算。

这时候就可以做一些关于这个进制下的数学题啦。

比如说知道了一个事件持续了多少个60进制的单位,去计算总共是多少基础单位。

这就考验咱们对这个进制的理解和运用能力啦。

第六步,也是很关键的一步哦,就是在实际生活或者工作中熟练运用60进制。

不管是看时钟,还是在一些特定的测量、计算中,都能自如地使用这个进制法则。

这就像骑自行车,骑熟练了就可以到处溜达啦。

宝子们,60进制法则的这六个步骤其实也不难理解啦,只要多琢磨琢磨,就像熟悉一个新朋友一样,慢慢地就会运用自如啦。

任意进制计数器的设计方法

任意进制计数器的设计方法

设计任意进制的计数器可以采用以下方法:

1. 确定计数器的最大值:首先确定计数器的位数,位数决定了计数器能表示的最大值。

对于n位计数器,最大值为进制的n

次方减一。

2. 设计进位逻辑:根据进制确定进位的条件和逻辑。

对于十进制计数器,当个位进位时,十位加一;当十位进位时,百位加一,以此类推。

对于其他进制计数器,也需要确定进位的条件和逻辑。

3. 设计计数逻辑:根据进制确定计数的条件和逻辑。

对于十进制计数器,当个位数达到最大值时,个位数归零,十位数加一;当十位数达到最大值时,十位数归零,百位数加一,以此类推。

对于其他进制计数器,也需要确定计数的条件和逻辑。

4. 实现计数器电路:根据计数器的位数和逻辑设计电路。

可以采用多级触发器实现计数器,如JK触发器或D触发器。

每个

触发器的输入连接到进位逻辑和计数逻辑的输出,形成级联的计数器电路。

5. 测试和验证:对设计的计数器进行模拟或实际测试,验证其功能和正确性。

可以使用计算机辅助设计软件进行模拟,或者通过实际连接电路进行测试。

需要注意的是,任意进制计数器的位数和进制需要事先确定,

并在设计时考虑到。

如果需要设计一个可以动态切换进制的计数器,需要通过电路或程序实现切换进制的功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

六十进制计数器

一.实验目的

1.掌握文本与原理图相结合的层次设计方法。

2.掌握六十进制计数器设计。

二.实验仪器及设备

计算机、Quartus II。

三.实验原理

利用层次设计方法:

底层采用文本输入方法,设计十进制和六进制计数器;

顶层用原理图设计六十进制计数器。

以下是个模块的对应元件:

.

四.实验内容及注意事项

1.根据给定的元件符号,使用VHDL编写源代码。

2.层次设计,底层以文本形式设计六进制和十进制。

3.原理图的设计方法设计六十进制计数器。

4.仿真完成后,将顶成原理图文件转换为VHDL文本文件。

5.给出波形仿真。

6.对比若将cqi设置为信号后的仿真波形,进行分析。

注意:

1.VHDL描述十进制和六进制计数器时注意进位的输出。

2.顶层设计六十进制计数器的时候,注意线的选择。

(6进制vhdl文本)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY count6 IS

PORT (clk,rst,en:IN STD_LOGIC;

cq:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

cout:OUT STD_LOGIC);

END count6;

ARCHITECTURE behave OF count6 IS

BEGIN

PROCESS(clk,rst,en)

VARIABLE cqi:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF rst='1' THEN cqi:=(OTHERS=>'0');cout<='0';

ELSIF (clk'EVENT and clk='1')then

IF en='1' THEN

IF cqi<5 THEN cqi:=cqi+1;cout<='0';

ELSE cqi:=(others=>'0');cout<='1';

END IF;

END IF;

END IF;

cq<=cqi;

END PROCESS;

END behave;

六进制计数器的源程序count6(十进制计数器count10与此类似)

(10进制vhdl文本)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY count10 IS

PORT(clk,rst,en:IN STD_LOGIC;

cq:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT:OUT STD_LOGIC);

END count10;

ARCHITECTURE behave OF count10 IS

BEGIN

PROCESS(clk,rst,en)

VARIABLE cqi:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF rst='1' THEN cqi:=(OTHERS=>'0');COUT<='0';

ELSIF(clk' EVENT and clk ='1') then

IF en='1' THEN

IF cqi<9 THEN cqi:=cqi+1;cout<='0';

ELSE cqi:=(others=>'0');cout<='1';

END IF;

END IF;

END IF;

cq<=cqi;

END PROCESS;

END behave;

五.实验报告

1.将顶层原理图转换为VHDL文本。

(60进制vhdl文本)

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY count60 IS

PORT

(

clk : IN STD_LOGIC;

rst : IN STD_LOGIC;

en : IN STD_LOGIC;

overflow : OUT STD_LOGIC;

high_cnt_val : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

low_cnt_val : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

);

END count60;

ARCHITECTURE bdf_type OF count60 IS

COMPONENT count10

PORT(clk : IN STD_LOGIC;

rst : IN STD_LOGIC;

en : IN STD_LOGIC;

COUT : OUT STD_LOGIC;

cq : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

);

END COMPONENT;

COMPONENT count6

PORT(clk : IN STD_LOGIC;

rst : IN STD_LOGIC;

en : IN STD_LOGIC;

cout : OUT STD_LOGIC;

cq : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

);

END COMPONENT;

SIGNAL SYNTHESIZED_WIRE_0 : STD_LOGIC;

BEGIN

b2v_inst : count10

PORT MAP(clk => clk,

rst => rst,

en => en,

COUT => SYNTHESIZED_WIRE_0,

cq => low_cnt_val);

b2v_inst1 : count6

PORT MAP(clk => SYNTHESIZED_WIRE_0,

rst => rst,

en => en,

cout => overflow,

cq => high_cnt_val);

END bdf_type;

2. 生成元件及RTL。

(60进制RTL)

(60进制符号原件)

3.各个模块仿真波形图。

(60进制仿真波形)

(6进制仿真波形)

(10进制仿真波形)

4. 书写实验报告时要结构合理,层次分明,在分析描述的时候,注意语言的流畅。