数字电路功耗估算

数字集成电路低功耗分析

数字集成电路低功耗分析摘要:电子产品功耗的大小不仅限制了便携设备电池使用时间,也在一定程度上影响着设备性能。

研究如何降低功耗己经成为所有IC设计者必须考虑的重要问题,对功耗的优化也是目前每个IC设计企业的必要环节。

本文主要对数字集成电路功耗的优化方法进行了分析,分别从工艺级、电路级、版图级、门级、寄存器级、算法级和系统级分析了低功耗的优化方法。

关键词:低功耗;集成电路;优化引言:随着移动设备快速大量的增加和芯片处理速度的提高,芯片的功耗己成为集成电路设计者必须考虑的重要问题,于此同时对芯片的整体性能评估己经由原来的面积和速度变成了面积、时序、可测性和功耗的综合考虑,而且功耗所占的比重越来越大。

低功耗技术的研究背景:集成电路是一个二十世纪发展起来的高技术产业,也是二十一世纪世界进入信息化社会的前提和基础。

在1958年德克萨斯仪器公司生产出第一块集成电路,集成电路产业就一直保持着快速的发展速度,处在数字化和信息化时代的今天,数字集成电路的应用和改进显得尤为重要,从电子管到晶体管再到中小规模集成电路和超大规模集成电路,到现在市场上主流的专用集成电路(ASIC),以及现处于快速发展的系统级芯片,数字集成电路始终朝着速度更快,集成度更高,规模更大的方向不断发展。

从目前状况来看,数字集成电路基本上仍然遵循摩尔定律来发展—集成度几乎每18个月增长一倍。

但是随着芯片规模的不断扩大,功耗问题变得越来越突出,并且成为制约数字集成电路发展的重要因素。

长期以来,面积最小化和处理的高速度是数字集成电路设计中最主要的问题。

现在,因为新的IC技术工艺的使用和集成度越来越高,降低芯片功耗逐渐成为了非常重要的一个因素。

在亚微米和深亚微米的技术中,由于能量消耗而产生的余热使电路中的某些功能受到了不同程度的影响。

功耗的增加意味着电迁移率的增加。

当芯片温度上达到一定的程度时,电路就无法正常工作,因此复杂系统的性能就会被严重的影响到,并且整个系统的可靠性将会降低,尤其对于要求具有长生命周期和高可靠性的电子产品来说,降低功耗是必然的选择。

DC-DC内部功耗计算

DC-DC内部功耗计算影响开关模式、DC-DC转换器效率的主要原因(转)2010-04-07 16:55影响开关模式、DC-DC转换器效率的主要因,本文详细介绍了开关电源(SMPS)中各个元器件损耗的计算和预测技术,并讨论了提高开关调节器效率的相关技术和特点。

概述效率是任何开关电源(SMPS)的重要指标,特别是便携式产品,延长电池使用寿命是一项关键的设计目标。

对于空间受限的设计或者是无法投入成本解决功率耗散问题的产品,高效率也是改善系统热管理的必要因素。

SMPS设计中,为获得最高转换效率,工程师必须了解转换电路中产生损耗的机制,以寻求降低损耗的途径。

另外,工程师还要熟悉SMPS IC的各种特点,以选择最合适的芯片来达到高效指标。

本文介绍了影响开关电源效率的基本因素,可以以此作为新设计的准则。

我们将从一般性介绍开始,然后针对特定的开关元件的损耗进行讨论。

效率估计能量转换系统必定存在能耗,虽然实际应用中无法获得100%的转换效率,但是,一个高质量的电源效率可以达到非常高的水平,效率接近95%。

绝大多数电源IC的工作效率可以在特定的工作条件下测得,数据资料中给出了这些参数。

Maxim的数据资料给出了实际测试得到的数据,其他厂商也会给出实际测量的结果,但我们只能对我们自己的数据担保。

图1给出了一个SMPS降压转换器的电路实例,转换效率可以达到97%,即使在轻载时也能保持较高效率。

采用什么秘诀才能达到如此高的效率?我们最好从了解SMPS损耗的公共问题开始,开关电源的损耗大部分来自开关器件(MOSFET和二极管),另外小部分损耗来自电感和电容。

但是,如果使用非常廉价的电感和电容(具有较高电阻),将会导致损耗明显增大。

选择IC时,需要考虑控制器的架构和内部元件,以期获得高效指标。

例如,图1采用了多种方法来降低损耗,其中包括:同步整流,芯片内部集成低导通电阻的MOSFET,低静态电流和跳脉冲控制模式。

我们将在本文展开讨论这些措施带来的好处。

电路中的电力负载与功耗分析

电路中的电力负载与功耗分析电力负载与功耗分析是在电路设计和应用中非常重要的一环。

通过对电路中电力负载和功耗的分析,可以更好地了解电路的性能、稳定性和功耗特性,从而为电路的优化提供参考。

本文将对电力负载和功耗分析的基本概念和方法进行介绍,并探讨其在实际应用中的重要性。

一、电力负载的概念和分类电力负载是指电路中接受电能并将其转换为其他形式能量的元件或部件。

根据其工作原理和特点,电力负载可以分为恒阻性负载、恒流性负载和恒功率性负载等不同类型。

1. 恒阻性负载:恒阻性负载的特点是其电阻值在工作过程中不发生变化,例如电阻器。

恒阻性负载在电路中所消耗的功率与电压和电流的乘积成正比。

2. 恒流性负载:恒流性负载的特点是其电流值在工作过程中不发生变化,例如电流源。

恒流性负载在电路中所消耗的功率与电压成正比。

3. 恒功率性负载:恒功率性负载的特点是其功率值在工作过程中不发生变化,例如电子设备。

恒功率性负载在电路中所消耗的功率与电压和电流的乘积成恒定值。

二、功耗的概念和计算方法功耗是指电路在单位时间内所消耗的能量,通常用瓦特(W)来表示。

功耗的计算可以通过电路中电压和电流的测量得到。

对于恒阻性负载和恒电流性负载,功耗的计算公式分别为P = U * I和P = I^2 * R,其中P表示功耗,U表示电压,I表示电流,R表示电阻。

对于恒功率性负载,功耗的计算则需要考虑到其功率保持不变的特点。

对于电压和电流变化的情况,根据功率的定义可以得到P = U * I = P0,其中P0表示恒功率性负载的额定功率。

因此,在电路中可以根据负载的特性以及电压、电流的变化情况来计算功耗。

三、电力负载与功耗分析的重要性电力负载与功耗分析在电路设计和应用中具有重要的作用。

1. 评估电路性能:通过对负载和功耗的分析,可以评估电路的性能指标,如电压稳定性、电流波动等。

将负载和功耗分析作为评估指标之一,可以从性能的角度评价电路的优劣并进行相应的调整和优化。

数字电路低功耗设计

数字电路低功耗设计数字电路是现代电子设备中的重要组成部分,其功耗的控制对于延长设备的续航时间、提高设备性能以及降低散热压力都具有至关重要的意义。

本文将介绍数字电路低功耗设计的相关内容,包括技术原理、优化方法和实践指导。

一、技术原理1.1 时钟频率控制时钟频率是数字电路中最主要的功耗来源之一,通过降低时钟频率可以有效减少功耗。

在设计数字电路时,应合理选择合适的时钟频率,并结合实际需求进行调整。

可以采用动态时钟频率调整技术,根据电路负载情况自适应地调整时钟频率,以实现在不损失性能的前提下降低功耗。

1.2 算法优化在数字电路设计中,算法的优化也是降低功耗的重要手段之一。

通过优化算法、改变数据处理方式等方法,可以减少电路的计算量和数据传输量,从而降低功耗。

例如,可以使用更高效的算法代替传统算法,减少计算步骤和数据冗余,提高电路的运算效率。

1.3 电源管理合理的电源管理对于数字电路的低功耗设计至关重要。

可以采用多电源供电技术,为不同模块提供不同的供电电压和电流,以满足不同模块的功耗需求。

另外,利用睡眠模式和唤醒机制也可以实现电路在不同工作状态下的功耗优化。

二、优化方法2.1 逻辑综合和布局布线优化在数字电路的实际设计过程中,采用合理的逻辑综合和布局布线方法可以达到低功耗的目的。

逻辑综合阶段可以通过综合工具对逻辑电路进行优化,减少门级数目、减少逻辑层次,从而减少功耗。

在布局布线阶段,可以进行电源线与信号线的合理布局,以降低功耗和信号干扰。

2.2 时钟网络优化时钟网络对数字电路的功耗影响明显,因此时钟树的优化也是低功耗设计中的重要环节。

通过对时钟信号的路径和布线进行优化,可以减少时钟延迟和功耗。

此外,还可以采用局部时钟网格布线技术,有效减少时钟传输路径的长度,降低电路的功耗。

2.3 选择合适的存储器存储器在数字电路中占据较大的比例,其功耗也相对较高。

因此,在低功耗设计中选择合适的存储器是非常重要的。

可以选择低功耗的存储器类型,例如低功耗SRAM、快速闪存等,同时合理设计存储器的访问方式和结构,以减少功耗。

MOSFET功耗估计及散热

DC/DC变换中MOSFET功耗计算本文分析了一个多相、同步整流、降压型CPU电源中MOSFET功耗的计算方法。

1 MOSFET功耗的计算为了确定一个MOSFET是否适合于特定的应用,必须计算其功耗,MOSFET功耗(PL)主要包含阻性损耗(PR)和开关损耗(PS)两部分,即PL=PR+PSMOSFET的功耗很大程度上依赖于它的导通电阻RDS(on),但是,MOSFET的RDS(on)与它的结温Tj有关。

而Tj又依赖于MOSFET管的功耗以及MOSFET的热阻θJA。

由于功耗的计算涉及到若干个相互依赖的因素,为此,可以采用一种迭代过程获得我们所需要的结果,如图1流程所示。

迭代过程起始于为每个MOSFET假定一个Tj,然后,计算每个MOSFET各自的功耗和允许的环境温度。

当允许的环境温度达到或略高于机壳内最高温度设计值时,这个过程便结束了。

这是一种逆向的设计方法,因为,先从一个假定的Tj开始计算,要比先从环境温度计算开始容易一些。

能否将这个计算所得的环境温度尽可能地提高呢?回答是不行的。

因为,这势必要求采用更昂贵的MOSFET,并在MOSFET下铺设更多的铜膜,或者要求采用一个更大、更快速的风扇产生气流等,所有这些都是不切实际的。

对于开关和同步整流MOSFET,可以选择一个允许的最高管芯结温Tj(hot)作为迭代过程的出发点,多数MOSFET的数据手册只规定了+25℃下的最大RDS(on),不过最近有些产品也提供了+125℃下的最大值。

MOSFET的RDS(on)随着温度的增高而增加,典型温度系数在0.35%/℃~0.5%/℃之间,如图2所示。

如果拿不准,可以用一个较为保守的温度系数和MOSFET的+25℃规格(或+125℃规格),在选定的Tj(hot)下以最大RDS(on)作近似估算,即式中:RDS(on)SPEC为计算所用的MOSFET导通电阻;TSPEC为规定RDS(on)SPEC时的温度。

数字电路的功耗优化分析

数字电路的功耗优化分析摘要:数字电路的功耗优化是现代电路设计中的一个主要问题。

本文介绍了数字电路功耗优化的基本概念和方法。

首先,介绍了数字电路功耗的来源和分类。

然后,详细讨论了数字电路功耗优化的技术,包括静态功耗优化、动态功耗优化和整体功耗优化。

最后,结合实例分析了数字电路功耗优化的实践应用。

关键词:数字电路,功耗,优化,静态功耗,动态功耗,整体功耗。

正文:一、引言随着现代电子技术的不断进步,数字电路的应用越来越广泛。

然而,数字电路的功耗问题一直是电路设计中的难点之一。

低功耗设计已经成为当前数字电路设计中的一个主要目标之一。

本文将会讨论数字电路功耗优化的基本概念和方法。

二、数字电路功耗的来源和分类数字电路的功耗主要有两个来源:静态功耗和动态功耗。

1. 静态功耗静态功耗指电路在不进行任何操作的情况下的功耗。

静态功耗来自电路的待机电流和漏电流。

静态功耗的大小与电路中的晶体管数量和电源电压有关。

2. 动态功耗动态功耗指电路在正常工作时的功耗。

动态功耗来自电路开关晶体管时的电荷在晶体管和电容器之间的存储和规律性的变化所引起的能量损失。

动态功耗的大小与电路的开关频率、电容器大小和电源电压有关。

三、数字电路功耗优化技术数字电路功耗优化技术包括静态功耗优化、动态功耗优化和整体功耗优化。

1. 静态功耗优化静态功耗优化主要有两种方法:电源电压缩放和晶体管(包括中间状态分配、动态门控时钟树分区等)的屏蔽与消除。

2. 动态功耗优化动态功耗优化主要有三种方法:时序完整性优化、能量回收和降压技术。

3. 整体功耗优化整体功耗优化是指对数字电路全局进行功耗优化。

整体功耗优化的目标是优化所有单元,以最小化时钟频率和功耗。

整体功耗优化通常需要使用一种称为“节点识别”的技术,以减少电路的路径长度和旁路电流。

四、数字电路功耗优化实践应用以NAND逻辑门为例进行数字电路功耗优化实践。

通过减少晶体管数量、缩小电源电压和调整逻辑电路结构,实现了对数字电路功耗的优化。

单片机功耗的计算办法

单片机功耗的计算办法

单片机的功耗是非常难算的,而且在高温下,单片机的功耗还是一个特别重要的参数。

暂且把单片机的功耗按照下面的划分。

1.内部功耗(与频率有关)

2.数字输入输出口功耗

2.1输入口

2.2输出高

2.3输出低

3.模拟输入口功耗

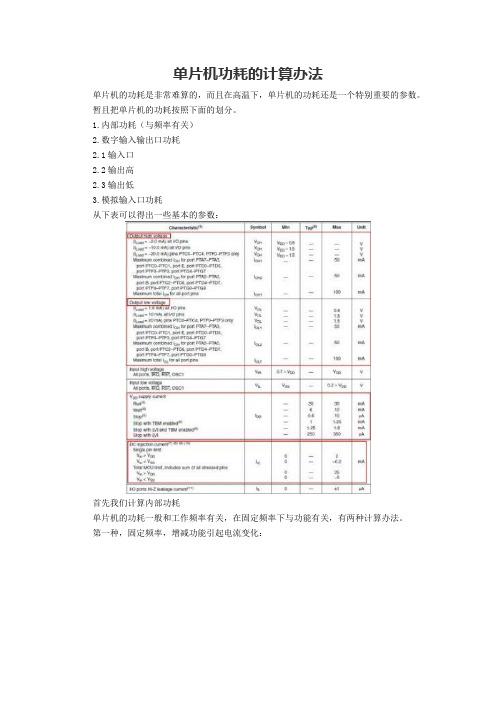

从下表可以得出一些基本的参数:

首先我们计算内部功耗

单片机的功耗一般和工作频率有关,在固定频率下与功能有关,有两种计算办法。

第一种,固定频率,增减功能引起电流变化:

第二种,频率变化,不考虑使用模块:

其次计算数字口功耗:

数字输出口,按照表格中的数据,得出内部的Rdson,可计算出输出高和输出低在内部的功耗。

这里需要注意的是,输入口的功耗一般不大,但是设计的IO口有电流注入的时候功耗较大,这时候嵌位二极管是工作的,注意这部分功耗。

P=I.inject*Vf_diode

输入功耗在没有Clamped的时候是相对较小的,如果输入电压过高和过低则会造成很多的问题。

MCU的所有功耗为三部分功率相加。

P.MCU=P.internal+P.IO+P.Analog。

数字电路降低功耗的方法

数字电路降低功耗的方法数字电路功耗的降低是现代电子技术设计的一个重要课题。

随着电子设备的普及和计算需求的增加,如何减少数字电路中的功耗成为了一个迫切需要解决的问题。

本文将探讨一些方法和技术,帮助降低数字电路的功耗。

1. 时钟频率优化在数字电路中,时钟频率是一个重要的参数,它决定了电路运行的速度。

然而,高频率的时钟意味着更高的功耗。

因此,通过优化时钟频率可以实现功耗的降低。

一种常见的方法是对时钟信号进行分频,降低时钟的频率,从而减少功耗。

2. 电源电压降低降低电源电压是另一个可以减少功耗的方法。

随着技术的进步,数字电路对电源电压的要求越来越低。

降低电源电压可以降低电路的功耗,但需要注意的是,电源电压的降低也会导致电路的性能下降,需要在功耗和性能之间进行权衡。

3. 优化电路结构合理的电路结构设计也可以降低功耗。

例如,采用低功耗的逻辑门电路替代传统的电路结构,可以显著减少功耗。

另外,通过优化电路中的开关电流路径,减少电流的损耗,也可以达到降低功耗的目的。

4. 采用节能型器件选择功耗较低的器件也是一个有效的方法。

现代科技已经提供了许多节能型的数字电路器件,如低功耗逻辑门、低功耗存储器等。

采用这些器件可以显著降低功耗,提高电路的能效比。

5. 关闭无用电路数字电路中常常存在一些无用的电路模块或电路分支,它们可能是由于设计中的一些历史原因或故障导致的。

及时检测和关闭这些无用电路模块,可以节省很多功耗。

因此,在电路设计和调试的过程中,对无用的电路要进行全面的识别和屏蔽。

6. 优化数据传输数字电路中常常需要进行大量的数据传输。

优化数据传输的方式可以减少功耗。

例如,采用数据压缩算法可以缩小数据量,减少传输数据的次数,从而减少功耗。

此外,采用高效的数据缓存技术和流水线技术,可以提高数据传输的效率,进一步减少功耗。

7. 功耗管理技术功耗管理技术是数字电路设计中一个重要的方向。

通过采用先进的功耗管理技术,可以根据不同的运行状态和需求,动态地调整电路的供电和工作频率,从而实现功耗的最优化。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电路功耗估算

数字电路功耗估算是在电子领域中非常重要的一项任务。

随着电子

设备的不断发展和智能化的需求增加,对于电路功耗的估算和优化已

经成为了不可忽视的一部分。

本文将介绍数字电路功耗估算的基本原

理和方法,以及目前常用的功耗估算工具和技术。

一、数字电路功耗估算的原理

数字电路功耗估算是通过对电路中的每一个模块和元件的功耗进行

分析和计算,最终得出整个电路的功耗消耗情况。

在进行功耗估算时,需要考虑以下几个因素:

1. 逻辑电平转换功耗:逻辑运算中的电平转换会带来一定的功耗损耗,这是因为在逻辑门的输入和输出之间会有电流通过。

通过计算逻

辑门的输入和输出之间的电流和电压差,可以得出逻辑电平转换的功耗。

2. 开关电流功耗:数字电路中的开关操作会导致电流从一个逻辑门

转换到另一个逻辑门。

当电流从一个逻辑门转换到另一个逻辑门时,

会产生一定的功耗。

通过计算每个开关的电流和电压差,可以得出开

关电流功耗。

3. 内部电源损耗:数字电路中的内部电源供应系统也会产生一定的

功耗。

这是因为内部电源系统需要维持整个电路的运行,并为逻辑门

和开关提供所需的电流和电压。

通过计算内部电源系统的电流和电压,可以得出内部电源损耗的功耗。

二、数字电路功耗估算的方法

数字电路功耗估算可以通过以下几种方法进行:

1. 理论模型估算:根据数字电路的理论模型和电路结构,通过计算

每个部分的功耗,然后将它们相加得到整个电路的功耗估算值。

这种

方法适用于简单的数字电路,但对于复杂的电路来说,计算量较大且

容易出错。

2. 仿真模拟估算:通过使用电路仿真软件,在实际工作负载下对数

字电路进行仿真模拟。

通过观察仿真结果,可以得到电路的功耗估算。

这种方法相对准确,但需要花费较长的时间和计算资源。

3. 电路特性估算:通过对数字电路的特性和规格进行分析和估算,

可以得出电路的功耗估算。

这种方法与实际电路的测试结果较为接近,但需要对电路的参数和特性有一定的了解和经验。

三、常用的功耗估算工具和技术

目前,有许多功耗估算工具和技术可供选择。

以下是一些常用的功

耗估算工具和技术:

1. 电路分析工具:如SPICE(Simulation Program with Integrated Circuit Emphasis)等,可以对数字电路进行精确的仿真和分析,包括

功耗估算。

2. 电路优化工具:通过对电路的结构和元件进行优化,可以降低电

路的功耗。

常见的电路优化技术包括流水线设计、时钟树优化和低功

耗电源设计等。

3. 电路功耗模型:有一些公开可用的电路功耗模型,可以用于对数字电路功耗进行估算。

这些模型基于统计学和实测数据,可以准确地估算电路功耗。

四、结语

数字电路功耗估算对于电子领域中的电路设计和优化至关重要。

通过对每个模块和元件的功耗进行分析和计算,可以得出整个电路的功耗消耗情况,并通过相应的工具和技术进行优化和改进。

电路功耗的估算不仅可以帮助设计人员优化电路性能,还可以帮助节约能源和提高电子设备的效率。

因此,数字电路功耗估算应该成为电子设计中的一个必备环节。