第五章存储器装置

第五章存储器

②再生操作: “再生”或“刷新”。由于4管存储元的信息电荷有

泄漏,电荷数不象6管存储元电路由电源经负载管源源不断地补

充,时间一长就会丢失信息。必须设法在外界按一定规律不断给

栅极进行充电,按需要补足栅极的信息电荷。

VD

VD

预充

字线选择

预充

A

BS0 T2

T0

B

T1

T3

BS1

2020/3/7

CD VS

C0 D

两次刷新操作之间的最小时间间隔=刷新周期/行数 优点:刷新期间不必停止读写 缺点:加长系统存取周期,降低整机速度。 (3)异步刷新方式:将集中刷新与分散刷新相结合,

将刷新操作平均分配到最大刷新时间间隔内进行。 刷新周期=最大刷新时间间隔/行数

2020/3/7

有一个RAM芯片,其芯片内部是256×256结构 例题 组成,问(1)采用集中刷新方式,设读/写周

2.CPU应用控制线发出读请求。

3.主存储器作出回答后将读出的信息放于数据总线,送入 数据20寄20/3/存7 器DR

DR

CPU

AR

数据总线 写

地址总线

主存

先明确要 将信息存 到主存哪 个位置并 通知主存, 然后再将

信息从 CPU送到 该位置。

CPU从主存中存/写信息:

1.CPU将信息字要在主存中存储的地址信号经地址寄存器 AR送地址总线,同时将信息字送数据寄存器DR,并发出 写命令,同时将信息字送到存储器相应位置。(CPU告诉 存储器要将信息字放在存储器的哪个位置,并发送信息字)

MAR(存储器地址寄存器):存放地址总线提供的将 要访问的存储单元的地址码。

读写电路:完成对存储体中数据的读写操作

控制电路:控制读写电路的读写过程

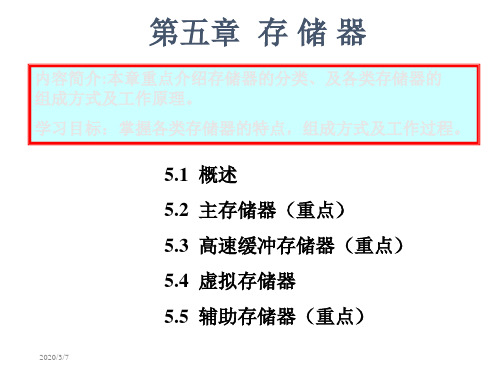

第五章 存储器

存储器的分类Leabharlann

存储器是计算机的重要组成部分之一,用来存储程序和数 据,表征了计算机的“记忆”功能 1.按用途分类 ⑴内部存储器 内部存储器又叫内存,是主存储器。用来存储当前正在使 用的或经常使用的程序和数据。CPU可以对他直接访问, 存取速度较快。 ⑵外部存储器 外部存储器又叫外存,是辅助寄存器。外存的特点是容 量大,所存的信息既可以修改也可以保存。存取速度较慢, 要用专用的设备来管理。 计算机工作时,一般由内存ROM中的引导程序启动程序, 再从外存中读取系统程序和应用程序,送到内存的RAM中, 程序运行的中间结果放在RAM中,(内存不够是也可以放 在外存中)程序的最终结果存入外部存储器。

一种内存储器

1.随机存储器(Random Access Memory) RAM有以下特点:可以读出,也可以写入。读出时并不损坏原来存储 的内容,只有写入时才修改原来所存储的内容。断电后,存储内容立即消 失,即具有易失性。 RAM可分为动态( Dynamic RAM)和静态(Static RAM)两大类。DRAM的特点是集成度高,主要用于大容量内存储器; SRAM的特点是存取速度快,主要用于高速缓冲存储器。 2.只读存储器(Read Only Memory) ROM是只读存储器。顾名思义,它的特点是只能读出原有的内容, 不能由用户再写入新内容。原来存储的内容是采用掩膜技术由厂家一次性 写入的,并永久保存下来。它一般 用来存放专用的固定的程序和数据。不 会因断电而丢失。 3.高速缓存存储器(Cache) 高速缓存存储器 Cache ,可以设置在CPU内部,它与运算器和控制 部件距离较近,工作过程完全有硬件电路控制,因此数据的存取速度很快, 一般速度高出内存数倍。Cache 容量较小,大都在1MB以下。在计算机运 行时,Cache用来存放当前正在执行的程序(段)或正在处理的数据。

第五章 存储器系统PPT课件

存取速度快,但集成度低,一般 用于大型计算机或高速微机的 Cache;

易失性 存储器

静态SRAM 速度较快,集成度较低,一般用

半导

MOS型

于对速度要求高、而容量不大的 场合(Cache)

体存 储器

非易失性存储器

动态DRAM 集成度较高但存取速度较低,一 般用于需较大容量的场合(主存)。

掩膜ROM 一次性可编程PROM 紫外线可擦除EPROM 电可擦除E2PROM 快闪存储器FLASH

u 存储芯片组织

l存储芯片互连

64Kx1,扩充64KB

A0~A15

D0~D7 64Kx8

A0~A15 R/W

R/W CS

64Kx1

64K64xK614xK614xIK61/O4xIK61/O4xIK61/O4xIK1/OxI1/OI/OI/OD7

I/O

D6

D4 D5

D2 D3

D1

D0

DB

8Kx8,扩充64KB

主存储器 cache 主存储器

设cache 的存取时间为tc,命中率为h,主存的存取时间 为tm,则平均存取时间:

ta = tc ×h +(tc + tm)×(1-h)。

【例5.1】 某微机存储器系统由一级cache 和主存组成。 已知主存的存取时间为80 ns,cache 的存取时间为6 ns, cache的命中率为85%,试求该存储系统的平均存取时间。

面神经麻痹的病理变化早期主要为面神经水肿髓鞘和轴突有不同程度的变性以在茎乳突孔和面神经管内的部分尤为显著存储芯片组织64kx1csl存储芯片互连面神经麻痹的病理变化早期主要为面神经水肿髓鞘和轴突有不同程度的变性以在茎乳突孔和面神经管内的部分尤为显著64kx1d064kx1d064kx1d064kx1d064kx1d064kx1d064kx1d08kx8d7d0cscscsdb128kx8扩充64kbcs38面神经麻痹的病理变化早期主要为面神经水肿髓鞘和轴突有不同程度的变性以在茎乳突孔和面神经管内的部分尤为显著64kx1cscscscscscscscsd7d41216kx4扩充64kbcs2415d3d0面神经麻痹的病理变化早期主要为面神经水肿髓鞘和轴突有不同程度的变性以在茎乳突孔和面神经管内的部分尤为显著l存储模块互连多字宽结构同一地址选中多个存储模块的对应单元获得多字宽数据数据寄存器cpu地址寄存器面神经麻痹的病理变化早期主要为面神经水肿髓鞘和轴突有不同程度的变性以在茎乳突孔和面神经管内的部分尤为显著多体交叉结构连续地址分布于不同存储模块便于cpu连续访问多个存储模块地址寄m0m1m2m3数据寄存器10141115m0m1m2m3启动m0启动m1启动m2启动m3一个存取周期访问4个存储体面神经麻痹的病理变化早期主要为面神经水肿髓鞘和轴突有不同程度的变性以在茎乳突孔和面神经管内的部分尤为显著地址译码技术地址译码技术译码电路根据地址总线信号产生出选中某存储器单元或io端口的控制信号译码地址锁存存储模块1存储模块n低位ab高位ab单元地址单元地址相关控制用最低的地址线选字用紧接着的高位地址线选片

【微机原理】第5章.微机的存储器

5.2随机存取存储器(RAM) 一、静态随机存取存储器

(一)静态RAM的基本存储电路 静态RAM的基本存储电路,是由6个MO S管组成的RS触发器.如图5.5所示:

(二)静态RAM的组成 静态RAM的结构组成原理图如图5.6所示:

(三)静态RAM的读/写过程 1.读出过程 (1)地址码A0-A11加到RAM芯片的

2.写入过程 (1)地址码加在RAM芯片的地址输入端,选中相应 的存储单元,使其可以进行写操作。 (2)将要写入的数据放在DB上。 (3)加上片选信号CS=0及写入信号R/W=0。这 两个有效控制信号打开三态门使DB上的数据进入输入 电路,送到存储单元的位线上,从而写入该存储单元。

(四)静态RAM芯片举例

(一)动态基本存储电路 1.三管动态基本存储电路

三管动态基本存储电路如图5.8所示,它由3个管 子和两条字选择线,两条数据线组成。

2.双译码方式(或称重合译码) 双译码方式如图5.4所示。

它将地址码分为X和Y两部分,用两个译码电路 分别译码。

X向译码又称行译码,其输出线称行选择线, 它选中存储矩阵中一行的所有存储单元。

Y向译码又称列译码,其输出线称列选择线, 它选中一列的所有单元。

只有X向和Y向的选择线同时选中的那一位存储 单元,才能进行读或写操作。

(三)读/写电路与控制电路

读/写电路包括读/写放大器、数据缓冲器(三态双向 缓冲器)等。它是数据信息输入和输出的通道。

外界对存储器的控制信号有读信号(RD)、写信号 (WR)和片选信号(CS)等,通过控制电路以控制 存储器的读或写操作以及片选。只有片选信号处于有效 状态,存储器才能与外界交换信息。

微

5.1存储器的分类与组成

机

5.2随机存取存储器(RAM)

微机原理与接口技术第5章存储系统

硬盘) 4、按在计算机系统中位置分类

寄存器、缓冲存储器(Cache)、主存储器(内存)、 辅助存储器(外存)

2020/4/4

4

内存用来存放CPU当前要运行的程序和数据,CPU 可直接用指令对内存进行读/写;外存用来存放CPU当 前暂时不用的程序和数据,CPU不能直接用指令对外 存进行读/写。

2020/4/4

8

5.1.3 存储系统的体系结构

1、存储系统的体系结构 把各种不同存储容量、存取速度和价格的存

储器按层次结构组成多层存储器,并通过管理软 件和辅助硬件有机组合成统一的整体,使所存放 的程序和数据按层次分布在各种存储器中。

2020/4/4

9

CPU 高速缓存

主存储器

I/O 控制电路

辅存 磁盘按照ຫໍສະໝຸດ AM存储器存储信息电路原理的不同,RAM可 分为静态RAM和动态RAM。

2020/4/4

16

静态RAM(SRAM)

一般用作计算机系统的高速缓冲存储器Cache

其特点是:基本存储电路一般由MOS晶体管触 发器组成,每个触发器可存放1位二进制的0或1。 只要不断电,所存信息就不会丢失。因此SRAM 工作速度快,稳定可靠,不需要外加刷新电路。 但它的基本存储电路所需的晶体管多,集成度不 易做的很高,功耗也较大。

第五章 存储系统

❖ 5.1 概述 ❖ 5.2 半导体存储器 ❖ 5.3 半导体存储器与CPU的连接方法 ❖ 5.4 外存储器简介 ❖ 5.5 新型存储器技术

2020/4/4

2

5.1 概述

存储系统:计算机中存放程序和数据的各种存储设 备、控制部件及管理信息调度的设备(硬件)和算法 (软件)所组成的系统。其中,存储器是存储系统中 最核心的设备。

第五章 存储器

存储器是计算机系统中必不可少的组成部分, 用来存放计算机系统工作时所用的信息—— 程序和数据。

存储器表征了计算机的记忆功能。

按构成材料和存储介质分类

半导体存储器 磁介质存储器,如: 磁盘和磁带等 光电存储器

按在计算机中的作用分类

主存储器(内存) 辅助存储器(外存) 高速缓冲存储器(Cache)

地址线:选择芯片中某一存储单元 数据线:数据输入/输出 读写线:控制命令 片选线:选择出某一芯片

内部结构模型

存储体

A0 A1

芯片内部 输出 三态 缓冲

译 码 器

D0~Dk

An

控制逻辑

CS

OE WE

2.典型SRAM芯片

2114(1K×4位): 6116(2K×8位) : 6264(8K×8位) : 62128(16K×8位) :

内存储器或主存储器

(1)主机内部 (2) 存放正在使用或经常使用的 数据和程序 (3)CPU可以直接对它访问 (4)存取速度快 (5) 容量大小受到地址总线位数 的限制

外存储器或辅助存储器

(1)主机外部 (2) 存放暂时不用的数据和程 序 (3) 不直接和 CPU 相连,通过 接口电路与主机相连 (4)存取速度慢 (5)容量较大

2164

NC Din /WE /RAS A0 A2 A1 GND 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 VCC /CAS DOUT A6 A3 A4 A5 A7

第三节 半导体只读存储器ROM

1、定义:在计算机正常工作状态下,存储器的信息只可以随 机读,不可以随机写。 2、性质:非易失性和可靠性。 ROM器件具有结构简单,位密度比读/写存储器高,一 3、分类 : 般用来存放系统启动程序,常驻内存的监控程序,参数 表,字库等,用户设计的单片机或单板机系统中也可用 a. 掩模ROM 它来存放用户程序。 b. 可编程的PROM ROM中信息是在芯片制造时由厂家写入的,用户对这 这种 ROM出厂时,里面没有信息,用户采用一些设备 c. 紫外线擦除、可编程的 EPROM 类芯片无法进行任何修改。 可以将内容写入 PROME 。但 PROM 2PROM d. 电擦除、可编程的 等 中内容一旦写入, 就不能再改变了。 e. 快擦写存储器(Flash ROM)

第5章+主存储器

写入或者读出,但当RAM存储器芯片掉电时,存储单元中的 信息将会丢失。是一种易失性存储器;但目前有些RAM 芯片, 由于内部带有电池,断电后信息不会丢失,称为非易失性 RAM。RAM 主要用来存放原始数据,中间结果或程序,也可 外界交换信息。

■ 动态RAM(Dynamic Random Access Memory,DRAM)。 动态RAM 的基本存储单元是单管动态存储电路,以极间分布

电容来存放信息。电容有电荷为“1”信息,电容无电荷为“0”信息 由于是靠电容的充放电原理来存储电荷,因此如果不及时进行刷新 极间电容中的电荷会因漏电而逐渐丢失,一般信息保持的时间 为2ms 左右。因此DRAM 需定时刷新,且必须配备专门的刷新电 路,保证至少在2ms 内对基本存储单元刷新一次。DRAM 集成度 高,价格低,多用在存储量较大的系统中,如微机中的内存储器就 是采用DRAM。

5.3.1 掩模ROM 掩模ROM 的信息是在芯片制造时由厂家写入的,一旦成为产

品,其信息是无法修改的。因此,掩模ROM 在出厂时内部存储 的数据就已经“固化”在里边了。当产量较少时,掩模ROM 的 成本很高,但如果是批量生产则相当便宜。所以掩模ROM 总是 用来存放不需要修改的程序或数据。

(2) D0~D7:8 根双向数据线。对SRAM 芯片来讲,数据线 的根数决定了芯片上每个存储单元的二进制位数,8 根数据线 说明6264 芯片的每个存储单元中可存储8位二进制数,即每个 存储单元有8 位。使用时,这8根数据线与系统的数据总线相连。 当CPU 存取芯片上的某个存储单元时,读出和写入的数据都通 过这8 根数据线传送。 (3) 控制线: ■ OE:输出允许信号。只有当OE为低电平时,CPU 才能从 芯片中读出数据。 ■ WE 写允许信号。当WE 为低电平时,允许数据写入芯片。 当WE 为高电平,OE为低电平时,允许数据从芯片中读出。

第5章 存储器(讲义)

1第5章 存储器存储器概述5.1半导体存储芯片与CPU的连接5.28088系统的存储器接口5.48086系统的存储器接口5.58086/8088的存储器组织5.325.1 存储器概述存储器(Memory)是用来存储程序和数据的部件,是计算机系统中必不可少的组成部分。

从与CPU的关系来看,可分为内存和外存。

内存通常由半导体存储器组成,它直接与CPU的外部总线相连,是计算机主机的组成部分,用来存放当前正在执行的数据和程序,是本章主要讨论的内容。

外存位于主机外面,它通过接口电路与主机相连接,是作为计算机的外部设备来配置的。外存用来存放暂时不用的那些程序和数据,使用时必须先调入内存才能执行。

CPUCACHE主存(内存)辅存(外存)

35.1 存储器概述CPURAMROM打印机磁盘显示器键盘地址总线数据总线控制总线READ/WRITE主存45.1 存储器概述半导体存储器的分类5.1.1典型的半导体存储器芯片5.1.3半导体存储器芯片的结构5.1.2

55.1.1 半导体存储器的分类随机存取存储器1只读存储器26图5.1 半导体存储器的分类71.随机存取存储器RAM存储器中的信息既可以读又可以写。RAM中的信息在掉电后立即消失,是一种易失性存储器(volatile memory)。分为:静态RAM(SRAM)动态RAM(DRAM)81)静态RAM(SRAM)SRAM:Static Random Access Memory利用触发器的两个稳定状态表示“1”和“0”,最简单的TTL电路组成的SRAM存储单元由两个双发射极晶体管和两个电阻构成的触发器电路组成;而MOS管组成的SRAM存储单元由6个MOS管构成的双稳态触发电路组成。

只要电源不掉电,写入SRAM的信息就不会丢失。同时对SRAM进行读操作时不会破坏原有信息。

SRAM一般采用“字结构”存储矩阵:每个存储单元存放多位(4、8、16等)。