数字逻辑设计第三版第四章答案

数字逻辑与数字系统设计习题参考答案

(4)(0.785)10=(0.011110000101)8421BCD

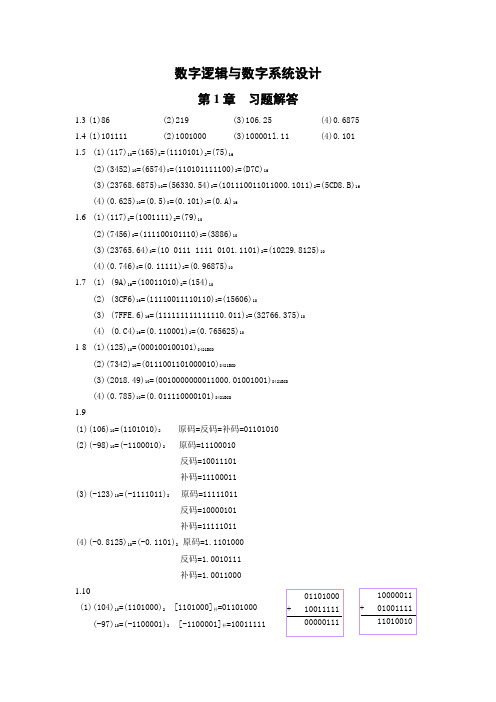

1.9

(1)(106)10=(1101010)2原码=反码=补码=01101010

(2)(-98)10=(-1100010)2原码=11100010

不考虑无关项,化简后的表达式:

F=

按考虑无关项化简结果绘制的逻辑电路习题4.10图(a)所示:

习题4.10图(a)

按不考虑无关项化简结果绘制的逻辑电路如习题4.10图(b)所示

习题4.10图(b)

4.11解:这是一个优先编码器的问题,设特快为A,直快为B,慢车为C,没有开车要求,输出为0,若A要求开车则输出,1,B要求开车输出为2,C要求开车输出3,根据A-B-C的优先顺序列功能表如下:

4.6解:根据题意:F= ,所以,可绘制电路如习题4.6图所示

习题4.6图

4.7解:根据题意:F= ,所以,可绘制电路如习题4.7图所示

习题4.7图

4.8解:

习题4.8图

4.9解:根据题意,三个变量有两个为1的卡诺图如习题4.9图(a)所示:

习题4.9图(a)

由此可列出逻辑表达式为:F= ,根据逻辑表达式可绘制逻辑电路习题4.9图(b)所示:

输入

输出

A

B

C

T1

T0

0

0

0

0

0

0

0

1

1

1

0

1

0

1

0

0

1

1

1

0

1

0

0

0

1

1

0

数字电子技术第4章组合逻辑电路习题解答

习题4.1写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。

习题4.1图解:B A B A B A B A B A F ⊕=+=+= 该电路实现异或门的功能4.2分析图所示电路,写出输出函数F 。

习题4.2图解:[]B A B BB A F ⊕=⊕⊕⊕=)(4.3已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟.图解:B A B A B A AB B AB A AB B AB A F ⊕=•=•••=•••=4.4由与非门构成的某表决电路如图所示。

其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。

(1) 试分析电路,说明决议通过的情况有几种。

(2) 分析A 、B 、C 、D 四个人中,谁的权利最大。

习题4.4图解:(1)ABD BC CD ABD BC CD L ++=••=B AC & && & D L B A =1 =1=1FF A B & &&& & F B A(3)4.5分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

习题4.5图解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕•⊕= (2)4.6试分析图所示电路的逻辑功能。

习题4.6图解:(1)ABC C B A F )(++=10电路逻辑功能为:“判输入ABC 是否相同”电路。

4.7已知某组合电路的输入A 、B 、C 和输出F 的波形如下图所示,试写出F 的最简与或表达式。

习题4.7图解:(1)根据波形图得到真值表:C AB BC A C B A F ++=4.8、设∑=)14,12,10,9,8,4,2(),,,(m D C B A F ,要求用最简单的方法,实现的电路最简单。

1)用与非门实现。

2)用或非门实现。

3) 用与或非门实现。

《数字电路与系统设计》第4章习题答案

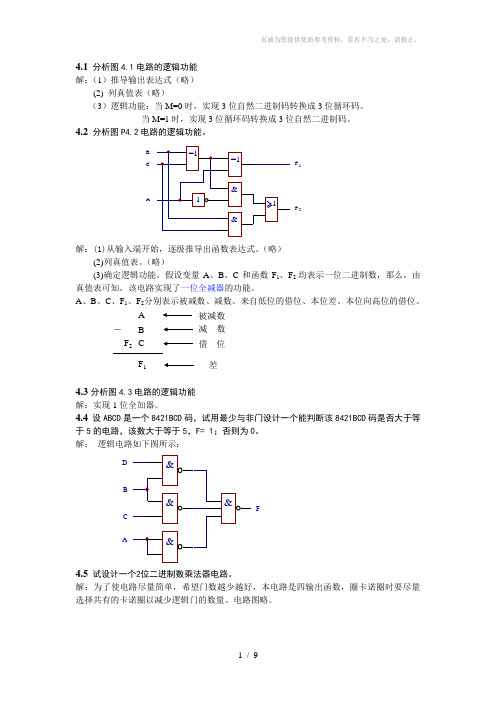

4.1分析图4.1电路的逻辑功能解:(1)推导输出表达式(略)(2) 列真值表(略)4.6 试设计一个将8421BCD 码转换成余3码的电路。

解: 电路图略。

4.7 在双轨输入条件下用最少与非门设计下列组合电路: 解:略4.8 在双轨输入信号下,用最少或非门设计题4.7的组合电路。

解:将表达式化简为最简或与式:(1)F=(A+C)(⎺A+B+⎺C)= A+C+⎺A+B+⎺C(2)F=(C+⎺D)(B+D)(A+⎺B+C)= C+⎺D+B+D+A+⎺B+C(3)F=(⎺A+⎺C)(⎺A+⎺B+⎺D)(A+B+⎺D)= ⎺A+⎺C+⎺A+⎺B+⎺D+A+B+⎺D(4)F=(A+B+C)(⎺A+⎺B+⎺C)= A+B+C+⎺A+⎺B+⎺C 4.9 已知输入波形A 、B 、C 、D ,如图P4.4所示。

采用与非门设计产生输出波形如F 的组合电路。

解: F=A ⎺C+⎺BC+C ⎺D 电路图略4.10 电话室对3种电话编码控制,按紧急次序排列优先权高低是:火警电话、急救电话、普通电话,分别编码为11,10,01。

试设计该编码电路。

解:略4.11 试将2/4译码器扩展成4/16译码器 解:A 3A 2A 1 A 0⎺Y 0⎺Y 1⎺Y 2⎺Y 3 ⎺Y 4 ⎺Y 5⎺Y 6⎺Y 7 ⎺Y 8⎺Y 9⎺Y 10⎺Y 11 ⎺ Y 12⎺Y 13⎺Y 14⎺Y 15A 1 ⎺EN ⎺Y 3A 0 2/4 ⎺Y 2译码器 ⎺Y 1⎺Y 0⎺EN A 1 2/4(1)A 0 ⎺Y 0⎺Y 1⎺Y 2⎺Y 3⎺EN A 1 2/4(2) A 0 ⎺Y 0⎺Y 1⎺Y 2⎺Y 3 ⎺EN A 1 2/4(3) A 0 ⎺Y 0⎺Y 1⎺Y 2⎺Y 3 ⎺EN A 1 2/4(4) A 0 ⎺Y 0⎺Y 1⎺Y 2⎺Y 34.12试用74138设计一个多输出组合网络,它的输入是4位二进制码ABCD,输出为:F1:ABCD是4的倍数。

数字电路与逻辑设计第四章组合逻辑电路

第四章 组合逻辑电路

设计的一般过程:

●建立给定问题的逻辑描述 ●求出逻辑函数的最简表达式 ●选择器件并对表达式变换 ● 画出逻辑电路图

弄清楚变量及函数,得 到描述给定问题的逻辑 表达式。求逻辑表达式 有两种常用方法,即真

值表法和分析法。

求出描述设计问题的 最简表达式,使逻辑电路 中包含的逻辑门最少且连 线最少。

令: 逻辑变量A、B、C --- 分别代表参加表决的3个成员, 并约定逻辑变量取值为0表示反对,取值为1表示赞成;

逻辑函数 F---- 表示表决结果。F取值为0表示被否定,F 取值为1表示通过。

按照少数服从多数的原则可知,函数和变量的关系是:当3 个变量A、B、C中有2个或2个以上取值为1时,函数F的值为1, 其他情况下函数F的值为0。

注意:在化简这类逻辑函数时,利无关项用随意性往往 可以使逻辑函数得到更好地简化,从而使设计的电路达到更 简!

第四章 组合逻辑电路

例 设计一个组合逻辑电路,用于判别以余3码表示的1 位 十进制数是否为合数。

解 设输入变量为ABCD,输出函数为 F,当ABCD表示 的十进制数为合数(4、6、8、9)时,输出F为1,否则F为0。

目的:了解给定逻辑电路的功能,评价设计方案的优劣, 吸取优秀的设计思想、改进和完善不合理方案等。

一般步骤:

第四章 组合逻辑电路

1.写出输出函数表达式 ;

2.输出函数表达式化简;

3.列出输出函数真值表 ;

4.功能评述 。

第四章 组合逻辑电路

1. 写出输出函数表达式

根据逻辑电路图写输出函数表达式时,一般从输入端开始 往输出端逐级推导,直至得到所有与输入变量相关的输出函数 表达式为止。

数字逻辑电路王秀敏第4章检测+习题答案100525

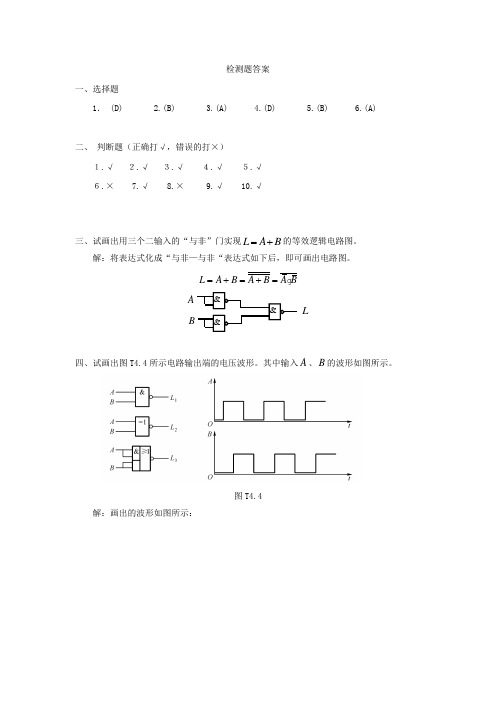

检测题答案一、选择题1. (D) 2.(B) 3.(A) 4.(D) 5.(B) 6.(A)二、判断题(正确打√,错误的打×)1.√2.√3.√4.√5.√6.× 7.√ 8.× 9.√ 10.√=+的等效逻辑电路图。

三、试画出用三个二输入的“与非”门实现L A B解:将表达式化成“与非—与非“表达式如下后,即可画出电路图。

L A B A B A B=+=+=四、试画出图T4.4所示电路输出端的电压波形。

其中输入A、B的波形如图所示。

图T4.4解:画出的波形如图所示:图A4.4五、 指出图T4-5所示电路的输出逻辑电平是高电平、低电平还 是高阻态。

已知图(a)中的门电路都是74系列的TTL 门电路,图(b)中的门电路为CC4000系列的CMOS 门电路。

图T4.5解: TTL 门电路的输入端悬空时,相当于高电平输入,输入端接有电阻时,其电阻阻值大于1.4k Ω时,该端也相当于高电平,电阻值小于0.8k Ω时,该端才是低电平。

而CMOS 逻辑门电路,输入端不管是接大电阻还是接小电阻,该端都相当于低电平(即低电位)。

所以有如下结论:(a) 1L 为低电平状态;2L 是低电平状态;3L 是高电平状态;4L 输出为高阻状态; (b) 1L 输出为高电平;2L 输出是低电平状态;3L 输出是低电平状态;第四章习题答案 题4.1填空题[1]任何时刻只能有一个三态门处于工作状态,而其它门则必须处于高阻态 [2]低 [3]下降,上升 [4]IHmin(VON)ILmax(VOFF),V V [5]OC题4.2 电路如图4.2(a)、(b)、(c)、(d)所示,试找出电路中的错误,并说明为什么。

图P4.2解 :图(a):电路中多余输入端接“1”是错误的,或门有一个输入为1,输出即为1。

图(b):电路中多余输入端接“0”电平是错误的,与门输入有一个为0,输出即为0。

图(c):电路中两个与门输出端并接是错误的,会烧坏器件。

数字逻辑与设计(詹瑾瑜)第四章2015

3、列出真值表 4、化简 F BC A 00 0 0 1 1

01 11 10 1 0 0 1 1 0

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

∑

S CO C S

=1

S=A B C=AB

&

C

27

二、全加器(Full Adder) 1、用逻辑门构成全加器 Ai Bi Ci-1 Si Ci 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 1 0 1 0 0 0 0 0 1 0 1 1 Ai Bi Ci-1

Si

Ci

31

2、集成全加器 集成全加器74183的引脚图如下所示:

Vcc 2Ai 2Bi 2Ci-1 2Ci 14 13 12 11 10 9 2Si 8 7

74183

1 1Ai 2 3 4 5 6 1Bi 1Ci-1 1Ci 1Si GND

这种双全加器具有独立的全加和与进位输出,这 样每个全加器既可单独使用也可级连起来使用。

17

B4 0 0 0 0 0 0 0 0

B3 B2 B1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

F 1 0 0 0 0 1 0 0

B4 B 3 1 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1

B2 B1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1

18

F 0 0 1 0 0 0 0 1

数字电路逻辑设计第四章【可编辑PPT】

★74LS148 8-3线优先编码器 应用2

用编码器构成A/D转换器

图4.15为74LS148构 成的A/D转换器。这个 电路主要由比较器、寄 存器和编码器3部分组成。

输入信号(模拟电压), 同时加到7个比较器的反 相端,基准电源经串联 电阻分压为8级,量化单 位q=UR/7,各基准电压 分别加到比较器的同相 端。

Y S I0 N I1 N I2 N I3 N I4 N I5 N I6 N I7 N ST YEXYS ST

8线–3线优先编码器真值表如下表所示(反码形式)

输入

输出

ST IN 0 IN 1 IN 2 IN 3 IN 4 IN 5 IN 6 IN 7

Y 2 Y 1 Y 0 Y EX Y s

0 1 2 3 4 5 6 7 EN

HPRI/BIN 低位片

YS

Y0

Y1

Y2

YEX

0 1 2 3 4 5 6 7 EN

HPRI/BIN 高位片

YS

Y0

Y1

Y2

YEX

&

&

&

Y0

Y1

Y2

&

Y3

YEX

中规模优先编码器

常用的中规模优先编码器有: 8线-3线优先编码器:CT54148/CT74148、 CT54LS148/CT74LS148、CC4532 10线-4线优先编码器:CT54147/CT74147、 CT54LS147/CT74LS147、CC40147

74LS148是8-3线优先编码器

74LS148编码器功能表

输入

EI I7 I6 I5 I4 I3 I2 I1 I0

1 XXXXXXXX 0 1 1 1 1 1 11 1 0 0 XXXXXXX 0 1 0 XXXXXX 0 1 1 0 XXXXX 0 1 1 1 0 XXXX 0 1 1 1 1 0 XXX 0 1 1 1 1 1 0 XX 01111110X 011111110

数字电路第四章答案

数字电路第四章答案【篇一:数字电路答案第四章时序逻辑电路2】p=1,输入信号d被封锁,锁存器的输出状态保持不变;当锁存命令cp=0,锁存器输出q?d,q=d;当锁存命令cp出现上升沿,输入信号d被封锁。

根据上述分析,画出锁存器输出q及 q的波形如习题4.3图(c)所示。

习题4.4 习题图4.4是作用于某主从jk触发器cp、j、k、 rd及 sd 端的信号波形图,试绘出q端的波形图。

解:主从jk触发器的 rd、且为低有效。

只有当rd?sd?1 sd端为异步清零和复位端,时,在cp下降沿的作用下,j、k决定输出q状态的变化。

q端的波形如习题4.4图所示。

习题4.5 习题4.5图(a)是由一个主从jk触发器及三个非门构成的“冲息电路”,习题4.5图(b)是时钟cp的波形,假定触发器及各个门的平均延迟时间都是10ns,试绘出输出f的波形。

cpf cp100ns10nsq(a)f30ns10ns(b)(c)习题4.5图解:由习题4.5图(a)所示的电路连接可知:sd?j?k?1,rd?f。

当rd?1时,在cp下降沿的作用下,且经过10 ns,状态q发生翻转,再经过30ns,f发生状态的改变,f?q。

rd?0时,经过10ns,状态q=0。

根据上述对电路功能的分析,得到q和f的波形如习题4.5图(c)所示。

习题4.6 习题4.6图(a)是一个1检出电路,图(b)是cp及j端的输入波形图,试绘出 rd端及q端的波形图(注:触发器是主从触发器,分析时序逻辑图时,要注意cp=1时主触发器的存储作用)。

cpj(a)qd(c)cp j(b)习题图解:分析习题4.6图(a)的电路连接:sd?1,k?0,rd?cp?q;分段分析习题4.6图(b)所示cp及j端信号波形。

(1)cp=1时,设q端初态为0,则rd?1。

j信号出现一次1信号,即一次变化的干扰,且k=0,此时q端状态不会改变;(2)cp下降沿到来,q端状态变为1,rd?cp,此时cp=0,异步清零信号无效;(3)cp出现上升沿,产生异步清零信号,使q由1变为0,在很短的时间里 rd又恢复到1;(4)同理,在第2个cp=1期间,由于j信号出现1信号,在cp下降沿以及上升沿到来后,电路q端和 rd端的变化与(2)、(3)过程的分析相同,其波形如习题4.6图(c)所示。

胡全连版数字逻辑第4章习题解答

习题四参照答案同步 RS触发器的输入波形见下列图,试对应画出Q 端的波形。

设初态为“0”。

CPRS图解:CPRSQ已知电路及输入端A、B,时钟 CP的波形以下图,试画出输出端Q 的波形,图中JK 触发器为边缘型触发器,初始状态为0。

AB=1&J Q CPF2AK Q BCP图解:写出 J、 K 与触发器的方程J=A⊕ B,K=AB Q n+1=J Q n+k Q nCPABJKQ试写出下边图触发器的次态方程。

Q QDI CI≥ 1&&&AB1A B( a)图(b)解:写出触发器的方程(a)Q n+1=A Q n+B Q n(b)Q n+1= D = B+A Q n,剖析以下图电路,说明电路的逻辑功能。

&Z&X T1Q1T2Q2C CCP图解:写出触发器的方程T1 =X,T2=Q1n X, Z=XQ1n Q2n电路的状态方程1n+111n1nQ= T⊕Q =X⊕QQ2n+1= T2⊕ Q2n= ( Q1n X)⊕ Q2n列状态表现态次态Q1 n+1 2 n+1/输出 ZQn nX=0X=1Q1Q2000 0/0 1 0/0010 1/0 1 1/010 1 0/00 1/011 1 1/00 0/1作状态图0/00/01/0011/11/010/00/001功能描绘:该电路在X=1 时作四进制的减 1 计数, X=0 时不改动。

已知电路及输入端M ,时钟 CP 的波形以下图,试画出输出端Q1、Q1发器初态均为 1。

Q1 CP MDQMF1QCP图解:写出触发器的方程D1=M ,1n,D2= Q电路的状态方程:Q1n+1= D1 =M, Q2n+1= D2= Q1n,时钟 CP上↑有效。

列状态表现态次态 Q2n+1 Q1n+1Q2n Q1n M=0M=1000010010010100111110111画出输出端Q2、 Q1的波形,设触发器初态均为1。

的波形,设触Q2 DQF2QCPMQ2Q1剖析图所示时序逻辑电路。

数字逻辑电路与系统设计习题答案

第1章习题及解答将下列二进制数转换为等值的十进制数。

(1)(11011)2 (2)()2(3)(1101101)2 (4)()2(5)()2(6)()2(7)()2(8)()2题解:(1)(11011)2 =(27)10 (2)()2 =(151)10(3)(1101101)2 =(109)10 (4)()2 =(255)10(5)()2 =()10(6)()2 =()10(7)()2=()10(8)()2 =()10将下列二进制数转换为等值的十六进制数和八进制数。

(1)(1010111)2 (2)(1)2(3)()2 (4)()2题解:(1)(1010111)2 =(57)16 =(127)8(2)(0)2 =(19A)16 =(632)8(3)()2 =()16 =()8(4)()2 =(2C.61)16 =()8将下列十进制数表示为8421BCD码。

(1)(43)10 (2)()10(3)()10 (4)()10题解:(1)(43)10 =(01000011)8421BCD(2)()10 =(.00010010)8421BCD(3)()10 =()8421BCD(4)()10 =(.0001)8421BCD将下列有符号的十进制数表示成补码形式的有符号二进制数。

(1) +13 (2)−9 (3)+3 (4)−8题解:(1) +13 =(01101)2(2)−9 =(10111)2(3) +3 =(00011)2(4)−8 =(11000)2用真值表证明下列各式相等。

(1)BA+=+B+BBAA(2)()()()=⊕A⊕CACABB(3)()C BA+=+BCA(4)CAB++A=AABC题解:(1)证明BA+=++BABBA(2)证明()()()ACABCBA⊕=⊕(3)证明()C BACBA+=+(4)证明CAB++=AACBA用逻辑代数公式将下列逻辑函数化成最简与或表达式。

(1)D++A=F+BCBCACA(2)()()D++=F+AACCDA(3)()()B++F+=B+DCDBDDA(4)()D++F+=ADCBCBA(5)()C A B C B AC F ⊕++= (6)()()C B B A F ⊕⊕= 题解:(1)BC A D C A BC C A B A F +=+++= (2)()()CD A D CD A C A A F +=+++=(3)()()C B B A D B D A C B D D D B F ++=++++= (4)()D C B A D C B AD C B A F +=+++= (5)()C B AC C A B C B AC F +=⊕++=(6)()()C A BC B A C B B A F ++=⊕⊕=或C A C B AB ++= 用卡诺图将下列逻辑函数化成最简与或表达式。