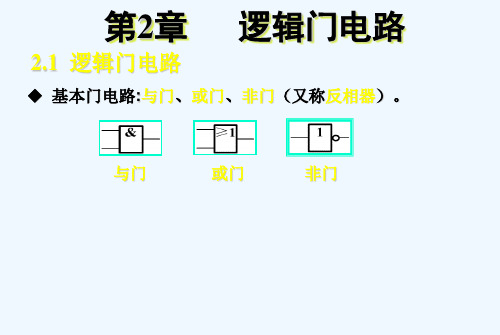

基本门电路逻辑符号

各种门电路、逻辑符号、逻辑表达式、真值表

各种门电路、逻辑符号、逻辑表达式、真值表1.二极管门电路1)二极管与门电路电路、逻辑符号、逻辑表达式、真值表逻辑表达式:Y=A•B或AB真值表Y A B00111112)二极管或门电路电路、逻辑符号、逻辑表达式、真值表逻辑表达式:Y=A+B真值表Y A B0011111112.C M O S门电路1)C M O S反相器电路及逻辑表达式YCMOS反相器逻辑功能:输入、输出状态相反;逻辑表达式:Y=A'.输入端噪声容限2)C M O S与非门电路及逻辑表达式3)C M O S或非门电路及逻辑表达式)(' =AB Y4)带缓冲级的C M O S门电路B=ABAY+'((')())='''5)漏极开路输出的门电路(O D 门)、逻辑符号及逻辑功能、应用(2)实现输出电平的变换OD 门)('=AB Y (1)“线与”的实现输出端逻辑式为:6)C M O S 传输门电路结构及逻辑符号7)几种常见的三态输出C M O S 门电路 三态反相器C =0, C '=1时传输门截止,高阻态,输出v o =0。

C =1, C '=0时传输门导通,输出v o =v I 。

3 –1–273.T T L门电路1)三极管反相器2)T T L反相器的电路结构和逻辑功能只要参数选择合理,当v I=V IL时,T截止,输出v O=V OH为高电平;当v I=V IH时,T饱和导通,输出v O=V OL为低电平.即:Y=A'则输出和输入的逻辑关系为:AY'=3)扇出系数(F a n -o u t )的计算4)输入端的负载特性OL(max)IL 1I I N ≤IL OL(max)1I I N ≤OH(max)IH 2I I N ≤IHOH(max)2I I N ≤则取N =min {N 1, N 2} 故一般对于TTL 门电路,若输入端通过电阻接地,一般: **➀当R P ≤0.7K Ω时,构成低电平输入方式; ➁当R P ≥1.5K Ω时,构成高电平输入方式。

与或非门电路

工作原理 请自行分析

2.3 门电路综合应用

例1: 由于检测危险的报警器自身也可能出现差错,因此为提高 报警信号的可靠性,在每个关键部位都安置了三个同类型的危 险报警器,如下图所示。只有当三个危险报警器中至少有两个 指示危险时,才实现关机操作。这就是三选二电路。 1) 根据题意作出真值表

2.3.1 三选二电路

1. TTL系列数字电路分类 小规模集成电路集成 2. TTL 系列数字电路的主要参数指标 中、大规模集成电路的集 ◆按集成度大小分类 成度比较高,大多数是一些具 度比较低,大多数是 3. TTL与非门输入特性和输出特性 有特定逻辑功能的逻辑电路。 小规模集成电路 与门、或门、与非门、 其中包括:加法器、累加器、 中规模集成电路 或非门、与或非门、反相 乘法器、比较器、奇偶发生器/ 器、三态门、锁存器、触 校验器、算术运算器、多(四、 大规模集成电路 六、八)触发器、寄存器堆、 发器、单稳态、多谐振荡 器; 超大规模的集成电路。 时钟发生器、码制转换器、数 据选择器/多路开关、译码器/ ◆按逻辑功能分类 以及一些扩展门、缓 分配器、显示译码器/驱动器、 ◆按国家标准分类 冲器、驱动器等比较基本、 位片式处理器片、异步计数器、 CV54/74系列 同步计数器、A/VD和VD/A转 简单、通用的数字逻辑单 换器、随机存取器( RAM)、 元电路。 CV54/74H系列 只读存储器 可以根据电路设计需 ( ROM/PROM/EPROM/EEP CV54/74S系列 要利用手册从中选择适用 ROM)、处理机控制器和支持 的电路构成所需的各种数 功能器件等。 CV54/74LS系列

2.4.2 其他常用TTL门电路 2.4.3 常用CMOS门电路

2.4 常用IC门简介 TTL系列数字电路的主要参数指标 (1)高电平输出电压VOH:2.7 ~ 3.4V (2)高电平输出电流I0H: (3)低电平输出电压VOL:0.2 ~ 0.5V (4)低电平输出电流IOL (5)高电平输入电压VIH:一般为2V (6)高电平输入电流IIH (7)低电平输入电压VIL:一般为0.8V

三个基本门电路代数式,图符号及真值表

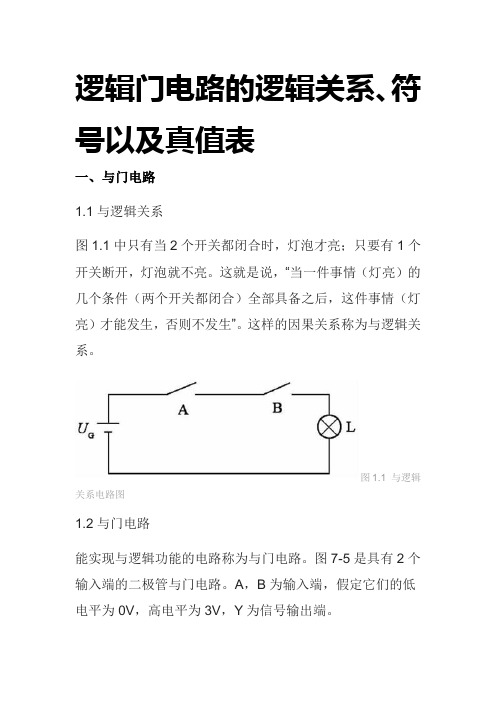

逻辑门电路的逻辑关系、符号以及真值表一、与门电路1.1与逻辑关系图1.1中只有当2个开关都闭合时,灯泡才亮;只要有1个开关断开,灯泡就不亮。

这就是说,“当一件事情(灯亮)的几个条件(两个开关都闭合)全部具备之后,这件事情(灯亮)才能发生,否则不发生”。

这样的因果关系称为与逻辑关系。

图1.1 与逻辑关系电路图1.2与门电路能实现与逻辑功能的电路称为与门电路。

图7-5是具有2个输入端的二极管与门电路。

A,B为输入端,假定它们的低电平为0V,高电平为3V,Y为信号输出端。

图1.2与门电路(1) 当A,B都处于低电平0V时,二极管VD1,VD2同时导通,Y=0V,输出低电平。

(忽略二极管的正向压降,下同)。

(2) 当A=0V,B=3V时,VD1优先导通,Y被箝位在0V,VD2反偏而截止。

(3) 当A=3V,B=0V时,VD2优先导通,Y被箝位在0V,VD1反偏而截止。

(4) 当A,B都处在高电平3V时,VD1与VD2均截止,Y 端输出高电平(即3V)。

与逻辑关系的逻辑函数表达式为Y=A*B。

表1.1是与门真值表,从真值表可以看出,与门电路的逻辑功能是“有0出0,全1出1”。

与门的逻辑符号如图1.3所示。

表1.1 与门真值表图1.3与门的逻辑符二、或门电路2.1或逻辑关系图2.1中电路由2个开关和灯泡组成。

由图可知,在决定一件事情的各种条件中,至少具备一个条件,这件事情就会发生,这种因果关系称为或逻辑关系。

图2.1 或逻辑关系电路图2.2或门电路能实现或逻辑关系的电路称为或门电路。

图2.2所示为具有2个输入端的二极管或门电路。

图2.2 或门电路真值表见表2.1,从真值表可以看出,或门的逻辑功能为“有1出1,全0出0”。

或门的逻辑符号如图2.3所示。

表2.1 或门真值表图2.3 或门逻辑符号三、非门电路(反相器)3.1非逻辑关系如图3.1开关与灯泡并联,当开关断开时,灯亮;开关闭合时,灯不亮。

这就是说,“事情(灯亮)和条件(开关)总是呈相反状态”,这种关系称为非逻辑关系。

基本门电路逻辑符号

1、基本门电路逻辑符号:1与门(And)或门(OR)非门(not)与非门(nand)或非门(nor)与或非(xor)2、Quartus II是Altera公司新一代的EDA设计工具,由该公司早先的MAXPLUSII演变而来,3、Quartus II集成开发环境的设计流程设计输入约束输入综合布局布线时序分析仿真器件编程与配置4、可编程逻辑器件PLD:低密度可编程逻辑器件(LDPLD)高密度可编程逻辑器件(HDPLD)5、EDA中文意思:电子设计自动化,由Electronic、Design、Automation。

6、HDL中文意思:硬件描述语言,由Hardware、Description、Language。

7、一个电路的HDL模块定义由:关键字module+名字开始,以endmodule结束8、一个电路的HDL模块声明由:模块名字和模块输入输出端口列表。

9、模块的端口类型有:输入端口(input)、输出端口(output)、输入/输出双向端口(inout)。

10、变量类型:wire线网型、 reg寄存器型、 memory寄存器型。

11、由持续赋值语气Assign赋值的变量必须定义:Wire类型12、在Always过程语句中被赋值变量必须定义为:reg类型13、在模块的端口声明部分如何说明总线型多位信号的位宽。

Wire[7:0] data;//说明一个8位数据总线data为wire型;Wire[31:0]adder;//说明一个32位地址总线adder为wire型。

14、wire类型变量和reg类型变量差别是什么?除了表示组合逻辑电路中的连接线,reg型变量还可以在时序电路中对应具有状态保持作用电路元件,根本区别就在于:reg型变量在定义时默认的初始值为不定值x,在设计时要求放在always过程语句内部通过过程赋值语句赋予明确的值。

如果寄存器变量没有得到新的赋值,它将一直保持原有的值不变。

15、LED数码管中分为:共阴极和共阳极。

常用逻辑门电路逻辑符号与功能

常用逻辑门电路逻辑符号与功能最常用的集成门电路有TTL系列集成规律门和CMOS系列集成规律门两大类。

就其功能而言,常用的有与门、或门、非门、与非门、或非门、与或非门、异或门以及集电极开路(OC)门、三态(TS)门等。

表1给出了常用规律门的规律符号与功能。

表1 常用规律门的规律符号与功能名称符号表达式名称符号表达式与门F=A·B与或非门或门F=A+B 异或门非门同或门与非门OC与非门输出端可以对接或非门三态与非门EN为使能掌握1.外部特性参数集成规律门的主要外部特性参数有输出高、低规律电平,开门电平,关门电平,扇入系数,扇出系数,输入短路电流,输入漏电流,平均传输时延和空载功耗等。

2.集成门电路的应用特点(1)在进行规律设计时,各类规律门可实现与其对应的规律运算功能。

(2)OC门的输出端可以直接连接,实现“线与”,此外可实现电平转换和直接驱动发光二极管等。

(3)TS门主要用于总线传送,多个TS门的输出端可以直接与总线连接,实现数据分时传送。

(4)用规律门组成实际电路时,对集成门的多余输入端必需恰当处理。

例如,TTL与门和与非门的多余输入端可以通过电阻接电源,或门和或非门的多余输入端可以通过电阻接“地”。

CMOS与门和与非门的多余输入端可以直接与电源相接;CMOS或非门的多余输入端可接“地”等。

总之,既要避开多余输入端悬空造成信号干扰,又要保证对多余输入端的处置不影响正常的规律功能。

3.常用TTL集成门电路芯片(1)集成与非门电路芯片常用的TTL与非门集成电路芯片有7400、7410和7420等。

7400是一种内部有四个两输入与非门的芯片,其引脚安排图如图1(a)所示;7410是一种内部有三个三输入与非门的芯片,其引脚安排图如图1(b)所示;7420是一种内部有两个四输入与非门的芯片,其引脚安排图如图1(c)所示。

图中,VCC为电源引脚,GND为接地脚,NC为空脚。

图1 与非门7400、7410和7420的引脚安排图。

基本逻辑门电路的符号和功能

基本逻辑门电路的符号和功能嘿,朋友们!今天咱们来唠唠基本逻辑门电路,那可真是数字世界里的奇妙小玩意儿。

先来说说与门吧。

与门就像是个超级挑剔的美食评委。

你想啊,它有好几个输入端口,就好比是摆在评委面前的一道道菜肴。

只有当所有的输入端口都输入高电平,也就是相当于所有菜肴都达到了评委超级严苛的标准时,它才会输出高电平,就像评委才会给出好评一样。

要是有一个输入端口是低电平,就如同有一道菜不合格,那它就会毫不留情地输出低电平,真是个一丝不苟的家伙呢。

或门就完全不一样啦。

或门像是个超级乐观的购物狂。

只要它的输入端口里有一个是高电平,就好比在一堆商品里只要看到有一个喜欢的,就会兴奋地输出高电平。

不管其他输入是啥样,只要有一个能让它心动的,它就满足了,完全不会像与门那样挑三拣四。

非门呢,那可是个叛逆的小机灵鬼。

它只有一个输入端口,就像是个总是和你唱反调的小伙伴。

你给它一个高电平,它就偏要输出低电平,你给它低电平,它又调皮地输出高电平,就像你说东它往西,总是和你对着干,不过也正是这种独特的“叛逆”,让它在逻辑电路里有着不可或缺的地位呢。

还有个异或门。

这异或门像是在玩一种特别的猜谜游戏。

如果它的两个输入端口的电平不一样,就像谜底和谜面不一样,那它就输出高电平,就像是猜中了谜底一样兴奋。

但要是两个输入端口电平相同,就像谜面和谜底一样,那它就输出低电平,感觉有点小失落呢。

这些逻辑门电路组合在一起呀,就像一群性格各异的小伙伴凑在一起搞事情。

它们能构建出超级复杂的电路,就像小伙伴们齐心协力搭建一个超级巨大又神奇的积木城堡。

从简单的计算器到超级复杂的计算机系统,都离不开这些逻辑门电路的功劳。

它们虽然小小的,却有着大大的能量,就像那些看似不起眼却有着非凡本领的超级英雄一样。

它们就像数字世界里的小精灵,在电路的世界里欢快地跳动着。

每一个逻辑门电路都有着自己独特的个性和功能,它们相互配合,共同演绎着数字电路的精彩大戏。

如果没有它们,咱们现在的数字生活可就要乱套啦,就像一场没有演员的戏剧,那得多无趣呀。

基本逻辑门符号

基本逻辑门符号

基本逻辑门符号主要有以下几种:

1. 与门(AND Gate):使用符号"&"表示。

当输入信号都为1时,输出为1,否则输出为0。

2. 或门(OR Gate):使用符号"|"表示。

当输入信号至少有一

个为1时,输出为1,否则输出为0。

3. 非门(NOT Gate):使用符号"~"表示。

当输入信号为1时,输出为0;当输入信号为0时,输出为1。

4. 异或门(XOR Gate):使用符号"^"表示。

当输入信号仅有

一个为1时,输出为1,否则输出为0。

5. 与非门(NAND Gate):使用符号"⊼"表示。

与门的输出取反。

6. 或非门(NOR Gate):使用符号"↓"表示。

或门的输出取反。

7. 异或非门(XNOR Gate):使用符号"⊕"表示。

异或门的输

出取反。

这些符号在逻辑电路图中用于表示不同的逻辑运算。

实用文库汇编之基本逻辑门电路符号-各种逻辑门的电路符号

*实用文库汇编之基本逻辑门电路符号1、与逻辑(AND Logic)与逻辑又叫做逻辑乘,下面通过开关的工作状况加以说明与逻辑的运算。

*从上图可以看出,当开关有一个断开时,灯泡处于灭的状况,仅当两个开关同时合上时,灯泡才会亮。

于是我们可以将与逻辑的关系速记为:“有0出0,全1出1”。

图(b)列出了两个开关的所有组合,以及与灯泡状况的情况,我们用0表示开关处于断开状况,1表示开关处于合上的状况;同时灯泡的状况用0表示灭,用1表示亮。

图(c)给出了与逻辑门电路符号,该符号表示了两个输入的逻辑关系,&在英文中是AND的速写,如果开关有三个则符号的左边再加上一道线就行了。

逻辑与的关系还可以用表达式的形式表示为:F=A·B上式在不造成误解的情况下可简写为:F=AB。

2、或逻辑(OR Logic)上图(a)为一并联直流电路,当两只开关都处于断开时,其灯泡不会亮;当A,B两个开关中有一个或两个一起合上时,其灯泡就会亮。

如开关合上的状况用1表示,开关断开的状况用0表示;灯泡的状况亮时用1表示,不亮时用0表示,则可列出图(b)所示的真值表。

这种逻辑关系就是通常讲的“或逻辑”,从表中可看出,只要输入A,B两个中有一个为1,则输出为1,否则为0。

所以或逻辑可速记为:“有1出1,全0出0”。

上图(c)为或逻辑门电路符号,后面通常用该符号来表示或逻辑,其方块中的“≥1”表示输入中有一个及一个以上的1,输出就为1。

逻辑或的表示式为:F=A+B3、非逻辑(NOT Logic)非逻辑又常称为反相运算(Inverters)。

下图(a)所示的电路实现的逻辑功能就是非运算的功能,从图上可以看出当开关A合上时,灯泡反而灭;当开关断开时,灯泡才会亮,故其输出F的状况与输入A的状相反。

非运算的逻辑表达式为图(c)给出了非逻辑门电路符号。

>复合逻辑运算在数字系统中,除了与运算、或运算、非运算之外,常常使用的逻辑运算还有一些是通过这三种运算派生出来的运算,这种运算通常称为复合运算,常见的复合运算有:与非、或非、与或非、同或及异或等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、基本门电路逻辑符号:1与门(And)或门(OR)非门(not)与非门(nand)或非门(nor)与或非(xor)2、Quartus II是Altera公司新一代的EDA设计工具,由该公司早先的MAXPLUS II演变而来,3、Quartus II集成开发环境的设计流程设计输入约束输入综合布局布线时序分析仿真器件编程与配置4、可编程逻辑器件PLD:低密度可编程逻辑器件(LDPLD)高密度可编程逻辑器件(HDPLD)5、EDA中文意思:电子设计自动化,由Electronic、Design、Automation。

6、HDL中文意思:硬件描述语言,由Hardware、Description、Language。

7、一个电路的HDL模块定义由:关键字module+名字开始,以endmodule结束8、一个电路的HDL模块声明由:模块名字和模块输入输出端口列表。

9、模块的端口类型有:输入端口(input)、输出端口(output)、输入/输出双向端口(inout)。

10、变量类型:wire线网型、 reg寄存器型、 memory寄存器型。

11、由持续赋值语气Assign赋值的变量必须定义:Wire类型12、在Always过程语句中被赋值变量必须定义为:reg类型13、在模块的端口声明部分如何说明总线型多位信号的位宽。

Wire[7:0] data;//说明一个8位数据总线data为wire型;Wire[31:0]adder;//说明一个32位地址总线adder为wire型。

14、wire类型变量和reg类型变量差别是什么?除了表示组合逻辑电路中的连接线,reg型变量还可以在时序电路中对应具有状态保持作用电路元件,根本区别就在于:reg型变量在定义时默认的初始值为不定值x,在设计时要求放在always过程语句内部通过过程赋值语句赋予明确的值。

如果寄存器变量没有得到新的赋值,它将一直保持原有的值不变。

15、LED数码管中分为:共阴极和共阳极。

16、阻塞式blocking的操作符“ = ”非阻塞式non-blocking的操作符“ <= ”阻塞赋值和非阻塞赋值的基本区别是:阻塞赋值是顺序执行语句,而非阻塞赋值是并行执行语句。

两种语句的含义不同,建模的应用也就不同。

17、2选1选择器 p20 2选1数据选择器 p64module A(P0,P1,S,F);input P0,P1,S;output F;reg F;always@( P0 OR P1 OR S) beginif(S==1’b0)F=P0;elseF=P1;endendmodule18、1对2数据分配器 p22 module A(S,D,Y0,Y1);input S,D;output Y0,Y1F;assign Y0=D*(~S);assign Y1=D*S;endmodule19、三人表决器 p107 module A(b1,b2,b3,u);input b1,b2,b3;output u;wire[1:0] B;assign B=b1+b2+b3;assign u=(B>=2)?1:0;endmodule20、七段LED数码管显示电路 p163module qiduan(data_in,//七段数码管显示电路的输入,对应图2.1.4中的in3-in0,in3对应输入的高位data_out);//七段数码管显示电路的输出,对应图2.1.4中的g-a,g对应输出的高位input[3:0] data_in;//输入输出端口定义output[6:0] data_out;reg[6:0] data_out;//使用always建模组合逻辑需要定义输出为寄存器always@(data_in) //输入为data_inbegincase(data_in)//输入的不同情况4'b0000: data_out = 7'b0111111; // 04'b0001: data_out = 7'b0000110; // 14'b0010: data_out = 7'b1011011; // 24'b0011: data_out = 7'b1001111; // 34'b0100: data_out = 7'b1100110; // 44'b0101: data_out = 7'b1101101; // 54'b0110: data_out = 7'b1111100; // 64'b0111: data_out = 7'b0000111; // 74'b1000: data_out = 7'b1111111; // 84'b1001: data_out = 7'b1100111; // 9default: data_out = 7'b0000000; //default,当输入为其他值时,输出有效,为全0endcaseendendmodule21、上升沿触发的D触发器 p185module dff(data,clk,q);input data,clk;output q;reg q;always@(posedge clk)beginq<=data;endendmodule22、带异步复位、上升沿触发的D触发器module dff_asynrst(data,rst,clk,q); input data,rst,clk;output q;reg q;always@(posedge clk or posedge rst) beginif(rst==1’b1)q<=1’b0;else q<=data;endendmodule23、带异步置位、上升沿触发的D触发器module dff_asynrst(data,rst,set,clk,q);input data,rst,set,clk;output q;reg q;always@(posedge clk or posedge rst or posedge set) beginif(rst==1’b1)q<=1’b0;else if(set==1’b1)q<=1’b1;else q<=data;endendmodule24、基本十进制计数器 p191 module A(clk,cnt);input clk;output[3:0] cnt;reg[3:0] cnt;always@(posedge clk)beginif(cnt==4’d9)cnt<=4’b0000;elsecny<=cnt+1’b1;endendmodule25、六十进制计数器(1)十进制计数器module aaa(clk,out,clk_out);input clk;output[3:0]out;reg[3:0]out;output reg clk_out; always@(posedge clk) beginif(out==9)beginout=0;clk_out=1;endelsebeginout=out+1;clk_out=0;endendendmodule(2)六进制计数器module bbb(clk,out,clk_out); input clk;output[3:0]out;reg[3:0]out;output reg clk_out;always@(posedge clk)beginif(out==5)beginout=0;clk_out=1;endelsebeginout=out+1;clk_out=0;endendendmodule26、 p1031.(1)结构描述方式module circuit1(A,B,C,D,F); input A,B,C,D;output F;nand(W1,A,B);and(W2,B,C,D);or(F,W1,W2);endmodule(2)数据流描述方式module circuit2(A,B,C,D,F); input A,B,C,D;output F;assign F=(~(A&B))|(B&C&D); endmodule(3)行为描述方式module circuit1(A,B,C,D,F); input A,B,C,D;output F;reg F;always @(A or B or C or D) beginF=(~(A&B))|(B&C&D);endendmodule27、分频电路设计,输入50MHz,输出1Hz,应对50MHZ输入时钟进行多少次分频, p228设原始的时钟周期为T,分频后的周期为t,则分频倍数为:N==分配系数为50000000,则最大计数到分频系数的一半,所以二进制计数器的位数为24。

module eee(clk50m,reset,clk1hz);input clk50m,reset;output clk1hz;reg clk1hz;reg [23:0] cnt;always@(posedge clk50m or posedge reset)beginif(reset==1'b1)cnt<=4'b0000;else cnt<=cnt+1'b1;endalways@(posedge clk50m or posedge reset) beginif(reset==1'b1)clk1hz<=1'b0;else if(cnt==24)clk1hz<=1'b1;else clk1hz<=1'b0;endendmodule。