基于CPLD的液晶显示驱动模块的设计

《基于FPGA的彩色液晶驱动板设计》

《基于FPGA的彩色液晶驱动板设计》一、引言随着科技的进步和人们对高质量显示设备需求的增加,彩色液晶显示技术得到了广泛的应用。

为了满足不同应用场景的需求,彩色液晶驱动板的设计成为了关键的技术之一。

本文将介绍一种基于FPGA(现场可编程门阵列)的彩色液晶驱动板设计,旨在提高显示效果、稳定性和可靠性。

二、设计目标1. 优化显示效果:提高彩色液晶屏的分辨率、亮度和色彩饱和度,使显示画面更加细腻、生动。

2. 提高稳定性:确保液晶驱动板在各种工作环境下稳定运行,降低故障率。

3. 增强可靠性:通过优化设计,提高液晶驱动板的抗干扰能力和使用寿命。

三、设计原理本设计采用FPGA作为核心控制器,通过编程实现对彩色液晶屏的驱动和控制。

FPGA具有可编程性、高速度和低功耗等优点,适用于复杂的数字电路系统。

1. 硬件组成:(1)FPGA控制器:负责整个系统的控制和数据处理。

(2)液晶屏:负责显示图像和文字信息。

(3)电源模块:为整个系统提供稳定的电源。

(4)通信接口:实现与外部设备的连接和通信。

2. 软件编程:(1)编写FPGA程序,实现彩色液晶屏的驱动和控制。

(2)通过编程控制液晶屏的扫描方式、亮度、对比度和色彩等参数,以达到优化显示效果的目的。

四、设计流程1. 需求分析:根据应用场景和用户需求,确定设计目标和规格。

2. 硬件选型:选择合适的FPGA控制器、液晶屏、电源模块和通信接口等硬件。

3. 电路设计:根据需求和选定的硬件,设计电路原理图和PCB布局。

4. 软件编程:编写FPGA程序,实现彩色液晶屏的驱动和控制。

5. 系统调试:对硬件和软件进行联合调试,确保系统稳定、可靠地运行。

6. 测试与优化:对系统进行性能测试和优化,以满足设计目标。

五、技术特点1. 高性能:采用FPGA作为核心控制器,实现高速、高效率的数据处理和控制。

2. 灵活性:FPGA具有可编程性,可根据需求进行定制化设计。

3. 低功耗:优化电路设计和软件编程,降低系统功耗。

基于CPLD的出租车计费系统设计

基于CPLD的出租车计费系统设计一、引言出租车计费系统是指通过计算出租车行驶的距离和时间来确定乘客需要支付的费用的系统。

传统的计费系统通常使用微控制器来控制计费规则和处理计费过程。

然而,随着计算机技术的进步,使用CPLD(复杂可编程逻辑器件)来设计出租车计费系统成为可能。

CPLD具有高度灵活性和可编程性,可以用于实现复杂的计费算法和处理大量的数据。

本文将详细介绍基于CPLD的出租车计费系统的设计方法和流程。

二、设计要求1.支持多种计费规则:根据不同城市的出租车计费规则的差异,计费系统需要支持多种不同的计费规则,包括按里程、按时间和混合计费等规则。

2.精确计算距离和时间:计费系统需要能够精确计算出租车的行驶距离和所花费的时间。

3.实时更新计费:计费系统需要实时更新乘客的费用,并在计费过程中能够实时处理折扣等特殊情况。

4.可配置的费率和计费规则:计费系统需要支持灵活配置费率和计费规则,并能够根据政策的变化进行更新。

5.可靠性和稳定性:计费系统需要具备高可靠性和稳定性,以确保计费过程的准确性。

三、设计方案1.系统框架:基于CPLD的出租车计费系统主要由以下几个部分组成:输入模块、计费算法模块、存储模块、显示模块和输出模块。

输入模块用于获取出租车行驶的距离和时间信息,计费算法模块用于根据距离和时间计算费用,存储模块用于存储费率和计费规则,显示模块用于显示乘客的费用,输出模块用于向乘客输出费用信息。

2.系统流程:(1)输入模块获取出租车行驶的距离和时间信息。

(2)计费算法模块根据距离和时间信息结合存储模块中的费率和计费规则,计算出乘客需要支付的费用。

(3)计费算法模块将计算出的费用存储到存储模块中。

(4)显示模块从存储模块中获取费用,并将费用信息显示给乘客。

(5)输出模块向乘客输出费用信息。

3.系统设计:(1)输入模块:使用距离传感器和时间传感器获取出租车行驶的距离和时间信息,并将数据传输给CPLD。

(2)计费算法模块:根据距离和时间信息以及存储模块中的费率和计费规则,使用CPLD设计计费算法,计算出乘客需要支付的费用。

基于DSP的液晶显示模块设计

2 0 1 4年 4月

文章编号 : 1 0 0 7 - 2 7 8 0 ( 2 0 1 4 ) 0 2 — 0 2 2 9 — 0 4

基于 D S P的 液 晶 显 示 模 块 设 计

姜建国 , 田金艳 , 刘松斌 , 雷卫兵

( 东北石油大学 电气信息工程学院, 黑龙江 大庆 1 6 3 3 1 8 )

D aq i ng 1 6 3 31 8, Chi n a)

Ab s t r a c t :El e c t r i c a l e n e r gy i s a wi d e l y us e d s e c o nd a r y e ne r gy . The qu a l i t y o f e l e c t r i c e ne r g y d i r e c t l y i nf l u e nc e s t he no r ma l o pe r a t i on o f e l e c t r i c a l e qu i pme n t . The r e f or e, i t h a s p r a c t i c a l s i g ni f i c a nc e t o a c h i e v e e ne r gy p a r a me t e r s o f t h e d yn a mi c d i s pl a y f o r r e a l — t i me mon i t o r i ng o f p o we r q ua l i t y.I n t hi s p a —

基于CPLD-FPGA技术的数字系统设计研究

基于CPLD/FPGA技术的数字系统设计研究摘要:cpld/fpga是复杂的可编程逻辑器件,都是由pal、gal 等器件发展而来。

cpld/fpga技术的数字系统设计,主要包括设计面积和速度两个方面,该文主要通过资源共享设计和流水线设计等来研究cpld/fpga技术的数字系统设计,希望在应用中有一定的借鉴作用。

关键词:数字系统 cpld/fpga 设计中图分类号:tp332 文献标识码:a 文章编号:1674-098x(2013)02(c)-00-011 cpld/fpga技术cpld/fpga是复杂的可编程逻辑器件,属于规模化的集成电路的范畴。

目前,该技术的集成度已经达到200万门/片,融合了asic 高集成度的特点以及可编程逻辑器便于设计生产的特点,比较适用于开发小批量产品和样品的研究制造,缩短了产品上市的时间。

cpld内利用长度固定的金属线把各逻辑块连接起来,设计出的各种逻辑电路都可以很好的预测时间,有效地弥补了分段式互连结构在时序不完全预测中的缺点。

cpld的特点有编程灵活、设计开发周期短、集成度高、适用范围宽、工具先进、成本较低、不用测试、价格大众化等。

cpld在众多的电路设计规模比较大,所以在产品的设计和生产上得到广泛应用,可以说cpld适用于所有可以使用中小型数字系统的集成电路的场合。

目前,cpld技术的数字系统器件已经成为电子产品必要的组成部分,关于cpld的设计和使用是电子工程师一种必备的技能。

fpga也是由pal和gal等发展而来,它以半定制电路的形式在asic中出现,既弥补了定制电路的缺陷,又消除了可编程器件的缺点。

fpga主要由输出输入模块、可配置逻辑模块和内部连线构成,在编程方面不限次数。

fpga作为复杂的可编程逻辑器件,在结构上和传统逻辑电路以及pal和gal器件有着很大的不同。

fpga采用小型查找表进行组合逻辑,每一个查找表都通过输入端连接一个触发器,再由触发器驱动另外的逻辑电路,构成的这种基本的逻辑单元模块有组合逻辑功能和时序逻辑功能,不同的逻辑模块之间是由金属线连接在一起的。

基于CPLD的两相步进电机细分驱动器设计

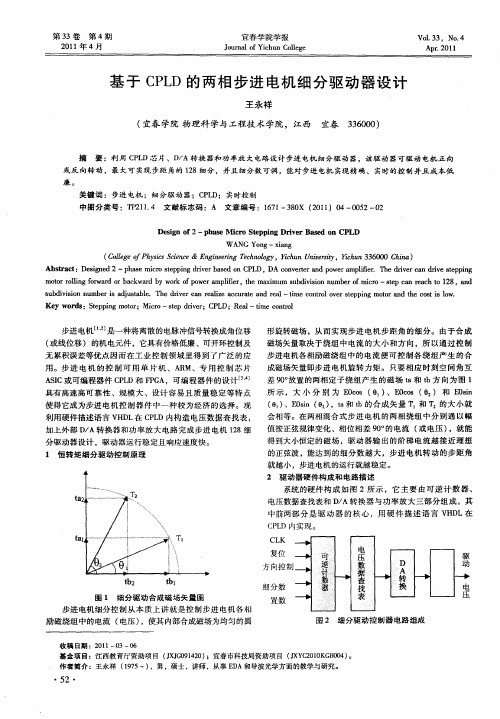

系统 的硬件 构成 如 图 2所 示 ,它主 要 由可 逆 计数 器 、 电压数据查找表 和 D A转换 器与功率 放大三 部分组成 ,其 / 中前两 部分 是 驱 动 器 的核 心 ,用 硬件 描 述 语 言 V L在 HD

C L P D内 实 现 。

CLK

—

复 位

—

: 司

第3 3卷 第 4期 21 0 1年 4月

宜 春 学 院 学 报

J u n lo c u olg o r a f Yih n C l e e

V0 L33. No. 4 Ap . r 201 1

基于 C L P D的 两 相 步进 电机 细 分 驱 动 器设 计

王 永祥

值按正弦规律变化 、相位 相差 9 。 电流 ( O的 或电压 ) ,就能 得到大小恒定的磁场 ,驱动器 输 出的阶梯 电流 越接近 理想 的正弦波 ,能达到 的细分 数越大 ,步进 电机转 动的步 距角

就 越 小 ,步 进 电 机 的 运 行 就 越 稳 定 。 2 驱 动 器硬 件 构 成 和 电 路描 述

( 宜春 学院 物 理科 学与 工程技 术 学院 ,江西 宜春

360 ) 300

摘

廉。

要 :利 用 C L P D芯 片 、 D A 转换 器和 功 率 放 大 电路 设 计 步进 电机 细 分驱 动 器 ,该 驱 动 器 可驱 动 电机 正 向 /

或反 向转动 ,最大可实现步距角的 18细分 ,并且细分数可调 ,能对步进 电机 实现精确 、实时的控制并且成本低 2

( oeeo hssSi c E gne n e nl y Ycu n e i , i u 30 0C i ) C lg l fP yi c ne& nien gTc oo , i nU w  ̄t Y hn3 6 0 hn c e h g h y c a

基于CPLD出租车计费器的课程设计

目录一.总体设计思路 (1)1. 设计目的 (1)2.系统原理框图 (1)二.功能模块设计 (2)1. 计费模块 (2)2. 数据转换模块 (2)3. 片选信号产生模块 (3)4. 显示模块 (3)5. 数码管控制模块 (4)6. 分频模块 (4)7. 数码管选择模块 (5)三.各个模块设计及仿真 (5)1.计费模块 (5)2.数据转换模块 (8)3.片选信号产生模块 (12)4.显示模块 (13)5.数码管控制模块 (14)6.分频模块 (16)7.数码管选择模块 (17)四.总体设计电路图 (18)五.硬件实现 (19)六.心得体会 (21)七.程序清单 (22)八.参考文献 (32)一.总体设计思路1. 设计目的随着EDA技术的高速发展,电子系统的设计技术发生了深刻的变化,大规模可编程逻辑器件COLD/FPGA的出现,给设计人员带来了诸多方便,利用它进行产品开发,不仅成本低,周期、可靠性高,而且具有完全的知识产权。

随着社会的不断进步,人们生活水平的不断提高,出租车逐渐成为人们日常生活不可缺少的交通工具。

而计价器作为出租车的一个重要组成部分,关系着出租车司机和乘客双方利益,起着重要的作用,因而出租车司机和乘客双方利益,起着重要的作用,因而出租车计价器的发展非常迅猛。

2.系统原理框图基于CPLD的出租车计费器的组成如图1所示。

各部分主要功能包括:信号输入模块对车轮传感器的脉冲信号进行计数,并以高低电平模拟出租车启动、停止、暂停、加速按钮,具有输入信号作用;数据转换模块将计费模块输出的车费和路程换成4位的十进制数据;译码/动态扫描模块将路程与费用的数值译码后用动态扫描的方式驱动数码管;数码管显示模块将公里和计费金额用4位LED数码管显示。

图1.1 系统总体框图二.功能模块设计1. 计费模块此模块为计费模块(即总体结构中的信号输入模块),实现计费功能,计费标准为:按行驶里程计费,起步价为7.00元,并在车行3公里后按2.20元/km计费,当计数器达到或超过20元时,每公里加收50%的车费,即按3.30元/km计费。

TFT—LCD显示及驱动电路的设计

视频解码 LCD显示 单片机

第一章概述

1.1

1.2

SPI

IIC

图1-1 系统框图

第二章

2.1

上把物质分为三态,固态、液态和气态。在自然界中,大部分材料随温度的变化只呈现固态、液态和气态。液晶(Liquid Crystal)是不同于通常的固态、液态和气态的一种新的物质状态,它是能在某个温度范围内兼有液体和晶体两者特性的物质状态,也叫液晶相或中介相,故又称为物质的第四态。

①满足视频解码芯片的选取要求。在TVP5150芯片内部有一个9位高速的带模拟处理器的A/D转换器;有专门的场同步信号和垂直同步信号,保证信号的正确采集;内部有专门的Y/C分离电路,实现视频解码数据按照ITU-RBT656输出;

②芯片本身的功耗才115mW,功耗低,便于系统多路采集设计;电路设计简单,内部自带可编程的ROM以及支持部分RAM。

图3-1TVP5150引脚功能

3.2.2

通道选择寄存器如图3-2所示:

图3-2通道选择寄存器

视频通道切换数据如表3-1所示:

表3-1

3.3

1、要求输入通道采用AIP1A通道。

2、视频输入模式允许NTSC-M、PAL (B, G, H, I)或者SECAM模式。

3、数据输出为8-bit ITU-R BT.656模式。

摘要

TFT—LCD显示及驱动电路设计由视频解码电路,LCD显示电路,电源控制电路和单片机控制电路四个模块组成。视频源产生模拟视频信号,由TVP5150视频解码把模拟视频信号解码输出数字视频信号,由LCD液晶屏显示。对视频解码和液晶显示器的配置是通过单片机完成的。本设计主要针对高校电视技术实践课程设计,应用于视频解码输出教学,实现信号处理可视模块化教学方案。

基于CPLD的图像采集存储模块的设计

视频 采集是 数字 图像获取 的最 基本 手段 .是 进 行 数字 图像处理 、 多媒 体 网络 传输等 的前 提 . 随着 图 像 数字化 处理技术 的高 速发展 .实 时图像采 集存 储 技术 也得 到 了迅 速 的发展 ,而且 对 图像采 集存储 的

维普资讯

文章 编 号 :0 19 4(0 70 -0 60 10 —9420 )50 6 —3

基 于 CP D 的图像 采集存储 模 块的设计 L

刘 政 . 汉 民 叶

( 林 _ 学 院 电子 与 计 算机 系 , 林 5 1 0 ) 桂 T - 桂 4 0 4

d r d c nr l u e a o t meh d f C L i te g t e n .T e a r a ay e t e i r lt n o L i i a n u n o to o P D n h a r g h p p l z s h t h i e n me eai f CP D n sg l i p t o n

摘 要 : 于嵌入 式 系统 中对 图像 实时采 集的 需要 . 出 了一种 利 用复 杂可 编程 逻辑 器件C L 基 提 PD 来设 计D P S 图像 压缩 系统 中数据 采 集存 储 模块 的方 案 ,重点 讨 论 了C L 在 数 据 采 集过 程 中 PD 的 工作流 程和 控制 方 法。 全文 详 细分析 了CP D输 入输 出信 号 的逻 辑控 制 时序 关 系 . 别就模 L 分 拟 I 总 线 、 据采 集 的逻辑 功 能设 计 、 P D逻 辑功 能仿 真验 证 等进 行 了详 细介 绍 ℃ 数 C L

基于FPGA的TFT-LCD液晶显示模块设计

基于FPGA的TFT-LCD液晶显示模块设计张超建;王厚军【摘要】针对多片显存驱动TFT-LCD液晶显示方法所带来的控制复杂、不易布线等情况,提出了一种基于FPGA的单片SRAM驱动LCD模块的新方法,并加以实现.采用FPGA完成LCD显示时序的产生、显示图像处理、单片SRAM读写切换控制等功能,有效节约了系统资源,大幅度减少了成本开支,已成功应用于某款数字存储示波器中.经验证,该方案控制简单、显示稳定,具有广阔的应用前景.【期刊名称】《中国测试》【年(卷),期】2010(036)005【总页数】3页(P73-75)【关键词】FPGA技术;显存;液晶显示屏;总线仲裁;数字存储示波器【作者】张超建;王厚军【作者单位】电子科技大学自动化工程学院,四川,成都,611731;电子科技大学自动化工程学院,四川,成都,611731【正文语种】中文【中图分类】TM935.39;TN949.1921 引言随着液晶技术的日益成熟,液晶显示屏(Liquid Crystal Display,简称LCD)在测试领域中得到了越来越广泛的应用,如今大部分新型示波器都采用了液晶显示屏。

在各种LCD的产品中,薄膜晶体管液晶显示器TFT(Thin Film Transistor)LCD 因其体积薄、重量轻、画面质量优异、功耗低、寿命长、数字化和无辐射等优点,已被广泛应用于各类图形显示系统。

一般LCD显示都采用专用的液晶显示控制模块,实现屏幕分割、屏幕逻辑运算等复杂的图形功能。

但这样必须要由DSP来控制显示模块,而且其刷新频率受到一定限制。

而示波器的实时性要求非常高,对刷新率要求也就很高,并且液晶显示界面基本上只是显示框架和实时波形等简单的图形,所以设计中,LCD显示没有采用专用控制芯片控制显示,而是采用外部硬件现场可编程门阵列(Field Programmable Gate Array,FPGA)产生LCD所需要的各种显示控制时序。

基于CPLD的高速数据采集系统控制模块的设计与实现

关键 词 : D elg P D; 据采 集与存储 控制逻 辑 ; 真 H LV ro ;C L 数 i 仿 中图分类 号 : P 0 . T 32 1 文 献标识 码 : A 文章 编号 :10 - 6 3 20 )3 07 — 3 07 2 8 (0 6 0 — 0 5 0

a q i t n a d s r g ;s lt n c us o t a e i ai i i n o mu o

在现代工业的发展 中, 实时测控系统得到广泛 应用 , 进而对高速数字信 号处理系统提出了更高 的 要求. 由于涉及大量 的计算 , 为了提高运算速度 , 应 用了 D P S 器件. 数据采集 系统是整个 系统 的核心部

曲震宇 , 刘胜辉

( 尔滨 理工 大学 计算机科学 与技术学 院, 哈 黑龙 江 哈尔滨 10 8 ) 50 0

摘

要 :采 用 E A技 术 , D 通过硬 件 实现 对数 据采 集 系统 的控 制 , 而提 高速度 和 可 靠性. 一 从 这

方法对控制逻辑的设计具有普遍意义. 用 H LV ro 和 C L 采 D el ig P D完成 了对高速数据采集系统及数 据存储控制逻辑的设计. 仿真验证结果表 明, 其控制模块的采样周期达到 04 s设计完全满足 系 . ,

的信号采集和处理能力.

1 数 字信号处理 系统 总体方案

数据采集系统是基于 D P S 信号处理系统的一部

分, 系统框图如图 1 所示. 该数字信号处理系统可用 于弱信号检测的应用研究中. 整个系统 由信号放大、

分之一 , 传统方法是应用 MC U或 D P 通过软件控 S,

制数据采集的模/ 数转换 , 这样必将频繁中断系统的 运行 , 从而减弱系统的数据运算能力 , 数据采集的速 度也将受到限制. S C L / P A的方案被认 为 D P+ P D F G 是数字信号处理系统的最优方案之一… , 由硬件控 制模/ 数转换和数据存储 , 从而最大限度地提高系统

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于CPLD的液晶显示驱动模块的设计万盛国1,刘 凯1,李 芳2(1 南京航空航天大学机电学院,江苏南京 210016)(2 南京航空航天大学金城学院数理力学系,江苏南京 211156)摘要:以复杂大规模可编程逻辑器件(CPLD)为核心,采用 CPLD+SRAM的方案进行液晶显示驱动电路的设计。

论述了液晶显示驱动模块的系统总体设计、控制器的设计及SRAM中数据的读写,并对CPLD的扫描时序进行了说明。

关键词:CPLD+SRAM;液晶显示驱动电路;扫描时序中图分类号:TP273 文献标识码:A 文章编号:1672-1616(2010)13-0055-03嵌入式系统是近来发展最快的技术之一。

显示器作为人机交互的关键部分,现已成为嵌入式设备中必不可少的外围接口器件之一。

薄膜晶体管液晶显示器(TFT-LCD)性能优良,自动化程度高,原材料成本低廉,可大规模生产,发展空间广阔;而现今TFT-LCD的价格更是日趋下降,因而其在嵌入式设备中的发展将有广阔的发展前景[1]。

由于TFT控制时序相对复杂,因而应运而生了TFT的控制器,但带有控制器的TFT显示屏价格昂贵,另外,液晶显示屏的接口没有统一的标准,不同的控制器与显示屏之间的接口不一定兼容[2],所以大多数用户选择自己制作控制器的方案。

本文采用的是 CPLD+SRAM的方案来实现通用液晶驱动电路的设计。

由于CPLD操作灵活、开发迅速、适用范围广、投资风险低、可多次编程擦写并可在系统编程,同时可针对特定型号的液晶模块进行编程,故可实现特定效果和参数的底层驱动[3]。

1 系统总体构架本系统中,LCD模块采用的是SHARP公司的不带LCD控制器的T FT-LCD(LQ104V1DG51)模块。

在设计控制器时,采用的是Altera公司的M AX II系列的CPLD(EPM570)作为核心部件,以ISSI公司的IS61LV25616AL大容量SRAM作为显示缓冲存储器,设计 CPLD+SRAM T FT-LCD控制器。

图1为液晶屏显示系统的系统框图。

CPLD 的主要功能是对CPU输入的8位并行数据进行转换处理[4],将5组8位并行数据依次转化为列地址(两组8位并行数据)、行地址(两组8位并行数据)、颜色数据(一组8位并行数据),通过地址译码将颜色数据对应地存储在外部缓存SRAM中。

这样,5组数据确定1个像素点的位置及其对应的颜色。

图1 液晶显示系统框图液晶屏的显示是通过CPLD以一定的驱动时序读SRAM中的8位颜色数据,通过一个三态缓冲电路将8位颜色数据以R3G3B2的形式映射到液晶屏端(R6G6B6)。

其中,CPU写数据和CPLD 从SRAM中读数据是2个独立的过程。

如果CPU 中有数据发送,则SRAM中数据更新,屏显示发生相应的变化;如果CPU中没有数据发送,CPLD仍不断从SRAM中读数据发送到屏上进行刷新,否则液晶屏将熄灭。

2 CPLD+SRAM控制器的设计CPLD作为显示控制器设计的核心,通过一定的时序来完成液晶屏的显示等相关功能。

本设计中采用的CPLD,其电气参数、引脚数目等符合本收稿日期:2010-03-08作者简介:万盛国(1988-),男,江西抚州人,南京航空航天大学硕士研究生,主要研究方向为数控技术。

55!智能控制技术! 万盛国 刘 凯 李 芳 基于CPLD的液晶显示驱动模块的设计设计要求,其I/O 电压为3.3V,适合与外部SRAM 电压匹配,同时也满足液晶屏的电压要求[4]。

由于CPLD 不具有存储功能,则CPLD 需与一个SRAM 相配合使用,才能保证CPLD 能通过地址译码源源不断地从SRAM 中读出数据并发送到液晶屏端,使得屏保持不熄灭。

因此, CPLD +SRAM 才是一个完整的控制器。

在本设计中,外部缓存SRAM 的主要作用是将CPU 发送的数据进行缓存,以供CPLD 读取。

图2为SRAM 的硬件接口原理图,其中外部缓存SRAM 的18位地址线(RAM A0~RAM A17)和16位数据线(RAM D0~RAM D15)通过与CPLD 的I/O 口相连以完成数据的传送,另外,SRAM 上的控制信号也都与CPLD 相连,并由CPU对其读写操作进行控制。

图2 SRAM 硬件接口原理图3 SRAM 中的数据读写一屏数据640∀480=307200,为300K (0x4B000),需要19位地址(8位数据),而本系统采用的IS61LV25616AL (SRAM )只有18位地址线(16位数据线)。

因此,本系统中将300K 的数据分为高240行和低240行2个部分,它们所采用的地址线相同,但数据线不相同,其中高240行数据采用的是高8位数据线,低240行数据采用的是低8位数据线。

系统工作时,SRAM 中数据的读写操作通过CPLD 所产生的地址RAM A0RAM A17对SRAM 的相应地址依次进行读写颜色数据,但由于高240行和低240行数据所采用的地址线相同,则SRAM 中数据的读入和写出要通过相应的参数来进行判定。

缓存SRAM 写入数据时,通过参数ram lb 和ram ub 来判断是高240行还是低240行的颜色数据,具体实现代码如下:ram d(7dow nto 0)<=ram w r d lb w hen ram lb=#0#and ram w e=#0#else (others =>#Z #); /*--高240行数据--*/ram d(15dow nto 8)<=ram w r d lb w hen ram ub=#0#and ram w e=#0#else(others=>#Z #); /*--低240行数据--*/CPLD 读取SRAM 中的数据是通过参数ram lb 来判断是读高8位数据线中数据还是低8位数据线中的数据,具体实现代码如下:if(ram lb =#0#)thenlcd r <=ram d(7dow nto 5);lcd g <=ram d(4dow nto 2);lcd b <=ram d(1dow nto 0);/*--读低8位数据线中的数据--*/elselcdr <=ramd(15dow nto 13);lcd g <=ram d(12dow nto 10);lcd b <=ram d(9dow nto 8);/*--读高8位数据线中的数据--*/end if;4 扫描时序液晶屏的显示是通过CPLD 的驱动时序读SRAM 中的颜色数据,并以一定的时序发送到液晶屏上显示。

显示过程包括2个循环:一个是行扫描循环,另一个是列扫描循环。

以本系统采用的LQ104V1DG51为例,其扫描时序如下所述。

在进行行扫描时,以5MHz 的clock 信号作为驱动时钟,clock 信号上升沿出现后的有效时间内,数据使能信号有效[5],行扫描有hsync start 、hsync low 、hsync bef 、hsync valid 、hsy nc in valid5种状态。

由于状态hsync start 是只有在CPU 发出复位信号才存在的状态,则正常运行情况下,行扫描存在hsync low 、hsync bef 、hsync valid 、hsync invalid 4种状态,分别对应图3行扫描时序信号中的TH c 、THe 、THd 、TH p 。

在进行列扫描时,列扫描根据vsy nc cnt(行扫描结束)信号的上升沿有vsync low 、vsync valid 、vsync invalid3种状态,对应的持续时间分别为行扫描周期TH 的44倍、480倍、14倍。

然而,在一个扫描循环过程中,当且仅当同时562010年7月 中国制造业信息化 第39卷 第13期满足hsy nc state=hsync valid 和vsync state=sync valid 时,CPLD 才从SRAM 中读数据,共计图3 行扫描时序信号640∀480个数据,完成一个扫描周期。

如此循环往复,即可实现对液晶显示器的刷新。

以行扫描为例,具体实现代码如下:∃∃hsync cnt <=hsync cnt +1; /*--计数--*/case(hsync state)isw hen hsy nc start=>∃∃/*--计数计到4时,转向hsync low 状态--*/w hen hsy nc low =>∃∃/*--计数计到2时,转向hsync bef 状态--*/w hen hsy nc bef=>∃∃/*--计数计到103时,转向hsy nc valid 状态--*/w hen hsy nc valid=>/*--读SRAM 中数据,发送到颜色信号线上--*//*--计数计到639时,转向hsync invalid状态--*/when hsync invalid=>∃∃/*--计数计到49时,则一行扫描结束--*/5 结束语本文针对通用的液晶显示模块,构建了 CPLD+SRAM 的液晶显示驱动电路,并以LQ104V1DG51为例,介绍了其具体的逻辑时序。

该驱动模块可对不同型号、类型、尺寸的TFT -LCD 液晶显示模块写入相应的程序,从而在硬件不作大改动的情况下方便地实现与多种显示屏的接口,提高系统的兼容性,降低开发成本。

参考文献:[1] [日]堀浩雄,铃木幸治.彩色液晶显示[M ].金振裕,译.北京:科学出版社,2003.[2] 周晓光,王永明,祝明德.基于CPLD 的液晶显示屏与嵌入式处理器的接口设计[J].电子测量技术,2006,29(5):23-25.[3] 王 妍,郑 君,李志扬,等.基于CPLD 和LCX016的通用投影仪的液晶驱动电路[J ].电子元器件应用,2008,10(3):22-26.[4] 宋丹娜,代永平,刘艳艳.基于CPLD 的LCOS 场序彩色视频控制器设计[J].液晶与显示,2009,24(8):74-100.[5] 王 妍,李志扬,郑 君.基于CPLD 的通用液晶驱动电路[J].郑州轻工业学院学报,2008,23(2):110-119.The Design of TFT -LC D Driving Module Based On CPLDWAN Sheng -guo,LIU Kai,LI Fang(Nanjing University of Aeronautics and Astronautics,Jiangsu Nanjing,210016,China)Abstract:Based on CPLD+SRAM and complex programmable logic device(CPLD),it designs LCD drive circuit,dissusses the overall design of LCD driving module,the desig n of T FT LCD controller and the read w rite operation of SRAM,and shows the detail about the scanning sequence of CPLD.Key words:CPLD+SRAM ;LCD Drive Circuit;Scanning Sequence57!智能控制技术! 万盛国 刘 凯 李 芳 基于CPLD 的液晶显示驱动模块的设计。