GPS接收机基带信号处理模块的FPGA实现

基于ARM+FPGA的GPS接收机设计

1 接 收 机 的 组成

接收机的组成可 以按 照功能划 分为两部 分 : 射频部 分 和基带处理部分 。射频部分主要 是完成 G S信号 的接 收、 P 下变频及采样 的功能 。基 带处 理部 分 主要是完 成 G S信 P

p roma c s2 0 m/ . h e ev rc n a h e e h g y a c n vg t n a d p st n n . th s s l sz ,o e r n e i 0 0 s T e r c ie a c iv ih d n mi a ia i n o i o i g I a mal ie lw f o i

d sg x li e ,n l d n e c p u e e g n ,r c ig e g n , e d lt n me s g s a d p st n r s l t n e in i e p a n d i cu i g t a tr n i e ta k n n i e d mo u a i s a e , n o i o e ou i . s h o i o

T ruht e etter e e ’ oioigpeio s6 1 gt e / m (a t e ,n h ya i hog ef l ts, e i r Sp si n rcs n i m(o i d ) 8 h id h cv tn i n u 1i d ) ad t d nmc tu e

接收机 的射频前端 采用 G 2 1 片 , 带处理部 分采用 A M P 0 5芯 基 R 9内核 的 A 9 S M 2 1芯片 和 C c n I T 1A 96 yl eI o 系列 的 E 2 7F 71 P C 0 628芯片 。同时 阐述来接收机的软件设计 , 括捕获 引擎 、 包 跟踪 引擎 、 解凋 电文 , 位解 定 算等 。该接收机通过现场实验定位精度为 6 经度 ) 8 纬度 ) 动态性 能达 2 0 m s可 以实现 高动态 m( / m( , 00 /, 导航定位 , 同时体 积小 , 功耗低 。

基于FPGA的GPS定位授时系统研究

• 57•随着科学技术的飞速发展,越来越多的设备对时间的精确度和同步性的要求越来越高。

由于原子钟的成本太高,各种基于嵌入式处理器的授时设备便应运而生。

本文设计了一种基于FPGA的GPS定位授时信息显示系统,采用Verilog HDL硬件描述语言编写了GPS授时定位信息采集、处理与显示程序,阐述了每个不同的功能模块的设计思想和实现方法。

在实际的运行过程中,该系统能实现GPS授时信息以及定位经纬度的正确显示,完成了UTC时间向北京时间转换显示,具有较好的实用性。

引言:生活中许多的嵌入式设备都需要精确的时间信息,使用时钟芯片的方式容易在掉电时丢失时间信息,而且精确度不高,例如许多无人值守的监控设备,需要监控的图像与精确的时间一起记录,以便后期的处理和查阅。

随着物联网技术的飞速发展与应用,夏凝对于产痛的电视广播授时方式,在某些特定的嵌入式应用场合中,GPS授时凭借其高精度、低成本的优势得到了广泛的应用。

GPS借助全球分布的同步卫星传输信号,实现了全球任意地方的授时定位服务,提供全球的授时服务使得其可以为分布面积广的嵌入式信息采集设备提供授时服务,成本较低使得越来越多的嵌入式设备集成了GPS接收器,操作简单使得其提供的授时产品可为大多数人使用。

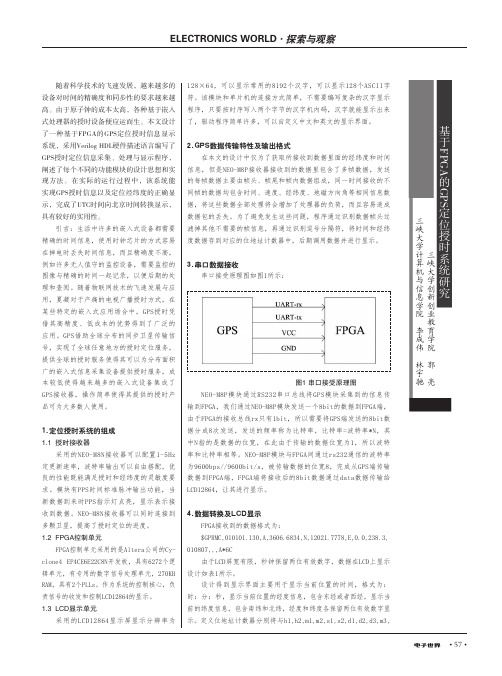

1.定位授时系统的组成1.1 授时接收器采用的NEO-M8N接收器可以配置1-5Hz 定更新速率,波特率输出可以自由搭配,优良的性能既能满足授时和经纬度的灵敏度要求。

模块有PPS时间标准脉冲输出功能,当新数据到来时PPS指示灯点亮,显示表示接收到数据。

NEO-M8N接收器可以同时连接到多颗卫星,提高了授时定位的进度。

1.2 FPGA控制单元FPGA控制单元采用的是Altera公司的Cy-clone4 EP4CE6E22C8N开发板,具有6272个逻辑单元,有专用的数字信号处理单元,270KB RAM,具有2个PLLs。

作为系统的控制核心,负责信号的收发和控制LCD12864的显示。

基于FPGA的导航接收机跟踪环路设计与实现

基于FPGA的导航接收机跟踪环路设计与实现顾睿文;黄仰博;苏映雪;欧钢【摘要】现阶段导航接收机设计的基本架构是FPGA+DSP或者FPGA+ ARM 的工作方式。

接收机存在研发时间长,研发难度较大的特点,且DSP/ARM 处理环路跟踪的同时需处理协议上的许多操作,在实现上较为复杂,实时性不高。

基于SOC技术,利用Xilinx公司提供的协处理器软核代替DSP部分功能,用于在单片FPGA内实现导航接收机的跟踪环路,并根据实际情况,设计了硬件加速器和相关值预处理模块,利用时分复用的方式节约了硬件资源,在单片FPGA上实现了跟踪环路的设计,降低了硬件成本,为高性能导航接收机芯片设计提供了一种思路。

%Nowadays the structure of Navigation Receiver is FPGA + DSP or FPGA +ARM .Usually ,it takes a lot of time and hardworking to realizeit .And DSP/ARM needs to deal with many works in the agreement ,and control the tracking loop is designed .It is hard to realize it .Based on SOC ,a kind of tracking channel is designed .In this loop ,the micro-processor provided by Xilinx is used to replace part work in DSP/ARM .The tracking chan-nel in a signal FPGA is realized .Actually ,hardware arithmetic accelerator FPGA and corre-lation data preprocessing is designed ,using time division multiplexing technology to reduce cost of hardware .It provides a good idea in navigation receiver designing .【期刊名称】《全球定位系统》【年(卷),期】2014(000)005【总页数】5页(P55-58,63)【关键词】FPGA;导航接收机;跟踪环路【作者】顾睿文;黄仰博;苏映雪;欧钢【作者单位】国防科学技术大学电子科学与工程学院卫星导航定位技术工程研究中心,湖南长沙 410073;国防科学技术大学电子科学与工程学院卫星导航定位技术工程研究中心,湖南长沙 410073;国防科学技术大学电子科学与工程学院卫星导航定位技术工程研究中心,湖南长沙 410073;国防科学技术大学电子科学与工程学院卫星导航定位技术工程研究中心,湖南长沙 410073【正文语种】中文【中图分类】P228.40 引言全球定位系统能够为用户提供精确的定位、测速、授时服务(PVT服务),在国民经济的快速发展的今天已经得到广泛的应用[1]。

浅谈北斗OEM主板的硬件构造

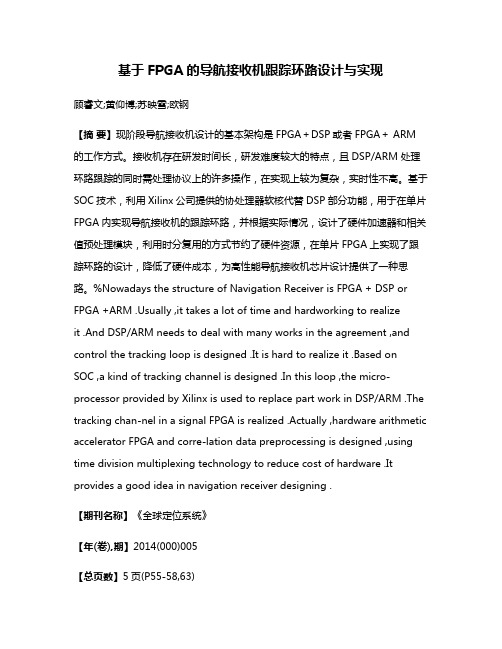

浅谈北斗OEM主板的硬件构造司南导航赵永茂北斗OEM主板作为高精度GNSS接收终端的核心部件,是大规模集成电路和高精度算法高度融合的结晶,为高精度卫星导航在各行业的应用奠定了重要的基础。

提及OEM主板的硬件构造,比如RF射频、FPGA、DSP等概念,一般都会觉得高深难以理解,本文就从应用的角度对OEM主板构造的相关内容进行阐述,希望能够为行业相关技术人员提供简单的入门知识。

北斗OEM主板各部分关系如下图所示:为了便于识别,下图以K708主板为例进行说明:各部件主要功能及工作原理阐述如下。

1.RF射频前端处理模块通过天线接收所有可见BDS/GPS/GLONASS卫星的信号,经前置滤波器和前置放大器的滤波放大后,再与本机振荡器产生的正弦波本真信号进行混频而下变频成中频信号,最后通过模数(A/D)转换器将中频信号转变成的数字中频信号;各卫星系统使用频率范围如下:2.FPGA基带处理模块通过处理射频模块所输出的数字中频信号,获得与接收到的卫星信号一致的本地载波和伪距信号,进而实现BDS/GPS/GLONASS卫星的捕获与跟踪,并且从中获取伪距和载波相位等测量值及解调出的导航电文;司南导航K7系列主板采用自主研发的专用ASIC芯片SNB1008,具有全系统信号支持、运算速度快、数据精度高、功耗低等优势;3.DSP核心CPU处理模块从基带处理输出的伪距、载波、多普勒观测值及导航电文,在核心CPU内,通过PVT、RTK、PPP等算法处理,最终获取用户终端的高精度三维位置、速度、时间等时间信息。

司南导航新一代RTK算法已于近期发布,在高精度GNSS定位的可用性及可靠性上取得了显著提升,可为高精度GNSS用于应用带来很好的用户体验。

4.大容量存储模块板卡大容量内存,可用于保存原始观测数据,可靠度更高,稳定性更好。

5.用户应用接口通过丰富的用户应用接口,可满足多行业用户对GNSS终端的多样化应用需求,按应用类别可分为:(1)IO接口(输入输出):如串口(LV_TTL或RS232)、USB、LAN、CAN等;(2)授时:TOD(RS232)+PPS秒脉冲;(3)频率输出:10M方波;(4)Event Mark事件输入。

GPS软件基带信号处理与定位实现

GPS软件基带信号处理与定位实现背景GPS(Global Positioning System)是由美国国防部研制并运行的卫星导航系统,在全球范围内为用户提供定位、导航和定时服务。

它利用多颗卫星和地面接收机进行数据传输和信号处理,定位精度高、覆盖范围广,被广泛应用于军事、民用和商业领域。

GPS信号由两个部分组成:导航消息和载波信号。

其中,载波信号又分为L1和L2两种频率,分别为1575.42MHz和1227.60MHz。

在信号传输过程中,会受到多普勒效应、多径效应、大气延迟等干扰,这些干扰会导致信号的延迟和失真,从而影响定位精度。

为了减少信号干扰和扭曲,需要进行GPS信号的基带信号处理。

基带信号处理包括信号去频偏、码跟踪、距离测量等步骤,最终实现GPS定位。

本文将介绍GPS软件中基带信号处理的方法和定位实现过程。

GPS基带信号处理信号去频偏GPS信号传输中会受到多普勒效应的影响,即卫星和地面接收机之间相对运动导致信号频率发生变化。

为了解决这种干扰,需要对信号进行去频偏处理。

去频偏的方法主要有两种:第一种是采用Costas环路去频偏方法。

这种方法是利用航空电子学中的相位比较技术,对信号的相位进行比较从而消除频偏影响。

第二种方法是采用数字信号处理技术进行Tricky-Tec去频偏,能够更好地适应频率变化。

码跟踪GPS信号中有伪随机码(PRN)和导航信息码。

PRN码是一组码元序列,作为卫星的标识符,用于区分不同卫星的信号。

导航信息码则包含了各项GPS参数以及导航消息,用于帮助接收机完成定位。

在信号传输过程中,接收机需要对PRN码跟踪并以确定的时间间隔采样,通过距离计算算法计算出信号的到达时间差,从而实现定位。

而PRN码受到热噪声和多径干扰影响,会引起码偏移和丢失,因此需要进行码跟踪来解决这些问题。

常用的码跟踪算法有Early-Late算法、Delay-Lock Loop算法和Costas环路算法。

这些算法能够对PRN码进行跟踪和纠偏,提高接收机接收信号的质量。

基于FPGA与DSP的嵌入式GNSS接收机设计

⑥

2 1 SiT c. nr. 0 c. ehE gg 1

基 于 F G 与 D P的 嵌 入 式 P A S G S N S接 收 机 设 计

.

杨 树 伟 张

冰 胡

锐

( 江苏科技大学电子信息 学院 镇江 2 2 0 ; , 10 3 北京耐威集思系统集成有限公司 北京 10 2 ) , 0 0 9

第 1 1卷

第2 7期

2 1 年 9月 01

科

学

技

术

与

工

程

Vo.1 No 7 S p.201 1 1 .2 e 1

17 — 1 1 (0 1 2 -6 30 6 1 8 5 2 1 ) 76 4 -6

Sce c c noo y n g n ei g i n e Te h l g a d En i e rn

摘

要

随着 G S 收机应用 的不断深入 , N S接 其对 系统 功耗 、 体积 等性能 的要求越来越 高。大规模 集成 电路芯片 如现场 可编

程逻 辑 门阵列( P A) 高速 数字信号处理 器( S ) FG 和 D P 等在嵌入 式 G S 收机设计 中得 到广 泛应用。卫星信号数 字处理是 接 N S接 收机 的核心部件之 一, 出了一种基于 F G 提 P A与 D P模 块化 的嵌入 式接 收机 的基 带信 号处 理系统设计。利用 F G S P A完成基 带 相 关器 的设计 , 并由 D P实现 卫星信 号的信 号处理和定位导航解算 。通过 静态测试 试验 , 明所设 计的 G S 收机具有体 S 说 N S接

各 种观 测 量 进 行 实 时 快 速 的 处 理 , 现 定 位 解 算 , 实 最后 向用户 输 出接 收 机 的位 置 、 速度 、 间信 息 。 时

基于FPGA原型的GPS基带验证系统设计与实现

( . s t e o i o l t n s o hn s A a e y o c n e ,B i n 0 0 9, hn ; 1I tu f M c e cr i fC iee c d m fS i c s e ig 1 0 2 C ia n it r e o c e j 2 H n z o h n k co l t n s C . t , n z o 10 3 C i ) . a gh u Z o g e Mi e cr i o ,Ld Ha gh u 3 0 5 , hn r e o c a

De i n a d i p e e t to sg n m l m n a i n o fGPS b s b nd v rfc to y t m s e n t a e a e i a i n s s e ba d o he FPGA o o o i pr t c l

文 讨 论 了 G S基 带 的 验 证 方 案 以 及 基 于 F G 的 设 计 实现 , 对 验 证 过 程 中 的 问 题 进 行 了 分 析 , 提 P PA 并 并

出相应 的 解决 办法 。

关 键 词 :F G 原 型 ; S; o 验 证 P A; GP S C;

中 图分 类 号 :T 4 2 N 9 文 献标 识 码 :A 文 章 编 号 :0 5 — 9 8 2 1 )7 0 5 — 2 2 8 7 9 (0 0 0 — 0 6 0

到 整 个 设 计 周 期 的 7 %以上 , 何 减 少 验 证 时 间 成 为 一 0 如 个 十 分 重 要 的 问 题 。 G S基 带 芯 片 是 一 个 典 型 的 S C, P o 其 主 要 功 能 模 块 是 相 关 器 , 以 实 现 G S信 号 的解 调 和 用 P 解 扩 。相 关 器 占据 了 基 带 芯 片 中 的 大 部 分 硬 件 资 源 , 其 仿 真 过 程 十 分 复 杂 且 耗 费 大 量 时 间 , 此 仅 仅 依 靠 软 件 因

基于FPGA的GPS和GSM双重车载定位

基于FPGA的GPS和GSM双重车载定位

目前在车辆GPS导航系统中,主要是直接利用无差分、无SA误差的GPS定位数据来实现车辆在地图上的定位。

考虑到定位信号存在一定的误差,5%概率下误差会超过15 m,同时城市中建筑物、桥梁以及树木等还对GPS信号形成遮挡,甚至会导致信号失效,从而进一步影响定位精度。

而车在行进过程中进行导航时,尤其是在路口以及立交桥等特殊地点的导航时,系统往往需要更为精确的定位。

为此,本设计充分利用了FPGA强大的逻辑控制功能和NiosⅡ处理器的多可配置标准外设接口功能,结合GPS和GSM 功能模块,设计了一款双重定位系统。

通常情况下用GPS进行定位,在特殊情况下可以开通GSM网络定位功能实现双定位,再通过GSM网络将定位信息、时间和终端特殊信息传送到监控中心,或者接收监控中心传来的信息,完成定位和监控等功能。

图1 GPS/GSM车载定位系统示意图

1 NiosⅡ软核嵌入式处理器

NiosⅡ处理器是Altera公司的第二代用户可配置的通用32位RISC

软核微处理器,是Altera公司特有的基于通用FPGA架构的软CPU内核。

N-iosⅡ系列支持使用专用指令。

专用指令是用户增加的硬件模块,它增加了算。

基于ARM9和FPGA的GPS接收机软硬件设计与实现

星为基础 的无线 电导航系统 ,具有全能性 ( 陆地 、海洋 、航 空 、航 天 ) 、全 球 性 、全 天 候 、连 续性 、实 时 性 的 导航 、定位 和定 时等功 能,能为各类静止或高速运动的用户迅速 提供精 密 的瞬 间三维空 间坐标 、速度矢量和精确授时等多种 服务。

De s i g n a n d i m pl e me n t a t i o n o f t he ha r d wa r e - pl us - s o f t wa r e pl a t f o r m O f

GPS r e c e i v e r b a s e d o n ARM 9 a n d F PGA

ADS 1 . 2 a n d r e a l i z e s t h e d e s i n g o n A RM +F P GA h a r d wa re s y s t e m.

Ke ywor d: G PS ; AR M 9; Ac qu i s i ion t a n d Tr a c ki ng

b a s e d o n t h e p r o p o s e d h a r d wa r e p l a f t o m, r s mu i l a t e s he t r e c e p t i o n a n d p r o c e s s i n g o f he t GP S s a t e l l i t e s i na g l b a s e d o n Qu a r t u s 1 1 9 . 1 a n d

总第 1 5卷 1 6 4期 2 0 1 3年 4月

大 众 科 技

Po p u l ar Sc i e n c e& Te c h n ol o g y

GPS基带信号源的数字模拟实现

航 天 控 制Aer os pace Contr ol Aug12009 Vol127,No.4GPS基带信号源的数字模拟实现田 琨 聂 磊北京航天自动控制研究所,北京100854摘 要 首先对GPS信号产生原理进行了分析,然后给出了一种基带数字信号源的产生方法,即用码发生器产生伪随机码,先和导航数据进行调制,再调制上用DDS产生的载波信号,最终形成一颗或多颗GPS卫星信号。

该方法用FPG A实现,不仅可以模拟GPS卫星信号的特性,而且考虑到调试接收机的动态捕获性能,信号源中还模拟了信号在运动状态下的情况。

该方法为接收机基带信号处理部分的调试节省了大量的时间,针对基带部分提供信号源,减少了调试中其他因素(例如射频部分)的错误而带来的干扰。

关键词 GPS;伪随机码;载波DDS;调制中图分类号:T N927+.2 文献标识码:A文章编号:100623242(2009)0420066205A M ethod of S i m ul a ti n g D i g it a l GPS Ba seband S i gna lTI A N Kun N I E LeiBeijing Aer os pace Aut omatic Contr ol I nstitute,Beijing100854,ChinaAbstract The thesis focuses all the atten tion on finding a solution to si m ulate GPS baseband signal,i.e.pseudocode generated by code2generator m odulates w ith navigation data,then m odulates w ith carrier gener2 ated by DDS.Th is solu tion can si m u late several GPS sa tellites to generate GPS baseband signal through a dig ital e m ulation m ethod in FPG A.Considering debug the dynam ic capture perfor m ance of GPS receiver, this solution also si m ulates the condition that the GPS receiver is m oving.B y this digital si m ulation of GPS baseband signal,it w ill be convenient and efficient w hile debug the part of baseband signal processing in GPS receiver,and it can decrease the unexpected interference,such as RF,on the perfor m ance of GPS receiver.Key words GPS;Pseudocode;Carrier DDS;M odu late 收稿日期:2008207231作者简介:田 琨(1974-),女,陕西西安人,硕士,工程师,主要研究方向为高动态接收机硬件研究与设计;聂 磊(1980-),男,黑龙江海伦人,硕士,助理工程师,主要研究方向为高动态接收机硬件研究与设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4 结束语

卫星定位接收机基带信号处理模块的芯片化研究是一项以掌握核心技术为目的的研究开发工作 ,它 的开发利用了以先进的设计思想和设计工具搭建起来的通用 GPS信号处理平台 ,使系统灵活性和实用性 大大提高 ,在实现 GPS接收机基本功能的同时 ,多种快速捕获和精确跟踪算法得以在该平台上进行验证 和改进 ,在稍加改动射频前端电路的情况下成为兼容型接收机 ,大大缩短了开发周期 。正因为这些 ,我们 有理由相信它必将对软件接收机的开发产生积极的作用 ,并可将较为成熟的技术应用于 Galileo 系统及我 国的北斗二代系统的研究 。 参考文献

2 基带信号处理模块设计

整个基带数字信号处理模块是由 FPGA 固件来实现 的 。所述模块的 FPGA 内部固件全部由我们自行研制开 发 。其中包括 : 载波 NCO、 码 NCO、 码发生器 、 积分清零单 元等核心单元以及相应的协调工作的必要模块 。以下对 图 1 接收机总体框图 包括码发生器和 NCO 在内的相关器进行描述 。 众所周知 ,任何一个同步捕获电路 ,其核心单元都是检测器 。它可以采用相干方式或者非相干方式 , [1] 可以采用不同的相关器形式 ,例如采用被动式 (匹配滤波器 )或者主动式 (积分清零相关器 ) 。考虑到硬 件实现的可行性 ,如图 2 所示 ,该系统在捕获和跟踪阶段都采用了积分清零相关器 。

3

摘 要 : 论述在 GPS接收机三个功能模块中基带信号处理模块的具体作用 。利用 FPGA 技术的先进性和软件无线 电技术的灵活性开发出具有自主知识产权的功能模块 。介绍其设计实现 ,着重于伪码生成器和 NCO 的实现 ,同时给出 相关的仿真结果 。 关键词 : 全球定位系统 ; 现场可编程门阵列 ; 相关器 ; Gold码 ; 数据振荡器 中图分类号 : P228. 4; TN431. 2 文献标识码 : A 文章编号 : CN11 - 1780 ( 2006 ) 04 - 0013 - 05

2006 年 7 月

遥 测 遥 控

[5]

・1 7 ・ 。

“DUM P ” 信号发生之时 ,并在滑动结束后重新开始新的 CA 码 ,各计数器也全部复位

图 8 码滑动仿真结果 图 9 是载波 NCO 的仿真结果 ,其驱动时钟“clk ” 为 5. 714MHz,频率控制字为 1F7B1B9,其输出频率为 1. 405396845MHz,相位控制字和相 位整调计数在测量值采样时钟 TIC 作用下被锁存 。为便于仿真 , TIC 暂 时设置为 1MHz。整周计数器将相 位累加器溢出的次数记录下来以备 后用 , 对比图中“overflow ” 信号的脉 冲个数和“DCO _Cycle _Count” 寄存 器的值可以看出载波 NCO 的大致 工作情况 。 图 9 载波 NCO 仿真波形

第 27 卷第 4 期

图 2 基带信号处理单元模块图 IF信号进入相关器之后 ,分为同相 ( Ⅰ) 和正交 ( Q ) 支路 , 分别与本地载波 NCO 所产生的本振相乘 , 进行载波剥离 。然后其 I支路和 Q 支路分别与超前 、 即时和滞后三路本地 CA 码相乘 ,进行扩频码剥离本 地产生的三路 CA 码是由在码 NCO 控制下的码发生器产生 ,随后经过 3 位的移位寄存器输出 。设定移位 寄存器时钟速率标称值为 2. 046MHz, 即为码产生器速率的两倍 , 则相关器的超前滞后间隔为半个码 片 。积分部分的积分控制模块包含若干子模块 。 在 FPGA 实现中 ,码控制环路前端模块较为 复杂 ,时序设计也较为繁锁 。它的主要功能模块 包括 : CA 码发生器 、 码 NCO、 码滑动模块 、 码相位 计数 、 历元计数器 、 以及积分清除器 。各个模块 间控制信号的位宽及方向示于图 3。 码发生器和码 NCO 模块是其中的核心模 块 ,这两个模块的性能直接决定了整个码环路前 端模块的性能 。码 NCO 是其他几个模块时钟信 号的来源 ,决定其性能的因素主要有杂散性能 、 输入输出时钟比等 ,其输出时钟用来驱动码发生 器、 码滑动模块 、 码相位计数模块 。码滑动模块 时序的实现也是一大难点 ,它是串行搜索中必不 可少的内容之一 ,它由减法计数器以及各种控制 电路组成 。其主要任务是在计数器回零之前使 码发生器停止工作 ,并在计数期间给积分清除器 和码相位计数器输出一个使能信号 ,表示无效的 工作周期 。而码相位计数器和历元计数器乃是 系统时间的秒内时间标度测量单元 , 分别在码 NCO 输出方波信号和码发生器输出的 DUM P (积 分同步信号 )信号驱动下工作 。

3 10 2 3 6 8 9 10 [ 3 ] 码发生器的逻辑图 ,它生成的多项式分别为 f1 ( x ) = 1 + x + x 和 f2 ( x ) = 1 + x + x + x + x + x + x ,

n

模块在 Reset信号使能之后 ,在频率为 1. 023MHz时钟作用下开始产生 Gold码 。

1 接收机总体框架

从功能角度看 , GPS接收机由射频前端 、 基带数字信号处理模块 、 导航解算及控制模块三个模块组成 。 射频前端模块主要任务是进行射频模拟信号下变频处理 ,同时进行滤波及增益控制 ,最后进行模数变换 , 经过量化之后产生数字信号处理模块所需的数字信号 。数字信号处理模块中首先进行数字下变频处理 , 再经过复数乘法器将中频数字信号变为基带信号 ,最后经过累加积分 ,将各种观测量送出 。导航解算控制 模块主要功能是将收集到的观测量进行处理 ,并给出相应的控制量给数字信号处理模块 ,从而形成闭合环 路 ,同时进行定位解算 。其总体结构示于图 1。

图 4 码产生模块 FPGA 实现图 系统 CA 码序列采用了 Gold 码 ,它是 m ,序列的复合码 , 由两个码长相等 、 码时钟相同的 m 序列优选 对的模 2 和构成 。每改变两个 m 序列相对位移就可以得到一个新的 Gold码序列 。共可以得到一族 2 - 1 个 Gold序列 , GPS系统只选用其中的 32 个作为卫星扩频码 。该系统的 CA 码发生器由两个 10 位移位寄 存器并联 ,将 G1 移位寄存器的输出与经过延时处理的 G2 移位寄存器进行模 2 加构成 。图 5 为并联 Gold

上升沿开始输出所选定的卫星的对应 Gold码 ,为了便于观察 ,我们只给出了相应码的前一小部分 。

图 7 CA 码仿真波形 图 8 的仿真结果是码发生器在码滑动模块作用下进行相位滑动的仿真 ,这里的滑动量为 5,由于其单 位是半码片 ,所以其代表的意思是滑动 2. 5 个码片 。滑动作用时间只是在积分同步信号“DUM P ” 产生之 后才能开始 , 从图 8 中的“FastCLK _out” 信号波形可以看到 , 它被停止了 5 个周期 , 停止的时间是在

概 述

20 世纪 90 年代以来 ,卫星定位技术的应用已经遍及陆地 、 海洋 、 航空和航天等各类军事和民用领域 ,

并已初步形成一个跨学科 ,跨行业的综合性 、 国际性高新技术产业 。在现有的几个卫星导航系统中 , GPS 系统是目前最为完善和用户数量最多的系统 ,对它的研究具有重要的实用价值 。然而 ,只局限于接收机应 用方面的研究是远远不够的 ,国外厂商对于核心技术的垄断与我国目前日益扩大的定位导航市场也是极 不相称的 。所以 , 我们必须自主开发多项核心技术 , 其中包括基带信号处理芯片 。电子设计自动化 ( EDA )技术和可编程逻辑器件 ( PLD )技术的快速发展使得这一设想成为可能 。

[2]

图 3 码环路前端模块

2006 年 7 月 2. 1 CA 码发生器模块

遥 测 遥 控

・1 5 ・

上面所述的模块中 ,尤以 CA 码发生器最为复杂 。考虑到此模块要同时产生 DUM P 信号和 CA 码序 列 ,而 CA 码序列要在码滑动计数器控制下工作 , 故将由码 NCO 产生的驱动时钟分为两路 , 一路产生 DUM P信号 ,另外一路处于码滑动计数器的控制下 。控制信号为图 4 中的“CLK_en ” 信号 。DUM P 信号支 路经过复位模块控制 ,进行 2 分频 ,产生 1. 023MHz的计数时钟 ,并由倒相模块和同步模块控制 ,前者由码 滑动模块的滑动量控制 ,后者由码滑动模块输出的控制量决定 ,最后输出 1023 计数溢出脉冲来作为积分 同步信号 DUM P。 CA 码支路时钟经过复位及选量模块后 , 进入一个由码滑动模块控制的三态门 , 在这里 决定其开关状态 。同样经过 2 分频之后 ,生成码产生核心模块所需要的 1. 023MHz时钟信号 ,最后经过码 片延迟输出到移位寄存器 。在产生码的同时 ,也要像 DUM P 支路一样由同步模块来保证这两个支路的同 步 ,并由 1022 计数器产生滑动允许信号给码滑动模块 。各子模块功能示于图 4。

3 基金项目 : 国家 863 计划资助课题 ( 2004AA133020) ; 北京大学工程研究院平台建设基金项目 。 收稿日期 : 2005 2 09 2 23 收修改稿日期 : 2005 2 11 2 18

・14・

张正 等 , GPS 接收机基带信号处理模块的 FPGA 实现

f0 = FCW

2

L

FCL K

( 5)

图 5 CA 码发生器核心模块逻辑图

当 FCW = 1 时 , 有

f0 = FCL K / 2

L

( 6)

为 DD S的频率分辨率 。 从资源和精度角度考虑 , 该系统载波 NCO 采用了 27 位相位累加器 ,输入时钟 频率为 5. 7142857MH z,故其频率分辨率为

f = ( 1) ( 2)

ω θ △ = π 2 π△ t 2

( 3)

・16・

张正 等 , GPS 接收机基带信号处理模块的 FPGA 实现

第 27 卷第 4 期

θ为一个采样间隔 △ t 之间的 其中 , △ 相位增量 , 采样周期 △ t = 1 / FCL K , 故式 ( 3 ) 可改写成 : θFCL K / 2 π ( 4) f = △ θ 可知 , 若能控制 △ , 就可控制不同的频 θ 率输出 。 △ 受频率控制字 FCW 的控制 , π FCW 2 θ= 即 △ 。 所以 , 改变 FCW 就可得 L 2 到不同的频率输出 f0 , 经过代换处理 , 就得到调谐方程 :