精品课件-数字系统设计基础-第10章

合集下载

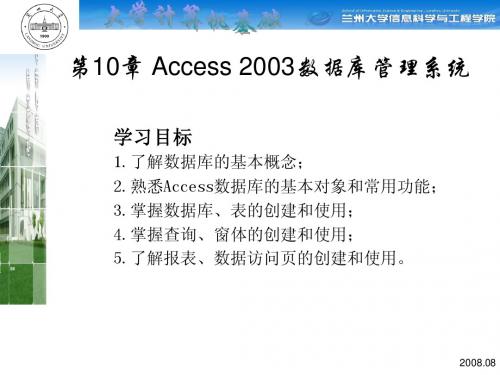

计算机基础第10章

2008.08

例 学生表结构

字段名称

说明

类型

宽度

主键

Stu_ID

学生编号

数字

8

是

Sname

学生姓名

文本

8

否

Age

学生年龄

数字

2

否

Sex

学生性别

文本

2

否

2008.08

4.数据库 数据库DB 数据库 数据库是计算机上的大量结构化的相关的数据集合。 5.数据库管理系统 数据库管理系统DBMS 数据库管理系统 DBMS是位于操作系统与用户之间的数据管理系统软 DBMS的主要功能有: 的主要功能有: 的主要功能有 · 定义功能:对各种数据对象进行定义。 · 数据操作:查询、插入、删除和修改数据。 · 数据库维护:数据的输入、转储,数据库的重组和性能监视 等。 · 数据控制:并发控制;安全保护;数据完整性保护;故障恢 复。 目前常用的DBMS有:目前常用的 有 Oracle,SQL Server,DB2,SyBase,FoxPro,Access等。

2008.08

6.数据库应用系统 数据库应用系统DBAS 数据库应用系统 DBAS是利用数据库资源开发的面向应用的软件系统。 DBAS组成:数据库、操作系统、数据库管理系统、中间件、开发工 具、应用软件、应用界面、数据库管理员(DBA)、用户。 典型的DBAS有: 管理信息系统(MIS)、 企业资源规划(ERP)、 办公自动化系统(OA)、 情报检索系统(IRS)、 客户关系管理(CRM)、 财务信息系统(FIS)等。

2008.08

(5)将主键拖到相关表的相关字段重叠放置,弹出“编辑关系”对话框。

(6)选择“实施参照完整性”,单击【创建】。创建的“关系”如图。

数字电路技术基础第十章

74121的输出脉冲宽度:

tp≈0.7RC

TR-A、TR-B是两个下降沿有效 的触发信号输入端,TR+ 是上 升沿有效的触发信号输入端。 Q和是两个状态互补的输出端。 Rext/Cext、Cext是外接定时电阻 和电容的连接端,外接定时 电阻R(R=1.4kΩ~40kΩ)接 在VCC和Rext/Cext之间,外接定 时 电 容 C ( C=10pF ~ 10μF ) 接在Cext(正)和Rext/Cext之间。 74121内部已设置了一个2kΩ 的定时电阻,Rin 是其引出端, 使用时只需将Rin与VCC连接起 来即可,不用时则应将Rin 开 路。

1

S

D

& G3 电路

0

(a)

1

t

(1)ui=0 时, =1, =0,uo 为高电平,这是第一种稳态。 S R

ui

0

G1 1 R

G2 & uo

ui(V) 1.4 0.7 0 uo 0 (b) 工作波形 UT+ UT- t

1

S

D

& G3

1

1

t

(a) 电路

(1)ui=0 时, =1, =0,uo 为高电平,这是第一种稳态。 S R

· 74221、4538、4098、74HC14、555

等集成电路的应用

7.1 波形变换电路

7.1.1 RC积分与微分电路

New!

7.1.2 单稳态触发器的工作原理

7.1.3 集成单稳态触发器 7.1.4 单稳态触发器应用举例

7.1.1 RC积分与微分电路

RC积分电路

基础知识

tW

电路条件: τ= RC >>tW tW——输入脉冲宽度

《数字系统设计基础》课件

指令执行流程

了解微处理器的指令执行流程和流水线架构,学习如何提高指令的执行效率。

中断和异常处理

掌握中断和异常处理的原理和方法,了解它们在微处理器中的作用。

PCIe和USB等,了解它们的特点和

应用。

3

总线结构

了解计算机总线系统的基本结构和组 成部分,包括数据总线、地址总线和 控制总线。

总线控制

学习总线控制的原理和方法,了解总 线争用和仲裁机制,以及总线的传输 速度和容量。

微处理器架构设计

微处理器基础

介绍微处理器的基本概念和组成部分,包括运算器、控制器和寄存器等。

中央处理器及其指令系统

指令集架构

介绍计算机指令集的类型 和特点,包括精简指令集 (RISC)和复杂指令集 (CISC)。

指令编码和格式

了解指令的编码方式和格 式,学习如何解析和执行 不同类型的指令。

流水线处理

熟悉流水线处理的原理和 优缺点,了解它在提高指 令执行效率方面的作用。

Hale Waihona Puke 输入输出系统输入设备

时钟信号和时序控制

介绍时钟信号的作用和产 生方法,以及时序控制在 数字系统中的应用。

计数器

学习计数器的原理和设计 方法,掌握计数器的工作 原理和时序特性。

计算机的基本组成部分

中央处理器

了解中央处理器的功能和组成 结构,以及CPU在计算机系统 中的作用。

内存

熟悉计算机内存的种类和层次 结构,了解内存在数据存储和 读写过程中的作用。

输入输出设备

掌握计算机输入输出设备的种 类和功能,了解它们在计算机 系统中的作用。

存储器系统

1

主存储器

介绍主存储器的工作原理和组织结构,包括RAM和ROM的特点和应用。

了解微处理器的指令执行流程和流水线架构,学习如何提高指令的执行效率。

中断和异常处理

掌握中断和异常处理的原理和方法,了解它们在微处理器中的作用。

PCIe和USB等,了解它们的特点和

应用。

3

总线结构

了解计算机总线系统的基本结构和组 成部分,包括数据总线、地址总线和 控制总线。

总线控制

学习总线控制的原理和方法,了解总 线争用和仲裁机制,以及总线的传输 速度和容量。

微处理器架构设计

微处理器基础

介绍微处理器的基本概念和组成部分,包括运算器、控制器和寄存器等。

中央处理器及其指令系统

指令集架构

介绍计算机指令集的类型 和特点,包括精简指令集 (RISC)和复杂指令集 (CISC)。

指令编码和格式

了解指令的编码方式和格 式,学习如何解析和执行 不同类型的指令。

流水线处理

熟悉流水线处理的原理和 优缺点,了解它在提高指 令执行效率方面的作用。

Hale Waihona Puke 输入输出系统输入设备

时钟信号和时序控制

介绍时钟信号的作用和产 生方法,以及时序控制在 数字系统中的应用。

计数器

学习计数器的原理和设计 方法,掌握计数器的工作 原理和时序特性。

计算机的基本组成部分

中央处理器

了解中央处理器的功能和组成 结构,以及CPU在计算机系统 中的作用。

内存

熟悉计算机内存的种类和层次 结构,了解内存在数据存储和 读写过程中的作用。

输入输出设备

掌握计算机输入输出设备的种 类和功能,了解它们在计算机 系统中的作用。

存储器系统

1

主存储器

介绍主存储器的工作原理和组织结构,包括RAM和ROM的特点和应用。

数字电路基础数字教案第10章课件

二、CMOS IC

《规范》及指导原则适用于食品药品 监管部 门对第 三类医 疗器械 批发/零 售经营 企业经 营许可 (含变 更和延 续)的 现场核 查,第 二类医 疗器械 批发/零 售经营 企业经 营备案 后的现 场核查 ,以及 医疗器 械经营 企业的 各类监 督检查

施密特触发器的主要特点:

输入信号在上升和下降过程中,电路状态转换的输入 电平不同

当VI 0时, VO0。

当VI ,至VI' VTH时,进入传输大 特区 性, 的故 放

VI' VO1 VO使电路迅速Βιβλιοθήκη 变VO到 VOHV I VTH

R1

R2 R2

V

I

VI

VT

(1

R1 R2

)V TH

《规范》及指导原则适用于食品药品 监管部 门对第 三类医 疗器械 批发/零 售经营 企业经 营许可 (含变 更和延 续)的 现场核 查,第 二类医 疗器械 批发/零 售经营 企业经 营备案 后的现 场核查 ,以及 医疗器 械经营 企业的 各类监 督检查

10.2 施密特触发器(常用的一类脉冲整形电路)

特点 1、两个稳定状态 2、输入信号从低电平上升过程中电路状态转

换时对应的输入电平与输入信号从高电平下 降过程中电路状态转换时对应的输入电平不 同 3、在电路状态转换时,通过电路内部的正反 馈过程使输出电压波形的边沿变陡

《规范》及指导原则适用于食品药品 监管部 门对第 三类医 疗器械 批发/零 售经营 企业经 营许可 (含变 更和延 续)的 现场核 查,第 二类医 疗器械 批发/零 售经营 企业经 营备案 后的现 场核查 ,以及 医疗器 械经营 企业的 各类监 督检查

一、微分型 G1和G2为CMOS门

《规范》及指导原则适用于食品药品 监管部 门对第 三类医 疗器械 批发/零 售经营 企业经 营许可 (含变 更和延 续)的 现场核 查,第 二类医 疗器械 批发/零 售经营 企业经 营备案 后的现 场核查 ,以及 医疗器 械经营 企业的 各类监 督检查

施密特触发器的主要特点:

输入信号在上升和下降过程中,电路状态转换的输入 电平不同

当VI 0时, VO0。

当VI ,至VI' VTH时,进入传输大 特区 性, 的故 放

VI' VO1 VO使电路迅速Βιβλιοθήκη 变VO到 VOHV I VTH

R1

R2 R2

V

I

VI

VT

(1

R1 R2

)V TH

《规范》及指导原则适用于食品药品 监管部 门对第 三类医 疗器械 批发/零 售经营 企业经 营许可 (含变 更和延 续)的 现场核 查,第 二类医 疗器械 批发/零 售经营 企业经 营备案 后的现 场核查 ,以及 医疗器 械经营 企业的 各类监 督检查

10.2 施密特触发器(常用的一类脉冲整形电路)

特点 1、两个稳定状态 2、输入信号从低电平上升过程中电路状态转

换时对应的输入电平与输入信号从高电平下 降过程中电路状态转换时对应的输入电平不 同 3、在电路状态转换时,通过电路内部的正反 馈过程使输出电压波形的边沿变陡

《规范》及指导原则适用于食品药品 监管部 门对第 三类医 疗器械 批发/零 售经营 企业经 营许可 (含变 更和延 续)的 现场核 查,第 二类医 疗器械 批发/零 售经营 企业经 营备案 后的现 场核查 ,以及 医疗器 械经营 企业的 各类监 督检查

一、微分型 G1和G2为CMOS门

数字系统设计基础

X

组合电路

Z

R←0

T3

010

AA+1

CLRA CLRR

E

INCA

控制器

CP1 E=1 发CLRA E=0 发CLRA

CP2

CP3

A0 发CLRR R0 发INCA

A0 发INCA AA+1

数字系统设计基础

(3) ASM图与控制器状态转移图的关系;

T1 001

A←A+1

0

1

E

0F 1

R←0

E F/INCA CLR

数字系统设计基础

T0 初态

0 S 1

A←0,F←0

E←1,F←1

T1 A←A+1

0

1

A3

E←1

E←0

A4 0

1

图 12.3.114 例12.3.3 ASM图

数字系统设计基础

A4

A3

A2

A1

E

0

0

0

0

1

0

0

0

1

0

0

0

1

0

0

数字系统设计基础

F 条件 状态 0 0 0 T1 0 0 0 T1 0 0 0 T1

数字系统设计基础

数字系统设计基础

三、算法状态机图(ASM图) 1.作用 严格按系统时序来描述系统的工作过程。 2.ASM图符号 (1)状态框 (2)条件框 (3)判断框

数字系统设计基础

(1)状态框

符号 二进制代码 寄存器操作

或输出

T3 011

R←0 START

(a)状态框

(b)实例

图12.3.7 状态框

状态框中的操作通常用RTL语言表示,若用助记符 代替,则该助记符是控制器发出的控制命令。

数字系统的设计基础72页PPT

用形式化方法描述数字系统的硬件电路。 80年代后期美国国防部开发出VHDL,1993年推出修订版 Verilog HDL 1993年 与C接近 95年以后国内开展这方面工作

3

第10章:数字系统硬件设计概述

10.1传统的硬件设计方法 ▪ 传统的设计方法是自下而上的设计方法 ▪ 采用通用的元器件 ▪ 后期进行仿真,浪费大,设计周期长 ▪ 主要设计文件是电路原理图,可读性差,文件量大

数字系统的设计基础

6

、

露

凝

无

游

氛

,

天

高

风

景

澈

。

7、翩翩新 来燕,双双入我庐 ,先巢故尚在,相 将还旧居。

8

、

吁

嗟

身

后

名

,

于

我

若

浮

烟

。

9、 陶渊 明( 约 365年 —427年 ),字 元亮, (又 一说名 潜,字 渊明 )号五 柳先生 ,私 谥“靖 节”, 东晋 末期南 朝宋初 期诗 人、文 学家、 辞赋 家、散

5 74LS08

D15

1S 4 74LS151 5

0.1S 3 10mS 2 1mS 1

I0 I1 I2 I3

Z 6

Z

0.1mS 15 I4

10uS 14 I5 13 I6 12 I7

11

10 9

A B C

7E

6 74LS90 12

7

2 3

MS1 MS2

MR1 MR2

Q0 Q1 Q2 Q3

9 8 11

MR1 MR2

Q0 9

Q1 Q2 Q3

8 11

14

D3

1

CLK0 CLK1

3

第10章:数字系统硬件设计概述

10.1传统的硬件设计方法 ▪ 传统的设计方法是自下而上的设计方法 ▪ 采用通用的元器件 ▪ 后期进行仿真,浪费大,设计周期长 ▪ 主要设计文件是电路原理图,可读性差,文件量大

数字系统的设计基础

6

、

露

凝

无

游

氛

,

天

高

风

景

澈

。

7、翩翩新 来燕,双双入我庐 ,先巢故尚在,相 将还旧居。

8

、

吁

嗟

身

后

名

,

于

我

若

浮

烟

。

9、 陶渊 明( 约 365年 —427年 ),字 元亮, (又 一说名 潜,字 渊明 )号五 柳先生 ,私 谥“靖 节”, 东晋 末期南 朝宋初 期诗 人、文 学家、 辞赋 家、散

5 74LS08

D15

1S 4 74LS151 5

0.1S 3 10mS 2 1mS 1

I0 I1 I2 I3

Z 6

Z

0.1mS 15 I4

10uS 14 I5 13 I6 12 I7

11

10 9

A B C

7E

6 74LS90 12

7

2 3

MS1 MS2

MR1 MR2

Q0 Q1 Q2 Q3

9 8 11

MR1 MR2

Q0 9

Q1 Q2 Q3

8 11

14

D3

1

CLK0 CLK1

《数字系统设计基础》教案(特等奖版)

《数字系统设计基础》课程教案

中国矿业大学计算机学院

<<数字系统设计基础>>教案

适用专业:

电子信息科学与技术/计算机科学与技术

年

级:

2013 级

学

期:

第 5 学期

任课教师:

王冠军

授课教材:潘松《EDA 技术与 VHDL(第 3 版)》 ,清华大学出版社

信息科学系教研室

《数字系统设计基础》课程教案

中国矿业大学计算机学院

《数字系统设计基础》课程教案

中国矿业大学计算机学院

授课次数 授课班级 授课章节 教学目的 和要求 教学重点 和难点 教学方法

第3次 信科 13 级 1-4 班

授课日期 授课时数

2015 年 9 月 11 日 2 课时

第 2 章 PLD 硬件特性与编程技术 2.5 硬件测试技术 2.6 FPGA/CPLD 产品概述 2.7 编程与配置 1、通过本次课向学生介绍硬件电路的测试技术; 2、掌握常见的 FPGA/CPLD 产品和相关的技术特征及编程下载方法。 重点:FPGA/CPLD 产品及相关技术特征 难点:基于 PLD 的编程下载方法 多媒体讲授+学生专题讨论 教学活动 首先请学生谈一下对于 硬件测试的认识。(大约 5 分钟),而后,补充并 总结硬件测试技术,以及 与其它技术的关系。 回顾上次课的内容。引 出 PLD 的两个重要分类: FPGA 与 CPLD。 介绍三个公司的 PLD 产品系列,同时介强这三 个公司的相关背景。 类比: 与软件企业类似, 都有自已的产品线系列。

第 0 章 前言 1、这课怎么上? 2、课程内容 3、参考书籍 4、教学资源下载 5、考核方法 教 学 进 程 6、与老师互助渠道 第 1 章概述 1.1 电子设计自动化技术及其发展 1、EDA 技术的引入 2、EDA 技术的三个发展阶段(CAD、CAE、EDA) 3、EDA 技术最新的发展阶段 ESDA 及相关的技术特征 1.2 电子设计自动化应用对象 1、超大规模可编程逻辑器件 (FPGA、CPLD) 2、全定制与半定制 ASIC 3、混合 ASIC 1.3 VHDL 1、常见的硬件描述语言介绍 提高学生的学习兴趣: 1、 数字技术对平常生活 的影响,举例学校的课表 显示系统、校园卡系统、 手机以及平板电脑等。 2、 目前求职市场对于硬 件技术人才的需求旺盛 (中兴、华为) 3、 研究生期间, 本课程 对于计算机专业的重要 性。 以集成电路技术发展过 程的关键人物,关键事件 针对大三这一重要学习 阶段,给出本课程的学习 目标及学习方法。 充分发挥学生的能动性 列出一些供学生上机实践 的题目。

中国矿业大学计算机学院

<<数字系统设计基础>>教案

适用专业:

电子信息科学与技术/计算机科学与技术

年

级:

2013 级

学

期:

第 5 学期

任课教师:

王冠军

授课教材:潘松《EDA 技术与 VHDL(第 3 版)》 ,清华大学出版社

信息科学系教研室

《数字系统设计基础》课程教案

中国矿业大学计算机学院

《数字系统设计基础》课程教案

中国矿业大学计算机学院

授课次数 授课班级 授课章节 教学目的 和要求 教学重点 和难点 教学方法

第3次 信科 13 级 1-4 班

授课日期 授课时数

2015 年 9 月 11 日 2 课时

第 2 章 PLD 硬件特性与编程技术 2.5 硬件测试技术 2.6 FPGA/CPLD 产品概述 2.7 编程与配置 1、通过本次课向学生介绍硬件电路的测试技术; 2、掌握常见的 FPGA/CPLD 产品和相关的技术特征及编程下载方法。 重点:FPGA/CPLD 产品及相关技术特征 难点:基于 PLD 的编程下载方法 多媒体讲授+学生专题讨论 教学活动 首先请学生谈一下对于 硬件测试的认识。(大约 5 分钟),而后,补充并 总结硬件测试技术,以及 与其它技术的关系。 回顾上次课的内容。引 出 PLD 的两个重要分类: FPGA 与 CPLD。 介绍三个公司的 PLD 产品系列,同时介强这三 个公司的相关背景。 类比: 与软件企业类似, 都有自已的产品线系列。

第 0 章 前言 1、这课怎么上? 2、课程内容 3、参考书籍 4、教学资源下载 5、考核方法 教 学 进 程 6、与老师互助渠道 第 1 章概述 1.1 电子设计自动化技术及其发展 1、EDA 技术的引入 2、EDA 技术的三个发展阶段(CAD、CAE、EDA) 3、EDA 技术最新的发展阶段 ESDA 及相关的技术特征 1.2 电子设计自动化应用对象 1、超大规模可编程逻辑器件 (FPGA、CPLD) 2、全定制与半定制 ASIC 3、混合 ASIC 1.3 VHDL 1、常见的硬件描述语言介绍 提高学生的学习兴趣: 1、 数字技术对平常生活 的影响,举例学校的课表 显示系统、校园卡系统、 手机以及平板电脑等。 2、 目前求职市场对于硬 件技术人才的需求旺盛 (中兴、华为) 3、 研究生期间, 本课程 对于计算机专业的重要 性。 以集成电路技术发展过 程的关键人物,关键事件 针对大三这一重要学习 阶段,给出本课程的学习 目标及学习方法。 充分发挥学生的能动性 列出一些供学生上机实践 的题目。

学习入门-学习入门-Altium-Designer第10章-信号完整性分析优选全文

1.互阻抗模型 PCB上两根走线之间的互阻抗模型如图10.1.3所示。

图10.1.3 PCB上两根走线之间的互阻抗模型

2. 电容耦合产生的串扰(容性串扰)

所有两相邻导线之间都存在电容。当在一条线(攻击线或主

动线)加上一个脉冲信号(vs)时,脉冲信号会通过电容Cm

向另一条线(受害线或被动线)耦合一个窄脉冲。也就是两

上升时间,用tr表

示。

图10.1.1 非理想的脉冲(数字)信号波形

2. 带宽(频宽)

对于高速数字电路,决定其所需之带宽(频宽)的是时钟脉冲信

号上升时间tr,而不是时钟脉冲信号的频率。对于频率相同的时 钟信号,如果它们的上升时间tr不同,所需电路的带宽(频宽)

也是不同的[24]。

带宽(频宽)与信号的上升时间tr有关。一个有价值的经验法则 ,信号的带宽(频宽)与上升时间tr的关系[51]可以用下式表示:

信号的传播速度Vp与材料的介电常数εr之间的关系如下所示:

(10.1.3)

式中:C为光速(3×108m/s);εr为材料的介电常数。

10.1.3 反射

1. 反射的产生 反射(Reflection)就是传输线上的回波,信号功率的一部分

经传输线传给负载,另一部分则向源端反射。 信号沿传输线传播时,如果阻抗匹配(源端阻抗、传输线阻

SI、PI和EMI设计紧密关联,而PDN(Power Distribution Network,电源分配网络)是 SI、PI和EMI的公共基础互连,相 互关系[22,25]如图10.1.6所示。而SI、PI和EMI协同设计是高速数字 系统设计的唯一有效途径。

图10.1.6 SI、PI和EMI与PDN的相互关系

EMI到达EMI接收器的路径。

精品课件-数字系统设计基础-第9章

3

3

态保持不变,暂稳态结束,电路将返回到初始的UO=0

第9章 脉冲波形的产生与整形

输出电压UO和电容C上电压UC的工作波形如图9-4(b)所示。

输出脉冲宽度TW是暂稳态的停留时间,根据电容C的充电过 程可知UC

UC(0+)=0 UC(∞)=UCC τ=RC

UT= 2UCC 3

第9章 脉冲波形的产生与整形 代入式(9-2)可得

直保持高电平不变,电路维持在暂稳态UO=1

第9章 脉冲波形的产生与整形

(3) 恢复期:当电容C上的电压上升到U6≥ 2UCC时,此时 3

U2> UC1C,RS触发器置 0,电路输出UO=0,V1导通,电容C通过 3

V1迅速放电,使UC≈0,此时U2> UCC ,U6< 1UCC , RS触2发器状

(9-2)

tW

lnU () U (0 ) U () UT

第9章 脉冲波形的产生与整形 图 9-2 从U(0+)到UT所经历的时间tW

第9章 脉冲波形的产生与整形

9.2 555 定时器

555定时器是一种数字和模拟相结合的中规模集成电路, 它是由于其芯片内部有3个5 kΩ的分压电阻而得名。555定时 器通过外接少量元器件就可以构成多谐振荡器、单稳态触发器 和施密特触发器。由于其使用灵活方便,因而在信号的产生与

UCC, UR22= UCC;若UCO1外接固定电压,则UR1=UCO,

3

3

1

2

第9章 脉冲波形的产生与整形

2. C1和C2为两个电压比较器。每个电压比较器有两个输入端, 标有“+”号的为同相输入端;标有“-”号的为反相输入端。 当同相输入端电压V +大于反相输入端电压V-,即V+> V- 时, 则电压比较器输出为高电平(对应逻辑值1”),反之电压比较 器输出为低电平(对应逻辑值“0”)。 两个输入端基本不向外电路索取电流,即输入电阻趋于无

数字电子技术基础-第十章--数字系统设计

�

第十章 数字系统设计

第一节 概述

一,数字系统的定义 二,数字系统的设计方法

(一)明确设计任务 (二)确定系统方案和逻辑划分 (三)数据通路的设计 (四)控制器的设计

பைடு நூலகம்

三,数字系统的实现方法

(一)采用通用的集成电路实现 (二)采用可编程逻辑器件和硬件描述语言实现 (三)采用单片微处理器作为核心实现 (四)采用片上系统实现

第六节 数字系统设计举例之四

例10-4 在进行智力竞赛抢答题比赛时,各 参赛者考虑好后都想抢先回答,如果没有 合适的设备,主持人将难以分辨出抢答者 的先后顺序,为了使比赛能顺利进行,需 要有一个能判断抢答者的先后顺序的设备, 称为智力竞赛抢答器.本题目要求设计一 个四路抢答器,可容纳4个队参加比赛.

一,状态框

二,判决框

三,条件输出框

第三节 数字系统设计举例之一

例10-1 设计一个数字系统,要求能完成如 下功能:

① 3位二进制数据的装载. ② 数据的左移功能. ③ 数据的普通的右移功能. ④ 兼有运算作用的数据的右移功能.

(1)明确设计要求.

(2)确定系统方案和逻辑划分,分 为控制器和数据通路两部分

第二节 算法状态机

算法状态机(Algorithmic state machine, 算法状态机( , ASM) 是一种描述时钟驱动的控制器的工 ) 作流程的方法. 图的元素包括状态框, 作流程的方法 . ASM图的元素包括状态框 , 图的元素包括状态框 判决框, 条件输出框, 判决框 , 条件输出框 , 输入路径和输出路 径.

(3) 给出待设计数字系统的ASM

(4)控制器的设计

(5)数据通路的设计

(6)用前面学过的同步时序电路的 设计方法设计控制器

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Di 2i

(10-10)

若RF=R,并将I=UR/R代入式(10-10),

U

UR 2n

n1 i0

Di 2i

(10-11)

第10章 数/模与模/数转换电路

10.2.3 1.

D/A转换器的主要技术指标 D/A转换器的转换精度包括分辨率和转换误差两个技

(1) 分辨率用于描述D/A转换器对输入量微小变化的敏感 程度。它是指输入数字量最低有效位为1时,对应输出可分辨 的电压变化量ΔU与数字量输入全为1时的最大输出电压Um之比,

Ii

UR 2n1i

R

UR 2n1 R

2i

(10-2)

第10章 数/模与模/数转换电路 2)当Di=0时,由于Si接地,Ii=0。因此,对于Di位所产生的

Ii

UR 2n1i

R

UR 2n-1 R

2i

Di

(10-3)

n1

n1

I Ii

i1

i0

UR 2n1 R

Di

2i

UR 2n1 R

n1 i0

Di 2i

当D=Dn-1…D0=0…0时,U=0 当D=Dn-1…D0=1…1时, 最大输出电压:

因而U

Um

2n1 2n

U

R

(10-7)

0

U

2n1 2n

U

R

(10-8)

第10章 数/模与模/数转换电路

2. 倒T型电阻网络D/A转换器 图10-3所示为R-2R倒T型D/A 从图中可以看出,由UR向里看的等效电阻为R,数码无论是 0还是1,开关Si都相当于接地。因此,由UR流出的总电流为 I=UR/R,而流入2R支路的电流是按2的倍数递减,流入运算放大

权电阻网络由n个电阻(20R~2n-1R)组成,电阻值的选择应使 流过各电阻支路的电流Ii和对应Di位的权值成正比。例如,数 码最高位Dn-1, 其权值为2n-1,闭合开关Sn-1,连接的 电阻Rn-1=2n-1-(n-1)R=20R;最低位D0,驱动开关S0,连接的权电 阻为R0=2n-1-0R=2n-1R。

(10-4)

第10章 数/模与模/数转换电路

U

RFI

RFU R 2n1 R

n1 i0

Di 2i

若Rf=(1/2)R,代入上式后则得

(10-5)

U

RFU R 2n1 R

n1 i0

Di 2i

UR 2n

n1 i0

Di 2i

(10-6)

从式(10-6)可见,输出模拟电压U的大小与输入二进制数的

第10章 数/模与模/数转换电路

(10-1)

n1

UO (IO ) K Di 2i

i0

其中,K

式(10-1)表明,要实现D/A转换,电路组成上应包括三个

主要部分: 能够反映各位权值大小的解码网络、 能够表示二

进制数0和1

第10章 数/模与模/数转换电路

10.2.2 D/A转换器的主要电路形式 1. 权电阻网络D/A转换器 图 10-2所示是权电阻网络D/A转换器的原理图,它由

权电阻网络、 模拟电子开关S0~Sn-1和求和放大器A

第10章 数/模与模/数转换电路 图 10-2 权电阻网络D/A转换器

第10章 数/模与模/数转换电路

开关Si的位置受数据锁存器输出的数码Di控制,当Di=1时, Si将电阻网络中相应的电阻Ri和基准电压UR接通; 当Di=0时, Si将电阻Ri

分辨率=

U

Um

ห้องสมุดไป่ตู้

1 2n 1

(10-12)

第10章 数/模与模/数转换电路

分辨率越高,转换时对输入量的微小变化的反应越灵敏。 而分辨率与输入数字量的位数有关,n (2) 由于D/A转换器各元件参数值不可避免地存在着误差,这 样D/A转换器的转换精度还应考虑转换误差的影响。转换误差 主要包括:

① 非线性误差。它是电子开关导通的电压降和电阻网络

第10章 数/模与模/数转换电路

第10章 数/模与模/数转换电路

10.1 概述 10.2 D/A转换器 10.3 A/D转换器 习题

第10章 数/模与模/数转换电路

10.1 概 述

随着半导体技术的发展,数字电子技术应用越来越广泛, 为了能使用数字电路来处理模拟信号,必须将模拟信号转换成 数字信号,才能送入数字系统进行处理。处理后的数字信号往 往还要转换成模拟信号,作为最后的输出去控制执行器件。把 从模拟信号到数字信号的转换称为模/数转换,或称为 A/D(Analog to Digital)转换,把从数字信号到模拟信号的转 换称为数/模转换,或称为D/A(Digital to Analog)转换。同 时,把实现A/D转换的电路称为A/D转换器(Analog Digital Converter),简写为ADC; 把实现D/A转换的电路称为D/A转换 器(DigitalAnalog Converter),简写为DAC

第10章 数/模与模/数转换电路

常见的D/A转换器有: 权电阻网络型、 T型电阻网络型、 倒T型电阻网络型和权电流型等。

A/D转换器的类型也有多种,可分为直接A/D转换器和间接 A/D转换器两大类。在直接A/D转换器中,输入的模拟信号直接 被转换成相应的数字信号; 而在间接A/D转换器中,输入的模 拟信号先被转换成某种中间变量(如时间、频率等),然后再将 中间变量转换为最后的数字量。

第10章 数/模与模/数转换电路 10.2 D/A转换器

10.2.1 D/A D/A转换器是将输入的二进制数字信号(如二进制数NB)转换 D/A转换器的框图如图10-1

第10章 数/模与模/数转换电路 图 10-1 D/A转换器方框图

第10章 数/模与模/数转换电路

输入为n位二进制数NB=Dn-1Dn-2…D1D0,输出的是与输入数 字信号成正比的电压UO或电流IO

第10章 数/模与模/数转换电路

因此,对于任意位Di,其权值为2i,闭合开关Si,连接的 权电阻值为Ri=2n-1-iR,即位权(i)越大, 对应的权电阻值就越 小。这样流过每个电阻的电流就和对应的权值成正比,再将这

当Di=1时,Si将相应的权电阻Ri=2n-1-iR与基准电压UR 接 通,此时,由于运算放大器负输入端为虚地,该支路产生的电

I

Dn1

I 21

Dn1

I 22

D1

I 2n1

D0

I 2n

I 2n

(Dn1 2n1

Dn2 2n2

D1 21

D0

20 )

I 2n

n1 i0

Di 2i

(10-9)

第10章 数/模与模/数转换电路 图 10-3 R-2R倒T型D/A转换器

第10章 数/模与模/数转换电路

U

IRF

IRF 2n

n1 i0