通用雷达并行信号处理系统中软件平台对并行性问题的研究和实现

基于GPU的雷达信息处理并行设计优化技术研究

电子技术• Electronic Technology82 •电子技术与软件工程 Electronic Technology & Software Engineering【关键词】雷达信息处理 GPU 异构并行1 前言目前,雷达系统的发展正在向数字化、软件化的方向发展,未来的趋势是智能化雷达,硬件处理器已经由单核进入多核时代,并且向着异构、众核的趋势发展,雷达的各种功能和工作流程由软件完成。

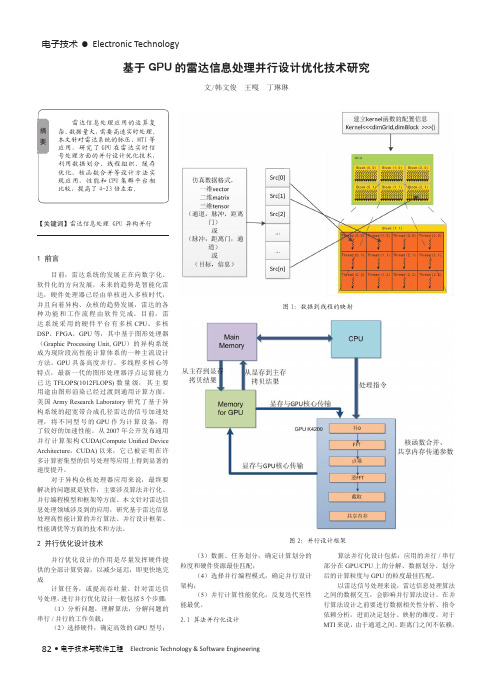

目前,雷达系统采用的硬件平台有多核CPU 、多核DSP 、FPGA ,GPU 等,其中基于图形处理器(Graphic Processing Unit, GPU )的异构系统成为现阶段高性能计算体系的一种主流设计方法。

GPU 具备高度并行、多线程多核心等特点,最新一代的图形处理器浮点运算能力已达TFLOPS(1012FLOPS)数量级,其主要用途由图形渲染已经过渡到通用计算方面。

美国Army Research Laboratory 研究了基于异构系统的超宽带合成孔径雷达的信号加速处理,将不同型号的GPU 作为计算设备,得了较好的加速性能。

从2007年公开发布通用并行计算架构CUDA(Compute Unified Device Architecture ,CUDA)以来,它已被证明在许多计算密集型的信号处理等应用上得到显著的速度提升。

对于异构众核处理器应用来说,最终要解决的问题就是软件,主要涉及算法并行化、并行编程模型和框架等方面。

本文针对雷达信息处理领域涉及到的应用,研究基于雷达信息处理高性能计算的并行算法、并行设计框架、性能调优等方面的技术和方法。

2 并行优化设计技术并行优化设计的作用是尽量发挥硬件提供的全部计算资源,以减少延迟,即更快地完成计算任务,或提高吞吐量。

针对雷达信号处理,进行并行优化设计一般包括5个步骤:(1)分析问题,理解算法,分解问题的串行/并行的工作负载;(2)选择硬件,确定高效的GPU 型号;基于GPU 的雷达信息处理并行设计优化技术研究文/韩文俊 王嘎 丁琳琳(3)数据、任务划分,确定计算划分的粒度和硬件资源最佳匹配;(4)选择并行编程模式,确定并行设计架构;(5)并行计算性能优化,反复迭代至性能最优。

一种PD雷达信号处理系统的并行实现

2 0 1 5年 6月

火 控 雷 达 技 术

Fi r e Co n t r o l Ra d a r Te c h n o l o g y

Vo 1 . 4 4 No . 2( S e r i e s 1 7 2 )

J u n .2 0 1 5

I m pl e me nt a Nhomakorabea i o n o f a Pa r a l l e l Si g n a l Pr o c e s s i ng S y s t e m o f PD Ra da r

Li a n Zh i l i n g

( N o . 3 8 R e s e a c h I n s t i t u t e o f C E T C, H e f e i 2 3 0 0 3 1 ) Ab s t r a c t : A s a c l a s s i c a l r a d a r s i g n a l p r o c e s s i n g m e t h o d , p u l s e - D o p p l e( P D )p r o c e s s i n g i s w i d e l y u s e d i n v a i r o u s r a d a r

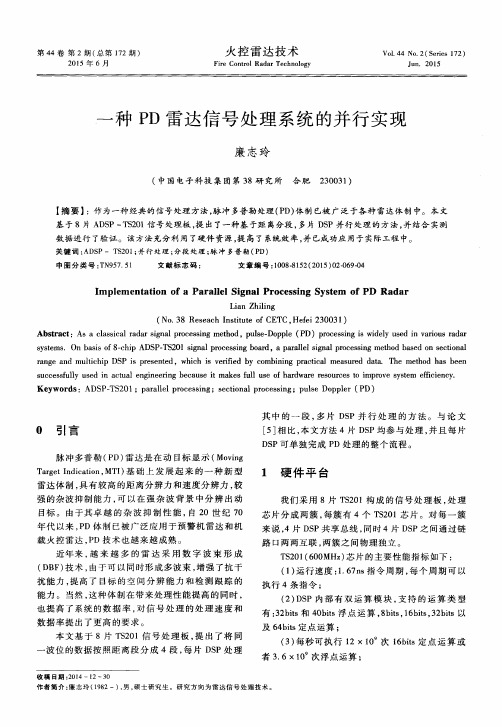

来说 , 4片 D S P共 享 总线 , 同时 4片 D S P之 间通 过链 路 口两两互 联 , 两簇 之间物 理独 立 。 T S 2 0 1 ( 6 0 0 MH z ) 芯 片 的主要性 能指 标如 下 : ( 1 ) 运行 速度 : 1 . 6 7 n s 指令 周期 , 每个 周期 可 以

执 行 4条 指 令 ;

雷达 体制 , 具 有较 高 的距 离分 辨力 和速 度分 辨力 , 较 强 的杂波 抑 制能 力 , 可 以在 强 杂 波 背 景 中分 辨 出动

并行处理技术在雷达数据处理中的应用研究

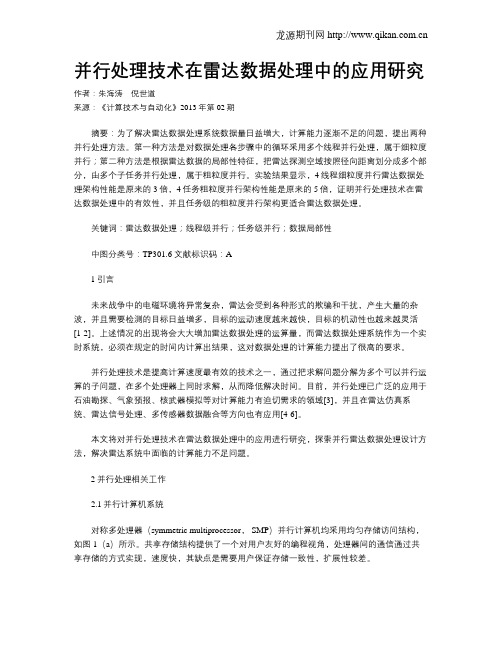

并行处理技术在雷达数据处理中的应用研究作者:朱海涛倪世道来源:《计算技术与自动化》2013年第02期摘要:为了解决雷达数据处理系统数据量日益增大,计算能力逐渐不足的问题,提出两种并行处理方法。

第一种方法是对数据处理各步骤中的循环采用多个线程并行处理,属于细粒度并行;第二种方法是根据雷达数据的局部性特征,把雷达探测空域按照径向距离划分成多个部分,由多个子任务并行处理,属于粗粒度并行。

实验结果显示,4线程细粒度并行雷达数据处理架构性能是原来的3倍,4任务粗粒度并行架构性能是原来的5倍,证明并行处理技术在雷达数据处理中的有效性,并且任务级的粗粒度并行架构更适合雷达数据处理。

关键词:雷达数据处理;线程级并行;任务级并行;数据局部性中图分类号:TP301.6 文献标识码:A1引言未来战争中的电磁环境将异常复杂,雷达会受到各种形式的欺骗和干扰,产生大量的杂波,并且需要检测的目标日益增多,目标的运动速度越来越快,目标的机动性也越来越灵活[1-2]。

上述情况的出现将会大大增加雷达数据处理的运算量,而雷达数据处理系统作为一个实时系统,必须在规定的时间内计算出结果,这对数据处理的计算能力提出了很高的要求。

并行处理技术是提高计算速度最有效的技术之一,通过把求解问题分解为多个可以并行运算的子问题,在多个处理器上同时求解,从而降低解决时间。

目前,并行处理已广泛的应用于石油勘探、气象预报、核武器模拟等对计算能力有迫切需求的领域[3],并且在雷达仿真系统、雷达信号处理、多传感器数据融合等方向也有应用[4-6]。

本文将对并行处理技术在雷达数据处理中的应用进行研究,探索并行雷达数据处理设计方法,解决雷达系统中面临的计算能力不足问题。

2并行处理相关工作2.1并行计算机系统对称多处理器(symmetric multiprocessor, SMP)并行计算机均采用均匀存储访问结构,如图1(a)所示。

共享存储结构提供了一个对用户友好的编程视角,处理器间的通信通过共享存储的方式实现,速度快,其缺点是需要用户保证存储一致性,扩展性较差。

并行处理技术在雷达信号处理中的应用研究

并行处理技术在雷达信号处理中的应用研究并行处理技术在雷达信号处理中的应用研究近年来,雷达技术的发展迅猛,随着雷达应用领域的拓展和传感器技术的不断革新,雷达信号处理的复杂程度也在不断提高。

为了满足对高性能、高速度、高精度的信号处理需求,人们开始广泛探索并行处理技术在雷达信号处理中的应用。

并行处理技术是一种多任务处理方法,通过同时执行多个任务来提高计算机系统的性能和效率。

在雷达信号处理中,由于信号的特殊性,需要对大量的数据进行复杂的算法运算和处理,而传统的串行处理方式往往会因为计算速度慢、处理能力低而无法满足实时性的要求。

因此,并行处理技术的引入成为提高雷达信号处理能力的重要途径。

并行处理技术的最大优势在于能够将任务划分为多个子任务,在多个处理单元上同时进行处理。

首先,通过任务分解和负载均衡,可以将大问题转化为多个小问题,并分配给不同的计算单元同时处理,从而减小了单个处理器的计算压力。

其次,并行处理技术可以加速计算过程,提高算法的运算速度。

在雷达信号处理中,除了需要进行数据采集和预处理外,还需要进行多维度的数据处理,如目标识别、跟踪和目标定位等。

这些任务可以通过并行处理技术同时进行,大大提高了系统的处理能力和实时性。

最后,并行处理技术还能够降低系统的能耗,提高能源利用效率。

在传统的串行处理方式下,大量的计算任务需要通过依次处理的方式完成,导致处理器工作时间长、功耗大。

而并行处理技术可以将任务同时分配给多个处理单元并行处理,减少了每个处理器的负载,并能够充分利用系统资源,从而有效降低整个系统的能耗。

并行处理技术在雷达信号处理中的应用涵盖了整个数据处理流程。

首先,在数据采集环节,通过并行采集技术可以同时采集多路信号,并行将数据传输给处理单元,提高了数据采集效率。

接着,在数据预处理阶段,通过并行计算技术可以同时执行多种数据处理算法,如滤波、降噪、数据校正等,提高了数据的质量和可靠性。

而在目标检测和跟踪阶段,通过并行处理技术可以对多个目标进行同时处理,大大提高了目标检测和跟踪的准确度和实时性。

基于雷达数据处理的并行处理技术研究

Ke y Wo r d s r a d a r d a t a p r oc e s s ,pa r a l l e l p r o c e s s ,l o c a l i t y,a i r s p a c e d i v i s i o n Cl as s Nu mb er TP3 0 ]6

总第 2 8 4期 2 0 1 3 年第 6 期

计算机与数字工程

Co mp u t e r& Di g i t a l En g i n e e r i n g

Vo 1 . 4 1 No . 6

9 22

基 于雷 达 数 据 处 理 的并 行 处 理 技 术 研 究

朱海涛 倪 世 道

内存两种存储结构_ 7 ] 。

对称多 处理 器 ( s y mme t r i c mu l t i p r o c e s s o r , S MP ) 并行

合肥 2 3 0 0 8 8 ) ( 中国电子科技集团公 司第三 十八研究所

摘

要

为了解决 雷达数据处理 系统数据量 日益增大 , 计算 能力逐渐不 足的问题 , 提出 了一种并行 数据处理方法 。在雷达数据处理中 ,

新量测点迹只可能来 自空间位置上与其相近的 目标 , 由此可以得 出雷达数据具有局部性特征 。根据 局部性特征把雷达探测空域按照距离 划

分成 多个部分 , 设计了并行 雷达数据处理架构 , 并在 4节点的分布式存储并行计算机系统上进行了实验 。实验结果表明 , 并行数据处理架构 性能接近原来的 5 倍, 证 明了提 出的并行雷达数据处理架构的正确性和 高效性 。 关键词 雷达数据处理 ; 并行处理 ;局部性 ;空域划分 T P3I n o r d e r t o s o l v e t h e s h o r t a g e o f c o mp u t i n g a b i l i t y i n r a d a r da t a p r o c e s s wi t h i n c r e a s i n g c o mp ut a t i o n,a me t h o d o f p a r a l l e l p r o c e s s i s p r o p o s e d .I n r a d a r d a t a p r o c e s s ,Ne w me a s u r e me n t c a n o n l y be f r o m t a r g e t ne a r i n s p a c e ,wh i c h s h o ws r a da r d a t a l o c a l i t y f e a t u r e . Ra d a r d e t e c t i o n a i r s p a c e i s d i v i d e d i nt o s e v e r a l p a r t s b y r a d i a l r a n g e b a s e d o n t h e l o c a l i t y f e a t u r e,a nd p a r a l l e l r a d a r p r o c e s s a r c h i t e c t u r e i s de — s i g n e d . Th e e x p e r i me n t r e s u l t o n di s t r i b u t e me mo r y p a r a l l e l c o mp u t e r s ys t e m wi t h 4 n o de s s h o ws t h a t ,t h e p e r f o r ma n c e o f p a r a l l e l r a d a r d a t a p r o c e s s i s a l mos t 5 t i me s o f s e r i a l d a t a pr oc e s s ,wh i c h i mpr o v e s t h e c o r r e c t n e s s a n d h i g h e f f i c i e n c y o f t h e p a r a l l e l r a d a r d a t a p r o c e s s a r c h i t e c —

一种雷达通用信号处理系统的实现与应用

一种雷达通用信号处理系统的实现与应用一种雷达通用信号处理系统的实现与应用FPGA是一种现场可编程器件,设计灵活方便可以反复修改内部逻辑,适用于算法结构比较简单、处理速度较高的情况。

DSP是一种基于指令集的处理器,适于大信息、复杂算法的信息处理场合。

鉴于两种处理器件自身优势,FPGA+DSP信号处理架构,已成为信号处理系统的常用结构。

但当前FPGA+DSP的信号处理平台或者是基于某些固定目的,实现某些固定功能,系统的移植性、通用性较差。

或者仅仅简要介绍了平台的结构没有给出一些具体的实现。

本文提出的基于FPGA+DSP通用信号处理平台具有两种处理器的优点,兼颐速度和灵活性,而且可以应用在不同雷达信号处理系统中,具有很强的通用性。

本文举例说明该系统在连续波雷达和脉冲雷达中的典型应用。

1系统资源概述1.1处理器介绍本系统FPGA选择Altera公司的EP2S60F1020。

Stratix II FPGA采用TSMC的90nm 低k绝缘工艺技术。

Stratix II FPGA支持高达1Gb·s-1的高速差分I/O信号,满足新兴接口包括LVDS,LNPECL和HyperTransport标准的高性能需求,支持各种单端I/O接口标准。

EP2S60系列内部有48352个ALUT;具有2544192bit的RAM 块,其中M512RAM(512bit)329个,M4K RAM(4kbit)255个,M-RAM(512kbit)2个。

具有嵌入式DSP块36个,等效18bit×18bit乘法器144个;具有加强型锁相环EPLL4个,快速锁相环FPLL8个。

这些锁相环具有高端功能包括时钟切换,PLL 重新配置,扩频时钟,频率综合,可编程相位偏移,可编程延迟偏移,外部反馈和可编程带宽等。

本系统DSP选择ADI公司的ADSP TS201。

它有高达600MHz的运行速度,1.6ns的指令周期;有24MB的片内DRAM;双运算模块,每个计算块包含1个ALU,一个乘法器,1个移位器,1个寄存器组和1个通信逻辑单元(CLU);双整数ALU,提供数据寻址和指针操作功能;集成I/O接口,包括14通道的DMA控制器,外部端口,4个链路口,SDRAM控制器,可编程标识引脚,2个定时器和定时器输出引脚等用于系统连接;IEEE1149.1兼容的JTAG端口用于在线仿真;通过共享总线可以无缝连接多达8个TigerSHARC DSP。

雷达信号处理机并行自动测试系统设计

雷达信号处理机并行自动测试系统设计

张晓曦;吴翼虎;刘永强

【期刊名称】《计算机测量与控制》

【年(卷),期】2016(24)1

【摘要】为了测试和评价某型雷达信号处理机的功能与性能,提供了一种以PCI总线为基础,结合虚拟仪器、数据库和直接数字频率合成等技术的多机并行自动测试系统设计,实现了为雷达信号处理机提供雷达回波模拟、高稳定度ADC采集时钟和多通道多类型信号输入,重点完成对雷达信号处理机多类型通讯总线测试和关键性能实时检测与分析,结合典型产品定量给出测试结果并分析,验证了测试系统的有效性.

【总页数】3页(P126-127,136)

【作者】张晓曦;吴翼虎;刘永强

【作者单位】中航工业西安航空计算技术研究所,西安 710065;中航工业西安航空计算技术研究所,西安 710065;中航工业西安航空计算技术研究所,西安 710065【正文语种】中文

【中图分类】TP3

【相关文献】

1.基于云计算的并行化自动测试系统设计 [J], 刘杰强;张阿真;刘恒毅;邹国际

2.空时二维雷达信号处理机的系统设计 [J], 王宗谦;苏涛;吴顺君

3.基于LabWindows/CVI的某应答机自动测试系统设计 [J], 刘希

4.基于"单片机+FPGA"的数字芯片自动测试系统设计 [J], 石英;陈心浩;何湘竹

5.基于StarFabric互联的并行雷达信号处理机 [J], 刘国满;郑坤;高梅国

因版权原因,仅展示原文概要,查看原文内容请购买。

通用计算平台上二次雷达信号与信息并行处理简介

• 43•引言:“雷达”是无线电探测及测距的简称,该术语最初是由美国海军提出的。

准确的说,通常所说的雷达都指的是一次雷达。

一次雷达通过旋转的天线向各个方向发射出具有一定频率的高功率脉冲,当发射的电磁波遇到合适的反射面时小部分能量朝天线旋转方向被反射回来。

一次雷达的关键设计就在于能够探测反射能量的装置。

利用这种方式探测到飞机以后,由于无线电波的传播速度是已知的,可以通过测量能量发射和反射能量被接收之间的时间间隔计算出飞机的距离,飞机的方向可以由飞机被探测时天线的方向来确定。

一次雷达的主要优点是其应用广泛,它运行时对要探测的物体没有特殊要求,只需要物体提供合适的反射表面即可,被探测的目标可以是飞机、舰船、车辆、导弹、建筑物以及云雨等等;其缺点在于一次雷达同时获得了来自雨、地面甚至鸟类的反射波,这些额外的反射波增加了其在识别真实目标与背景杂斑的难度,并且一次雷达一般不能提供准确的飞行高度值。

二次雷达,准确的说是二次监视雷达,克服了一次雷达遇到的一些困难,它要求飞机机载一种特殊的收发装备,即应答机。

二次雷达同样通过旋转天线发送无线电频段的脉冲,不同的是其能量功率非常低。

二次雷达发射的能量只需要克服到达应答机的单向路径的能量损耗,而一次雷达必须考虑双向路径的能量损耗。

二次雷达发送功率为几百瓦的脉冲信号,而一次雷达则需要发送功率为几百甚至几千千瓦的脉冲信号。

接收到地面站发射的信号以后,应答机发送一个不同频率的应答信号。

利用询问与应答信号不同的频率,可以滤除易被混淆的来自雨、鸟类及岩层回波。

与一次雷达一样,二次雷达通过时间的延迟和天线的方向来确定飞机的距离和方向。

但是,随着空中交通通信日益繁忙,二次雷达运行过程中的串扰和虚假目标等问题日趋严重,需要更多手段解决所面临问题。

近年来,雷达领域对软件化雷达的关注越来越多。

软件化雷达是软件无线电技术在雷达领域的应用,是雷达向智能化雷达发展必须要经历的历史阶段。

“软件化雷达”是具有标准化、模块化和数字化技术等特点的新型雷达系统,具有开放式体系结构,可以适应“面向实际需求,以软件技术为核心”的开发理念,以软件化开发模式灵活地实现系统扩展、更新和升级并可以基于数据解决雷达遇到的诸多问题(包括但不限于窜扰、虚假目标识别等等),因此是雷达领域的重要发展方向。

软件雷达信号处理的多GPU并行技术

软件雷达信号处理的多GPU并行技术

秦华;周沫;察豪;左炜

【期刊名称】《西安电子科技大学学报(自然科学版)》

【年(卷),期】2013(040)003

【摘要】针对中央处理器(CPU)平台难以满足雷达信号处理实时性不足的问题,利

用图形处理器(GPU)并行运算能力强的特点,在CPU-GPU异构系统中采用任务级、数据级和线程级并行策略,设计了基于多图形处理器的雷达信号处理并行算法.新算

法根据图形处理器的访存机制进行优化设计,充分利用了图形处理器的并行计算资源.实验结果表明:基于4块图形处理器的多任务并行化计算平台与中央处理器平台相比较,加速比最大可达42.78,并且能够满足雷达信号处理的实时性要求.

【总页数】7页(P145-151)

【作者】秦华;周沫;察豪;左炜

【作者单位】海军工程大学海洋电磁环境研究所,湖北武汉430033;海军工程大学

海洋电磁环境研究所,湖北武汉430033;海军工程大学海洋电磁环境研究所,湖北武

汉430033;海军工程大学电子工程学院,湖北武汉430033

【正文语种】中文

【中图分类】TN958

【相关文献】

1.基于GPU加速的雷达信号处理并行技术 [J], 秦华;周沫;察豪;沈括

2.多GPU并行技术在雷达信号处理中的应用 [J], 栾厚斌;王玫;;

3.基于GPU的软件雷达信号处理 [J], 田乾元; 徐朝阳; 赵泉

4.GPU 并行计算在雷达信号处理中的应用 [J], 杨千禾

5.GPU并行计算在雷达信号处理中的应用 [J], 杨千禾

因版权原因,仅展示原文概要,查看原文内容请购买。

软件雷达信号处理的多GPU并行技术

中 图分 类 号 : T N9 5 8 文献标识码 : A 文章 编 号 : 1 0 0 1 - 2 4 0 0Re s e a r c h o n mu l t i — GPU pa r a l l e l t e c h no l o g y i n s o f t wa r e r a d a r s i g na l pr o c e s s i ng

摘 要 :针 对 中央 处 理 器 ( C P U) 平 台难 以满 足 雷达 信 号 处 理 实 时 性 不 足 的 问题 , 利 用 图形 处 理 器 ( GP U) 并 行运 算能力强的特点 , 在C P U— GP U 异 构 系 统 中采 用 任 务 级 、 数据级 和线程 级并行 策略 , 设计 了基于 多 图 形处理器 的雷达信号处理并行算法. 新 算 法 根 据 图形 处 理 器 的访 存 机 制 进 行 优 化 设 计 , 充 分 利 用 了图 形 处 理 器 的 并 行 计 算 资 源. 实验 结果 表 明 : 基 于 4块 图形 处 理 器 的 多 任 务 并 行 化 计 算 平 台 与 中央 处 理 器 平 台相 比较 , 加 速 比最 大 可达 4 2 . 7 8 , 并且 能 够 满 足 雷 达 信 号 处 理 的 实 时性 要 求.

Q N Hu a ,ZHOU Mo ,CHA Ha o ,ZUO We i 。

( 1 .El e c t r o ma g n e t i s m I n s t i t u t e o f Oc e a n,Na v a l En g i n e e r i n g Un i v . ,W u h a n 4 3 0 0 3 3 ,Ch i n a 2.S c h o o l o f E l e c t r o n i c En g i n e e r i n g ,Na v a l E n g i n e e r i n g Un i v. ,W u h a n 4 3 0 0 3 3 ,C h i n a ) A b s t r a c t : S i n c e t h e c o n v e n t i o n a l c e n t r a l p r o c e s s i n g u n i t( C PU ) p l a t f o r m c o u l d h a r d l y f u l f i l 1 t h e r e a l - t i me r e q u i r e me n t o f r a d a r s i g n a l p r o c e s s i n g, a s o f t wa r e r a d a r s i g n a l p a r a l l e l p r o c e s s i n g a l g o r i t h m b a s e d o n mu l t i - GP U i s

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

通用雷达并行信号处理系统中软件平台对并行性问题的研究

和实现

作者:周鸣昕, 汤俊, 彭应宁, 王秀坛

作者单位:清华大学电子工程系,北京,100084

刊名:

计算机应用研究

英文刊名:APPLICATION RESEARCH OF COMPUTERS

年,卷(期):2002,19(11)

被引用次数:1次

1.吕映芝;张素琴;蒋维社编译原理 1998

2.许勇;汤俊一种适于软件雷达系统数据结构的设计和实现[期刊论文]-系统工程与电子技术 2001(02)

3.Hwang Kai;Xu Zhi-wei Sealable Parallel Computers for Realtime Signal Processing 1996(07)

4.Hwang Kai;王鼎兴高等计算机系统结构--并行性,可扩展性,可编程性 1995

1.杨玥.王秀坛基于超级计算机的通用并行雷达信号处理[期刊论文]-微计算机信息 2005(30)

本文链接:/Periodical_jsjyyyj200211017.aspx。