根据FPGA技术完成对加减速控制器的设计

基于LabVIEW_FPGA的步进电机控制系统设计毕业设计论文

毕业设计(论文)任务书摘要步进电机作为执行机构,是机电一体化的关键产品之一。

步进电机突出的优点是它可以在宽广的频率范围内,通过改变脉冲频率来实现调速,快速起停、正反转控制等,并且由其组成的开环系统既简单、廉价,又非常可靠,广泛地应用在各种计算机控制的自动系统中。

随着微电子和计算机技术的发展,步进电机的需求和应用量与日俱增。

本文研究了步进电机的工作原理,对步进电机控制系统进行了整体方案的设计、硬件的选择及接线;在学习了LabVIEW的基础上,研究了LabVIEW FPGA模块的编程和应用;对PXI-7833R板卡进行了全面的学习,研究了如何使用LabVIEW对FPGA板卡进行编程;通过LabVIEW完成产生频率可调的脉冲信号和布尔信号的程序,经编译后下载到PXI-7833R板卡,以实现步进电机控制脉冲及方向信号的生成;完成了步进电机控制系统的软件设计,包括前面板设计、连续运转和指定角度运转程序以及步进电机启动和停止过程的加减速程序。

最后,完成了程序的调试,验证该步进电机控制系统设计的可行性。

本文将虚拟仪器与FPGA技术应用于步进电机的速度控制和转动方向控制,对拓宽步进电机的应用领域具有积极的意义。

关键词:步进电机控制;LabVIEW;FPGA ;脉冲发生AbstractAs executive components,stepping motor is one of the key products of mechatronics,widely used in all kinds of automatic control system. Stepping motor’s prominent advantage is that it can realize speed change, fast start and stop, positive and negative control and so on in wide frequency range, by changing the pulse frequency, and the open loop system made up by which is very simple, cheap, and reliableWith the development of microelectronics and computer technology,the demand and apply for step motor is steadily on the increase., so it has extremely extensive application in many fields.This article Studing the work principle of stepping motor, designing the whole project of the step motor control system, the choice of hardware and wiring; based on the study of LabVIEW, studing the programming and application of LabVIEW FPGA module, and designing by using the FPGA module; studing the PXI-7833R target comprehensively and how to programe on the FPGA target through LabVIEW; completing the program of generating the frequency adjustable pulse signal and Boolean signal Through the LabVIEW, downloading to PXI-7833R after compiling so as to realize the stepping motor control pulse and direction signal generation; Completing the software design of the stepping motor control system, including the front panel design, program of continuous operation, operating at designated angle and the stepping motor ’s acceleration and deceleration during start and stop. At last,completing debug to validate that the design of stepping motor control system is feasible.This study is good for virtual instrument to be used in the step motor speed control and rotation direction control mode, broadening the application field of stepping motor.Key words:stepping motor control;LabVIEW;FPGA;impulse generation.目录摘要 (I)Abstract (II)目录.............................................................................................................. I II 第1章绪论. (1)1.1课题研究的意义及现状 (1)1.2论文主要研究内容 (3)第2章步进电机控制系统总体方案设计 (4)2.1步进电机控制系统的方案选择 (4)2.2步进电机控制系统的开发软件选择 (6)第3章步进电机控制系统硬件的设计 (9)3.1概述 (9)3.2硬件的选择 (9)3.3硬件连线 (23)第4章步进电机控制系统软件的设计 (24)4.1软件编程环境的建立 (24)4.2“连续运行”VI的编程 (25)4.3“指定角度运行”VI的编程 (26)4.4主程序的编程 (27)4.5前面板的设计 (32)第5章实验 (34)5.1接线 (34)5.2软件调试 (36)5.3调试过程的总结 (37)结论 (38)参考文献 (39)致谢 (41)附件1 (42)附件2 (51)第1章绪论1.1 课题研究的意义及现状近年来硬盘制造业高速发展,大容量、小体积、高读取速度的硬盘,是硬盘市场的发展趋势。

FPGA加法器乘法器

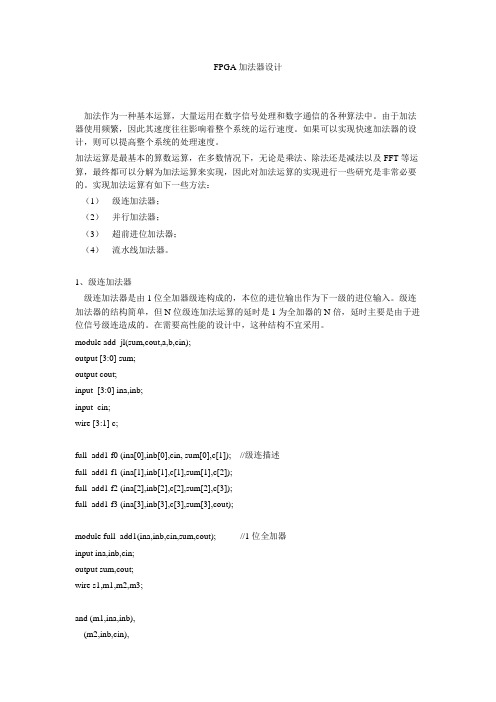

FPGA加法器设计加法作为一种基本运算,大量运用在数字信号处理和数字通信的各种算法中。

由于加法器使用频繁,因此其速度往往影响着整个系统的运行速度。

如果可以实现快速加法器的设计,则可以提高整个系统的处理速度。

加法运算是最基本的算数运算,在多数情况下,无论是乘法、除法还是减法以及FFT等运算,最终都可以分解为加法运算来实现,因此对加法运算的实现进行一些研究是非常必要的。

实现加法运算有如下一些方法:(1)级连加法器;(2)并行加法器;(3)超前进位加法器;(4)流水线加法器。

1、级连加法器级连加法器是由1位全加器级连构成的,本位的进位输出作为下一级的进位输入。

级连加法器的结构简单,但N位级连加法运算的延时是1为全加器的N倍,延时主要是由于进位信号级连造成的。

在需要高性能的设计中,这种结构不宜采用。

module add_jl(sum,cout,a,b,cin);output [3:0] sum;output cout;input [3:0] ina,inb;input cin;wire [3:1] c;full_add1 f0 (ina[0],inb[0],cin, sum[0],c[1]); //级连描述full_add1 f1 (ina[1],inb[1],c[1],sum[1],c[2]);full_add1 f2 (ina[2],inb[2],c[2],sum[2],c[3]);full_add1 f3 (ina[3],inb[3],c[3],sum[3],cout);module full_add1(ina,inb,cin,sum,cout); //1位全加器input ina,inb,cin;output sum,cout;wire s1,m1,m2,m3;and (m1,ina,inb),(m2,inb,cin),(m3,ina,cin);xor (s1,a,b),(sum,s1,cin);or (cout,m1,m2,m3);endmodule2、并行加法器并行加法器可采用Verilog语言的加法运算符直接描述,或称为数据流描述方式,实现容易,其运算速度快,但耗费资源多,尤其是当加法运算的位数较宽时,其耗用资源将会大大增加。

fpga latency 与 delay的解决方法

fpga latency 与 delay的解决方法

1. 流水线设计:采用流水线结构可以将一个大的操作分解为多个小的阶段,并在每个阶段之间插入寄存器,从而减少Latency 和 Delay。

通过并行处理多个操作,可以提高系统的整体性能。

2. 时序约束:在 FPGA 设计中,合理设置时序约束是非常重要的。

通过指定关键路径的时序要求,可以指导综合工具进行优化,减少Latency 和 Delay。

同时,合理的时序约束可以避免时序违规,确保系统的稳定运行。

3. 优化时钟频率:降低时钟频率可以减少信号的传输延迟,从而降低Latency 和Delay。

然而,需要在性能和功耗之间进行权衡。

4. 使用高速时序模块:FPGA 厂商提供了一些高速时序模块,如高速时钟网络、专用乘法器等,可以提高系统的运行速度,减少Latency 和 Delay。

5. 合理布局布线:在 FPGA 实现过程中,布局布线对Latency 和 Delay 有很大影响。

合理的布局布线可以减少走线长度和信号传输延迟,从而提高系统性能。

6. 算法优化:对算法进行优化可以减少操作的次数和数据传输量,从而降低Latency 和 Delay。

例如,使用乒乓操作、数据压缩等技术。

7. 利用硬件加速器:如果系统中存在一些计算密集型任务,可以考虑使用硬件加速器来提高性能。

硬件加速器可以在更短的时间内完成计算,减少Latency 和 Delay。

总之,解决 FPGA 中的Latency 和 Delay 问题需要综合考虑多种因素,并采取适当的优化策略。

在设计过程中,需要不断进行性能评估和时序分析,以确保系统的时序满足要求。

基于双STM32+FPGA的桌面数控车床控制系统设计

2°2作第6期________________________________________________________________NCTechnology数按技术基于双STM32+FPGA的桌面数控车床控制系统设计文杰棱韩震宇王咏麒田海林(四川大学制造科学与工程学院,四川成都610065)摘要:针对桌面数控车床对成本和体积提出的新要求,研究设计出基于双STM32和FPGA的嵌入式数控系统。

将数控系统加工模式重新划分,并按客户机-服务器设计模式将数控系统任务划分为两部分。

针对两部分的任务需求设计对应的硬件系统,在相应的硬件平台研究实现具体软件功能。

最终在两台不同桌面车床进行车削实验,验证修改数控系统在功能、精度和稳定性等方面的不足,实验证明嵌入式数控系统能满足一般数控加工需求。

关键词:桌面数控车床;嵌入式数控系统;客户机-服务器模式;STM32中图分类号:TG659文献标识码:BDOI:10.19287/ki.1005-2402.2021.06.024Design of control system of desktop CNC lathe based on dual STM32+FPGAWEN Jieleng,HAN Zhenyu,WANG Yongqi,TIAN Hailin(School of Mechanical Engineering,Sichuan University,Chengdu610065,CHN)Abstract:For lowering the cost and volume of desktop CNC lathes,an embedded CNC based on STM32and FPGA is researched and designed.The CNC operating modes are redivided,and the whole CNC tasks aredivided into client and server according to the client-server structure.According to the task requirementsof the two parts,the corresponding hardware is designed,the specific software functions are studied andimplemented.Finally,experiments were performed on two different desktop lathes to verify then modifythe deficiencies of the CNC in terms of function,accuracy and stability.The experiment proved that theembedded CNC could meet the general CNC machining needs.Keywords:desktop CNC lathe;embedded CNC;client-server model;STM32桌面数控设备对小尺寸零件加工在成本、功耗和占地面积等方面有着巨大优势。

基于FPGA实现梯形-S形算法

18 集成电路应用 第 38 卷 第 3 期(总第 330 期)2021 年 3 月Research and Design研究与设计0 引言常见的步进电机加减速控制算法有梯形算法[1],指数型算法和S 型算法,三种算法各有特点[2]。

梯形-S 型加减速算法结合了梯形算法和S 型算法的优点[3-5],其核心思想是在速度快速变化的同时让加速度不产生突变[6],使得被控对象能够快速、平稳的运动[7]。

现场可编程门阵列(Field Programmable Gate Array ,FPGA )相比专有集成电路,可以看作为一种半定制电路,用户可根据自己的需求通过特定的布局布线设计出特定功能的集成电路[8]。

1 梯形-S型算法梯形-S 型控制算法共分为5个过程,在运动开始时,首先进入匀加速阶段,加速到一定阶段,进入减加速阶段,通过减加速进入匀速状态Vmax ,之后进入加减速状态开始减速,减速到一定阶段,最后进入减速状态,直至最终的速度Vend 。

梯形-S 型控制的具体操作如下所示:(1)变量初始化。

整个过程所使用的量,都需要回到原始位置。

(2)减加速判断。

将时间划分五等份,当时钟到达t1时,开始减加速过程。

(3)最大速度判断。

当时钟到达t1后,判断是否到达最大速度Vmax ,如果到达则进入匀速状态,否则继续保持减加速状态。

(4)加减速判断。

当时钟到达t3时,开始加减速状态。

(5)加减速开始后,时钟到达t4时,开始匀减速阶段,直至速度减至最小速度Vend ,结束整个过程。

作者简介:郭风祥,天津工业大学控制科学与工程学院,硕士研究生,研究方向:深度学习、FPGA加速。

收稿日期:2020-11-04,修回日期:2021-02-03。

摘要:阐述在分析梯形-S型加减速算法原理的基础上,通过使用查找表法,简化了梯形-S型加减速算法的实现,缩减了梯形-S型加减速算法所需的资源占比。

基于算法进行仿真验证,搭建实验平台对算法进行证实,并且给出脉冲数据表的设计方法和梯形-S型加减速控制的RTL分析试图。

基于DSP和FPGA的激光加工系统控制器的设计

现代电子技术Modern Electronics Technique2014年6月1日第37卷第11期Jun.2014Vol.37No.11在激光数控加工系统中,运动控制器的设计占据极其重要的位置,其性能的好坏影响到工件的加工质量。

现在的激光数控加工系统中的运动控制器,大多数采用“PC 机+运动控制卡”的模式[1⁃2]。

然而,这类激光加工系统的控制器由PC 机通过ISA 总线或者PCI 局部总线来实现直接对电机的控制,从而导致了激光加工系统过多依赖于PC 机,使激光加工系统在脱离PC 机后无法正常工作。

而且,这类激光加工控制器的运动控制模块和激光系统状态监控模块独立分开,集成度不高。

为克服现有激光系统控制器的缺点,根据现有的控制器模式——“DSP+FPGA ”模式[3⁃7],笔者采用TI 公司的TMS320F28335和ALTERA 公司的EP2C8Q208C8N 来实现一种集成度高,同时可独立于PC 机运行的集成激光控制器。

1系统体系概述集成控制器系统硬件平台主要包括:主控模块、通信接口模块、外扩存储器模块、DAC 模块、机构状态监控模块、电机控制信号接口模块。

系统可工作在手动模式和自动加工模式,当系统工作在手动模式时,控制器通过CAN 总线接收来自PC 机或工业触摸屏的操作指令,对被控对象的相关参数进行设定及控制;当系统工作在自动加工模式时,控制器通过CAN 总线接收来自PC 机加工数据,根据加工信息进行速度处理和插补算法运算,从而生成插补脉冲给运动执行单元及激光器的电源控制信号。

而且,控制器在完成加工数据接收后,可以独立于PC 机而正常运行。

系统的核心芯片采用TI 公司C2000系列具有32位浮点数处理单元的TMS320F2833和ALTERA 公司的EP2C8Q208C8N 。

DSP 主要对加工数据进行运算处理、对被控对象进行参数设定及生成控制信号;同时FPGA 利用内部FIFO 对来自DSP 处理好的插补脉冲信息进行缓存并输出、对系统的状态信号进行监控及实现其他相关逻辑控制。

fpga 脉冲电路

fpga 脉冲电路

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,常用于实现各种数字电路和系统。

在 FPGA 中,可以使用逻辑单元和时钟资源来设计和实现脉冲电路。

脉冲电路是一种产生脉冲信号的电路,通常包括时钟信号源、计数器、分频器、延迟线等组件。

以下是一个简单的 FPGA 脉冲电路的设计示例:

1. 时钟信号源:使用 FPGA 内部的时钟资源或外部时钟输入,生成一个基准时钟信号。

2. 计数器:使用计数器对时钟信号进行计数,以控制脉冲的频率和宽度。

3. 分频器(可选):如果需要生成不同频率的脉冲,可以使用分频器对计数器的输出进行分频。

4. 延迟线(可选):可以使用延迟线来调整脉冲的相位或延迟时间。

5. 输出模块:将计数器或分频器的输出连接到 FPGA 的输出引脚,以产生脉冲信号。

在设计脉冲电路时,需要根据具体的需求选择合适的时钟频率、计数器位数、分频比、延迟时间等参数。

同时,还需要注意时序约束和时钟管理,以确保电路的稳定性和可靠性。

这只是一个简单的示例,实际的 FPGA 脉冲电路可能会更加复杂,并且可能包括其他功能,如脉宽调制、脉冲序列生成、触发电路等。

具体的设计将取决于你的具体应用和需求。

如果你需要更详细或特定的信息,我将很愿意帮助你。

请提供更多的背景和具体问题,以便我能够更好地为你提供帮助。

基于FPGA的设计 正文

引言随着经济和科学技术的发展,电梯在高层建筑物的作用越来越凸出。

目前电梯主要分为机械系统与控制系统两大部份,而电梯的控制系统主要有三种控制方式分别是:继电路控制系统(“早期安装的电梯多位继电器控制系统)、基于FPGA控制系统、微机控制系统。

实现继电路控制系统方法很多,可以用标准逻辑器件、可编程序控制器PLC、单片机等方案来实现。

但是这些方法的功能修改及调试都需要硬件电路的支持,在一定程度上增加了功能修改及系统调试的困难,且该系统由于故障率高、可靠性差、控制方式不灵活以及消耗功率大等缺点,已渐渐被人民淘汰。

微机控制系统虽在智能控制方面有较强的功能,但也存在抗扰性差,系统设计复杂,一般维修人员难以掌握其维修技术等缺陷,没能广泛应用电梯中。

而基于FPGA的电梯控制系统由于可靠性高,使用维修方便,抗干扰性强,设计和调试周期较短等优点,在电梯控制中得到广泛应用,从而使电梯由传统的继电器控制方式发展为计算机控制的一个重要方向,成为当前电梯控制和技术改造的热点之一。

本文给出一个基于FPGA的6层自动升降电梯控制系统的设计方案。

它的设计是采用通俗易懂的Verilog HDL硬件描述语言使用EDA技术在Quartus II软件平台上设计完成,程序设计、编译以及时序仿真通过后再下载到开发板配合外围电路(模拟电梯的电路)来验证该系统的可行性。

这个系统分主要有6个模块,分别是键盘响应寄存处理模块、上升/下降请求寄存处理模块、电梯运行和停止处理模块、开门/关门与延时处理模块、电梯运行方向判断模块和电梯运行状态显示模块。

通过模块化设计不仅提高了程序编程错误的排查能力还提高了系统的可靠性。

1 概论1.1 电梯国内外现状1.1.1国内现状电梯作为中国对外最早的行业经过多年的发展,电梯产品无论在数量和质量都有了显著的提高,和国外产品差距越来越小。

考虑到经济性,现有国内的电梯控制系统,通常采用微机或可编程逻辑控制器对变频器进行多段速控制。

基于SDR_的FPGA_加速MIMO_通信系统设计

Telecom Power Technology通信网络技术ADC/DAC射频前端SDR前端处理单元数字信号处理MIMO技术SDR核心处理单元MIMO算法加速并行计算单元FPGA加速单元DAC/RF后端射频后端MIMO后端处理单元图1 系统架构设计Digital to Analog Converter,号转换为数字信号或从中频信号还原为射频信号。

核心处理单元包括数字信号处理()和MIMO信号处理算法,用于信号的处理、滤波、解调,并实施MIMOMIMO算法加速器和并行计算单元,通过 2024年3月25日第41卷第6期153 Telecom Power TechnologyMar. 25, 2024, Vol.41 No.6全清华:基于SDR 的FPGA 加速MIMO 通信系统设计硬件加速提高系统的实时性和处理速度。

MIMO 后端处理单元包括DAC/RF 后端和射频后端,负责将数字信号转换为模拟信号,并进行射频信号调制和解调,与其他通信设备无缝连接。

2 基于SDR 的信号转换与处理方法SDR 前端处理单元和SDR 核心处理单元在射频信号接收、数字信号处理及MIMO 信号处理方面的交互关系如图2所示。

设射频信号为x (t ),经过RF 前端后为y RF (t ),经过ADC 转换得到数字信号为y ADC (t ),该过程用公式表示为 y RF (t )=RF Frontend [x (t )] (1) y ADC (t )=ADC [y RF (t )] (2)SDR 核心处理单元包括DSP 和MIMO 信号处理算法,其数学描述如下:设数字信号为y (n ),DSP 模块进行信号处理、滤波及解调,得到处理后的信号z (n )。

同时,MIMO 信号处理算法处理输入信号,包括信号分离、合并等操作,得到MIMO 系统的输出信号为 z (n )=DSP [y (n )] (3)SDR 核心处理单元SDR 前端处理单元x (t )y RF (t )y ADC (t )z n (t )RF 前端ADCDSPMIMO图2 SDR 的基本原理3 基于FPGA 的MIMO 系统设计文章设计的基于FPGA 的MIMO 系统如图3所示,由发射模块和接收模块2个部分组成。

fpga多通道脉冲计数器的设计与实现

fpga多通道脉冲计数器的设计与实现在数字电路设计领域中,FPGA(现场可编程门阵列)被广泛应用于各种应用,其中包括多通道脉冲计数器。

本文将从FPGA多通道脉冲计数器的设计与实现展开讨论,深入探讨其原理、技术和应用。

1. 引言FPGA多通道脉冲计数器是一种基于FPGA技术的高性能计数器,可同时对多个输入通道的脉冲信号进行计数和分析。

其设计与实现涉及到数字电路设计、时序控制、信号处理等多个方面,具有很高的工程价值和学术研究意义。

2. FPGA技术概述FPGA是一种可编程逻辑器件,具有灵活可编程、并行处理能力强、资源丰富等特点,广泛用于数字信号处理、通信、图像处理等领域。

在多通道脉冲计数器设计中,FPGA的并行计算和资源复用能力将发挥重要作用。

3. 多通道脉冲计数器原理多通道脉冲计数器是指能够同时对多个输入通道的脉冲信号进行计数和统计的计数器。

其原理是通过FPGA多通道输入模块对输入信号进行采样和处理,然后将处理后的数据传输至计数模块进行计数和存储,最终实现对多通道脉冲信号的精确计数和分析。

4. 设计与实现在实际设计中,多通道脉冲计数器的FPGA实现需要考虑到输入通道数、时钟频率、计数精度、数据存储等多个方面的问题。

通过适当的电路设计和FPGA编程,可以实现高性能、高稳定性的多通道脉冲计数器。

5. 应用与展望多通道脉冲计数器在核物理实验、粒子物理研究、医学影像等领域有着广泛的应用前景,其FPGA实现技术将成为未来研究的热点之一。

6. 总结与展望通过本文的讨论,我们全面了解了FPGA多通道脉冲计数器的设计与实现,明确了其原理、技术特点和应用前景。

随着FPGA技术的不断发展和应用,多通道脉冲计数器将在更多领域展现出其重要作用。

个人观点:FPGA多通道脉冲计数器的设计与实现是一个充满挑战和机遇的领域,需要对数字电路、信号处理、FPGA编程等多个方面有深入的理解和应用。

随着科学技术的发展,多通道脉冲计数器将在更多领域得到应用,为相关领域的研究和应用带来新的机遇和突破。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

根据FPGA技术完成对加减速控制器的设计

引言

几十年来,数字技术、计算机技术和永磁材料的迅速发展,为步进电机的应用开辟了广阔

的前景。由步进电机与驱动电路组成的开环数控系统,既非常简单、廉价,又非常可靠。

此外,步进电机还广泛应用于诸如打印机、雕刻机、绘图仪、绣花机及自动化仪表等。正

因为步进电机的广泛应用,对步进电机的控制的研究也越来越多,在启动或加速时若步进

脉冲变化太快,转子由于惯性而跟随不上电信号的变化,产生堵转或失步;在停止或减速

时由于同样原因则可能产生超步。为防止堵转、失步和超步,提高工作频率,要对步进电

机进行升降速控制。本文介绍一个用于自动磨边机的步进电机升降速控制器,由于考虑了

通用性,它可以应用于其他场合。

从步进电机的矩频特性可知,步进电机的输出转矩随着脉冲频率的上升而下降,启动频率

越高,启动转矩就越小,带动负载的能力越差,启动时会造成失步,而在停止时又会发生

过冲。要使步进电机快速的达到所要求的速度又不失步或过冲,其关键在于使加速过程中

加速度所要求的转矩既能充分利用各个运行频率下步进电机所提供的转矩,又不能超过这

个转矩。因此,步进电机的运行一般要经过加速、匀速、减速三个阶段,要求加减速过程

时间尽量的短,恒速时间尽量长。特别是在要求快速响应的工作中,从起点到终点运行的

时间要求最短,这就必须要求加速、减速的过程最短,而恒速时的速度最高。而以前升速

和降速大多选择按直线规律,采用这种方法时,它的脉冲频率的变化有一个恒定的加速度。

在步进电机不失步的条件下,驱动脉冲频率变化的加速度和步进电机转子的角加速度成正

比。在步进电机的转矩随脉冲频率的上升保持恒定时,直线规律的升降速才是理想的升降

速曲线,而步进电机的转矩随脉冲频率的上升而下降,所以直线就不是理想的升降速曲线。

因此,按直线规律升降速这种方法虽然简单,但是它不能保证在升降速的过程中步进电机

转子的角加速度的变化和它的输出力矩变化相适应,不能最大限度的发挥电机的加速性

能。本系统寻求一种基于FPGA控制的按指数规律升降速的离散控制算法,经多次运行,

达到预期目标。