数字电路与逻辑设计复习资料(含答案)

数字逻辑与电路复习题及答案

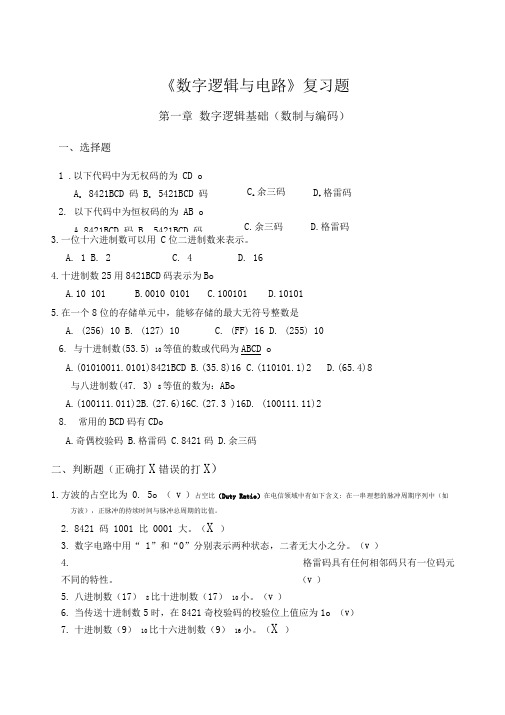

《数字逻辑与电路》复习题第一章数字逻辑基础(数制与编码)一、选择题1.以下代码中为无权码的为CD。

A. 8421BCD码B. 5421BCD码C.余三码D.格雷码2.以下代码中为恒权码的为AB 。

码 B. 5421BCD码 C. 余三码 D. 格雷码3.一位十六进制数可以用 C 位二进制数来表示。

A. 1B. 2C. 4D. 164.十进制数25用8421BCD码表示为 B 。

A.10 101B.0010 0101C.100101D.101015.在一个8位的存储单元中,能够存储的最大无符号整数是CD 。

A.(256)10B.(127)10C.(FF)16D.(255)106.与十进制数()10等值的数或代码为ABCD 。

A. (0101 8421BCDB.16C.2D.87.与八进制数8等值的数为:A B 。

A.2B.16C. )16D. 28. 常用的B CD码有CD。

A.奇偶校验码B.格雷码码 D.余三码二、判断题(正确打√,错误的打×)1. 方波的占空比为。

(√)2. 8421码1001比0001大。

(×)3. 数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

(√)4.格雷码具有任何相邻码只有一位码元不同的特性。

(√)5.八进制数(17)8比十进制数(17)10小。

(√)6.当传送十进制数5时,在8421奇校验码的校验位上值应为1。

(√)7.十进制数(9)10比十六进制数(9)16小。

(×)8.当8421奇校验码在传送十进制数(8)10时,在校验位上出现了1时,表明在传送过程中出现了错误。

(√)三、填空题1.数字信号的特点是在时间上和幅值上都是断续变化的,其高电平和低电平常用1和0来表示。

2.分析数字电路的主要工具是逻辑代数,数字电路又称作逻辑电路。

3.在数字电路中,常用的计数制除十进制外,还有二进制、八进制、十六进制。

4.常用的BCD码有8421BCD码、2421BCD码、5421BCD码、余三码等。

《数字电路与逻辑设计》试题及答案

《数字电路与逻辑设计》试题院校_ _ 年级_____ _____ 专业层次专升本姓名______________ 分数______________一. 填空题(每小题2分,共10分)1.任何有限的逻辑关系,不管多么复杂,其逻辑函数都可通过逻辑变量的与、或、非三种运算符加以实现,但逻辑函数的一般表达式唯一的,而其标准表达式唯一的。

2.任意两个最小项之积为,任意两个最大项之和为。

3.对于逻辑函数BCAABF+=,但这=,为了化简,利用逻辑代数的基本定理,可表示为CAB+ACF+可能引起型险象,因为在B=1、C=1时,化简前逻辑函数的值恒为1,但化简后逻辑函数的值为AA+。

4.当我们在计算机键盘上按一个标为“9”的按键时,键盘向主机送出一个ASCII码,这个ASCII码的值为。

5.在3.3V供电的数字系统里,所谓的高电平并不是一定是3.3V,而是有一个电压范围,我们把这个电压范围称为容限;同样所谓的低电平并不是一定是0V,而也是有一个电压范围,我们把这个电压范围称为容限。

二. 选择题(每小题2分,共10分)1.在下列程序存储器的种类中,可在线改写的有。

a. PROM;b. E2PROM;c. EPROM;d. FLASH_M2.为了实现某种逻辑运算关系,其实现方法有多种多样,其中历史上曾经用到的有以下几种方式,但实现的空间密度最小、能耗最低、能得到普及应用的实现方式是。

a. 机械式;b.电磁式;c. 分立元件式;d. 集成电路3.在数字电路中,根据电路是否具有反馈记忆功能,将其分为组合逻辑电路和时序逻辑电路两种。

下列各项中,为组合逻辑电路的是,为时序逻辑电路的是。

a. 触发器;b. 译码器;c. 移位寄存器;d. 计数器;e. 加法器;f. 编码器;g. 数值比较器; h. 寄存器; i. 多路选择器4.卡诺图上变量的取值顺序是采用的形式,以便能够用几何上的相邻关系表示逻辑上的相邻。

a. 二进制码;b. 循环码;c. ASCII码;d. 十进制码5.在可编程逻辑芯片中,有PROM、PAL、GAL、CPLD等多种结构方式,其中PROM是,PAL是,GAL是,CPLD是。

数字电路和逻辑设计基础(含答案)

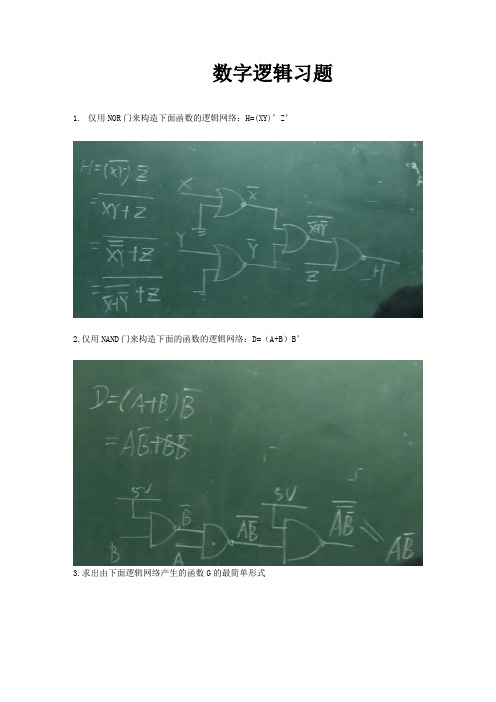

数字逻辑习题1.仅用NOR门来构造下面函数的逻辑网络:H=(XY)’Z’

2.仅用NAND门来构造下面的函数的逻辑网络:D=(A+B)B’

3.求出由下面逻辑网络产生的函数G的最简单形式

4.卡诺图化简:G(A,B,C,D)=Σm(2,3,4,7,8,14,15)

5. 卡诺图化简:G(A,B,C,D)=Σm(0,1,3,4,6,7,12,13,14)

6.卡诺图化简:G(A,B,C,D)=Σm(0,4,5,6,7,8,13,14,15)

7.卡诺图化简:G(A,B,C,D)=Σm(1,2,3,4,6,7,9,12,13)

8.采用一个组合电路来控制一个十进制的七段显示,此电路有4个输入,并提供用压缩十进制数表示的4位代码(0(d)=0000,……8(d)=1000,9(d)=1001)。

7个输出用来定义哪段激活,以显示给定的十进制数

(1)写出这个电路的真值表

(2)用sop形式表示真值表

(3)用pos形式表示真值表

(4)写出各段化简的表达式

7.时序电路分析

补充:。

数字电路及逻辑设计复习题

B

&

&

FB

&

≥1

F

C

&

C

&

(C)

(D)

17. 维持阻塞D触发器电路中,当CP脉冲升沿过后,输入信号D改变,则其输出状态 ______。

(A) 不变; (B) 不定; (C) 随D而变

18. 要实现图中各 TTL 门电路输出端所示的逻辑关系,各电路的接法正确的有 ______________。

A B 悬空

)2。

16. 用与非门实现逻辑函数 Z=AB+AC 时,逻辑表达式应写成__________。

真值表

C 00001111 D1 0 0 1 1 0 0 1 1 D2 0 1 0 1 0 1 0 1 F1 F2 17. 填写如图 TTL 电路的真值表。

D1

&

&

F2

D2

EN F1

C

18. 用代数法可把逻辑函数 Z = AB + ABD + AC + BCD 化简为___________。

相异点

模拟多路转换器

数字多路转换器

11. 凡是使电流IL流入反相器的负载,叫做________,使IL从反相器流出的负载,叫做 ________。

数字电路与逻辑设计

第 6 页 共 24 页

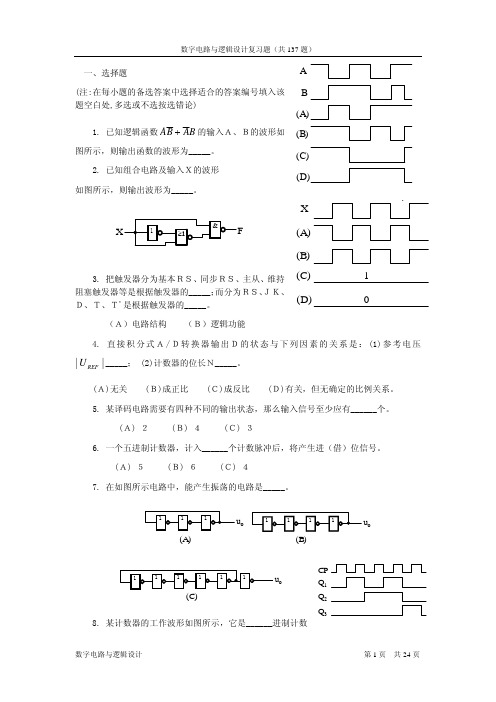

数字电路与逻辑设计复习题(共 137 题)

12. 基本RS、同步RS、主从JK和维持阻塞D四种不同结构的触发器中,可以作计 数器和移位寄存器的有____________________。

| U REF | _____; (2)计数器的位长N_____。

(A)无关 (B)成正比 (C)成反比 (D)有关,但无确定的比例关系。 5. 某译码电路需要有四种不同的输出状态,那么输入信号至少应有______个。

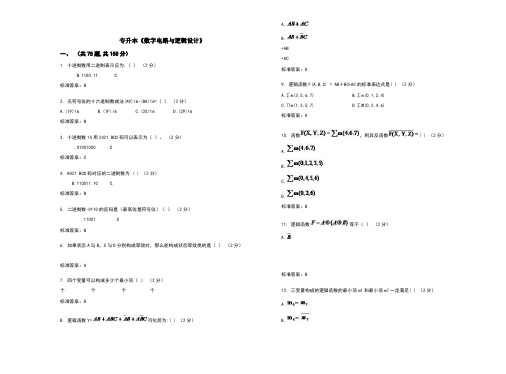

专升本《数字电路与逻辑设计》_试卷_答案

专升本《数字电路与逻辑设计》一、(共75题,共150分)1. 十进制数用二进制表示应为:()(2分)B.1100.11C.标准答案:B2. 无符号位的十六进制数减法(A9)l6-(8A)16=()(2分)A.(19)16B.(1F)l6C.(25)16D.(29)16标准答案:B3. 十进制数15用2421 BCD 码可以表示为()。

(2分).01001000 C标准答案:C4. 8421 BCD码对应的二进制数为 ( ) (2分)B.110011.10C.标准答案:B5. 二进制数-0110的反码是(最高位是符号位)()(2分).11001 C标准答案:B6. 如果状态A与B,C与D分别构成等效对,那么能构成状态等效类的是()(2分)标准答案:A7. 四个变量可以构成多少个最小项()(2分)个个个个标准答案:D8. 逻辑函数Y=可化简为:( ) (2分)A.B.+AB+AC标准答案:D9. 逻辑函数F(A,B,C) = AB+BC+AC的标准表达式是( ) (2分)A.∑m(3,5,6,7)B.∑m(0,1,2,4)C.∏m(1,3,5,7)D.∑M(0,2,4,6)标准答案:A10. 函数,则其反函数( ) (2分)A.B.C.D.标准答案:B11. 逻辑函数等于()(2分)A.标准答案:B12. 三变量构成的逻辑函数的最小项m1和最小项m7一定满足( ) (2分)A.B.C.D.标准答案:C13. 下图为OC门组成的线与电路其输出F为(2分)C.D.标准答案:B14. 要求RS触发器(R、S均为高电平有效)状态由0 →1,其输入信号为()。

(2分)=01 =1 C=d0 =10标准答案:A15. JK触发器的J=K=1,当触发信号到来时,输出次态Qn+1为:( ) (2分)B.0C.不变D.与现态相反标准答案:D16. 设计—个1位十进制计数器至少需要多少个触发器( ) (2分)个个个个标准答案:B17. T型触发器当时钟脉冲输入时,其输出状态()(2分)A.保持不变B.在T=1时会发生改变C.等于输入端T的值D.随时间改变标准答案:B 18. 移位寄存器74194工作在左移串行输入方式时,S1 S0的取值为( ) (2分).01 C标准答案:C19. LED共阴极七段显示器可由下列哪一个IC来推动七字节较适宜()(2分).7447 C标准答案:C20. 电源电压为+12V的555集成定时器中放电三极管工作在截止状态,输出端OUT为1时,其TH 和TR的输入电压值分别为 ( ) (2分)A.,和TR 均大于C.,和TR 均小于标准答案:A21. 逻辑函数,是F的对偶函数,则()。

数字逻辑与电路复习题带参考答案

《数字逻辑与电路》复习题第一章 数字逻辑基础(数制与编码)一、选择题3.一位十六进制数可以用 C 位二进制数来表示。

A. 1B. 2C. 4D. 164.十进制数25用8421BCD 码表示为Bo A.10 101B.0010 0101C.100101D.101015.在一个8位的存储单元中,能够存储的最大无符号整数是A. (256) 10B. (127) 10C. (FF ) 16D. (255) 10与十进制数(53.5) 10等值的数或代码为ABCD o A.(01010011.0101)8421BCD B.(35.8)16 C.(110101.1)2D.(65.4)8与八进制数(47. 3) 8等值的数为:ABoA.(100111.011)2B.(27.6)16C.(27.3 )16D. (100111.11)2 常用的BCD 码有CDoA.奇偶校验码B.格雷码C.8421码D.余三码二、判断题(正确打X 错误的打X )1.方波的占空比为 0. 5o ( V )占空比(Duty Ratio )在电信领域中有如下含义: 在一串理想的脉冲周期序列中(如方波),正脉冲的持续时间与脉冲总周期的比值。

2. 8421 码 1001 比 0001 大。

(X )3. 数字电路中用“ 1”和“0”分别表示两种状态,二者无大小之分。

(V )4.格雷码具有任何相邻码只有一位码元不同的特性。

(V )5. 八进制数(17) 8比十进制数(17) 10小。

(V )6. 当传送十进制数5时,在8421奇校验码的校验位上值应为1o (V )7. 十进制数(9) 10比十六进制数(9) 16小。

(X )1 .以下代码中为无权码的为 CD oA . 8421BCD 码B . 5421BCD 码 2. 以下代码中为恒权码的为 AB oA.8421BCD 码B. 5421BCD 码C .余三码D .格雷码C.余三码D.格雷码6. 8.8.当8421奇校验码在传送十进制数(8)10时,在校验位上出现了1时,表明在传送过程中出现了错误。

数字逻辑复习资料2____答案

数字逻辑复习资料答案一、判断题:下面描述正确的打‘√’,错误的打‘×’1、TTL器件比CMOS器件功耗小[×]2、3线-8线译码器74138有8个数据输入端,3个数据输出端[×]3、7段显示译码器是唯一地址译码器[×]4、数据分配器是单输入多输出通道器件[√]5、数据选择器具有多个数据输入通道[√]6、74LS151是8选1数据选择器,也可用它来实现逻辑函数[√]7、卡诺图可用来化简任意个变量的逻辑表达式[×]8、只要输入信号同时变化,就可消除竞争冒险[×]9、三态门表示有三种输出状态[√]10、集电极开路门可用于线与,但必须接上拉电阻[√]11、为了表示104个信息,需7位二进制编码[√]12、BCD码能表示0至15之间的任意整数[×]13、余3码是有权码[×]14、2421码是无权码[×]15、二值数字逻辑中变量只能取值0和1,且表示数的大小[×]16、计算机主机与鼠标是并行通信[×]17、计算机主机与键盘是串行通信[√]18、占空比等于脉冲宽度除于周期[√]19、上升时间和下降时间越长,器件速度越慢[√]20、卡诺图可用来化简任意个变量的逻辑表达式[×]21、为了增加以下电路的暂稳态时间,可采取方法(1)加大Rd(×);(2)减小R(×);(3)加大C(√);(4)增加输入触发脉冲的宽度(×);(5)减小Cd(×);(6)减小Rd(×);(7)增大Cd(×);(8)减小输入触发脉冲的宽度(×)。

二、写出图中电路的逻辑函数表达式。

1、F=A⊕B2、F=CDAB+三、选择题:(多选题,多选或少选不得分)四、填空题(每空1分,共20分)1、寄存器中,与触发器相配合的控制电路通常由门电路(选择提示:门电路、触发器、晶体二极管)构成。

数字电路与逻辑设计(人民邮电出版社)课后答案(邹红主编)

数字电路与逻辑设计复习

第二章 逻辑函数及其简化 公式法化简

① F=(A⊕B)(B⊕C) ●A+B+A+C

解: F=[(A⊕B)(B⊕C) +A+B] ●(A+C) =[(AB+AB)(BC+BC)+A+B) ●(A+C)

第二章 逻辑函数及其简化 1 若A、B、C、D、E为某逻辑函数输入变量,函数的最大项表达式 所包含的最大项的个数不可能是: A 32 B 15 C 31 D 632 2 以下表达式中符合逻辑运算规则的是: A. C●C=C2 B. 1+1=10 C. 0﹤1 D. A+1=1 3 符合逻辑运算规则的是: A. 1×1=1 B. 1+1=10 C. 1+1=1 D. 1+1=2 4 逻辑函数F=AB+CD+BC的反函数F是:_____;对偶函数F﹡是:____; 5 逻辑代数的三个重要规则是:_________,__________,_________ 当逻辑函数有n个变量时,共有____种变量取值组合。 6 异或与同或在逻辑上正好相反,互为反函数,对吗? 7 逻辑变量的取值,1比0大,对吗? 8 F=A⊕B⊕C=A⊙B⊙C,对吗? 答案:1. D 2. D 3. C 4. ___ 5. ____ ____ 6. √ 7. × 8. √

第一章 绪论 1.数制的转换 (1)任意进制→十进制(按位权展开相加) (2)十进制→任意进制(除R取余,乘R取整) (3) 二进制--八进制--十六进制(中介法) (4)精度要求(1/Ri<精度要求值) 2.常用的BCD码 有权码(8421码、2421码、5121码、631-1码) 无权码(余3码,移存码、余3循环码)。

《数字逻辑与电路》复习题及答案

《数字逻辑与电路》复习题及答案《数字逻辑与电路》复习题第⼀章数字逻辑基础(数制与编码)⼀、选择题1.以下代码中为⽆权码的为CD。

A. 8421BCD码B. 5421BCD码C.余三码D.格雷码2.以下代码中为恒权码的为AB 。

A.8421BCD码B. 5421BCD码C. 余三码D. 格雷码3.⼀位⼗六进制数可以⽤ C 位⼆进制数来表⽰。

A. 1B. 2C. 4D. 164.⼗进制数25⽤8421BCD码表⽰为 B 。

A.10 101B.0010 0101C.100101D.101015.在⼀个8位的存储单元中,能够存储的最⼤⽆符号整数是CD 。

A.(256)10B.(127)10C.(FF)16D.(255)106.与⼗进制数(53.5)10等值的数或代码为ABCD 。

A. (0101 0011.0101)8421BCDB.(35.8)16C.(110101.1)2D.(65.4)87.与⼋进制数(47.3)8等值的数为:A B。

A.(100111.011)2B.(27.6)16C.(27.3 )16D. (100111.11)28.常⽤的B C D码有C D。

A.奇偶校验码B.格雷码C.8421码D.余三码⼆、判断题(正确打√,错误的打×)1. ⽅波的占空⽐为0.5。

(√)2. 8421码1001⽐0001⼤。

(×)3. 数字电路中⽤“1”和“0”分别表⽰两种状态,⼆者⽆⼤⼩之分。

(√)4.格雷码具有任何相邻码只有⼀位码元不同的特性。

(√)5.⼋进制数(17)8⽐⼗进制数(17)10⼩。

(√)6.当传送⼗进制数5时,在8421奇校验码的校验位上值应为1。

(√)7.⼗进制数(9)10⽐⼗六进制数(9)16⼩。

(×)8.当8421奇校验码在传送⼗进制数(8)10时,在校验位上出现了1时,表明在传送过程中出现了错误。

(√)三、填空题1.数字信号的特点是在时间上和幅值上都是断续变化的,其⾼电平和低电平常⽤1和0来表⽰。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电路与逻辑设计复习资料 一、单项选择题 1. 十进制数53转换成八进制数应为( B )。 A. 64 B.65 C. 66 D. 110101 2.将十进制数(18)10 转换成八进制数是(B )。 A. 20 B.22 C. 21 D. 23 3. 十进制数53转换成八进制数应为( D )。 A. 62 B.63 C. 64 D. 65 4. 当逻辑函数有n个变量时,共有( D )种取值组合。 A. n B. 2n C. 2n D. 2

n

5. 为了避免干扰,MOS与门的多余输入端不能( A )处理。 A. 悬空 B. 接低电平 C. 与有用输入端并接 D. 以上都不正确 6. 以下电路中可以实现“线与”功能的有( C )。 A. TTL与非门 B. TTL或非门 C. OC门 D. TTL异或门 7. 用6264型RAM构成一个328K位的存储器,需要( D )根地址线。 A. 12 B. 13 C. 14 D. 15 8. 同步时序电路和异步时序电路比较,其差异在于后者( B )。 A. 没有触发器 B. 没有统一的时钟脉冲控制 C. 没有稳定状态 D. 输出只与内部状态有关 9. 用6264型RAM构成3232K位的存储器,需要( D )片进行扩展。 A. 4 B.8 C. 14 D.16 10. 逻辑函数()FAAB =( D )。

A. ABe B. A C. AB D. B 11. 函数FABCABCD的反函数为( C )。 A. ()()FABCABCD B. ()()FABCABCD C. ()()FABCABCD D. FABCABCD 12.在图1所示的TTL电路中,输出应为( B )。 A . F=0 B. F=1 C. F=A D. F=A

图1 13. 将FABCACDCD展开成最小项表达式应为( A )。 A. (0,3,4,7,8,12,14,15)m B. (0,3,4,7,8,12,13,15)m C. (0,2,4,7,8,12,14,15)m D. (0,3,4,7,8,11,14,15)m 14. 用异或门实现反相功能,多余输入端应接( B )。 A. 地 B. 高电平 C. 低电平 D. 以上都不正确 15. 同CBA相等的逻辑函数表达式是( D )。 A. ()ABC B. ))((CABA C. )(CBA D. ))((CABA 16. 图2是CMOS电路,则输出( C )。 A. YABCDEF B. YABCDEFg C. YABCDEFg D. ()()YABCDEFg

图2 17.下面可以实现线与的是( B )。 A. TTL门 B.OC门 C.三态门 D.以上都不可以 18. 用6264型RAM构成一个168K位的存储器,需要( A )根地址线。 A. 14 B. 13 C. 12 D. 11 19、三变量函数F(A,B,C)=A+BC的最小项表示中不含下列哪项(A )。 A. m2 B.m5 C. m3 D. m7 20、一片64k×8存储容量的只读存储器(ROM),有(C )。 A. 64条地址线和8条数据线 B.64条地址线和16条数据线 C. 16条地址线和8条数据线 D.16条地址线和16条数据线 21、16个触发器构成计数器,该计数器可能的最大计数模值是 (D )。 A. 16 B.32 C. 162 D. 216 22、一个64选1的数据选择器有( A )个选择控制信号输入端。 A. 6 B. 16 C. 32 D. 64 23、函数()FAAB的结果是( C )。 A. AB B. AB C. AB D. AB 24、芯片74LS04中,LS表示:(B )。 A. 高速COMS B. 低功耗肖特基 C. 低速肖特基 D. 低密度高速 25、下列等式不正确的是( C )。 A. ABCABC; B. (A+B)(A+C)=A+BC C. ()AABAB; D. ABACBCABAC 26.用或非门构成钟控R-S触发器发生竞争现象时,输入端的变化是( A )。 A、00→11 B、01→10 C、11→00 D、10→01 27. 对n个变量,最小项的个数为( C )。 A. n B. 21n C. 2n D. 21n 28. 使用TTL集成门电路时,为实现总线系统应该选用( B )门电路。 A. 集电极开路TTL与非门 B. 三态输出门 C. TTL或非门 D. OD门 29. 芯片74LS00中,LS表示 ( B ) A.高速COMS B.低功耗肖特基 C.低速肖特基 D.低密度高速 30. 将一个JK触发器转变成T触发器,JK触发器的输入应该采取的连接方式:( C )

A. JTKT B. 11JK C. JTKT D. JTKT 31. 对于含有约束项的逻辑函数,用卡诺图化简时,任意项( C )处理。 A. 必须当作0 B. 必须当作1 C. 方便化简时当作1,不方便化简时当作0 D. 以上都不正确 32.用全加器将8421BCD码转换成余3BCD码时,其中固定的一个输入端应接( A )。 A. 0011 B.1100 C. 1101 D.1000

二、填空题 1. (0111)8421 BCD= ( 7 )10 。 2. 已知()FABCDg,则其对偶函数为 *()()FABCD 。 3. 当逻辑函数有n个变量时,共有 2n; 种取值组合。 4. 为了避免干扰,MOS门的多余输入端不能 悬空 处理。 5. 在单稳态触发器、多谐振荡器、施密特触发器中具有两个稳态的电路是 施密特触发器 。 6. 已知一个四变量的逻辑函数的标准最小项表示为F(a,b,c,d)=

(0,2,3,4,6,8,9,11,13)m,那么用最小项标准表示*F (2,4,6,7,9,11,12,13,15)m ,以

及F (1,5,7,10,12,14,15)m 。 7. 如果用J-K触发器来实现T触发器功能,则T,J,K三者关系为 T=J=K ;如果要用J-K触发器来实现D触发器功能,则D,J,K三者关系为 D=J=K 。 8. 要构成17进制计数器最少需要 5 个触发器。 9. TTL与门多余输入端应该接 高电平(1) ,TTL或门多余输入端应该接 低电平(0) 。 10. 逻辑函数= B 。 11. 数字电路按照功能可以分为组合逻辑电路和 时序 逻辑电路。 12. 时钟触发器根据时钟控制信号有效时机的不同,可以把触发控制的方式分为两大类,即 电平 触发控制方式和 边沿 触发控制方式。 13. 直接写出下列函数的反演式和对偶式: ABCAF;F= ACAB(+)(+) ; F= ABAC(+)(+) 。

14. 在单稳态触发器、多谐振荡器、施密特触发器中具有两个稳态的电路是施密特触发器 ,具有两个暂态的电路是 多谐振荡器 。

三、分析题 1. 分析图3所示电路的逻辑功能,其中,电路有3个输入变量A,B,C和1个控制变量M。

。 图3 解:01234567,0,0,,0,,,1DMDDDMDDMDMD 由此列出真值表

M=0 M=1 当M=0时实现“意见一致”功能,即A,B,C状态一致时输出为1;当M=1时实现“多数表决”功能,即输出与A,B,C中多数的状态一致。

2. 分析图4所示电路的逻辑功能,写出3210QQQQ的状态转移表(设初始置入的数据为0010)。

图4 解:置入的数据322310,,1,0DQDQDD,1LDQ。 由此列出状态转移表。

电路实现模9的计数分频。 3. 分析图5所示电路的逻辑功能,其中,74LS283是四位二进制加法器,k为控制变量。 图5 解:(1)当0k时,0(03)iiiBkBBi:,0iC 一组数是3210AAAA,另一组数是3210BBBB,电路实现两组数的加法功能。 (2)当1k时,1(03)iiiBkBBi: ,1iC 一组数是3210AAAA,另一组数是3210BBBB取反加1,电路实现两组数的减法功能。

4. 写出图6所示电路的驱动方程、状态转移方程、输出方程和状态转移表,并分析其逻辑功能 (设初始状态为000)。

图6 4.解:驱动方程 13212123133,1,1,1nnnnnJQQKJQKQQJK

状态转移方程和输出方程 11321[]nnnnQQQQCP1212312[]nnnnnnQQQQQQCP 1332[]nnQQQ

23nnZQQ

状态转移表 电路为模7异步计数器,具有自启动功能。 5. 写出图7(a)所示电路的状态转移方程,并在图3(b)中画出Q的波形(设初始状态0nQ)。

(a) (b) 图7

解:1[]nnQAQCP

D Q Q A

CP

= 1