组合逻辑电路知识材料

4 组合逻辑电路

4.1 组合逻辑电路的分析

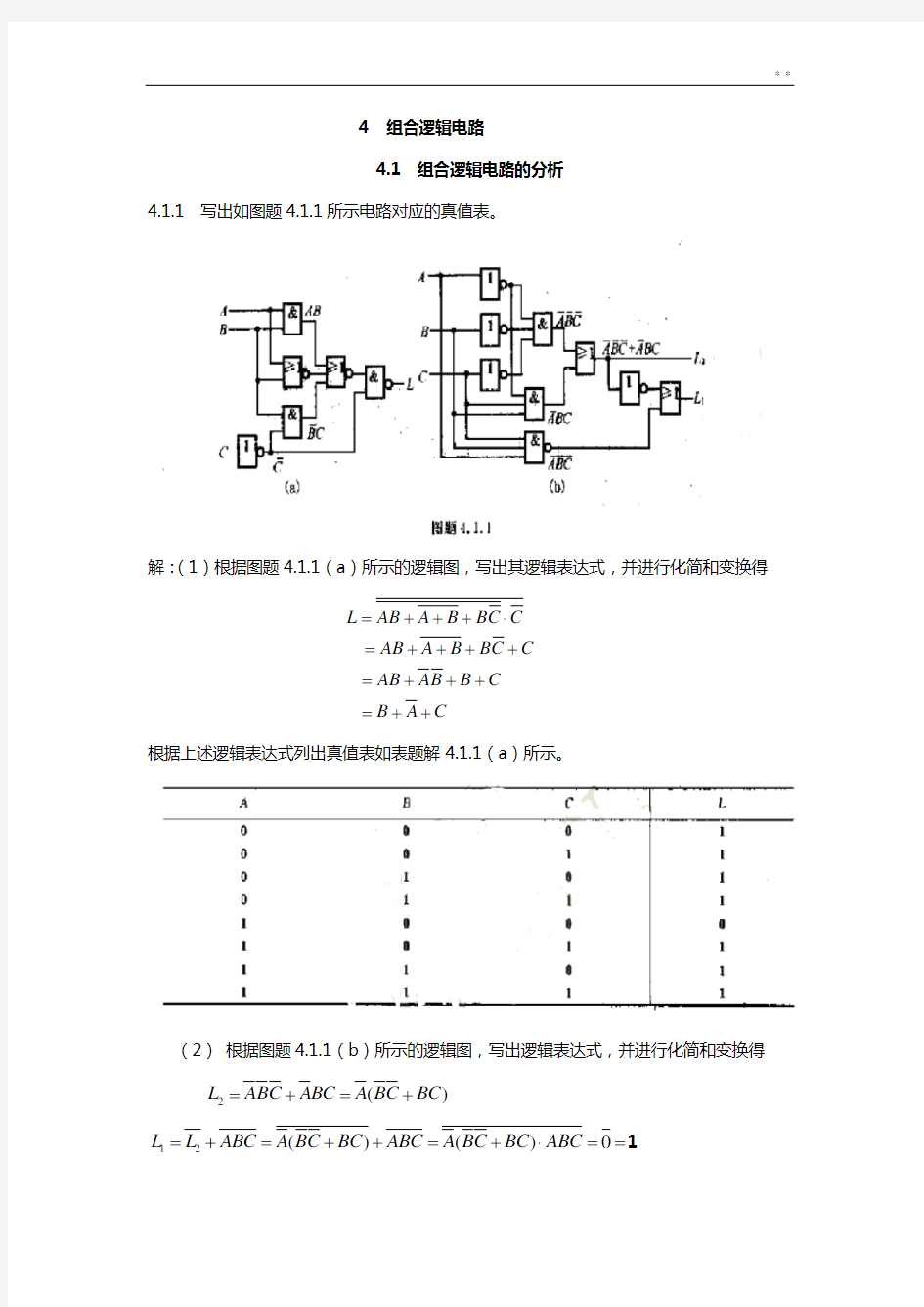

4.1.1 写出如图题4.1.1所示电路对应的真值表。

解:(1)根据图题4.1.1(a )所示的逻辑图,写出其逻辑表达式,并进行化简和变换得

L AB A B BC C AB A B BC C AB AB B C B A C

=+++?=++++=+++=++

根据上述逻辑表达式列出真值表如表题解4.1.1(a )所示。

(2) 根据图题4.1.1(b )所示的逻辑图,写出逻辑表达式,并进行化简和变换得

2()L ABC ABC A BC BC =+=+

12()()0L L ABC A BC BC ABC A BC BC ABC =+=++=+?==1

根据上述逻辑表达式列出真值表,如表题解4.1.1(b)所示。

4.1.2组合逻辑电路及输入波形(A、B)如图题4.1.2所示,试写出输出端的逻辑表达式

并画出输出波形。

解:由逻辑电路写出逻辑表达式

=+=

L AB AB A B

首先将输入波形分段,然后逐段画出输出波形。当A、B信号相同时,输出为1,不同时,输出为0,得到输出波形,如图题解4.1.2所示。

4.1.4 试分析图题4.1.4所示逻辑电路的功能。

解:组合逻辑电路的分析步骤是,首先由逻辑电路写出逻辑表达式,然后根据逻辑表达式列出真值表,再由真值表判断逻辑功能。由逻辑电路写出逻辑表达式

L A C D

=⊕⊕⊕

()()

列出真值表,如表题解4.1.4所示。

由真值表可知,输入奇数个1(或0),输出L=1,输入偶数

个1(或0),输出L=0.该电路为奇校电路。

4.1.5 逻辑电路如图题4.1.5所示,试分析其逻辑功能。

解:根据组合逻辑电路的分析步骤

(1) 由逻辑电路写出输出与输入的逻辑表达式

1L A B AB =+=

2()()L A B A B A B A B AB AB =+++=+?+=+

3L A B AB =+=

(2)

列出真值表,如表题解4.1.5所示。

由真值表可知,当A >B , L 1=1, L 2=L 3=0; 当A <B , L 3=1, L 1=L 2=0; 当A=B , L 2=1,L 1=L 3=0。

该逻辑电路为1位数值比较器。

4.1.6 试分析图题4.1.6所示逻辑电路的功能。

解:根据组合逻辑电路的分析步骤,首先写出逻辑表达式

()

()

O i

i

i i

S A B C

C A B C AB

A B C AB

AB AC BC

=⊕⊕

=⊕?

=⊕+

=++

根据逻辑表达式列真值表,如表题解4.1.6所示。

该电路为1位数全加器。A、B为被加数及加数,

i

C为低位进位,S为和,C O为高位进位。

4.1.7分析图题4.1.7所示逻辑电路的功能。

解:由逻辑电路写出表达式

000

000

11100

1111100

()

S A B

C A B

S A B A B

C A B A B A B

=⊕

=

=⊕⊕

=+⊕

列出真值表,如表题解4.1.7所示。

由逻辑表达式和真值表可判断该电路是2位数全加器。A1A0、B1B0分别为2位被加数及加数,S1、S0为和,C0为A0、B0相加向高位的进位,C1为A1、B1及C0相加向更高位的进位。

4.1.8分析图题4.1.8所示逻辑电路的功能。

解:按照组合逻辑电路的分析步骤进行。

(1)根据逻辑电路可写出各输出端的逻辑表达式,并直接进行化简和变换。

4321L ABC A

B C L BC BC BC BC L C L D

F AB AC AB AC

==++=?=+===?=+

(2) 列写真值表,如表题解4.1.8所示。

(3) 确定逻辑功能。分析真值表可知,当ABCD 所表示的二进制数小于或等于9时,输

出L 4L 3L 2L 1为对应输入的十进制数9的补码。例如,对十进制数8求9的补码为9-8=1。同时标志位F 输出为0。当输入的二进制数大于9时,输出与输入已不是上述的逻辑关系,并且标志位F 输出为1,说明此事电路输出的是伪码。这个电路逻辑功能是计算十进制数9的补码。

4.2 组合逻辑电路的设计

4.2.1 试用2输入与非门设计一个3输入的组合逻辑电路。当输入的二进制码小于3时,输出为0;输入大于等于3时,输出为1。

解:根据组合逻辑的设计过程,首先确定输入、输出变量、列出真值表,由卡诺图化简得到与或式,然后根据要求对表达式进行变换,画出逻辑图。

(1) 设输入变量为A 、B 、C ,输出变量为L ,根据题意列真值表,如表题解4.2.1所示。

(2)由卡诺图化简,如图题解4.2.1(a)所示,经过变换得到逻辑表达式为

=+=

L A BC ABC

(3)用2输入与非门实现上述逻辑表达式,如图题解4.2.1(c)所示。

4.2.2 试设计一个4位的奇偶校验器,即当4位数种有奇数个1时输出为0,否则输出为1.可以采用各种逻辑功能的门电路来实现。

解:(1)按照组合逻辑电路的设计步骤,设4个输入为A、B、C、D,输出为L。当ABCD 中有奇数个1,输出L=0;当ABCD有偶数个1或没有1,输出为L=1,由此列出真值表,如表题解4.2.2。

(2)由真值表画出卡诺图,如图题解4.2.2(a)所示。

(3) 由卡诺图写出逻辑表达式,并进行变换得

()()()()()()()()()()()()()()L ABCD ABCD ABCD ABCD ABCD ABCD ABCD ABCD AB CD CD AB CD CD AB CD CD AB CD CD ABC D AB C D AB C D AB C D AB AB C D AB AB C D A B C D A B C D A B C D

=+++++++=+++++++=⊕+⊕+⊕+⊕=+⊕++⊕=⊕⊕+⊕⊕=⊕⊕⊕

(4) 由逻辑表达式可见,用异或门可以简化逻辑电路,因此,由异或门和非门构成的逻

辑电路,如图题解4.2.2(b )所示。

4.2.4 试设计一可逆的4位码转换电路。当控制信号C=1时,它将8421码转换为格雷码;C=0时,它将格雷码转换为8421码。可以采用任何门电路来实现。

解:(1)设X 3、X 2、X 1、X 0分别为4个输入信号,Y 3、Y 2、Y 1、Y 0分别为4个输出信号,根据题意列出真值表,如表题解4.2.4所示。当C=1时,输入X 3X 2X 1X 0作为8421码,对应的输出g 3g 2g 1g 0为格雷码;当C=0时,输入X 3X 2X 1X 00则作为格雷码,对应的输出b 3b 2b 1b 0为8421码。注意,此事X 3X 2X 1X 0作为格雷码的排列顺序不是按照它所对应的十进制数递增顺序,而是按照8421码的递增顺序排列。

(2)分别画出C=1和C=0时各输出函数的卡诺图,如图题解4.2.4(a )所示。

(3)由卡诺图可求得各输出逻辑表达式。若同时考虑C 变量,当C=1时,有

332323232

12121210101010()()()()()()g X C

g X X X X C X X C g X X X X C X X C g X X X X C X X C

=??=+=⊕??=+=⊕??=+=⊕?

当C=0时,有

3

32

323232

1321321321321323213232132132132103210()()()()()()()()()b X C

b X X X X X X C

b X X X X X X X X X X X X C X X X X X X X X X X C X X X X X X C

X X X C b X X X X C

?=??=+=??=+++????=+++????

??=⊕+⊕????

?=⊕⊕?=⊕⊕⊕?? 将上述两组方程合并,得到总的输出逻辑表达式

333333

222323232

111213212121()()()()()()Y g b X C X C X Y g b X X C X X C X X Y g b X X C X X X C X X C Y X C

=+=+==+=⊕+⊕=⊕=+=⊕+⊕⊕=⊕+⊕

展开且重新组合,得

11

22122000011()()()

Y X CX CY X CX CY Y g b X CX CY =⊕+=⊕?=+=⊕?

由此可画出与非门和异或门实现的逻辑电路,如图题解4.2.4(b )所示。

4.2.5 试设计一组合逻辑电路,能够对输入的4位二进制数进行求反加1的运算。可以 采用任何门电路来实现。

解:(1)设输入变量为A 、B 、C 、D ,输出变量L 3、L 2、L 1、L 0,由题意列真值表,如表题解4.2.5所示。

(2) 由真值表画卡诺图,如图题解4.2.5(a )所示。

(3) 由卡诺图可求得各输出逻辑表达式。

3210()()

L AB AC AD ABCD A B C D L BC BD BCD B C D L CD CD C D L D

?=+++?

=⊕++??=++??=⊕+??=+=⊕??=? 根据上述表达式用或门和异或门实现逻辑电路,如图题解4.2.5(b )所示。

4.2.6 某足球评委会由一位教练和三位球迷组成,对裁判员的判罚进行表决。当满足以下

条件时表示同意:有三人或三人以上同意,或者有两人同时同意,但其中一人是教练。试用2输入与非门设计该表决电路。

解:(1)设一位教练和三位球迷分别用A和B、C、D表示,并且这些输入变量为1时表示同意,为0表示不同意。输出L表示表决结果,L为1时表示同意判罚,为0表示不同意。由此列出真值表,如表题解4.2.7所示。

(2)由真值表画卡诺图,如图题解4.2.7(a)所示。

由卡诺图化简得

L=AB+AC+AD+BCD

由于规定只能用2输入与非门,将上式变换为两变量的与非-与非运算式

L AB AC AD BCD

AB AC AD B CD

=???

=????

(1)根据L的逻辑表达式,画出由2输入与非门组成的逻辑电路,如图题解4.2.7(b)所示。

4.2.7设计一2位二进制数相加得逻辑电路,可以用任何门电路实现。

提示:

10

10

10

A A

B B

S S

A1、A0和B1、B0分别为被加数和加数,S1、S0为相加的和,C1为进位位。

解:设A1、A0和B1、B0分别为2位数加法的被加数和加数。S1、S0为2位数加法的和,C1为向更高位的进位。由此列出真值表,如表题解4.2.8所示。

由真值表可得卡诺图,如图题解4.2.8(a)所示。

由卡诺图可得S 1、S 0、C 1的简化逻辑表达式

111011011011011001100

0111101111001111110000111100001111000000000

11110010011()()()()()()()()()S A B A A B B A B A A B B A B A B A B A B A A B A B B A B A B A B A B A B A B A B A B A B A B A B A B A B A B A B S A B A B A B C A B A A B B A B A B =+++++=+++++=⊕++⊕=⊕+⊕=⊕⊕=+=⊕=++=0011()

A B A B ++

由逻辑表达式可以画出逻辑图,如图题解4.2.8(b )所示。

4.2.9 某雷达站有三部雷达A 、B 、C ,其中A 和B 功率消耗相等,C 的功率是A 的2倍。这些雷达由2台发电机X 和Y 供电,发电机X 的最大输出功率等于雷达A 的功率消耗,发电机Y 的最大功率等于雷达X 的3倍。要求设计一个逻辑电路,能够根据雷达的起动和关闭信号,以最节约得方式起、停发动机。

解:设雷达A 、B 、C 起动为1,关闭为0,发电机X 、Y 起动

为1,停止为0。由题意可知,当A 或B 工作时,只需要X 发电;A 、B 、C 同时工作时,需要X 和Y 同时发电;其他情况只需要Y 发电。由此列出真值表,如表题解4.2.9所示。

由真值表可画出卡诺图,如图题解4.2.9(a )所示。由卡诺图可得简化逻辑表达式

X ABC ABC ABC

Y AB C

=++=+

由逻辑表达式,可画出与、或、非门构成的逻辑电路,如图题解4.2.9(b )所示。

4.3.10有一水箱由大、小两台水泵M L 和M S 供水,如图P3.4所示。水箱中设置了3个水位检测元件A 、B 、C 。水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。现要求当水位超过C 时水泵停止工作;水位低于C 点而高于

B 点时M S 单独工作;水位低于B 点而高于A 点时M L 单独工作;水位低于A 点时M L 和M S 同时工作。试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

真值表中的C AB C,B A ,C B A ,C B A 为约束项,利用卡诺图[图3.4(a)]化简后得到

??

?=+=B

M C

B A M L S )0,1,(M S 状态表示停止状态表示工作的L M 逻辑图如图A3.4(b)

4.4

若干典型的组合逻辑集成电路

4.4.1 优先编码器CD4532的输入端I 1=I 2=I 3=1,其余输入端均为0,试确定其输出Y 2Y 1Y 0。

解:优先编码器CD4532除数据输入端I i 外,还有输入使能端EI ,由于EI=0,根据其功能表可知,使能端EI 没有加有效信号,所以,Y 2Y 1Y 0=000。

4.4.2 试用与非门设计一4输入的优先编码器,要求输入、输出及工作状态标志均为高电平有效。列出真值表,画出逻辑图。

解:设输入I 0、I 1、I 2、I 3,输出及工作状态标志分别为Y 0、Y 1和GS ,根据题意列出真值表,如表题解4.4.2所示。由真值表可以得出该优先编码器的逻辑表达式,并写出与非﹣与非表达式

323

12323232123013130123

0123Y I I I I I I I Y I I I I I I I I I I GS I I I I I I I I =+=+==+=+==+++= 由与非门构成的逻辑电路如图题解4.4.2所示。

(1) 优先编码器74HC147的功能表如表题4.4.3所示,试用74HC147和适当的门构成

输出为8421BCD 码,并具有编码输出标志的编码器。

Y Y Y Y是8421BCD码的反码,因此只要在74HC147的解:由表题4.4.3可知,输出3210

输出端增加反相器就可以获得题中所要求的输出码。在输入端均为高电平时工作状态标志GS位0,而有低电平信号输入时GS为1,可由与非门实现此功能。74HC147为9个输入

I I时,L3~L0为0,GS 端,此题需要10个输入端,因此0I接在与非门的输入端,当09

为1。题中所要求的编码器的逻辑电路如图题解4.4.3所示。

4.4.5为了使74HC138译码器的第10脚输出为低电平,试标出各输入端应置的逻辑电平。解:首先查74HC138的引脚图,了解各个引脚的含义。根据题意,74HC138的引脚图如图题解4.4.5所示。当A2、A0、E3接高电平,

A、2E、1E接低电平,电源输入端16号

2

脚解﹢5V,接地端8号脚接地时,第10号脚5Y输出为低电平。

组合逻辑电路习题解答

自我检测题 1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。 2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。 3.8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为 2Y 1Y 0Y 。输入输出均为低电平有效。当输入7I 6I 5I …0I 为时,输出2Y 1Y 0Y 为 010 。 4.3线—8线译码器74HC138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 。 5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。 6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。 7.一位数值比较器,输入信号为两个要比较的一位二进制数,用A 、B 表示,输出信号为比较结果:Y (A >B ) 、Y (A =B )和Y (A <B ),则Y (A >B )的逻辑表达式为B A 。 8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。 9.多位加法器采用超前进位的目的是简化电路结构 × 。 (√,× ) 10.组合逻辑电路中的冒险是由于 引起的。 A .电路未达到最简 B .电路有多个输出 C .电路中的时延 D .逻辑门类型不同 11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的 A .在输出级加正取样脉冲 B .在输入级加正取样脉冲 C .在输出级加负取样脉冲 D .在输入级加负取样脉冲 12.当二输入与非门输入为 变化时,输出可能有竞争冒险。 A .01→10 B .00→10 C .10→11 D .11→01 13.译码器74HC138的使能端321E E E 取值为 时,处于允许译码状态。 A .011 B .100 C .101 D .010 14.数据分配器和 有着相同的基本电路结构形式。 A .加法器 B .编码器 C .数据选择器 D .译码器 15.在二进制译码器中,若输入有4位代码,则输出有 个信号。 A .2 B .4 C .8 D .16 16.比较两位二进制数A=A 1A 0和B=B 1B 0,当A >B 时输出F =1,则F 表达式是 。 A . B A F = B .0101B B A A F ++= .0011B A B A F ++=

组合逻辑电路基础知识、分析方法

组合逻辑电路基础知识、分析方法 电工电子教研组徐超明 一.教学目标:掌握组合逻辑电路的特点及基本分析方法 二.教学重点:组合逻辑电路分析法 三.教学难点:组合逻辑电路的特点、错误!链接无效。 四.教学方法:新课复习相结合,温故知新,循序渐进; 重点突出,方法多样,反复训练。 组合逻辑电路的基础知识 一、组合逻辑电路的概念 [展示逻辑电路图]分析得出组合逻辑电路的概念:若干个门电路组合起来实现不同逻辑功能的电路。 复习: 名称符号表达式 基本门电路与门Y = AB 或门Y = A+B 非门Y =A 复合门电路 与非门Y = AB 或非门Y = B A+ 与或非门Y = CD AB+ 异或门 Y = A⊕B =B A B A+ 同或门 Y = A⊙B =B A AB+ [展示逻辑电路图]分析得出组合逻辑电路的特点和能解决的两类问题: 二、组合逻辑电路的特点 任一时刻的稳定输出状态,只决定于该时刻输入信号的状态,而与输入信号作用前电路原来所处的状态无关。不具有记忆功能。

三、组合逻辑电路的两类问题: 1.给定的逻辑电路图,分析确定电路能完成的逻辑功能。 →分析电路 2.给定实际的逻辑问题,求出实现其逻辑功能的逻辑电路。→设计电路 14.1.1 组合逻辑电路的分析方法 一、 分析的目的:根据给定的逻辑电路图,经过分析确定电路能完成的逻辑功能。 二、 分析的一般步骤: 1. 根据给定的组合逻辑电路,逐级写出逻辑函数表达式; 2. 化简得到最简表达式; 3. 列出电路的真值表; 4. 确定电路能完成的逻辑功能。 口诀: 逐级写出表达式, 化简得到与或式。 真值表真直观, 分析功能作用大。 三、 组合逻辑电路分析举例 例1:分析下列逻辑电路。 解: (1)逐级写出表达式: Y 1=B A , Y 2=BC , Y 3=21Y Y A =BC B A A ??,Y 4=BC , F=43Y Y =BC BC B A A ??? (2)化简得到最简与或式: F=BC BC B A A ???=BC BC B A A +??=BC C B B A A +++))(( =BC C B A B A BC C B B A +??+?=++?)(=BC B A BC C B A +?=++?)1( (3)列真值表: A B C F 0 0 0 1 0 0 1 1 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 (4)叙述逻辑功能: 当 A = B = 0 时,F = 1 当 B = C = 1 时,F = 1 组合逻辑电路 表达式 化简 真值表 简述逻辑功能

数电填空题知识点总结

1、逻辑代数有与、或和非三种基本运算。 2、四个逻辑相邻的最小项合并,可以消去__2________个因子;__2n _______个逻辑相邻的最小项合并,可以消去n个因子。 3、逻辑代数的三条重要规则是指反演规则、代入规则和对偶规则。 4、 n个变量的全部最小项相或值为 1 。 6、在真值表、表达式和逻辑图三种表示方法中,形式唯一的是真值表。 8、真值表是一种以表格描述逻辑函数的方法。 AB相邻的最小项有 AB’C’, ABC , 9、与最小项C A’BC’。 10、一个逻辑函数,如果有n个变量,则有 2n个最小项。 11、 n个变量的卡诺图是由 2n个小方格构成的。 13、描述逻辑函数常有的方法是真值表、逻辑函数式和逻辑图三种。 14、相同变量构成的两个不同最小项相与结果为 0 。 15、任意一个最小项,其相应变量有且只有一种取值使这个最小项的值为1 。 1.在数字电路中,三极管主要工作在和两种稳定状态。 饱和、截止 2.二极管电路中,电平接近于零时称为,电平接近于VCC是称为。 低电平、高电平 3.TTL集成电路中,多发射极晶体管完成逻辑功能。 与运算 4.TTL与非门输出高电平的典型值为,输出低电平的典型值为。 、 5.与一般门电路相比,三态门电路中除了数据的输入输出端外,还增加了一个片选信号端,这个对芯片具有控制作用的端也常称为。 使能端 6.或非门电路输入都为逻辑1时,输出为逻辑。 7.电路如图所示,其输出端F的逻辑状态为。 1 8.与门的多余输出端可,或门的多余输出端可。 与有用输入端并联或接高电平、与有用输入端并联或接低电平 10.正逻辑的或非门电路等效于负逻辑的与非门电路。 与非门 11.三态门主要用于总线传输,既可用于单向传输,也可用于双向传

数字电子技术第三章(组合逻辑电路)作业及答案

数字电子技术第三章(组合逻辑电路)作业及答案 -标准化文件发布号:(9456-EUATWK-MWUB-WUNN-INNUL-DDQTY-KII

第三章(组合逻辑电路)作业及答案 1、写出图3-1所示组合逻辑电路中输入输出的逻辑关系式和真值表。 图3-1:组合逻辑电路逻辑图 解:(1)C A A AC B A Y +=++=1 (2)D B C B A CD B A CD B A D BD CD A B A Y ++=++=+=++=)( 2 2、试分析图3-2所示组合逻辑电路,写出其逻辑函数表达式。若设S 1﹑S 0为功能控制信号,A ﹑B 为输入信号,L 为输出,说明当S 1﹑S 0取不同信号值时,电路所实现的逻辑功能。 图3-2:组合逻辑电路逻辑图 3、试用与门、或门和非门,或者与门、或门和非门的组合来实现如下各逻辑函数关系,画出相应的逻辑电路图。 (1)1 Y AB BC =+ A B S 1 S 0 =1 =1 & =1

(2)2Y A C B =+() (3)3Y ABC B EF G =++() & & 1 ≥Y1. 1 A B C . & 1 ≥Y2 . 1 A B C & 1 ≥1 ≥& & 1 A B C . E F G .Y3 . . . 4、试用门电路设计4线-2线优先编码器,输入、输出信号都是高电平有效,要求任一按键按下时,G S 为1,否则G S =0;还要求没有按键按下时,E O 信号为1,否则为0。

5、试用逻辑门电路设计一个2选1数据选择器,输入信号为A、B,选择信号为S,输出信号为Y,要求写出真值表、逻辑函数表达式和画出逻辑电路图。 6、某公司3条装配线各需要100kW电力,采用两台发电动机供电,一台100kW,另外一台是200kW,3条装配线不同时开工,试设计一个发电动机控制电路,可以按照需求启动发电动机以达到节电的目的。

第五章组合逻辑电路典型例题分析

第五章 组合逻辑电路典型例题分析 第一部分:例题剖析 例1.求以下电路的输出表达式: 解: 例2.由3线-8线译码器T4138构成的电路如图所示,请写出输出函数式. 解: Y = AC BC ABC = AC +BC + ABC = C(AB) +CAB = C (AB) T4138的功能表 & & Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7 “1” T4138 A B C A 2A 1A 0Ya Yb S 1 S 2 S 30 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1 S 1S 2S 31 0 01 0 01 0 01 0 01 0 01 0 01 0 01 0 0 A 2A 1A 0Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 70 1 1 1 1 1 1 11 0 1 1 1 1 1 11 1 0 1 1 1 1 11 1 1 0 1 1 1 11 1 1 1 0 1 1 11 1 1 1 1 0 1 11 1 1 1 1 1 0 11 1 1 1 1 1 1 0

例3.分析如图电路,写出输出函数Z的表达式。CC4512为八选一数据选择器。 解: 例4.某组合逻辑电路的真值表如下,试用最少数目的反相器和与非门实现电路。(表中未出现的输入变量状态组合可作为约束项) CC4512的功能表 A ? DIS INH 2A 1A 0Y 1 ?0 1 0 0 0 00 00 00 0 0 0 0 00 0 ?????0 0 00 0 10 1 00 1 11 0 0 1 0 11 1 01 1 1 高阻态 0D 0D 1D 2D 3D 4D 5D 6D 7 Z CC4512 A 0A 1A 2 D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 DIS INH D 1 D A B C D Y 0 0 0 0 1 0 0 0 1 00 0 1 0 10 0 1 1 00 1 0 0 0 CD AB 00 01 11 1000 1 0 0 101 0 1 0 1 11 × × × ×10 0 1 × × A B 第一步画卡诺图第三步画逻辑电路图

人教版高中物理选修3-1知识点整理及重点题型梳理] 简单逻辑电路

人教版高中物理选修3-1 知识点梳理 重点题型(常考知识点)巩固练习 简单的逻辑电路 【学习目标】 1.知道数字电路和模拟电路的概念,了解数字电路的优点。 2.知道“与”门、“或”门、“非”门电路的特征,逻辑关系及表示法。 3.初步了解“与”门、“或”门、“非”门电路在实际问题中的应用。 4.初步了解三种门电路的逻辑关系和数字信号和数字电路的含义。 【要点梳理】 要点一、数字信号与模拟信号 1、数字信号 数字信号在变化中只有两个对立的状态:“有”或者“没有”。而模拟信号变化则是连续的。 如图所示分别为几种常见模拟信号和几种常见数字信号: 2、数字信号的处理 处理数字信号的电路叫做数字电路,数字电路主要研究电路的逻辑功能,数字电路中最基本的逻辑电路是门电路。 通常把高电势称为1,低电势称为0。 数字信号的0和1好比是事物的“是”与“非”,而处理数字信号的电路称数字电路,因此,数字电路就有了判别“是”与“非”的逻辑功能。 我们将数字电路中基本单元电路称为逻辑电路,而最基本的逻辑电路是门电路。

那么数字信号的处理模式就是: 数字电路→逻辑电路→门电路 知识点二─、简单的逻辑电路 1、“与”门的逻辑关系,真值表和电路符号 所谓门,就是一种开关,在一定条件下它允许信号通过,如果条件不满足,信号就被阻挡在“门”外。 (1)对“与”门的理解 如果一个事件和几个条件相联系,当这几个条件都满足后,该事件才能发生,这种关系叫“与”逻辑关系,具有这种逻辑关系的电路称为“与”门电路,简称“与”门。 如图所示,如果把开关A闭合作为条件A满足,把开关B闭合作为条件B满足,把电 灯L亮作为结果Y成立,则“与”逻辑关系可以示意为:A Y B ? ? ? ? 。 它们的逻辑关系如下表所示: (2)“与”门的真值表 如把开关接通定义为1,断开定义为0,灯泡亮为1,不亮为0,那么上表的情况可用下表的数学语言来描述,这种表格称为真值表。 “与”门的真值表

第5章 典型组合逻辑电路

I I 4 5 7 I 1 6 2 I I I 0 3 I I I 9 8 I 图 P5.7 图P5.8 第5章 组合逻辑电路应用 习题5 5.1 设计一个10线-4线编码器,输出为8421BCD 码。 5.2 试用2片8线-3线优先编码器74148,设计一个10线-4线优先编码器。连接时允许附加必要的门电路。 5.3 试分析图P5.3所示电路的功能(74148为8线-3线优先编码器)。 5.4 分析图P5.4所示电路的功能。 5.5 用2片3线-8线译码器74138,组成4线-16线译码器。 5.6 某一个8421BCD 码七段荧光数码管译码电路的e 段部分出了故障,为使数码管能正确地显示0~9十种状态,现要求单独设计一个用与非门组成的e 段译码器。已知共阳极数码管如图P5.6所示。 5.7 分析图P5.7所示电路的功能(74148为8线-3线优先编码器)。 5.8 画出用两片4线-16线译码器74154组成5线-32译码器的接线图。图P5.8是74154的符号,S A 和S B 是两个控制端(亦称片选端),译码器工作时应使S A 和S B 同时为低电平,当输入信号A 3A 2A 1A 0为0000到1111共16种状态时,输出端从Y 0到Y 15依次给出低电平输出信号。 图P5. 4 图P5.6 图P5.3

5.9 设计一个编码转换器,将三位2进制码转换为循环码。 5.10 某医院的某层有6个病房和一个大夫值班室,每个病房有一个按扭,在大夫值班室有一个优先编码器电路,该电路可以用数码管显示病房的编码。各个房间按病人病情严重程度不同分类,1号房间病人病情最重,病情按房间号依次降低,6号房间病情最轻。试设计一个呼叫装置,该装置按病人的病情严重程度呼叫大夫,若两个或两个以上的病人同时呼叫大夫,则只显示病情最重病人的呼叫。 5.11 设计一个电话机信号控制电路。电路有I 0(火警)、I 1(盗警)和I 2(日常业务)三种输入信号,通过排队电路分别从Y 0、Y 1、Y 2输出,在同一时间只能有一个信号通过。如果同时有两个以上信号出现时,应首先接通火警信号,其次为盗警信号,最后是日常业务信号。试按照上述轻重缓急设计该信号控制电路。要求用集成门电路7400(每片含4个2输入端与非门)实现。 5.12 试用一片3线-8线译码器T3138,实现下列逻辑函数(可使用必要的门电路): (1)B A L =1 (2)B A AB L +=2 (3)C B A L ⊕⊕=3 5.13 用4路数据选择器实现下列函数: (1) ∑=)5,4,2,0(),,(1m C B A L (2) ∑= )7,5,3,1(),,(2m C B A L (3)∑=)7,5,2,0(),,(3m C B A L (4)∏= )3,2,0(),,(4M C B A L 5.14 用8路数据选择器实现下列函数: (1) ∑=)15,13,10,8,7,5,2,0(),,,(1m D C B A L (2) ∑= )12,10,9,5,4,3,0(),,,(2m D C B A L (3) C B AB C B A L +=),,(3 5.15 将四选一数据选择器,扩展为16选一数据选择器。 5.16 用3线-8线译码器74138和8选1数据选择器74151和少量与非门实现组合逻辑电路。当控制变量C 2C 1C 0=000时,F=0;C 2C 1C 0=001时,F=ABC ;C 2C 1C 0=010时,F=A+B+C ;C 2C 1C 0=011时,F=ABC ;C 2C 1C 0=100时,F=C B A ++;C 2C 1C 0=101时,F=C B A ⊕⊕;C 2C 1C 0=110时,F=AB+AC+BC ;C 2C 1C 0=111时,F=1。画出电路图。 5.17 分析图P5.17所示电路的工作原理,说明电路的功能。

组合逻辑电路的设计

组合逻辑电路的设计 一.实验目的 1、加深理解组合逻辑电路的工作原理。 2、掌握组合逻辑电路的设计方法。 3、掌握组合逻辑电路的功能测试方法。二.实验器材 实验室提供的芯片:74LS00与非门、74LS86异或门,74LS54与或非门,实验室提供的实验箱。 三.实验任务及要求 1、设计要求 (1)用与非门和与或非门或者异或门设计一个半加器。 (2)用与非门和与或非门或者异或门设计一个四位奇偶位判断电路。 2、实验内容 (1)测试所用芯片的逻辑功能。 (2)组装所设计的组合逻辑电路,并验证其功能是否正确。 三.实验原理及说明 1、简述组合逻辑电路的设计方法。 (1) 分析实际情况是否能用逻辑变量来表示。 (2) 确定输入、输出逻辑变量并用逻辑变量字母表示,作出逻辑规定。 (3) 根据实际情况列出逻辑真值表。 (4) 根据逻辑真值表写出逻辑表达式并化简。 (5) 画出逻辑电路图,并标明使用的集成电路和相应的引脚。 (6) 根据逻辑电路图焊接电路,调试并进一步验证逻辑关系是否与实际情况相符。2、写出实验电路的设计过程,并画出设计电路图。 (1) 半加器的设计如果不考虑有来自低位的进位将两个1 位二进制数相加。 A、B是两个加数,S是相加的和,CC是向高位的进位。 逻辑表达式 S=AB+AB=A? B CC=AB (2) 设计一个四位奇偶位判断电路。当四位数中有奇数个1 时输出结果为1;否则为0。 A, B, C, D分别为校验器的四个输入端,丫时校验器的输出端

逻辑表达式 Y=ABC'D'+A'BCD'+A'B'CD 'A'B'C'D+ABCD+A 'D+AB '+ABCD =(A ? B) ? (C ? D) 四?实验结果 1、列出所设计电路的MULTISM 仿真分析结果。 (1)半加器的设计,1-A 被加数,2-B 加数,XMMI (和数S )XMM (进位数CO A B S CO 0 0 0 0 0 1 1 0 1 0 1 0 1 1 1 A B c D 输出Y 0 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 ;: r P1A… : ; — Vi.c 一隔 .... 74LSM0 (2)设计一个四位奇偶位判断电路 VCC 二 UJU. iEX - 74 L SOOD

数字电路组合逻辑电路设计实验报告

数字电路组合逻辑电路设 计实验报告 The Standardization Office was revised on the afternoon of December 13, 2020

实验三组合逻辑电路设计(含门电路功能测试)

一、实验目的 1.掌握常用门电路的逻辑功能 2.掌握小规模集成电路设计组合逻辑电路的方法 3.掌握组合逻辑电路的功能测试方法 二、实验设备与器材 Multisim 、74LS00 四输入2与非门、示波器、导线 三、实验原理 TTL集成逻辑电路种类繁多,使用时应对选用的器件做简单逻辑功能检查,保证实验的顺利进行。 测试门电路逻辑功能有静态测试和动态测试两种方法。静态测试时,门电路输入端加固定的高(H)、低电平,用示波器、万用表、或发光二极管(LED)测

出门电路的输出响应。动态测试时,门电路的输入端加脉冲信号,用示波器观测输入波形与输出波形的同步关系。 下面以74LS00为例,简述集成逻辑门功能测试的方法。74LS00为四输入2与非门,电路图如3-1所示。74LS00是将四个二输入与非门封装在一个集成电路芯片中,共有14条外引线。使用时必须保证在第14脚上加+5V电压,第7脚与底线接好。 整个测试过程包括静态、动态和主要参数测试三部分。 表3-1 74LS00与非门真值表 1.门电路的静态逻辑功能测试 静态逻辑功能测试用来检查门电路的真值表,确认门电路的逻辑功能正确与否。实验时,可将74LS00中的一个与非门的输入端A、B分别作为输入逻辑变量,加高、低电平,观测输出电平是否符合74LS00的真值表(表3-1)描述功能。

11简单的逻辑电路练习

11简单的逻辑电路 知识点一逻辑电路的符号及真值表 1.(多选)在基本逻辑电路中,当所有输入均为0时,输出不是1的逻辑电路是() A.“与”门电路 B.“或”门电路 C.“非”门电路 D.以上三项都不可能 2.关于图L2-11-1中门电路的符号,下列说法中正确的是() 图L2-11-1 A.甲为“非”门、乙为“与”门、丙为“或”门 B.甲为“与”门、乙为“或”门、丙为“非”门 C.甲为“非”门、乙为“或”门、丙为“与”门 D.甲为“或”门、乙为“与”门、丙为“非”门 3.下表是某逻辑电路的真值表, 图L2-11-2 4.如图L2-11-3所示,甲、乙两图所表示的逻辑关系分别对应图丙和丁中的、. 图L2-11-3 知识点二逻辑电路的应用 5.为了保障行驶安全,一种新型双门电动公交车安装了如下控制装置:

只要有一扇门没有关紧,公交车就不能启动.如果规定:车门关紧时为“1”,未关紧时为“0”;当输出信号为“1”时,公交车可以正常启动行驶,当输出信号为“0”时,公交车不能启动.能正确表示该控制装置工作原理的逻辑门是() A.“与”门 B.“或”门 C.“非”门 D.“与非”门 6.(多选)两个人负责安装一个炸药包,然后启爆,两个人分别控制两个相串联的开关.只有当两个人都撤出危险区,在安全区把开关接通时,炸药包才能爆炸.如果有一个人未撤出危险区,开关没有接通,炸药包就不能启爆,这就是“与”的概念.如果用“0”表示不启爆,“1”表示启爆,用符号“×”表示“与”的运算符号,则下列运算式正确的是() A.0×0=0,表示二人都不启爆,炸药包不爆炸 B.0×1=1,表示一人不启爆,另一人启爆,炸药包爆炸 C.1×0=1,表示一人启爆,另一人不启爆,炸药包爆炸 D.1×1=1,表示二人都启爆,炸药包爆炸 7.两只晶体二极管组成如图L2-11-4所示电路,A、B为输入端,Y为输出端,当A或B接高电势时,Y端电势为正,那么该电路是门电路. 图L2-11-4 8.如图L2-11-5所示的由基本门电路组成的电路中,能使蜂鸣器发出声音的是() 图L2-11-5 9.(多选)“或”门电路的逻辑关系可表示为A+B=Z,则下列结果正确的是() A.0+0=1 B.0+1=1 C.1+0=1 D.1+1=0 10.在集成电路中,经常用若干基本门电路组成复合门电路.图L2-11-6为两个基本门电路组合的逻辑电路,根据真值表,对虚线框内门电路类型及真值表内x值的判断正确的是 () 图L2-11-6

数字电子技术第四章组合逻辑电路

第四章组合逻辑电路 4.1概述 1、数字电路种类:逻辑电路根据输岀信号对输入信号响应的不同分为两类:一类是组合逻辑电路,简称组合电路;另一类是时序逻辑电路,简称时序电路。 2、组合逻辑电路定义:某一时刻电路的输出状态仅由该时刻电路的输入信号决定,而与该电路在此输入信号之前所具有的状态无关。从电路结构上来看,组合逻辑电路的输出端和输入端之间没有反馈回路。 3、电路结构框图 组合电路的一般电路结构如右图所示。可用如下表达式裏示: X n-P X n) 点. | i 1)电路由逻辑门构成,不含记忆元件. 2)输出卷反馈到输入的回路(不含反馈元 件)所以输出与电路原来状态无关时序电路(以 后祥细讨论)某一时刻电路的输岀状态不仅取决 于该时刻电路的输入信号,还与该电路在此输入 信号之前所具有的状态有关。组逻电合辑路 X千― n-1 X n 组合电路有两类问题:7?给定电路,分析其功能。

4.2组合逻辑电路的分析方法与设计方法 421组合电路的分析方法 一、分析步骤: 1、由已知的逻辑图,写出相应的逻辑函数式; 2、对函数式进行化简; 3、根据化简后的函数式列真值表; 4、找出其逻辑功能; 5、评价与改进。(评价给定的逻辑电路是否经济、合理。)设计步骤用框图表示如下:

A?B (A^)C i+AB C (A^B)C f +AB = (A^B)C i +AB 一位二进制加法器。 A 为被加数, B 为加数, C,为低位的进位数。 S 为本位之和, C 。是本位向高位的进 位数。 ? 真值表 A^B 0 0 7 0 1 1 0 0 0 0 0 0 0 0 1 0 0 1 0 1 s (A?B)C Z 0 0 1 0 1 0 0 1 1 0 0 1 0 1 A?B?C. AB T" 0 0 0 0 0 0 0 0 1 0 1 Co P 0 0

数电知识点总结(整理版)

数电复习知识点 第一章 1、了解任意进制数的一般表达式、2-8-10-16进制数之间的相互转换; 2、了解码制相关的基本概念和常用二进制编码(8421BCD、格雷码等); 第三章 1、掌握与、或、非逻辑运算和常用组合逻辑运算(与非、或非、与或非、异或、同或)及其逻辑符号; 2、掌握逻辑问题的描述、逻辑函数及其表达方式、真值表的建立; 3、掌握逻辑代数的基本定律、基本公式、基本规则(对偶、反演等); 4、掌握逻辑函数的常用化简法(代数法和卡诺图法); 5、掌握最小项的定义以及逻辑函数的最小项表达式;掌握无关项的表示方法和化简原则; 6、掌握逻辑表达式的转换方法(与或式、与非-与非式、与或非式的转换); 第四章 1、了解包括MOS在内的半导体元件的开关特性; 2、掌握TTL门电路和MOS门电路的逻辑关系的简单分析; 3、了解拉电流负载、灌电流负载的概念、噪声容限的概念; 4、掌握OD门、OC门及其逻辑符号、使用方法; 5、掌握三态门及其逻辑符号、使用方法; 6、掌握CMOS传输门及其逻辑符号、使用方法; 7、了解正逻辑与负逻辑的定义及其对应关系; 8、掌握TTL与CMOS门电路的输入特性(输入端接高阻、接低阻、悬空等); 第五章 1、掌握组合逻辑电路的分析与设计方法; 2、掌握产生竞争与冒险的原因、检查方法及常用消除方法; 3、掌握常用的组合逻辑集成器件(编码器、译码器、数据选择器); 4、掌握用集成译码器实现逻辑函数的方法; 5、掌握用2n选一数据选择器实现n或者n+1个变量的逻辑函数的方法; 第六章 1、掌握各种触发器(RS、D、JK、T、T’)的功能、特性方程及其常用表达方式(状态转换表、状态转换图、波形图等); 2、了解各种RS触发器的约束条件; 3、掌握异步清零端Rd和异步置位端Sd的用法; 2、了解不同功能触发器之间的相互转换; 第七章 1、了解时序逻辑电路的特点和分类; 2、掌握时序逻辑电路的描述方法(状态转移表、状态转移图、波形图、驱动方程、状态方程、输出方程); 3、掌握同步时序逻辑电路的分析与设计方法,掌握原始状态转移图的化简;

组合逻辑电路习题解答

( 有些题答案错了 )自我检测题 1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。 2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。 3.8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为 2Y 1Y 0Y 。输入输出均为低电平有效。当输入7I 6I 5I …0I 为时,输出2Y 1Y 0Y 为 010 。 4.3线—8线译码器74HC138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 。 5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。 6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。 7.一位数值比较器,输入信号为两个要比较的一位二进制数,用A 、B 表示,输出信号为比较结果:Y (A >B ) 、Y (A =B )和Y (A <B ),则Y (A >B )的逻辑表达式为B A 。 8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。 9.多位加法器采用超前进位的目的是简化电路结构 × 。 (√,× ) 10.组合逻辑电路中的冒险是由于 引起的。 A .电路未达到最简 B .电路有多个输出 C .电路中的时延 D .逻辑门类型不同 11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的 A .在输出级加正取样脉冲 B .在输入级加正取样脉冲 C .在输出级加负取样脉冲 D .在输入级加负取样脉冲

12.当二输入与非门输入为 变化时,输出可能有竞争冒险。 A .01→10 B .00→10 C .10→11 D .11→01 13.译码器74HC138的使能端321 E E E 取值为 时,处于允许译码状态。 A .011 B .100 C .101 D .010 14.数据分配器和 有着相同的基本电路结构形式。 A .加法器 B .编码器 C .数据选择器 D .译码器 15.在二进制译码器中,若输入有4位代码,则输出有 个信号。 A .2 B .4 C .8 D .16 16.比较两位二进制数A=A 1A 0和B=B 1B 0,当A >B 时输出F =1,则F 表达式是 。 A . B A F = B .0101B B A A F ++= .0011B A B A F ++= 17.集成4位数值比较器74LS85级联输入I A <B 、I A=B 、I A >B 分别接001,当输入二个相等的4位数据时,输出F A <B 、F A=B 、F A >B 分别为 。 A .010 B .001 C .100 D .011 18.实现两个四位二进制数相乘的组合电路,应有 个输出函数。 A . 8 B .9 C .10 D .11 19.设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要 个异或门。 A .2 B .3 C .4 D .5 20.在图中,能实现函数C B B A F +=的电路为 。 (a ) (b ) (c ) 图 A .电路 (a ) B .电路(b ) C .电路(c ) D .都不是 习 题 1.分析图所示组合逻辑电路的功能,要求写出与-或逻辑表达式,列出其真值表,并说明电路的逻辑功能。 图 解: CO =AB +BC +AC AC BC AB C B A ABC CO C B A ABC S +++++=+++=)()(

数字电路组合逻辑电路设计实验报告

实验三组合逻辑电路设计(含门电路功能测试)

一、实验目的 1.掌握常用门电路的逻辑功能 2.掌握小规模集成电路设计组合逻辑电路的方法 3.掌握组合逻辑电路的功能测试方法 二、实验设备与器材 Multisim 、74LS00 四输入2与非门、示波器、导线 三、实验原理 TTL集成逻辑电路种类繁多,使用时应对选用的器件做简单逻辑功能检查,保证实验的顺利进行。 测试门电路逻辑功能有静态测试和动态测试两种方法。静态测试时,门电路输入端加固定的高(H)、低电平,用示波器、万用表、或发光二极管(LED)测出门电路的输出响应。动

态测试时,门电路的输入端加脉冲信号,用示波器观测输入波形与输出波形的同步关系。 下面以74LS00为例,简述集成逻辑门功能测试的方法。74LS00为四输入2与非门,电路图如3-1所示。74LS00是将四个二输入与非门封装在一个集成电路芯片中,共有14条外引线。使用时必须保证在第14脚上加+5V电压,第7脚与底线接好。 整个测试过程包括静态、动态和主要参数测试三部分。 表3-1 74LS00与非门真值表 1.门电路的静态逻辑功能测试 静态逻辑功能测试用来检查门电路的真值表,确认门电路的逻辑功能正确与否。实验时,可将74LS00中的一个与非门的输入端A、B分别作为输入逻辑变量,加高、低电平,观测输出电平是否符合74LS00的真值表(表3-1)描述功能。 测试电路如图3-2所示。试验中A、B输入高、低电平,由数字电路实验箱中逻辑电平产生电路产生,输入F可直接插至逻辑电平只是电路的某一路进行显示。

仿真示意 2.门电路的动态逻辑功能测试 动态测试用于数字系统运行中逻辑功能的检查,测试时,电路输入串行数字信号,用示波器比较输入与输出信号波形,以此来确定电路的功能。实验时,与非门输入端A加一频率为

组合逻辑电路的分析

一.目的 由逻辑图得出逻辑功能 二.方法(步骤) 1.列逻辑式: 由逻辑电路图列输出端逻辑表达式; (由输入至输出逐级列出) 2.化简逻辑式: 代数法、卡诺图法; (卡诺图化简步骤保留) 3.列真值表: 根据化简以后的逻辑表达式列出真值表;4.分析逻辑功能(功能说明): 分析该电路所具有的逻辑功能。 (输出与输入之间的逻辑关系); (因果关系) (描述函数为1时变量取值组合的规律) 技巧:先用文字描述真值表的规律(即叙述函数值为1时变量组合所有的取值),然后总结归纳电路实现的具体功能。 5.评价电路性能。 三.思路总结:

四.注意: 关键:列逻辑表达式; 难点:逻辑功能说明 1、逻辑功能不好归纳时,用文字描述真值表的规律。(描述函数值为1时变量组合所有的取值)。 2、常用的组合逻辑电路。 (1)判奇(偶)电路; (2)一致性(不一致性)判别电路; (3)相等(不等)判别电路; (4)信号有无判别电路; (5)加法器(全加器、半加器); (6)编码器、优先编码器; (7)译码器; (8)数值比较器; (9)数据选择器; (10)数据分配器。 3、多输出组合逻辑电路判别: 1)2个输出时考虑加法器:2输入半加;3输入全加。 2)4输出时考虑编码器:4输入码型变换;编码器。

五.组合逻辑电路分析实例 例1 电路如图所示,分析电路的逻辑功能。 A B Y 解: (1)写出输出端的逻辑表达式:为了便于分析可将电路自左至右分三级逐级写出Z 1、Z 2、Z 3和Y 的逻辑表达式为: 321 3121Z Z Y BZ Z AZ Z AB Z ==== (2)化简与变换:将Z 1、Z 2、和Z 3代入到公式Y 中进行公式化简得: B A B A BZ AZ BZ AZ Z Z Z Z Y +=+=+=+==11113232 (3)列出真值表:根据化简以后的逻辑表达式列出真值表如表所示。

数电练习_组合逻辑电路知识分享

数电练习2013_组合 逻辑电路

一、填空题 1.分析组合逻辑电路的步骤为:(1);(2); (3); (4)根据真值表和逻辑表达对逻辑电路进行分析,最后确定其功能。 2.在逻辑电路中,任意时刻的输出状态仅取决于该时刻输入信号的状态,而与信号作用前电路的状态无关,这种电路称为。因此,在电路结构上一般由组合而成。 3.十六进制数(F6.A)的等值八进制数是(),等值二进制数是 (),十进制数(56)的8421BCD编码是(),等值二进制数是()。 4. 实现两个一位二进制数相加,产生一位和值及一位进位值,但不考虑低位来的进位位的加法器称为________;将低位来的进位位与两个一位二进制数一起相加,产生一位和值及一位向高位进位的加法器称为________。 5.在下图所示的 卡诺图中,函数 F至少用个 与非门实现。设 输入原、反变量都提供。

6. 已知某组合电路的输入A、B、C、D及输出F的波形如图所示,则F对A、 B、C、D的最简与或表达式为F=。 参考答案: 1. (1)由逻辑图写出个输出端逻辑表达式;(2)化简和变换各逻辑表达式;(3)列出真值表 2. 组合逻辑电路门电路 3. 366.5 / 11110110.1010 / 01010110 / 111000 4. 半加器全加器 5. 3个 6.C B + C A+ D C 二、选择题 1.图(a)-(c)的三幅波形图中,正确表达了脉冲信号的宽度是() 2. 下列逻辑代数运算错误的是()

A. A 00=? B. A +1=A C. A A =?1 D. A +0=A 3.下列函数中等于A 的是( ) A. A +1 B. A A + C. AB A + D. A (A +B ) 4. 由开关组成的逻辑电路如图所示,设开关接通为“1”,断开为“0”,电灯亮为“1”,电灯L 暗为“0”,则该电路为( ) A. “与”门 B. “或”门 C. “非”门 D. 以上各项都不是 5.若把某一全加器的进位输出接至另一全加器的进位输入,则可构成( ) A. 二位并行进位的全加器 B. 二位串行进位的全加器 C. 一位串行进位的全加器 D. 以上各项都不是 6. 逻辑电路的真值表如下所示,由此可写出其逻辑函数表达式为( )。 A. C AB C B A C B A F ++= B. C B B A F += C. C B C B A F += D. AC B F += A B C F A B C F 0 1 1 1

第六篇几种常用的组合逻辑电路

第六章几种常用的组合逻辑电路 一、填空题 1、(8-1易)组合逻辑电路的特点是:电路在任一时刻输出信号稳态值由决定(a、该时刻电路输入信号;b、信号输入前电路原状态),与无关(a、该时刻电路输入信号;b、信号输入前电路原状态),属于(a、有;b、非)记忆逻辑电路。 2、(8-2易)在数字系统中,将具有某些信息的符号变换成若干位进制代码表示,并赋予每一组代码特定的含义,这个过程叫做,能实现这种 功能的电路称为编码器。一般编码器有n个输入端,m个输出端,若输入低电平有效,则在任意时刻,只有个输入端为0,个输入端为1。对于优先编码器,当输入有多个低电平时,则。 3、(8-3易,中)译码是的逆过程,它将转换成。译码器有多个输入和多个输出端,每输入一组二进制代码,只有个输出端有效。n 个输入端最多可有个输出端。 4、(8-2易)74LS148是一个典型的优先编码器,该电路有个输入端和个输出端,因此,又称为优先编码器。 5、(8-4中)使用共阴接法的LED数码管时,“共”端应接,a~g应接输出有效的显示译码器;使用共阳接法的LED数码管时,“共”端应接,a~g应接输出有效的显示译码器,这样才能显示0~9十个数字。 6、(8-4中)译码显示电路由显示译码器、和组成。 7.(8-4易)译码器分成___________和___________两大类。 8.(8-4中)常用数字显示器有_________,_________________,____________等。 9.(8-4中)荧光数码管工作电压_______,驱动电流______,体积_____,字形清晰美观,稳定可靠,但电源功率消耗______,且机械强度_____。 10.(8-4中)辉光数码管管内充满了_________,当它们被______时,管子就发出辉光。 11.(8-4易)半导体发光二极管数码管(LED)可分成_______,_______两种接法。 12.(8-4中)发光二极管正向工作电压一般为__________。为了防止二极管过电流而损坏,使用时在每个二极管支路中应______________。 13.(8-3中)单片机系统中,片内存储容量不足需要外接存储器芯片时,可用_________作高位地址码。 14.(8-3中)数字系统中要求有一个输入端,多个数据输出端,可用_________输入端作为

数字电子技术第4章_组合逻辑电路习题解答

习题 4.1写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。 习题4.1图 解:B A B A B A B A B A F ⊕=+=+= 该电路实现异或门的功能 4.2分析图所示电路,写出输出函数F 。 习题4.2图 解:[]B A B B B A F ⊕=⊕⊕⊕=)( 4.3已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟. 图 解:B A B A B A AB B AB A AB B AB A F ⊕=?=???=???= 4.4由与非门构成的某表决电路如图所示。其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。 (1) 试分析电路,说明决议通过的情况有几种。 (2) 分析A 、B 、C 、D 四个人中,谁的权利最大。 解:(1)ABD BC CD ABD BC CD L ++=??= (2) L B A =1 =1 =1 F F B A

(3)根据真值表可知,四个人当中C 的权利最大。 4.5分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。 习题4.5图 解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕?⊕= (2) 4.6试分析图所示电路的逻辑功能。 习题4.6图 解:(1)ABC C B A F )(++= 10

(2) 电路逻辑功能为:“判输入ABC 是否相同”电路。 4.7已知某组合电路的输入A 、B 、C 和输出F 的波形如下图所示,试写出F 的最简与或表达式。 习题4.7图 解:(1)根据波形图得到真值表: C AB BC A C B A F ++= 4.8、设∑=)14,12,10,9,8,4,2(),,,(m D C B A F ,要求用最简单的方法,实现的电路最简 单。 1)用与非门实现。 2)用或非门实现。 3) 用与或非门实现。 F C B A

组合逻辑电路

第五章组合逻辑电路 内容提要 【熟悉】组合逻辑电路的特点(功能、结构) 【掌握】组合逻辑电路的一般分析方法和设计方法 【熟悉】常见的五种组合逻辑电路 【掌握】中规模集成组合逻辑电路的应用(扩展与实现组合逻辑函数) 【了解】组合逻辑电路中的竞争和险象 一.一.网上导学 二.二.本章小结 三.三.典型例题 四.四.习题答案 网上导学 一. 一.组合逻辑电路的特点:p123 功能:输出仅取决于该时刻的输入而与电路原状态无关(无记忆功能); 结构(无记忆元件,无反馈环路). 二. 二.组合逻辑电路的一般分析方法(组合逻辑电路图→求解逻 辑功能): 组合逻辑电路图→列出逻辑函数表达式(迭代法,由输入逐级向后推) →求标准表达式或简化的表达式(转换或化简) →列出相应的真 值表→判断电路功能。例5.2.1(异或门) P124 分析图5.3.3逻辑电路

1.1.迭代法求输出逻辑表达式,如图: 图中,C=B A ,D=AB,用迭代法求出电路输出逻辑表达式 F= 2.列出真值表(表5.2.1, P125) 分析真值表可知该电路是一个异或门 例2. 试分析下面电路 1.由上图可知E=AB,D=AC,G=BC,迭代法得F=E+D+G=AB+AC+BC 2. 列出相应的真值表

由真值表可以看出,该逻辑电路是一个三人多数表决电路。 三. 三. 组合逻辑电路的一般设计方法: 根据设计要求(要实现的逻辑功能)→画出逻辑电路图. 设计要求→列出真值表(确定输入、输出变量及它们的逻辑关系) →化简写出简化的逻辑表达式(→或转换成逻辑器件所需的表达形式)→画出逻辑图。 例5.3.1(多数表决器) P125。 举例:设计一个一位加法器(半加器)电路. 1. 1. 该电路有两个输入An 、Bn 和二个输出Sn 和Cn, An Bn Sn Cn 0 0 0 0 0 1 1 0 1 0 1 0 1 1 1 Sn=Bn An Bn An Bn An ⊕=+,Cn=An*Bn 3. 3. 画出逻辑图 四.组合逻辑电路中的竞争和险象:P126~P129