实验四存储器EM实验

实验六程序存储器EM读写操作实验

实验六程序存储器EM读写操作实验【实验要求】利用CP226 实验箱上的K16…K23 开关做为DBUS数据的输入端,其它开关做为控制信号的输入端,实现程序存储器EM 的读写操作。

【实验目的】掌握模型机中程序存储器EM 的引脚结构、工作原理及控制方法。

【主要集成电路芯片及其逻辑功能】本实验所涉及的主要集成电路芯片为HM6116,用于存放程序和数据。

HM6116是一种2K ×8位的高速低耗静态CMOS随机存取存储器芯片,芯片包含11条地址线(A0~A10)、8条数据线(I/O1~I/O8)、1条电源线、1条接地线GND和3条控制线--片选信号CE(E)、写允许信号WE(W)和输出允许信号OE(G)(控制信号均为低电平有效)。

HM6116引脚结构如下图所示,其读写操作逻辑如下表所示。

【实验涉及的逻辑电路及原理】程序存储器EM 由一片HM6116构成,通过一片74HC245与数据总线DBUS相连,存储器EM的地址可选择由PC或MAR 提供。

存储器EM读写操作实验原理逻辑电路如下图所示,其中EMRD、EMWR、EMEN分别为存储器读、存储器写、存储器连通控制信号,ICOE为中断信号,CK为脉冲信号。

存储器EM 的数据输出直接接到指令(控制)总线IBUS,指令总线IBUS 的数据还可以来自一片74HC245。

当ICOE 为0 时,这片74HC245 输出中断指令B8。

程序存储器EM读写操作实验原理逻辑电路【实验内容及步骤】(1)实验连接线实验具体连接线如下表所示。

存储器EM读写实验连接线连接信号孔接入孔作用状态说明1 J2座J3座将K23-K16接入DBUS[7:0] 实验模式:手动2 IREN K6 IR、uPC写允许低电平有效3 PCOE K5 PC输出地址低电平有效4 MAROE K4 MAR输出地址低电平有效5 MAREN K3 MAR写允许低电平有效6 EMEN K2 存储器与数据总线相连低电平有效7 EMRD K1 存储器读允许低电平有效8 EMWR K0 存储器写允许低电平有效9 CK 已连PC工作脉冲上升沿打入10 CK 已连MAR工作脉冲上升沿打入11 CK 已连存储器写脉冲上升沿打入12 CK 已连IR、uPC工作脉冲上升沿打入(2)PC/MAR 输出地址选择二进制开关K5、K4分别用于置控制信号PCOE、MAROE。

实验4:双端口存储器实验 ----独立方式

河北环境工程学院

《计算机组成原理》实验报告

作者:

系(部):

专业班级:

学号:

成绩:__________________

评阅教师:__________________

年月日

一、实验目的

1、了解双端口静态存储器IDT7132的工作特性及其使用方法;

2、了解半导体存储器怎样存储和读取数据;

3、了解双端口存储器怎样并行读写;

4、熟悉LK-TEC-9模型计算机存储器部分的数据通路;

二、预习内容

1.掌握双端口存储器的使用方法

2. 掌握TEC-8模型计算机存储器的部分的数据通路

三、实验环境及主要器件

1.TEC-8实验系统 1台

2. 逻辑测试笔 1支

3. 双踪示波器 1台

4. 逻辑测试笔 1支

四、实验内容

1、从存储器地址10H开始,通过左端口连续向双端口RAM中写入3个数:85H,60H,38H。

在写的过程中,在右端口检测写的数据是否正确。

2、从存储器地址10H开始,连续从双端口RAM的左端口和右端口同时读出存储器的内容。

五、实验步骤

六、实验结果分析与讨论。

计组存储器实验实验报告(3篇)

第1篇一、实验目的1. 理解存储器的基本组成和工作原理;2. 掌握存储器的读写操作过程;3. 熟悉存储器芯片的引脚功能及连接方式;4. 了解存储器与CPU的交互过程。

二、实验环境1. 实验设备:TD-CMA计算机组成原理实验箱、计算机;2. 实验软件:无。

三、实验原理1. 存储器由地址线、数据线、控制线、存储单元等组成;2. 地址线用于指定存储单元的位置,数据线用于传输数据,控制线用于控制读写操作;3. 存储器芯片的引脚功能:地址线、数据线、片选线、读线、写线等;4. 存储器与CPU的交互过程:CPU通过地址线访问存储器,通过控制线控制读写操作,通过数据线进行数据传输。

四、实验内容1. 连线:按照实验原理图连接实验箱中的存储器芯片、地址线、数据线、控制线等;2. 写入操作:将数据从输入单元IN输入到地址寄存器AR中,然后通过控制线将数据写入存储器的指定单元;3. 读取操作:通过地址线指定存储单元,通过控制线读取数据,然后通过数据线将数据输出到输出单元OUT;4. 实验步骤:a. 连接实验一(输入、输出实验)的全部连线;b. 按实验逻辑原理图连接两根信号低电平有效信号线;c. 连接A7-A0 8根地址线;d. 连接13-AR正脉冲有效信号线;e. 在输入数据开关上拨一个地址数据(如00000001,即16进制数01H),拨下开关,把地址数据送总线;f. 拨动一下B-AR开关,实现0-1-0”,产生一个正脉冲,把地址数据送地址寄存器AR保存;g. 在输入数据开关上拨一个实验数据(如10000000,即16进制数80H),拨下控制开关,把实验数据送到总线;h. 拨动控制开关,即实现1-0-1”,产生一个负脉冲,把实验数据存入存储器的01H号单元;i. 按表2-11所示的地址数据和实验数据,重复上述步骤。

五、实验结果与分析1. 通过实验,成功实现了存储器的读写操作;2. 观察到地址线、数据线、控制线在读写操作中的协同作用;3. 理解了存储器芯片的引脚功能及连接方式;4. 掌握了存储器与CPU的交互过程。

CPTH模型机感性认识及模块实验

实验一CPTH模型机感性认识及模块实验感性认识:一计算机组成原理实验课概述二 CPTH硬件系统基本组成三 CPTH软件系统基本组成四 CPTH指令系统五 CPTH实验系统特点模块实验:1. 寄存器实验2. 运算器实验3. 存储器实验一计算机组成原理实验课概述计算机组成原理实验课程,是专门为计算机学院相关专业高年级开设的一门专业骨干课程,它主要研究计算机的基本组成与运行原理,它深入到CPU的内部,查看,测试各主要信号与部件的工作状态,即将CPU解剖开,观察一条指令在执行过程中数据的走向、各控制信号的状态及相关寄存器的值。

而CPTH模型机是专为计算机组成原理实验课设计的,它是一台硬件,软件相对完整,独立的小型计算机系统,即是一台简单的计算机,它包括了一台计算机常有部分CPU,主存,I/O接口等。

二 CPTH硬件系统基本组成运算器:运算器ALU用一片lattice公司的LC4256V-100在线可编程逻辑芯片实现的,出厂时,已下载了用VHDL语言编写的运算功能(8种)。

寄存器:累加器寄存器A、工作寄存器W:(1片74HC574/每);左移门L、直通门D、右移门R:(2片74LS245同相器/每);寄存器组:R0-R3:(2片74HC574/每);地址寄存器MAR、堆栈寄存器ST:(2片74HC574/每);中断向量寄存器IA、输入端口寄存器IN、输出端口寄存器OUT等。

控制器:程序计数器PC、微程序计数器uPC:(2片74LS161四位加1计数器/每);微程序存储器uM:(3片6116),事先存入24位微指令,电路设置为:只能读,不能写;指令寄存器IR:(1片74HC574)、中断控制电路、跳转控制电路等;组合逻辑控制器:用一片lattice公司的LC4256V-100可编程的逻辑芯片实现。

出厂时已下载了用ABEL语言编写的的组合逻辑控制器文件(组合逻辑表达式),实现控制功能。

通过开关KC切换。

存储器:程序存储器EM由一片6116 RAM 构成,是用户存放程序和数据的地方。

存储器实验 总结

存储器实验总结1. 引言存储器在计算机系统中起到了至关重要的作用。

它用于存储和检索数据,是计算机进行信息处理和数据传输的基础。

本文将总结存储器实验的过程、方法和结果,并对实验中遇到的问题以及取得的成果进行分析和评价。

2. 实验过程2.1 实验目标本次实验的目标是通过搭建存储器系统的实验平台,了解存储器的工作原理和性能,并通过实际操作和测试验证相关理论。

2.2 实验步骤1.搭建存储器系统实验平台:根据实验指导书提供的材料和方法,组装并连接存储器系统的硬件设备。

2.熟悉实验设备:了解存储器系统的各个组成部分的功能,学习使用实验设备的操作方法。

3.进行实验操作:按照实验指导书的要求,进行存储器的读写操作、存储器容量和速度的测试等。

4.记录实验数据和结果:准确记录实验过程中的数据和结果,包括读写操作的时间、存储器容量的测量值等。

5.分析实验结果:根据实验数据和结果,分析存储器的性能和工作原理。

2.3 实验设备和环境•操作系统:Windows 10•实验平台:Intel x86 架构的计算机•实验设备:存储器模块、存储器控制器、数据总线、控制总线等•编程工具:C++ 编译器、汇编器等3. 实验结果3.1 存储器的读写操作在实验过程中,我们分别进行了存储器的读操作和写操作,并记录了每次操作的时间。

通过对比不同操作的时间,我们可以评估存储器的读写速度。

实验结果显示,存储器的读操作平均时间为 X 毫秒,写操作平均时间为 Y 毫秒,表明存储器的读写速度较为稳定。

3.2 存储器容量的测量我们还对存储器的容量进行了测试。

实验中,我们分别使用不同大小的数据块对存储器进行写入,然后读取存储器中的数据块,并记录了写入和读取的时间。

通过对比不同数据块的操作时间,我们可以评估存储器的容量。

实验结果显示,存储器的容量为 Z 字节,并且与设备说明书中的容量一致。

3.3 实验中的问题和解决方案在实验过程中,我们也遇到了一些问题,例如实验设备的连接错误、数据传输错误等。

(完整word版)计算机组成原理实验1~4

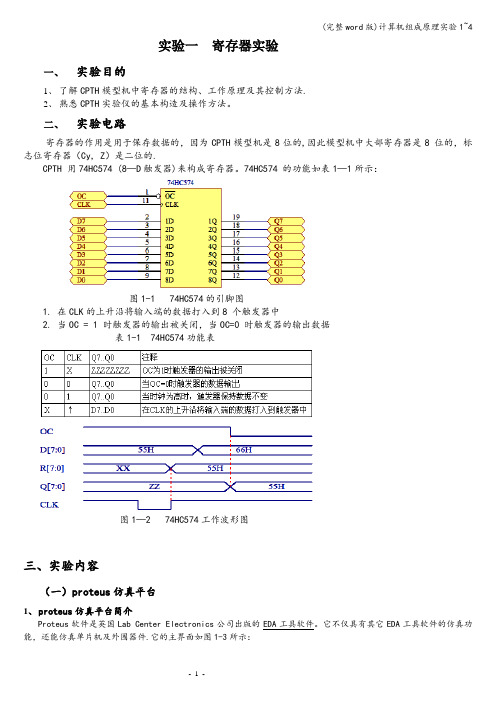

实验一寄存器实验一、实验目的1、了解CPTH模型机中寄存器的结构、工作原理及其控制方法.2、熟悉CPTH实验仪的基本构造及操作方法。

二、实验电路寄存器的作用是用于保存数据的,因为CPTH模型机是8位的,因此模型机中大部寄存器是8 位的,标志位寄存器(Cy, Z)是二位的.CPTH 用74HC574 (8—D触发器)来构成寄存器。

74HC574 的功能如表1—1所示:图1-1 74HC574的引脚图1. 在CLK的上升沿将输入端的数据打入到8 个触发器中2. 当OC = 1 时触发器的输出被关闭,当OC=0 时触发器的输出数据表1-1 74HC574功能表图1—2 74HC574工作波形图三、实验内容(一)proteus仿真平台1、proteus仿真平台简介Proteus软件是英国Lab Center Electronics公司出版的EDA工具软件。

它不仅具有其它EDA工具软件的仿真功能,还能仿真单片机及外围器件.它的主界面如图1-3所示:图1—3 proteus仿真平台主界面2、在proteus平台上运行电路:寄存器_1.DSN。

拨动开关,观察灯的亮灭,回答思考题1。

思考题1:先使OC=1,拨D0~D7=00110011,按下CK提供CLK上升沿;再拨D0~D7=01000100,OC=0,此时Q0~Q7为多少?3、CPTH模型机上,寄存器A的电路组成如图1-4所示。

在proteus平台上运行电路:寄存器_2.DSN,回答思考题2。

图1-4 寄存器A原理图思考题2:数据从D端传送到Q端,相应的控制端如何设置?3、CPTH模型机上,寄存器组R0~R3的电路组成如图1-5所示。

在proteus平台上运行电路:寄存器_3。

DSN,回答思考题3。

图1—5 寄存器组R0~R3 原理图74LS139是2—4线译码器,由A、B两个输入端选择控制4个输出端Y0~Y3,使能端E低电平有效,允许译码输出。

74HC32是或门,两个输入端同时为低电平,输出为低电平.具体的控制方式见表1-2。

存储器实验实验报告

存储器实验实验报告一、实验目的练习使用STEP开关了解地址寄存器(AR)中地址的读入了解STOP和STEP开关的状态设置了解向存储器RAM中存入数据的方法了解从存储器RAM中读出数据的二、实验设备1、TDN-CM+组成原理实验仪一台2、导线若干3、静态存储器:一片6116(2K*8)芯片地址锁存器(74LS273)地址灯AD0-AD7三态门(74LS245)三、实验原理实验所用的半导体静态存储器电路原理如图所示,实验中的静态存储器由一片6116(2K*8)芯片构成,其数据线接至数据总线,地址线由地址锁存器(74LS273)给出。

地址灯AD0-AD7与地址线相连,显示地址线状况。

数据开关经一个三态门(74LS245)连至数据总线,分时给出地址和数据。

实验时将T3脉冲接至实验板上时序电路模块的TS3相应插孔中,在时序电路模块中有两个二进制开关“STOP”和“STEP”,将“STOP”开关置为“RUN”状态、“STEP”开关置为“EXEC”状态时,按动微动开关START,则TS3端输出连续的方波信号当“STOP”开关置为RUN状态,“STEP”开关置为“STEP”状态时,每按动一次微动开关“start”,则TS3输出一个单脉冲,脉冲宽度与连续方式相同。

四、实验内容如下图存储器实验接线图(一)练习使用STEP开关往地址寄存器(AR)中存入地址设置STOP和STEP开关的状态:从数据开关送地址给总线:SW-B=___打开AR,关闭存储器:LDAR=___、CE=___按下Start产生T3脉冲关闭AR,关闭数据开关:LDAR=__、SW-B=__(二)往存储器RAM中存入数据1.设定好要访问的存储器单元地址2.从数据开关送数给总线:SW-B=___3.选择存储器片选信号:CE=___4.选择读或写:WE=____5.按下Start产生T3脉冲6.关闭存储器片选信号:CE=___7.关闭数据开关:SW-B=___(三)从存储器RAM中读出数据1.设定好要访问的存储器单元地址2.选择存储器片选信号:CE=___3.选择读或写:WE=____4.按下Start产生T3脉冲5.关闭存储器片选信号:CE=___五、实验结果总结六、思考题在进行存储器操作(写/读)是不是必须先往地址寄存器(AR)存入所访问的存储器单元地址?T3在本实验中起了哪些作用,如何区分它们?在进行存储器读写操作时,CE和WE信号有没有先后顺序?为什么?。

程序存储器EM的工作原理

程序存储器EM的工作原理程序存储器是计算机中的一种重要组件,用于存储和读取计算机的指令集和程序数据。

其中,电子存储器(EM)是一种常见的程序存储器类型。

其工作原理可以简单描述为电子存储和读出。

EM是一种基于电子技术的存储器,由许多存储单元组成,每个存储单元都可以存储一个比特的信息(0或1)。

这些存储单元通常由电容器或者双稳态器件(比如晶体管)构成。

电容器储存信息的是电荷量,而晶体管主要利用电流状态来表示信息。

在EM中,每个存储单元都有一个唯一的地址,用于访问它的信息。

当计算机需要写入或读取某个存储单元时,它将发送地址信号和数据信号给EM。

地址信号用于选择目标存储单元,而数据信号则携带要写入或读取的信息。

写入数据时,EM会根据地址信号确定要写入数据的存储单元,并将数据信号转换为相应的电荷量或电流状态存储在该存储单元中。

这个过程称为写入操作。

读取数据时,EM会根据地址信号选择要读取的存储单元,并将存储单元中的电荷量或电流状态转化为电压或电流信号,然后送回给计算机。

计算机会将这些信号进行解码,使其能够被处理,从而完成读取操作。

EM还有一些重要的特性和操作。

其中之一是访问速度。

EM的访问速度较快,因为信息可以通过电子信号进行直接存取,而不需要机械动作。

此外,EM的存储容量通常较大,它可以存储大量的信息。

这使得EM成为计算机的主要存储器之一。

然而,EM也有一些局限性。

首先是易失性。

EM的存储单元是通过电路元件存储信息的,一旦断电,存储的信息会丢失。

因此,当计算机断电或重新启动时,必须重新加载所有的程序和数据。

其次是存储器的密度限制,即每个存储单元只能存储一个比特的信息。

为了满足更大容量的存储需求,需要增加存储单元数量,进一步增加设备的体积和成本。

为了克服EM的这些缺点,人们开发了许多其他类型的存储器,比如固态硬盘(SSD)和硬盘驱动器(HDD)。

这些存储器不仅具有非易失性,还有更高的存储密度和更快的访问速度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验四存储器EM实验

实验背景

存储器是计算机的重要组成部分之一,它负责存储计算机处理数据所需要的程序和数据。

在计算机的运作中,存储器起到缓冲、暂存、传递数据的作用。

现实生活中,我们可以将存储器看做是我们大脑的记忆系统,就像我们可以从记忆中取出一些信息一样,计算机可以从存储器中读取程序和数据。

存储器按照物理结构可以分成两种:随机访问存储器(RAM)和只读存储器(ROM)。

RAM是一种易失性存储器,意味着在断电之后,RAM中的数据会被擦除。

ROM是一种非易失性存储器,意味着即使断电,ROM中的数据也会保持不变。

现代计算机一般都使用RAM和ROM的组合来存储程序和数据。

实验原理

本实验选择EEPROM,EEPROM是一种带有“可编程”功能的非易失性存储器,其功能类似于ROM。

EEPROM可以多次擦写和编程,因此比传统ROM更为灵活。

EEPROM通常用于存储设备的参数,而不是存储程序。

EEPROM包含一个晶体管和一个电容器的结构,它的存储通过在电容器中存储的电荷来完成。

EEPROM读取的过程包括两个操作:地址操作和读操作。

首先,将要读取的地址写入EEPROM的地址端口中,然后将读取操作信号写入EEPROM的控制端口,EEPROM会返回与地址相对应的数据。

每个EEPROM芯片都有唯一的地址范围,因此在使用时需注意。

实验器材

1. 单片机:ATmega16

2. EEPROM芯片:AT24C02

3. 电路板

5. 电源

6. 万用表

7. Oscilloscope

实验步骤

1. 在电路板上组装电路

2. 使用编程器对ATmega16进行编程,程序中将ATmega16的端口配置为与EEPROM通信的ISRAB协议。

3. 将ATmega16和EEPROM芯片插入到电路板中。

4. 启动电源,并使用万用表检查电路是否正常。

5. 将示波器连接到ATmega16和EEPROM上,检查ATmega16是否能正常向EEPROM进行读操作。

6. 如果ATmega16能够成功读取EEPROM中的数据,则说明实验成功。

实验结果

本实验使用ATmega16单片机对EEPROM进行读操作,成功地从EEPROM中读取了数据。

在读取数据时,ATmega16将要读取的地址传输到EEPROM,EEPROM返回与地址相对应的数据,在示波器上可以看到读取操作的波形。

这次实验的成功证明了单片机可以与EEPROM芯片进行正常通信,也提供了单片机如何访问EEPROM的参考实例。

结论

参考文献

1.《单片机技术及应用》

2.《单片机和现代进销存软件的开发与应用》

4.《ATmega16的GPIO与外部中断实验设计》

5.《C51单片机仿真实验与原理》。