基于FPGA的PROFIBUS_DP从站链路层控制器IP核的设计

基于FPGA的USB接口IP核设计

基于FPGA的USB接口IP核设计USB(通用串行总线)作为一种外设连接技术,是计算机外设连接技术的重大变革,USB具有速度快、通用性好、扩展性强、功耗低、稳定、易开发等众多优点,在实践中获得了广泛的应用,逐步成为PC机的一种标准接口。

USB接口控制芯片是实现USB设备与主机建立通信所必须的芯片,目前国内的USB开发者所采用的芯片都是由国外的芯片商所提供,如Cypress、NEC、Motorola等大的IC设计公司,价格较贵。

由于USB的广泛应用,国内外众多科研机构和集成电路设计公司都把目光投向USB这项具有广阔市场前景的技术。

USB内核(USB Core)是USB接口控制芯片的关键模块,设计一个稳定、高速的USB内核更是芯片成功推向市场的前提。

1 USB通信原理USB通信逻辑上分成了3层:信号层、协议层和数据层。

信号层用来实现在USB 设备和主机的物理连接之间传输位信息流的信息。

逻辑层用来实现在USB设备和USB主机端的协议软件之间传输包字节流的信息,它们在信号层被编码成NRZI位信息后传送出去。

数据传输层用来实现在USB主机端的客户端驱动程序和设备端的功能接口之间传输有一定意义的信息,这些信息在协议层被打包成包格式。

1.1 传输的基本单元包(Packet)是USB系统中信息传输的基本单元。

结构,如图1所示,根据USB 规范,包的类型有:令牌包、数据包、握手包和专用包。

USB总线操作(通讯过程)都可以归结为3种包的传输:令牌包、数据包和应答包。

任何操作都是从主机开始的,主机以预先排好的时序,发出一个描述操作类型、方向、外设地址以及端点号,称之为令牌包Foken Packet。

然后由在令牌中指定的数据发送者发出一个数据包Data Packet或者报告它没有数据可以传输。

而数据的目的地一般要以一个应答包Handshake Packet做出响应表明传输是否成功。

1.2 事务处理事务处理(Transaction)是指USB总线上数据信息的一次接收或发送的处理过程。

(完整)PROFIBUS网络的DP主站与DP从站

PROFIBUS网络的DP主站与DP从站PROFIBUS网络的硬件由主站、从站、网络部件和网络组态与诊断工具组成。

网络部件包括通信媒体(电缆),总线连接器、中继器、耦合器;以及用于连接串行通信、以太网、AS-i、EIB等网络系统的网络转接器。

PROFIBUS — DP设备可以分为3种不同类型的站。

(1)1类DP主站1类DP主站(DPM1)是系统的中央控制器,DPM1在预定的周期内与DP从站循环地交换信息,并对总线通信进行控制和管理.DPM1可以发送参数给DP从站,读取从站的诊断信息,用全局控制命令将它的运行状态告知给各从站.此外,还可以将控制命令发送给个别从站或从站组,以实现输出数据和输入数据的同步。

下列设备可以作1类DP主站:1)集成了DP接口的plc,例如CPU 315 —2DP、CPU 313C -2DP 等。

2) CPU和支持DP主站功能的通信处理器(CP).3)插有PROFIBUS网卡的PC,例如WinAC控制器.可以用软件功能选择PC作1类主站或是作编程监控的2类主站,可以使用CP 5511、CP 5611和CP 5613等网卡.4)连接工业以太网和PROFIBUS — DP的IE/PB链接器模块。

5) ET 200S/ET 200X的主站模块。

(2)2类DP主站2类DP主站(DPM2)是DP网络中的编程、诊断和管理设备。

PC 和操作员面板/触摸屏( OP/TP)可以作2类主站。

DPM2除了具有1类主站的功能外,在与1类DP主站进行数据通信的同时,可以读取DP从站的输入/输出数据和当前的组态数据,可以给DP从站分配新的总线地址.(3) DP从站DP从站是采集输入信息和发送输出信息的外围设备,只与它的DP 主站交换用户数据,向主站报告本地诊断中断和过程中断:支持DPV1的非智能DP从站称为“标准"从站,它没有CPU模块,通过接口模块(IM)与DP主站通信。

ET 200是用得最多的标准DP从站,它们按主站的指令驱动I/O,并将I/O输入及故障诊断等信息返回给主站。

基于FPGA的通用卷积层IP核设计

基于FPGA的通用卷积层IP核设计作者:安国臣袁宏拓韩秀璐王晓君侯雨佳来源:《河北科技大学学报》2021年第03期摘要:针对目前卷积神经网络在小型化、并行化过程中遇到的计算速度不够、可移植性差的问题,根据卷积神经网络和FPGA器件的特点,提出了一种利用VHDL语言参数化高速通用卷积层IP核的设计方法。

利用卷积层的计算方式,将卷积核心设计为全并行化、流水线的计算模块,通过在卷积核心的每一行连接FIFO的方式改善数据流入的方式,减少地址跳转的操作,并加入控制核心使其可以随图像和卷积窗口大小调整卷积层参数,生成不同的卷积层,最后将卷积层与AXIS协议结合并封装成IP核。

结果表明,在50 MHz的工作频率下,使用2×2大小的卷积核对100×100的图像进行卷积计算,各项资源利用率不超过1%,耗时204 μs,计算速度理论上可以达到最高5 MF/s。

因此,设计方案在增加卷积模块可移植性的同时又保证了计算速度,为卷积神经网络在小型化器件上的实现提供了一种可行的方法。

关键词:集成电路技术;卷积神经网络;FPGA;卷积层;设计参数化中图分类号:TP274;TP391 文献标识码:Adoi:10.7535/hbkd.2021yx03005Design of universal convolutional layer IP core based on FPGAAN Guochen1, YUAN Hongtuo1, HAN Xiulu1, WANG Xiaojun1, HOU Yujia2(1.School of Information Science and Engineering,Hebei University of Science and Technology,Shijiazhuang,Hebei 050018,China;2.Shijiazhuang Foreign Education Group,Shijiazhuang,Hebei050022,China)Abstract:Aiming at the problems of insufficient computing speed and poor portability in the miniaturization and parallelization of convolutional neural network,this paper proposes a design of high-speed universal convolutional layer IP core using VHDL language based on the characteristics of convolutional neural network and FPGA yer based on convolution calculation,convolution core design is put forward for the parallel calculation and pipeline module,through each line in the convolution of the core connect to FIFO to improve the data flow,reduce the operating address jump,and join the control core to make it can adjust the convolution with images and convolution window size to layer parameters,generate different convolution layer,finally,the convolution layer is combined with the AXIS protocol and encapsulated into IP core.Under the working frequency of 50 MHz,the convolution calculation of 100×100 images with 2×2 convolution check is carried out.The utilization rate of each resource is less than 1%,and the time is 204 μs.The theoretical calculation speed can reach the maximum of 5 MF/s.The IP core structure of the convolutional layer not only increases the portability of the convolutional module,but also ensures the computing speed,which provides a feasible implementation method for the implementation of convolutional neural network on miniaturized devices.Keywords:integrated circuit technology;convolutional neural network;FPGA;convolution layer;design parameterization隨着深度学习研究的发展,卷积神经网络在语音识别[1]、图像理解[2]、目标跟踪[3-4]等领域发挥着重要作用。

FPGA和ARM的Profibus-DP主站通信平台设计

Pr i s DP ot oli na y e nd he t ke as i r t ol s dic s d The m a t r s a in omm u c ton p a f r i sgne . ofbu Pr oc sa l z d a t o n p sng p o oc i s us e . s e t to c nia i l lo m s de i d

信 协 议 , 点 是 令 牌 轮 转 协议 ; 出 了该 主 站 通 信 平 台的 系统 构 建 。该 通 信 平 台 可 以 独 立 实现 P oiu ~ 重 给 r f sDP主 站 ( b 1类 )

与其他主站( 1类 和 2类 ) 令 牌 传 递 的 主 主 通 信 功 能 , 及 其 与 从 站 的 主 从 通 信 功 能 。 的 以 关 键 词 :P oiu — P;主 站 ;令 牌 传 递 ;F GA;ARM r f sD b P 中 图 分 类 号 :TP 9 . 235 文 献 标 识 码 :A

F GA 和 ARM 的 P o iu - P r fb sDP主 站 通 信 平 台 设 计

孙 倩 华 。 庆 丰 , 继 强 满 夏

( 京 航 卒 航 天 大 学 机 械 工 程 及 自动 化 学 院 ,北 京 1 0 9 ) 北 0 l 1

摘 要 :提 出一 个使 用 F GA 和 ARM 微 控 制 器 实现 P oiu — P r f sDP主 站 ( b 1类 ) 信 平 台的 解 决 方 案 ; 析 了 P oiu P通 通 解 r f sD h

引 言

P o iu rf sDP是 由 西 门 子 公 司 推 的 一 种 开 放 式 现 场 b 总线 标 准 , 于 现 场 级 分 布 式 自动 化 外 没之 间 的高 速 数 据 用

基于ARM与FPGA的PROFIBUS-DP智能主站设计与实现

基于ARM与FPGA的PROFIBUS-DP智能主站设计与实现李丽娜;郝莉

【期刊名称】《中国仪器仪表》

【年(卷),期】2011(0)S1

【摘要】针对PROFIBUS现场总线发展现状,介绍了几种实现PROFIBUS-DP主站的可行方案,主要阐述基于ARM与FPGA的DP主站实现,完成相应的硬件设计和软件设计,并在文中给出主要的硬件结构图和程序流程图。

【总页数】4页(P80-83)

【关键词】PROFIBUS-DP主站;ARM与FPGA;从站状态机

【作者】李丽娜;郝莉

【作者单位】北京和利时系统工程有限公司

【正文语种】中文

【中图分类】TH7

【相关文献】

1.基于ARM+FPGA的EtherCAT主站设计及实现 [J], 徐健;唐小琦;宋宝

2.FPGA和ARM的Profibus-DP主站通信平台设计 [J], 孙倩华;满庆丰;夏继强

3.基于ARM的PROFIBUS-DP智能主站设计与研究 [J], 杨博;雷振伍;刘大千

4.基于ARM的PROFIBUS-DP智能主站设计 [J], 刘经宇;方彦军

5.基于VxWorks+ARM9的PROFIBUS-DP冗余主站的设计 [J], 胡明华;蒋济友;夏继强;满庆丰

因版权原因,仅展示原文概要,查看原文内容请购买。

嵌入式PROFIBUS-DP从站通信接口的设计

嵌入式PROFIBUS-DP从站通信接口的设计摘要:论述了一种PROFIBUS-DP从站开发方案,为自主开发具有PROFIBUS-DP通信功能产品的用户,以OEM方式提供PROFIBUS-DP从站通信接口。

关键词:现场总线;PROFIBUS-DP;从站;通信接口0引言目前国内对自动化产品(电器、仪表、驱动装置等)提出PROFIBUS通信功能要求,主要来源于:(1)国外生产设备及技术的引进,特别是从欧洲引进的成套设备通常采用PROFIBUS现场总线,因此对国内配套产品提出了现场总线PROFIBUS通信功能的技术要求;(2)国内自动化系统厂家比较成功的、面向行业的控制系统,要求系统技术向现场总线技术发展,同时也要求现场设备向智能化、网络化方向发展。

基于上述需求,嵌入式PROFIBUS-DP从站通信接口的设计为自主开发具有PROFIBUS-DP通信功能产品的用户提供了一种快速、高效的解决方案。

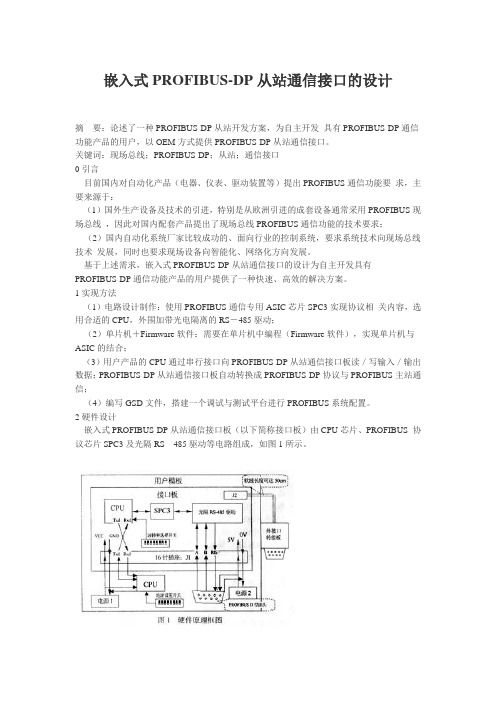

1实现方法(1)电路设计制作:使用PROFIBUS通信专用ASIC芯片SPC3实现协议相关内容,选用合适的CPU,外围加带光电隔离的RS-485驱动;(2)单片机+Firmware软件:需要在单片机中编程(Firmware软件),实现单片机与ASIC的结合;(3)用户产品的CPU通过串行接口向PROFIBUS-DP从站通信接口板读/写输入/输出数据;PROFIBUS-DP从站通信接口板自动转换成PROFIBUS-DP协议与PROFIBUS主站通信;(4)编写GSD文件,搭建一个调试与测试平台进行PROFIBUS系统配置。

2硬件设计嵌入式PROFIBUS-DP从站通信接口板(以下简称接口板)由CPU芯片、PROFIBUS 协议芯片SPC3及光隔RS 485驱动等电路组成,如图1所示。

接口板与用户模板采用串口连接,使用波特率选择开关可选择指定的7种波特率(9600、19.2K、38.4K、57.4K、115.2K、230.4K、460、8K)中的一种;接口板需要用户模板提供2组5 V电源(VCC/GND150 mA和5 V/0V-100 mA),分别作为接口板的电源及光隔外电源,由16针插座J1引入。

基于FPGA的MVB网络链路层IP核设计

基 于 F GA 的 MVB网络 链 路 层 P I P核 设 计

黄 采 伦 陈 艳 子 周 少 武 陈 特 放 。 , , ,

( . 南科 技 大 学信 息 与电 气工程 学 院 , 南 湘潭 4 1 0 ;. 1湖 湖 1 2 1 2 中南大 学信 息科 学与 工程 学 院 ,

C AN 等) 列 车 上 的应 用 相 比 , B在 实 时 性 、 在 MV 可

对连 接 MVB上 的设 备 按性 能 分 为 6类 , 次 是 : 依 0 类、 一类 、 类 、 类 、 二 三 四类 、 类 五 。0类 设 备 不 具有 数据通 信 能力 , 主要 包 括 中继器 和总 线 耦合 器 等; 一类 设 备具 有设 备 状态性 能 和过程数 据性 能 , 其 它 4 设备 在 一类设 备 具有 的性 能基础 上依 次增 加 类

通信 控制器 芯片 MVB 的垄 断 , C 给在 国内列 车上 推

广使 用 I C一6 3 5标 准 和 开发 基 于此 标 准 的其 它 E 17

应 用 带来 了极 大的 阻力[ 。同时 由于 当时 制造 工 。 ]

层协议 芯 片替代 方 案 。

关键 词 : 多功 能 车辆 总线 ; 场 可 编 程 门 阵 列 ; 现 列 车通 信 网络

bu a e l e hede i n o P o e orne wo k s, nd r a i d t sg fI c r s f t r z ln a r o he ba e o i k 1ye n t s fFPGA . i h t ke l c wh c a s p a e

中图分 类号 : P 3 . ; Ng . T 34 7T 15

文 献标识 码 : A

PROFIBUS-DP介绍

2

一、PROFIBUS-DP简介

DP是Decentralized Periphery(分布式外部设备)的缩写。 PROFIBUS-DP(简称为DP)主要用于制造业自动化系统中单元 级和现场级通信。特别适合PLC与现场级分布式I/O设备之间的 快速循环效据交换。DP是PROFIBUS中应用最广的通信方式。

7

三、PROFIBUS-DP设备的分类

PROFIBUS-DP网络的硬件由主站、从站、网 络部件和网络组态与诊断工具组成。网络部 件包括通信电缆、总线连接器、中继器、耦 合器,以及用于连接串行通信、以太网、AS-i、 EIB等网络系统的网络连接器。

PROFIBUS-DP设备分为以下3种不同类型的 站:

16

4.2、PLC的PROFIBUS通信处理器

S7-200的PROFIBUS通信处理器为EM277,在网络中只 能作从站。

S7-300的PROFIBUS通信处理器为CP342-5、CP343-5 和有光纤接口的CP 342-5 FO。

S7-400的PROFIBUS通信处理器为CP443-5基本型、CP 443-5扩展型、IM 467和IM467-FO。CP 443-5支持冗余 的总线拓扑结构。

12

3.3、DP从站

DP从站是PROFIBUS网络上的被动节点,用于输入信息 的采集和输出信息的发送,DP从站只与它的DP主站交 换用户数据,向主站报告本地诊断中断和过程中断。典 型的从站设备是传感器、执行器和测量变送器。在DP通 信过程中,从站是被动的。

非智能型的分布式I/O没有程序存储和程序执行功能,通 信适配器或接口模块用来接收主站的指令,按主站指令 驱动I/O,并将I/O输入及故障诊断等信息返回给主站。

PROFIBUSDP主从配置方法步骤

PROFIBUSDP主从配置方法步骤Profibus DP是一种常见的工业领域使用的通信协议,用于连接主控制设备和从控制设备。

主从配置是建立Profibus DP通信的关键步骤之一、下面将详细介绍Profibus DP主从配置的方法步骤。

1.硬件准备:首先,需要准备好Profibus DP网络所需的硬件设备,包括主控制设备、从控制设备、Profibus DP总线电缆和连接器。

主控制设备和从控制设备要能够支持Profibus DP协议。

2.确定网络拓扑结构:根据实际需要确定Profibus DP网络的拓扑结构,包括总线的起点和终点、主设备和从设备的位置等。

常见的拓扑结构有星型、总线型和环型。

3.连接总线电缆:根据确定的拓扑结构,连接总线电缆。

将总线电缆逐层连接到各个从设备上。

4.设置从设备:对于每个从设备,需要进行相应的设置,包括地址设定、通信速率设定、数据长度设定等。

这些设置应该与主设备的设置相匹配,以实现正常的通信。

在设置地址时,需要确保各个从设备的地址不重复。

5.设置主设备:设置主设备的操作与设置从设备类似,需要设定主设备的地址、通信速率、数据长度等参数。

主设备通常还需要配置输入输出模块、控制逻辑等内容,以实现对从设备的控制。

6.进行通信测试:完成主从设备的设置后,可以进行通信测试。

通过发送读写命令,检查从设备是否正常响应,并验证通信的正确性和稳定性。

如果发现通信故障,可以通过查看故障代码进行故障诊断。

7.完善配置:根据实际需要,进一步完善配置。

可以添加更多的从设备,配置更多的输入输出模块,调整通信速率和数据长度等参数,以满足具体的应用需求。

总的来说,Profibus DP主从配置方法的步骤包括硬件准备、确定网络拓扑结构、连接总线电缆、设置从设备、设置主设备、进行通信测试和完善配置。

这些步骤可以帮助用户成功地建立起Profibus DP通信,并实现对从设备的控制。

FPGA的高速多通道数据采集控制器IP核设计

FPGA的高速多通道数据采集控制器IP核设计随着可编程逻辑器件的不断进步和发展,FPGA 在嵌入式系统中发挥着越来越重要的作用。

本文介绍的在电能质量监测系统中信号采集模块控制器的IP 核,是采用硬件描述语言来实现的。

首先它是以ADS8364 芯片为控制对象,结合实际电路,将6 通道同步采样的16 位数据存储到FIFO 控制器。

当FIFO 控制器存储一个周期的数据后,产生一个中断信号,由PowerPC 对其进行高速读取。

这样能够减轻CPU 的负担,不需要频繁地对6 通道的采样数据进行读取,节省了CPU 运算资源。

1 ADS8364 芯片的原理与具体应用A/D 转换芯片ADS8364 是TI 公司推出的专为高速同步数据采集系统设计的高速度、低功耗、6 通道(三相电压、三相电流)同步采样的16 位A/D 转换芯片。

采用模拟和数字分别供电,在模拟输入端,有模拟参考电压输入、输出引脚和信号六通道正反相输入引脚;在数字端,主要包括控制ADS8364 的读/写、复位、片选引脚和转换结果输出总线。

ADS8364 芯片的转换过程为:当ADS8364 的HOLDX 保持至少20 ns 的低电平时,转换开始。

当转换结果被存入输出寄存器后,引脚EOC 的输出将保持半个时钟周期的低电平,以提示数据分析处理器进行转换结果的接收,处理器通过置RD 和CS 为低电平可使数据通过并行输出总线读出。

在转换数据的接收过程中,ADS8364 芯片各引脚工作的时序达到协调一致,才能保证监测设备良好工作,具体时序安排如ADS8364 芯片的数据输出方式分别由BYTE、ADD 与地址线A2、A1、A0 组合控制,转换结果的读取方式由电能质量监测系统中采用的数据分析处理器决定,一般可取直接读取、循环读取和FIFO 方式的任何一种。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数据传输和较小系统开销的要求, 对 OSI 参考模型 的七层协议进行 了 简 化 , 定 义 了 物 理 层 、数 据 链 路 层和用户层, 如图 1 所示[1]。其中数据链路层在协议 中 称 为 现 场 总 线 数 据 链 路 层 FDL ( Fieldbus Data Link layer) , 它是协议中有关数据通信的最基础部 分。

帧格式, 包括: 无数据字段固 定 长 度 的 帧 ( SD1) 、有 数据字段可变长度 的 帧 ( SD2) 、有 数 据 字 段 固 定 长 度的帧( SD3) 、令牌帧( SD4) 、短应答帧(SC)。对于从 站 FDL, 需 要 处 理 SD1、SD2、SD3、SC 四 种 , 完 成 这 些帧组帧与拆帧工作, 实现比特数据流与数据帧之 间的转换。所有帧的帧格式如图 2 所示。

协议处理模块是芯片的核心功能模块, 其主要 工 作 为 对 UART 收 发 器 接 收 的 数 据 根 据 协 议 规 范 进行具体分析和处理。该模块的工作过程说明如 下:

模块由帧检查状态机和帧处理状态机两个同 步状态机 [3] 组成。其中, 帧检查状态机实时监测 UART 收发器的工作状态, 若发现收发器接收到有 效的帧字节数据, 则根据该字节在接收数据帧中的 位置, 以及该数据帧的帧类型进行帧格式检查: 若 不符合帧格式, 则复位状态机, 丢弃该帧; 若为帧数

析和处理。 FDL 对 数 据 帧 的 收 发 需 符 合 总 线 规 定 的 时 间

参数。涉及到的时间参数主要包括时隙时间 TSL、同 步时间 TSYN、响应方 站 延 迟 时 间 TSDR、最 小 从 站 站延时 minTSDR、最大从站站延时 maxTSDR 等。以 上参数由 FMA1/2 提供。同时, FMA1/2 还负责对参 数的设定和管理, 提 供 如 复 位 、设 定 值 、读 值 、事 件 等服务。

规范, 给出了该控制器的总体结构和逻辑设计。该控制器可以完成 PROFIBUS- DP 协议数据链路层的功能, 结合外

部微处理器, 可构造一个完整的智能 PROFIBUS- DP 从站。该控制器可以支持最大至 12M 的通信波特率。

关键词: PROFIBUS- DP, 从站, FPGA, 链路层控制器

协议规定 FDL 负责向上层用户提 供 四 种 数 据 传输服务: 发送数据需应答( SDA) , 发送数据无需应 答( SDN) , 发送并请求数据需应答( SRD) , 循环发送 并请求数据需应答( CSRD) 。在 PROFIBUS- DP 总线 中, 数据传输依靠的是 SDN 和 SRD 两种 FDL 服务。 所有服务的实现依赖于对数据帧帧控制字节的分

由于状态机比较复杂, 在此处将其工作流程图 简单示意如图 5 所示。

波特率自动搜索模块在上电之后开始工作, 该 模块控制波特率发生器, 根据从低到高的顺序以相 应波特率进行搜索, 若在规定的时间或重试次数内 未搜索到正确的报文, 则转入下一级波特率进行搜 索, 直至搜索成功。在搜索成功后, 自动搜索波特率 模块控制波特率发生器输出当前波特率, 并通知其 它模块进行工作, 否则一直处于搜寻状态。本地 MCU 可通过内部寄存器组查询通信波特率状态信 息。

该模块的正常工作还依赖于以下功能单元: 接 收、发送缓冲区和相应的控制电路, 用于配合 UART 实现 SRD 和 SDN 服务; FMA1/2 单元, 用于为协议 ( 也包括物理层协议) 中用到的参数提供管理服务。 其中, 收发缓冲区由 FPGA 芯片内部的嵌入式 RAM 块实现, 长度各为 255 字节, 可支持 PEODIBUS- DP 扩展帧。为保证收发的可靠性, 采用了双缓冲的模 式, 当收发模块使用其中一个缓冲区时, MCU 可与 另一个缓冲区进行数据交换。FMA1/2 单元由 FMA1/ 2 控制逻辑和内部寄存器组构成。内部寄存器组负 责存储总线参数信息及控制信息, 芯片中有关的总 线信息都由其提供; 而控制逻辑负责根据寄存器组 中的控制信息提供对总线参数寄存器的管理。 3.3 MCU 接口模块

1 引言 PROFIBUS 是 由 SIEMENS 等 公 司 联 合 开 发 的

现场总线技术, 其中, PROFIBUS- DP 专为自动控制 系统和设备级分散 I/O 之间的通信而设计, 实现了 分布式控制系统的快 速 、循 环 数 据 传 输 , 在 国 内 工 业控制领域已经取得了大量的应用。PRODIBUS 协 议较为复杂, 目前只有少数国外厂商提供专用的 PROFIBUS 总 线 接 口 芯 片 , 如 SIEMENS 的 SPC3、 SPC4 以及 Motorola 的 68302、68360 等, 价格较高。 而 国 内 对 于 PROFIBUS 总 线 的 研 究 目 前 仍 局 限 于 应用领域, 绝大部分采用的是国外厂家提供的产 品, 即使是少部分国内厂家开发的产品, 也无一例 外地依靠国外厂商提供的芯片, 导致我国的自动化 行业难以掌握核心技术, 限制了该技术在国内一些 特殊领域的应用。与此同时, FPGA( 现场可编程门 阵列) 在电子、通信、计算机等领域得到了迅速普及 和应用, 基于 FPGA 的 IP 软核设计作为当前数字系

收稿日期: 2006- 04- 28 基金项目: 北京市教育委员会重点学科共建项目

( XK 100060419)

统设计领域中的重要方式之一, 已经成为 ASIC 前 端设计的重要手段。

为了推动 PROFIBUS- DP 在我国自动化行业的 发展和应用, 在认真分析总线协议的基础上, 本文 利用通用的 FPGA 芯片实现现场总线通信内核的固 化, 从而为开发出 PEOFIBUS- DP 协议芯片, 真正掌 握该总线标准的核心技术, 推动该技术的应用打下 基础。文中主要论述了 PROFIBUS- DP 的数据链路 层控制 LLC( Link Layer Control) 芯片的设计过程及 实现方法。

UART 收 发 器 负 责 FDL 数 据 帧 和 比 特 数 据 流 之间的转换。为了保证数据接收的可靠性, 对 RXD 以 16 倍于通信比特率的速度在比特位的中间位置 ( 第 7、8、9 个时钟点) 进行三点采样, 取出现 2 次以 上的信号作为真正的信号, 用以避免总线无效电平 干扰。 3.2 链路层协议处理模块

3 FDL IP 核的设计与实现 根据协议分析, 可以确定 FDL IP 核的功能如

下: 完成物理层的比特数据流和用户层数据的转 换, 维护对物理层和数据链路层的参数管理, 并向 上层协议提供数据传输服务。为了便于应用, 除了 实现上面分析的功能对外接口单元, 包括与物理层的接口和 与本地 MCU 的接口以及辅助管理单元。

中图分类号: TP293.5

文献标识码: A

文章编号: 1000- 7180( 2007) 01- 0102- 04

The Design of PROFIBUS- DP Slave Station Link Layer Contr oller based on FPGA

ZHU Bo, XIA Ji-qiang, ZHOU Li-ping, MAN Qing-feng

其搜寻的主要过程如图 4 所示。

104

微电子学与计算机

2007 年第 24 卷第 1 期

据单元, 则将其存入接收缓冲区中; 若为其它帧字 符, 则从中提取 FDL 相关信息, 如是否存在地址扩 展、使用的服务 存 取 点 等 , 为 帧 处 理 状 态 机 的 工 作 做好准备。同时, 该状态机还负责控制校验和计算 模块的工作, 将最终校验和与接收到的 FCS 进行比 对, 若不一致则认为帧数据接收错误, 将该帧丢弃。 待接收的字节数达到长度字节规定的长度后, 则认 为接收完毕, 启动帧处理状态机。随后帧处理状态 机对 FC 字节进行分析: 若为 SDN 或 SRD 服务, 则 根据协议规定的服务规程进行处理, 并映射为 DDLM 服务, 通知上层协议; 若为 FDL 状态请求, 则 进行 FDL 状态应答。

3.1 物理层接口模块 物理层接口模块负责芯片 FDL 层 与 物 理 层 之

间的连接, 完成物理层的比特数据流与 FDL 数据帧 之间的转换, 是 LLC 芯片的重要部分。该接口主要 包括波特率自动搜索模块和 UART ( 异步串行收发 器) 两部分。

PROFIBUS- DP 支 持 9.6K ̄12M 之 间 的 多 种 波 特率传输, 共分为 10 级。在同一网络上所选用的传 输波特率必须相同。为了省去人为设置的环节, 避 免可能因人为设置波特率不正确而导致的通信错 误, 在接口中设计了波特率自动搜索模块, 该模块 监听总线上的数据, 据此判定总线上数据通信的波 特率, 从而自动将芯片的通信波特率调整到相同速 度。

( School of Mechanical Engineering and Automation, Beijing University of Aeronautics and Astronautics, Beijing 100083)

Abstr act: A solution was put forward, to design a PROFIBUS- DP slave station controller based on FPGA. PROFIBUS- DP DLL (Data Link Layer) Protocol was analyzed, and the controller’s whole structure and logic design were detailed. The controller can afford the functions that PROFIBUS- DP DLL protocol specified, and implement a DP slave station when integrated a MCU. The highest communication rate of this station can go up to 12Mbps. Key wor ds: PROFIBUS- DP, Slave, FPGA, Link layer controller