Cmos 四象限乘法器的精确设计

乘法器设计方法

乘法器设计方法

乘法器是计算机中用于执行乘法运算的重要组件之一。

乘法器的设计方法可以分为以下几种:

1. 基于模2乘法的乘法器设计方法:此方法利用数字电路中的“与门”和“异或门”等基本逻辑门来实现乘法运算。

根据乘法的位运算特性,可以将乘法拆分成各位上的与门和异或门操作,然后通过级联这些门来实现完整的乘法运算。

2. 基于部分积累加法的乘法器设计方法:该方法利用部分积和累加的方式来实现乘法运算。

乘法器将两个操作数拆分成若干部分积,然后进行部分积的累加,最终得到乘法结果。

这种设计方法可以提高乘法器的运算速度和效率。

3. 基于Booth编码的乘法器设计方法:此方法利用Booth编码技术来减少乘法器中的部分积个数,从而减少乘法器的规模和功耗。

Booth编码是一种通过对数字进行编码来表示正负数的方法,利用Booth编码可以将乘法运算转化为模2加法运算,从而简化乘法器的设计和实现。

4. 基于乘法查找表的乘法器设计方法:该方法利用事先生成好的乘法查找表来实现乘法运算。

乘法查找表中存储了所有可能的乘法结果,通过查表即可得到运算结果。

这种设计方法在少位数乘法中具有较高的速度和效率。

5. 基于并行结构的乘法器设计方法:此方法利用并行计算的原理,将乘法运算过程中的各个部分并行处理,以提高乘法器的

运算速度。

这种设计方法常用于乘法器的优化和高速运算要求较高的场合。

以上是乘法器的一些常见设计方法,具体的设计方法选择应根据实际需求和应用场景来确定。

CMOS高性能运算放大器研究与设计

CMOS运算放大器的优势

CMOS运算放大器具有低功耗、高集成度、宽频带和良好的温度稳定性等优点。 相较于其他类型的运算放大器,如双极型和MOSFET型,CMOS运放具有更低的功耗 和更高的集成度,使得它在便携式设备和嵌入式系统中的应用具有显著优势。

CMOS低功耗运算放大器的设计 考虑因素

设计CMOS低功耗运算放大器时,需要考虑以下几个关键因素:

随着科技的不断发展,电子设备对高性能运算放大器的需求日益增长。其中, CMOS多级运算放大器因其高精度、低功耗、高稳定性等优点,被广泛应用于各种 模拟电路中。本次演示将探讨高性能CMOS多级运算放大器的研究与设计。

一、CMOS多级运算放大器概述

CMOS多级运算放大器是一种复杂的模拟电路,其性能由其增益、带宽、电源 抑制比、共模抑制比等因素决定。在CMOS工艺中,通过多级的放大级联,可以实 现更高的放大倍数和更低的噪声。

CMOS高性能运算放大器研究与设计

01 引言

03 研究方法

目录

02 文献综述 04 参考内容

引言

随着科技的不断发展,运算放大器在各种应用领域中的作用越来越重要。特 别是在复杂电子系统中,高性能运算放大器的设计和应用更是不可或缺。CMOS技 术由于其低功耗、高集成度和易于规模化的优点,成为了高性能运算放大器设计 的首选。本次演示将重点探讨CMOS高性能运算放大器的设计与研究。

3、仿真与优化

在设计和版图完成后,需要通过仿真软件对电路进行仿真,以验证其性能是 否满足设计要求。如果性能不满足要求,需要对电路和版图进行优化。优化的目 标通常包括提高增益、提高带宽、降低电源抑制比、降低噪声等。

三、高性能CMOS多级运算放大 器的应用

高性能CMOS多级运算放大器因其优异的性能被广泛应用于各种模拟电路中, 如放大器、比较器、模拟乘法器、模拟加减法器等。同时,在通信、雷达、音频 处理、图像处理等领域,高性能CMOS多级运算放大器也有着广泛的应用。

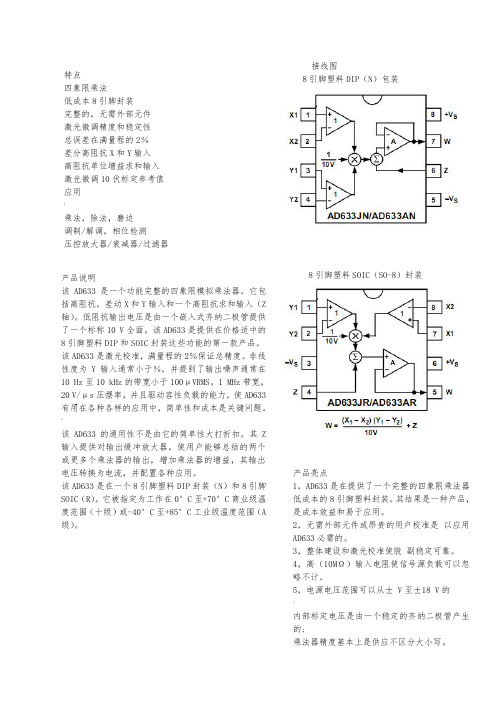

AD633四象限乘法器中文资料

特点四象限乘法低成本8引脚封装完整的,无需外部元件激光微调精度和稳定性总误差在满量程的2%差分高阻抗X和Y输入高阻抗单位增益求和输入激光微调10伏标定参考值应用乘法,除法,磨边调制/解调,相位检测压控放大器/衰减器/过滤器接线图8引脚塑料DIP(N)包装8引脚塑料SOIC(SO-8)封装产品说明该AD633是一个功能完整的四象限模拟乘法器。

它包括高阻抗,差动X和Y输入和一个高阻抗求和输入(Z轴)。

低阻抗输出电压是由一个嵌入式齐纳二极管提供了一个标称10 V全面。

该AD633是提供在价格适中的8引脚塑料DIP和SOIC封装这些功能的第一款产品。

该AD633是激光校准,满量程的2%保证总精度。

非线性度为Y输入通常小于0.1%,并提到了输出噪声通常在10 Hz至10 kHz的带宽小于100μVRMS。

1 MHz带宽,20 V/μs压摆率,并且驱动容性负载的能力,使AD633有用在各种各样的应用中,简单性和成本是关键问题。

该AD633的通用性不是由它的简单性大打折扣。

其Z输入提供对输出缓冲放大器,使用户能够总结的两个或更多个乘法器的输出,增加乘法器的增益,其输出电压转换为电流,并配置各种应用。

该AD633是在一个8引脚塑料DIP封装(N)和8引脚SOIC(R)。

它被指定为工作在0°C至+70°C商业级温度范围(十级)或-40°C至+85°C工业级温度范围(A级)。

产品亮点1,AD633是在提供了一个完整的四象限乘法器低成本的8引脚塑料封装。

其结果是一种产品,是成本效益和易于应用。

2,无需外部元件或昂贵的用户校准是以应用AD633必需的。

3,整体建设和激光校准使脱副稳定可靠。

4,高(10MΩ)输入电阻使信号源负载可以忽略不计。

5,电源电压范围可以从±4.5 V至±18 V的内部标定电压是由一个稳定的齐纳二极管产生的;乘法器精度基本上是供应不区分大小写。

cmos运放设计计算

cmos运放设计计算

设计CMOS运放器时,有几个重要参数需要计算,包括:增益、带宽、相位裕度和功耗。

1. 增益计算:CMOS运放器的增益可以根据其差动对输入以及特定的电源电压计算出来。

增益的计算通常采用差分对输入以及单端对输出的方式。

增益(Av)可以用以下公式计算:

Av = gm * RL

其中gm为微分对输入的跨导,RL为负载电阻。

2. 带宽计算:CMOS运放器的带宽取决于它的增益带宽积(GBW)。

可以使用以下公式计算GBW:

GBW = Av * fT

其中fT为晶体管的截止频率。

3. 相位裕度计算:CMOS运放器的相位裕度衡量着它在其中的运行频率范围内保持稳定的能力。

相位裕度可以通过下面的公式计算:

PM = 180° - | PMi - PMo |

其中PMi为输入相位延迟,PMo为输出相位延迟。

通过比较输入和输出相位延迟,可以计算出相位裕度。

4. 功耗计算:CMOS运放器的功耗可以通过计算其静态功耗和动态功耗来估计。

静态功耗是由于电流在非导通状态下流动而产生的功耗,而动态功耗是由于开关电流而产生的功耗。

静态功耗可以根据电流和电源电压计算得出。

动态功耗可以通过计算每一个开关周期的能量消耗来估计。

以上仅为CMOS运放器设计的基本计算方法,实际设计中需要根据具体的器件和电路参数进行详细计算和优化。

4位乘法器的设计

数字电子技术课程设计报告题目: 4位乘法器的设计学年 2009-2010 学期 2专业***** 班级:***学号:****** 姓名:***指导教师: ***8时间:2010年3 月1 日~2010 年3 月4 日浙江万里学院电子信息学院目录一、设计任务与要求 (3)二、设计总体方案 (3)三、各单元模块电路的设计实施方案 (5)四、结果分析 (7)五、体会和总结 (10)附录一、电路设计总图 (10)附录二、主要芯片引脚图 (10)1、 设计任务与要求试设计一4位二进制乘法器输入信号:4位被乘数A (A 3 A 2 A 1 A 0),4位乘数B (B 3 B 2 B 1 B 0),启动信号START 。

输出信号:8位乘积P (P 7 P 6 P 5 P 4 P 3 P 2 P 1 P 0),结束信号END 。

当发出一个高电平的START 信号以后,乘法器开始乘法运算,运算完成以后发出高电平的END 信号。

2、设计总体方案移向-加法器数混合乘法器实现框图如图所示,主体包括寄存序列、与逻辑和加法器等三部分。

乘数通过实现框图看出其原理就是:被乘数与乘数进入寄存序列,然后通过与逻辑和加法器的运算后得到被乘数与乘数的乘积。

其中启动信号用来启动乘法运算,而清零信号则为积存器和计数器的清零信号。

可以确定乘法器的表达式为:B AII B AI B AII AI Y ⨯+⨯⨯=⨯+⨯=222)2(移向-加法器树混合乘法器算法方案框图设计出的移向-加法器树混合乘法器框。

END P AB START1 0 1 11 1 0 1×1 0 1 10 0 0 01 0 1 11 0 1 111011001移向-加法器数混合乘法结构框图从结构框图中可以看出:被乘数与4位二进制乘数的低二位通过寄存器相乘得到的6位的2进制数部分积,然后被乘数与4位二进制的高二位在通过寄存器阵列相乘后也得到了6位2进制数部分积。

2个部分积通过加法器后得可以得到8位2进制乘积了。

AD633四象限乘法器中文资料

接线图8引脚塑料DIP (N )包装"~.特点 四象限乘法 低成本8引脚封装 完整的,无需外部元件 激光微调精度和稳定性 总误差在满量程的2% 差分高阻抗X 和Y 输入 高阻抗单位增益求和输入 激光微调10伏标定参考值 应用 ! 乘法,除法,磨边调制/解调,相位检测 压控放大器/衰减器/过滤器 产品说明 该AD633是一个功能完整的四象限模拟乘法器。

它包括高阻抗,差动X 和Y 输入和一个高阻抗求和输入(Z 轴)。

低阻抗输出电压是由一个嵌入式齐纳二极管提供了一个标称10 V 全面。

该AD633是提供在价格适中的8引脚塑料DIP 和SOIC 封装这些功能的第一款产品。

该AD633是激光校准,满量程的2%保证总精度。

非线性度为Y 输入通常小于%,并提到了输出噪声通常在10 Hz至10 kHz 的带宽小于100μVRMS 。

1 MHz 带宽,20 V/μs 压摆率,并且驱动容性负载的能力,使AD633有用在各种各样的应用中,简单性和成本是关键问题。

"该AD633的通用性不是由它的简单性大打折扣。

其Z 输入提供对输出缓冲放大器,使用户能够总结的两个或更多个乘法器的输出,增加乘法器的增益,其输出电压转换为电流,并配置各种应用。

该AD633是在一个8引脚塑料DIP 封装(N )和8引脚SOIC (R )。

它被指定为工作在0°C 至+70°C 商业级温度范围(十级)或-40°C 至+85°C 工业级温度范围(A 级)。

8引脚塑料SOIC (SO-8)封装 产品亮点1,AD633是在提供了一个完整的四象限乘法器 低成本的8引脚塑料封装。

其结果是一种产品,是成本效益和易于应用。

2,无需外部元件或昂贵的用户校准是 以应用AD633必需的。

3,整体建设和激光校准使脱 副稳定可靠。

4,高(10M Ω)输入电阻使信号源负载可以忽略不计。

5,电源电压范围可以从± V 至±18 V 的 /内部标定电压是由一个稳定的齐纳二极管产生的;乘法器精度基本上是供应不区分大小写。

CMOS高精度霍尔开关电路设计

CMOS高精度霍尔开关电路设计CMOS(互补金属氧化物半导体)是一种常用于集成电路设计的技术。

在设计高精度霍尔开关电路时,我们可以利用CMOS技术的优势来实现低功耗、高速度和高稳定性。

1.了解需求和规格:首先,需要明确设计的目标和要求。

这包括输入电压范围、工作频率、输出电压范围等。

同时,还要考虑功耗、面积和成本等设计限制。

2.电路框图设计:根据需求和规格,绘制电路框图。

霍尔开关电路通常包括霍尔元件、稳压电路、放大器、比较器等部分。

在CMOS设计中,可以使用晶体管来实现这些功能。

3.模拟电路设计:将电路框图转化为电路图,设计模拟电路部分。

在高精度霍尔开关电路中,放大器和比较器是关键的部分。

放大器用于放大霍尔元件的输出信号,使其可以被后续电路处理;比较器用于将放大器输出的信号与阈值进行比较,并将结果转化为数字信号。

4.数字逻辑设计:将模拟电路部分转化为数字电路。

利用CMOS技术中的晶体管和逻辑门来实现信号处理和控制。

5.器件选择和布局布线:选择合适的器件和元件,并进行布局和布线。

这包括选择合适的晶体管、电阻、电源和地线等。

布局要考虑电路的性能要求,比如应尽量减少干扰和噪声。

6.电路仿真和优化:通过电路仿真软件对设计进行模拟和优化。

这有助于找到性能瓶颈和改进电路的稳定性和精度。

7.制作电路图:根据设计结果,绘制电路图。

这包括详细的电路连接和元器件的数值参数。

8.制作原型:根据电路图制作原型电路板,通过实际测试和验证来评估电路的性能和稳定性。

9.优化和调整:根据测试结果,对电路进行优化和调整。

这可能包括更改电路参数、布线和元器件的选择。

10.整合和验证:将电路集成到系统中进行验证。

这可能需要与其他电路和设备进行适配和测试。

总结来说,CMOS高精度霍尔开关电路设计需要进行需求分析、电路框图设计、模拟电路设计、数字逻辑设计、器件选择和布局布线、电路仿真和优化、制作电路图、制作原型、优化和调整、整合和验证等一系列步骤。

CMOS详细设计PPT课件实用PPT课件

第13页/共43页

CMOS优化设置(高级用户)、BIOS FEATURES SETUP

HDD S.M.A.R.T. Capability (硬盘S.M.A.R.T.能力)选项:Enabled,Disabled SMART(

第12页/共43页

CMOS优化设置(高级用户)、BIOS FEATURES SETUP

MPS Version Control For OS (面向操作系统的MPS版本)选项:1.1,1.4它专用于多处理

器主板,用于确定MPS(MultiProcessor Specification,多重处 理器规范)的版本,以便让PC制造商构建基于英特尔架构的多处理 器系统。与1.1标准相比,1.4增加了扩展型结构表,可用于多重 PCI总线,并且对未来的升级十分有利。另外,v1.4拥有第二条PCI 总线,还无须PCI桥连接。新型的SOS(Server Operating Systems ,服务器操作系统)大都支持1.4标准,包括WinNT和Linux SMP( Symmetric Multi-Processing,对称式多重处理架构)。如果可以 的话,尽量使用v1.4。 OS Select For DRAM > 64MB

Security Option

(安全选项)选项:System,Setup只要在BIOS中建立了密码 ,此特性才会开启,设置为System时,BIOS在每一次启动都会输 入密码,设置为Setup时,在进入BIOS菜单时要求输入密码。如 果你不想别人乱动你的机器,还是加上密码的好。

4乘4位阵列乘法器设计

课程设计报告课程设计题目:4乘4位阵列乘法器设计学生姓名:杨博闻学号:201120070115专业:计算机科学与技术班级:1120701指导教师:汪宇玲2014年1月4日一、设计目的1.掌握乘法器的原理及其设计方法。

2 .熟练应用CPLD 设计及EDA 操作软件。

二、设计设备1.TDN-CM+或TDN-CM++教学实验系统一套。

2 ·PC 微机一台。

3·ispDesignEXPERT 软件模型机数据通路结构框图三、设计原理本实验用CPLD 来设计一个4 ×4 位乘法器,相对于画电路图输入,用ABEL 语言描述是比较方便的。

其算式如下(其中括号中的数字表示在ABEL 源程序描述中的功能块调用编号):a3 a2 a1 a0 ×b3 b2 b1 b0----------------------------------------------------------------------------------------------------------a3b0(10) a2b0(6) a1b0(3) a0b0(1)a3b1(13) a2b1(9) a1b1(5) a0b1(2)a3b2(15) a2b2(12) a1b2(8) a0b2(4)+a3b3(16) a2b3(14) a1b3(11) a0b3(7)----------------------------------------------------------------------------------------------------------- p7 p6 p5 p4 p3 p2 p1 p0四、设计步骤1.安装EDA 软件打开计算机电源,进入Windows 系统,安装上述ispDesignEXPERT 软件。

安装完成后,桌面和开始菜单中则建有ispDesignEXPERT 软件图标。

实验八,用LPM设计可调的8位数控分频器和4位乘法器(1)

河南工业大学EDA技术实验报告专业电科班级1304姓名学号201316030433实验地点6316+ 6515 实验日期2015-11-13 成绩评定一、实验项目实验八用LPM设计可调的8位数控分频器和4位乘法器二、实验目的1.基于LPM_COUNTER的数控分频器设计:数控分频器的功能要求为:若在其输入端给予不同的数据,输出脉冲具有相应的对输入时钟的分频比。

2.基于LPM_ROM的4位乘法器的设计:硬件乘法器有多种实现方法,相比之下,由高速RAM构成的乘法表方式的乘法器的运算速度最快。

本次实验就是利用原理图的绘制方法设计一个4位乘法器。

三、实验原理LPM _ROM实验原理图如下:LPM_ COUNTER实验原理图如下:图3 ROM数据表四、仿真结果及分析LPM_COUNTER的数控分频器的仿真波形图如下:基于LPM_ROM的4位乘法器的仿真波形如下:由图可知,当输入为1和9的时候,输出为9;当输入为2和6时,输出为12,等等,则可知输出结果是正确的的,则仿真波形为正确的。

五、硬件验证过程及结果分析对于LPM_COUNTER的数控分频器,首先按照原理图输入的设计步骤,通过元件输入窗口在原理图编辑窗口中调用兆功能块,按照上面的原理图方式连接起来,其中计数器LPM_COUNTER模块的参数设置可以自己设置,然后进行编译,仿真,这些都成功后就可以进行硬件验证了。

引脚锁定仍然和以前一样,将输入输出引脚锁定到合适的位置,然后编译,下载。

这样就可以将编译好的程序下载到试验箱上步骤:连接USB下载线,点击Tools选择Programmer.进入下载环境,在Hardware setup 选择USB,然后选择START 等待下载完成。

硬件验证:将十芯线一端插在之前锁定的q[0..7]引脚上,另一端插在24位输出显示HEX模块的数码管引脚上。

将十芯线一端插在之前锁定的d[0..7]引脚上,另一端插在24位输出显示HEX模块的D0~D8引脚上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第2l卷 2 1 99i年4

CMOS[/q象限乘法器的精确设计※ 椿长贵郭砺志 罗晋生 (西安变通夭学电子工程系) 摘 要

Vo1.21,№2 ADr.1 991

术文提 丫一种新型CMOS ̄象限乘法器,它基于MOSFET的电流一电压平方律 模型,采用电 此例电路及四管单元乘睡电路使乘法器能精确完成乘法运算。该乘 法器的电路结构简单、精确度高及实现四象限相乘的特点,使之在CMOS ̄信集成 电路,信号处理及运算电子系统中有广阔的应 {前景。文中对电路的结构进行了详 细分折和设计 并给出了HSPICE一Ⅱ模拟结果。 关锗词:CMOS模拟乘法器,铝栅P阱CMOS ̄艺,HSPICE-Ⅱ程序

引 言 模拟乘法器在通讯、信号处理及运算领 域有十分广泛的用途。由于Gilbert单元电 路的诞生,使双极集成电路在制作乘法器方 面取得了极大成功。尽管在过去十几年中由 于精确比例电容阵列、内部补偿的运算放大 器的成熟,使MOS模拟集成电路得到了迅 猛发展 ,如M0s A/D转换器、PCM调制/ 解调器、开关电容滤波器已得到广泛应用, 然而,由于MOS与双极晶体管工作机理上的 差异,使得采用MOS FET实现乘法运算遇 到了很大障碍。 人们早期提出的MOS乘法器结构是采用 可变跨导技术 和脉宽调制技术【 。最 近,基于代数平方的乘法器已有报导【。 ,怛 ※本文编辑部于1 991年2月收到。 ·8· 从电路结构上仍需要较多的M0s管。本文提 出的CMOS乘法器的乘法电路采用四管单 元 精确完成乘法功能,也适合于高频应 用。 电路分析与设计 我们设计的CMOS乘法器是依据M0S FET饱和区的平方律特性通过失调偏置实现 的,圈1为电路原理图 MM1,MM2, M:M3,MM4构成四管乘法单元,它们有相同 的版图尺寸,而且都工作在饱和区。设MOS 管的跨导因子为K,刚: ,-= z+ 。=置(y 一 ~ 0) +置( + + 一V ) lz=ljt+,“=K(y 十一y 一 r) +K(y , +y 一y ) V,+ 。li l ( )fJ

圈1 CMOS乘法器硬理图

田而差分输m电流为: ’ ff 一 2:2K y · (1) … £(1)ll_以行Ⅲ,差分辅Ⅲ电流正比于 V 和y 的乘积。为了保证MM1~MM4始终 工作在饱和医,要求输人电压满足下列关 系: l +y,l≤~V"一 一yD f (2) 即当y 、 y 均小于零时,要防止四管单元.审 ,壬何一个管子脱离饱和状态。 图2为实现上述原理的完整乘法器电路 图,MN 、MN MNI、MN2构成电压偏置 电流;MN3~MNl4构成各自电路级的电流源} MY.、MY2和M 、MY^两个差分级通过 MP 、MP。和M 、M 构成的电 鼙完饿电 压比例传输}同样,M)【1、MX。和M譬a、.MX 及

因2 CMOS模拟乘法器电路图 MY· MY 和MY 、MY6也完成电压比例传 输。若取上述四个差分级有相同的直流偏置 电流,且Mxl~Mx 、MY1~MYB有相同的 跨导因子 MPl、MP 与M 、Ⅷ ,MP1、 :M 与Ⅷ5、MP日与M'P7、MPB与M 、MP1n l卣电梳比均为4:1,9IlJ有: fy日:i/2v {Vc=I/2(V +y ) (4) 【Vf =1/2v

MP ~MPlB电流镜和MN】。~MN 电流镜构 成电流双端一单端输出转换

l产 v 总之,四管单 完成乘法运算;电压比例电 路提供四管单元所需输人电压,同时通过 整电流铳的电流比例使 V 的输入范围 扩展到各自的满量程额度,从而实现精确乘 法功能。 设计实例及模拟结果 根据模拟M0s集成电路设计理论,对图 (2)电路进行设计。衷I列出了所设计的管 子尺寸。设计所采用工艺为铝栅p阱CMOS2 ̄ 艺,标准线条宽度为8~1O m,该工艺下的 M0s器件模型参数如表Ⅱ所示。 采用HSPLCE一Ⅱ对设计方案进行了模

袭I CMO¥乘法器蕾子尺寸

拟 裘Ⅲ给出了模拟结果。该乘法器为电流 输出型,相当于一个跨导器,负载输出通过 拨}U雠工性负载 q‘把电流输出转换为电压输 fH。曲表Ⅲ可见,输八范围可达满量程,输 出电压可调节负载电阻使之限制在额定输出 范围内。 ’ -/ 图3路出了采用I-I..qPLCE-"IT程序摸拟的 乘法器传输特性曲线及非线性误差,可以看 出,满量程非线性误差小于±1畅。

表ⅢcMOS乘滏鼍HSPICE 报螬暴 参 数 数 值 单 位 输入电压范围 士4 { V 输出电压范围l ±‘ l v lII i.._~……一 跨导因子 J 5.2 L07s J l/0

非线性误差 J ±l孵 。 (F.s) 带宽( , j f q.5 f MHz L~— I系统失蠲电流f 0.06 f A …——一———·÷Ill一—÷一一 一:——一—— 功耗电溢 1:一} 3 f —mA

芯片设计面积 往 偏置电路使M 、VrN 的栅电位分别为 电源电压 ±6 0.38 一3.oV

寝11 CMOS,摸报集成电路 鼹件棋翟参数:一

y 。 J 0.8 -o.e} V 0.I }0.I f¨m L…—— l 1·2 . I·2 l pm

(L—lO,Um) o.004 0.008 f

" i 1.5E+16 10E+15。cm 3 一

l 500 l㈣ lcm v.8)一 !蔓 2.5~E+:_L 一

·1O·

\ 、 \一:

非蛀蛙碗差帆-I \ c 。一I / \ —。。 \乞

/ tl /

/ \: /

I}t3 cM0s乘法器HsPIcE模拟 传输特性及非线性误差

啊 结论 提出的采用四管单元及电压比例电路制 作CMOS模拟乘法器的设计方案使电路结构 简单,不需误差补偿元件而直堪 实现精磕乘 法。这种乘法器不仅在通讯、信号处理及数 学运算领域有广泛的用途 而且在模拟CM- OS VLSI系统(如连续时间滤波器,神经网 络芯片)中具有广阔的应用前景。

参考文献 [1]Y.Tsividis,IEEE J.Solid-Stare Circ., 1 987。sc 2(3)1 31 7~32l J.N.Babanezhad et 口j。ibid.1985, SO-20(6) 11 58~1168 D.C.SOO and R.G.Meyer,ibid.1 982, SC-1 7(6):11 74~11 78 S.C.Qin and R.L.Gieger,ibld.1087, SC一2O(6):1 143 ̄I 146 D.Brodarae at,Electronics Letter, 1 982,18,229 ̄260 3.S.Pena一 nol and J.A.Connelly, 雎暖E J.Solid-Stale Circufts,1 987,SC- 22(6):1064—1 073 K.Bult and H.Walllng ̄,ibid.1986, SC-21(6):430 ̄435

A Precision Design of CMOS Four Quadrant Multiplier Lin Changgui J Guo Lizhi,Luo Jinsheng Deparqnent o,Etecrrordc Engineer ̄n.g,Xi/a ̄Jiaotong University:

Abstract

A new CMOS four quadrant multiplier based on the MOSFET current—voltage, ̄ta- re law is proposed.The multiplier uses a voltage ratio circuit and a fottr-trar ̄'iS- tor cell multiplying circuit which enable its precision muhiplying operation.T矗 simple circuit structure,high precision operation and four quadmnt muhiplylng capability features make the multiplier widely applicable tO CMOS commuaicat壬c ICs,signal processing equiPments and electronic computing systemsA detailed

analysis oil the design and the circuit structure is given and the simulated res l荫

using HSPICE-II is presentedKey Wo rds:CMOS Analog Multiplier,AI Gate p--well CMOS Process, HSPICE-II Program 。 。

11,

㈣ ㈨ m