模拟集成电路设计——两级全差分高增益放大器设计

复旦大学模拟电路二级运放实例 (1)

尹睿

版权所有,不得侵犯!传播与修改请保留版权信息。

目录

1 2 引言 ..................................................................................................................... 1 电路分析 .............................................................................................................. 2 2.1 2.2 2.3 2.4 2.5 2.6 2.7 3 3.1 3.2 3.3 3.4 电路结构 ....................................................................................................... 2 电路描述 ....................................................................................................... 2 静态特性 ....................................................................................................... 3 频率特性 ....................................................................................................... 5 相位补偿 ....................................................................................................... 7 调零电阻 ....................................................................................................... 7 偏置电路 ..................................................................................................... 10 共模输入范围 .............................................................................................. 13 输出动态范围 .............................................................................................. 13 单位增益带宽(GBW) .............................................................................. 14 输入失调电压 .............................................................................................. 14

19_两级CMOS运算放大器的设计与spectrum仿真

LAB2 两级 CMOS 运算放大器的设计V DDirefM3 M4 M6xycvout vin1M1M2Vnvin2C LM7M8M53I d5一:基本目的:V SS图 1 两级 CMOS 运算放大器参考《CMOS 模拟集成电路设计第二版》p223.例 6.3-1 设计一种 CMOS 两级放大器,满足下列指标:A v = 5000V /V (74db )GB = 5MHzV out 范围=± 2VV DD = 2.5V C L = 10 pF ICMR = -1 ~ 2VV SS = -2.5V SR > 10V / μs P diss ≤ 2mW相位裕度: 60为什么要使用两级放大器,两级放大器的优点:单级放大器输出对管产生的小信号电流直接流过输出阻抗,因此单级电路增益被克制在输出对管的跨导与输出阻抗的乘积。

在单级放大器中,增益是与输出摆幅是相矛盾的。

要想得到大的增益我们能够采用共源共栅构造来极大地提高输出阻抗的值,但是共源共栅构造中堆叠的 MOS 管不可避免地减少了输出电压的范畴。

由于多一层管子就要最少多增加一种管子的过驱动电压。

这样在共源共栅构造的增益与输出电压范畴相矛盾。

为了缓和这种矛盾引进了两级运放,在两极运放中将这两点各在不同级实现。

如本文讨论的两级运放,大的增益靠第一级与第二级相级联而构成,而大的输出电压范畴靠第二级这个共源放大器来获得。

C表1 典型的无缓冲CMOS 运算放大器特性二:两级放大电路的电路分析:图1 中有多个电流镜构造,M5,M8 构成电流镜,流过M1 的电流与流过M2 电流Id1,2 =Id 3,4=Id 5/ 2 ,同时M3,M4 构成电流镜构造,如果M3 和M4 管对称,那么相似的构造使得在x,y 两点的电压在Vin 的共模输入范畴内不随着Vin 的变化而变化,为第二极放大器提供了恒定的电压和电流。

图1 所示,Cc 为引入的米勒赔偿电容。

表 2 0.5 μm 工艺库提供的模型参数p 1 p 2 z 1N P表 3 某些惯用的物理常数运用表 2、表 3 中的参数C OX = εox / t oxK ' = μ0C ox计算得到K ' ≅ 110μA / V 2K ' ≅ 62μA / V 2第一级差分放大器的电压增益为:A v 1 =第二极共源放大器的电压增益为-g m 1g ds 2 + gds 4(1)A v 2 =因此二级放大器的总的电压增益为-gm 6 g ds 6 + gds 7(2)A = A A =g m 1 g m 6=2g m 2 g m 6(3)v v 1 v 2 g + gg + gI (λ + λ)I (λ + λ)相位裕量有ds 2ds 4ds 6ds 7524667Φ = ±180 - tan -1(GB ) - tan -1(GB ) - tan -1(GB) = 60 Mp 2p 2v 1规定 60°的相位裕量,假设 RHP 零点高于 10GB 以上tan -1( A ) + tan -1(GB) + tan -1(0.1) = 1200tan -1(GB) = 24.30因此 p 2 ≥ 2.2GB即g m 6> 2.2( g m 2 ) C L C c由于规定60o 的相位裕量,因此g m 6> 10( gm 2 ) ⇒ g C c C c> 10g m 2可得到C c> 2.2C L10 = 0.22C L =2.2pF因此由赔偿电容最小值 2.2pF ,为了获得足够的相位裕量我们能够选定 Cc=3pF考虑共模输入范畴:在最大输入状况下,考虑 M1 处在饱和区,有V DD -V SG 3 -V n ≥ V IC (max) -V n -V TN 1 ⇒ V IC (max) ≤ V DD -V SG 3 + V TN 1在最小输入状况下,考虑 M5 处在饱和区,有V IC (min) -V SS -V GS 1 ≥ V Dsat 5 ⇒ V IC (min) ≤ V SS + V GS 1 + V Dsat 5(4)(5)而电路的某些基本指标有p 1 = -g m 1 A v C C(6)p = -g m 6 2C(7)Lz = g m 6 C C(8)GB =g m 1C C(9)CMR:正的 CMRV (最大)=V - V (最大) + V(最小)(10)inDDT 3 T 1负的 CMR V (最小)=V ++ V (最大) + V(饱和)(12)inSST 1 DS 5GB 是单位增益带宽 P1 是 3DB 带宽 GB= A v ⋅ p 1m 6W I 5 由电路的压摆率 SR =I d 5 得到C CI d 5 =(3*10-12)()10*106)=30μ A(为了一定的裕度, 我们取 iref I d 1,2 = I d 3,4 = I d 5 / 2 = 20μA下面用 ICMR 的规定计算(W/L)3= 40μA 。

全差分运算放大器设计

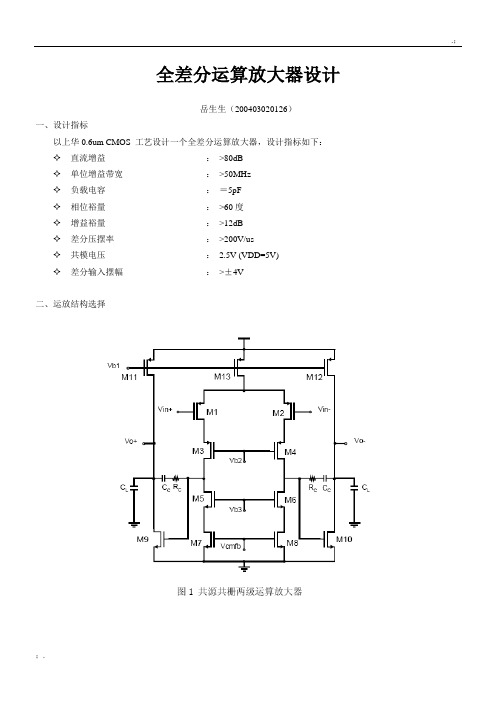

全差分运算放大器设计岳生生(200403020126)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益:>80dB✧单位增益带宽:>50MHz✧负载电容:=5pF✧相位裕量:>60度✧增益裕量:>12dB✧差分压摆率:>200V/us✧共模电压:2.5V (VDD=5V)✧差分输入摆幅:>±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg gg G A R r rr r g g r r r r=-=-=-+第二级增益92291129911()m o o o m m o o gg G AR r rgg=-=-=-+整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

实验3 差分放大电路设计实验

模拟电路课程设计报告题目:差分放大器设计专业年级:2012级通信工程组员:20121342104 王开鹏20121342105 王娜20121342107 王象指导教师:方振国2014年11月27日差分放大器设计一、实验内容设计一具有恒流源的单端输入一双端输出差动放大器。

VCC =12V,VEE=-12V,R L =20kΩ,Uid=20Mv。

性能指标要求R id>25kΩ,A vd≥25,K CMR>60Db。

二、实验原理图3.3.31、恒流源差分放大器在生产实践中,常需要对一些变化缓慢的信号进行放大,此时就不能用阻容耦合放大电路了。

为此,若要传送直流信号,就必须采用直接耦合。

差分式直流放大电路是一种特殊的直接耦合放大电路,要求电路两边的元器件完全对称,即两管型号相同、特性相同、各对应电阻值相等。

为了改善差分式直流放大电路的零点漂移,利用了负反馈能稳定工作点的原理,在两管公共发时极回路接入了稳流电阻R E和负电源V EE,R E愈大,稳定性愈好。

但由于负电源不可能用得很低,因而限制了R E阻值的增大。

为了解决这一矛盾,实际应用中常用晶体管恒流源来代替R E,形成了具有恒流源的差分放大器,电路如图3.3.3所示。

具有恒流源的差分放大器,应用十分广泛。

特别是在模拟集成电路中,常被用作输入级或中间放大级。

图3.3.3中,V1、V2称为差分对管,常采用双三极管,如5G921、BG319或FHIB等,它与信号源内阻R b1、R b2、集电极电阻R Cl、R C2及电位器RP共同组成差动放大器的基本电路。

V3、V4和电阻R e3、R e4、R共同组成恒流源电路,为差分对管的射极提供恒定电流I o。

电路中R1、R2是取值一致而且比较小的电阻,其作用是使在连接不同输入方式时加到电路两边的信号能达到大小相等、极性相反,或大小相等、极性相同,以满足差模信号输入或共模信号输入时的需要。

晶体管V1与V2、V3与V4是分别做在同一块衬底上的两个管子,电路参数应完全对称,调节RP 可调整电路的对称性。

现代模拟集成电路设计

《现代模拟集成电路设计》是2024年清华大学出版社出版的图书,作者是孙楠、刘佳欣、揭路。

本书围绕先进工艺节点,基于跨导效率的设计方法介绍现代模拟集成电路的分析与设计方法。

全书大体上分为三部分: 第一部分(第1~7章)对模拟集成电路中的基本元件晶体管,以及基本的分析与设计方法进行介绍,包括晶体管的长沟道模型与小信号模型、晶体管的基本电路结构、晶体管的性能指标、基于跨导效率的模拟电路设计方法、模拟电路的带宽分析方法、模拟电路中的噪声等。

第二部分(第8~10章)介绍模拟电路设计中常见的一些问题与设计技巧,如器件偏差、差分结构、负反馈技术等,并引入模拟电路中最常见的电路结构,即运算放大器与开关电容电路。

第三部分(第11~14章)详细介绍了运算放大器的分析与设计方法,并提供完整的运算放大器设计实例作为参考。

此外,第15章和第16章还介绍了基准源电路以及集成电路的工艺演进。

一种两级全差分折叠共源共栅运算放大器的设计

Rcc

=

Cc + CL gm12Cc

=

4.75 gm12

(2.10)

2.确定尾电流大小 由图 2.1 可知当输入差分信号很大时,不妨设 M2 管截止,此时通过 Cc2 的充电电流大

小为 ID6-ID10,由此可计算出压摆率为

SR = ID6 − ID10 > 2V / μs Cc

(2.11)

其中 Cc=8pF,故 ID6-ID10=16μA。在设计中为了留有裕量,取 ID6-ID10=25μA。又

载电容较大,为 30pF。可以预计电路的主极点位于第一级放大器的输出端,而非主极点位 于第二级放大器的输出端,且与主极点的值相差不远。频率补偿的目的就是尽可能使这两个 极点分离开,可以采取的方案有密勒补偿。同时,还可以引入左半平面的零点,以补偿非主

2

极点造成的相频恶化,例如给 CMFB 的共模取样电阻并上电容等。 除了考虑电路差模环的频率稳定性外,还应该考虑共模环的稳定性。因为 CMFB 电路

为了达到 60º相位裕度,应满足

(2.6)

PM = 180 + Ph[T ( jGB)] = 60

(2.7)

由

Ph[T ( jω)] = − tan−1( ω ) − tan−1( ω ) + tan−1( ω )

− p1

− p2

−z

(2.8)

代入(2.7)式,并设 z > 10GB,可以求得|p2|=2.2GB,Cc > 0.22CL=6.6pF。在设计中为

(2.13)

式中 VDS6 < VTP 总能成立,所以输入管 M1、M2 工作于饱和区。实际上,输入共模电压最 小可以低于 0V。输入共模电压最大值至少应为 1.2V,有

CMOS-两级运算放大器

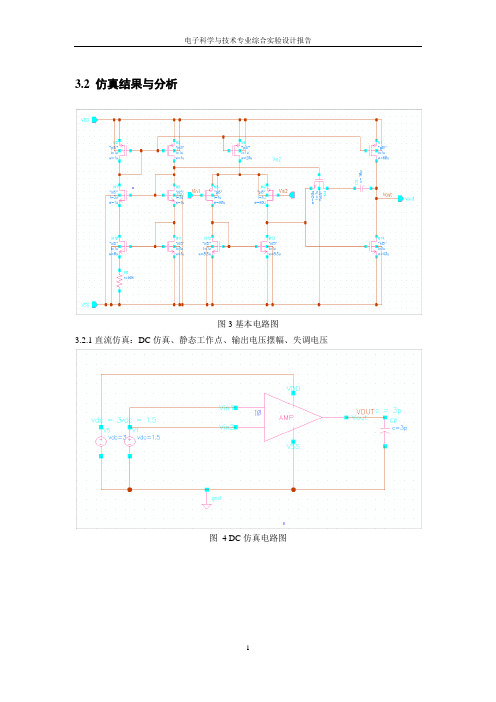

3.2 仿真结果与分析图3基本电路图3.2.1直流仿真:DC仿真、静态工作点、输出电压摆幅、失调电压图 4 DC仿真电路图图5 DC仿真结果分析:如图所示输入级放大电路由M1~M5 组成。

M1 和M2 组成PMOS 差分输入对,差分输入与单端输入相比可以有效抑制共模信号干扰;M3、M4 电流镜为有源负载;M5 为第一级提供恒定偏置电流。

输出级放大电路由M6、M7 组成。

M6 为共源放大器,M7 为其提供恒定偏置电流同时作为第二级输出负载。

相位补偿电路由M14 和Cc 构成。

M14 工作在线性区,可等效为一个电阻,与电容Cc 一起跨接在第二级输入输出之间,构成RC 密勒补偿。

M3 和M4 为第一级负载,将差模电流恢复为差模电压。

M6 为第二级跨导级,将差分电压信号转换为电流,而M7 再将此电流信号转换为电压输出。

由图知各个器件在静态工作点均工作在饱和区,M14工作于线性区。

图6输出电压摆幅电路图图7输出电压摆幅仿真结果图分析:输出动态范围即输出摆幅,是所有晶体管都工作在饱和区时的输出电压的范围。

如果输出电压过低,M6工作在线性区,如果输出电压过高,M7 工作在线性区。

所以输出摆幅范围是V GST6≤V OUT≤V DD-V GST7。

一旦输出电压超过输出摆幅,某一个MOS 管就会进入线性区,输出阻抗降低,增益也就会下降。

降低过驱动电压可以拓展输出摆幅。

注意,如果仅仅是容性负载,输出电压可以达到电源电压和地,但此时增益严重下降,失真已经出现。

如果有阻性负载(接地),输出电压是无论如何都到达不了电源电压的。

由图可知输出电压摆幅为0.27V≤V OUT≤2.97V。

图8失调电压电路图图9失调电压仿真结果图分析: 对于差分输入、单端输出的运放,为最大化输出摆幅,输出电压共模点取在输出摆幅的一半处,即(V DD-V GST7+V GST6)/2,如果M6和M7过驱动电压相同,那么输出电压共模点取在V DD/2 处。

跨导放大器的分析与设计(1)-清华大学模拟集成电路分析与设计

单级OTA

z 输出共模电平 不稳定

依赖于上下 两个电流镜 之间的电流 匹配程度

需要共模反 馈环路来稳 定输出共模 电平

差模半电路

跨导放大器的负载

z 低负载阻抗RL会大幅降低放大器的增益

RL可能是片外负载或来自反馈网络的负载效应

z 反馈系统的高精度要求放大器有高的增益

反馈网络采用高阻值电阻

M2的过驱动电压增加,输出端摆幅减小

z 减小噪声:减小Cgg1,提高M1的特征频率

常用积分公式

单级Cascode放大器

z 减小噪声:减小gm2(减小Cascode管的跨导效率)

M2的过驱动电压增加,输出端摆幅减小 减小gm2/gm1和Cx

两级放大器

推导过程见网 络学堂中上载 的阅读材料

z 降低噪声:增加Cc z 如果CL较小,β较大,第二级对噪声有较大贡献

z 右半平面零点将减小相位裕度

除非gm2>>βgm1

消除右半平面零点的影响

z 消除补偿电容Cc所引起的前馈通路

插入源极跟随器 插入共栅放大器

z 电阻与Miller电容串联

将零点频率推高到无穷远处 将零点移到左半平面,并与非主极点相消

消除右半平面零点:插入源极跟随器

z前馈支路由CC

M3

和Cgs3串联组成:

绝大多数集成放大器都 是OTA

电压控制电流源(VCCS) 高输出阻抗

不能驱动低的电阻性负 载

采用电容性反馈(如开 关电容电路)

提要

z 跨导放大器的基本概念 z 单级跨导放大器 z 两级OTA的基本特性 z 两级OTA的频率补偿:Miller补偿 z 反馈型OTA中的噪声 z 两级OTA的设计 z 阶跃响应:线性建立过程 z 阶跃响应:放大器中的压摆问题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

全差分高增益放大器的设计一、设计产品名称全差分高增益放大器二、设计目的1. 掌握模拟集成电路的基本设计流程;2. 掌握Cadence基本使用方法;3. 学习模拟集成电路版图的设计要点;4. 培养分析、解决问题的综合能力;5. 掌握模拟集成电路的仿真方法;6. 熟悉设计验证流程方法。

三、设计内容全差分高增益放大器(Full-differential OTA)是一种非常典型的模拟IP,在各类模拟信号链路、ADC、模拟滤波器等重要模拟电路中应用广泛,是模拟IC 设计人员必需掌握的一种基础性IP 设计。

采用华大九天Aether 全定制IC 设计平台及其自带的0.18um PDK,设计一款全差分高增益放大器电路,完成电路图设计、前仿真、Layout 设计和物理验证(DRC&LVS)。

考虑以下OTA 架构:图1 OTA架构四、电路设计思路模拟集成电路的设计分为前端与后端,设计流程可以分为明确性能要求、选择电路结构、计算器件参数、原理图绘制、前仿真、版图绘制、DRC设计规则检查、LVS版图与电路图一致性检查、寄生参数提取及后仿真、流片测试。

本次实验使用基于华大九天Aether 全定制IC 设计平台及其自带的0.18um PDK,实现模拟集成电路全差分高增益放大器的全流程设计与仿真。

(1)性能指标:需要验证三种PVT Corner:a) 电源电压1.8V,温度27℃,corner 为TT;b) 电源电压1.6V,温度80℃,corner 为SS;c) 电源电压2.0V,温度-40℃,corner 为FF;要求各Corner 下开环技术指标(含Cload=10fF):①放大器开环DC 增益Av0≥90dB;②0dB 带宽BW0≥500MHz;③相位裕度Phase Margin≥50°。

④DC 抑制比PSRR-0≥60dB,(3*2=6 分)⑤10MHz 时抑制比PSRR-10M≥45dB。

(3*2=6 分)(2)电路结构选择:根据性能指标要求,可以采用两级运放的设计,其中第一级运放主要为了提高增益,第二级主要为了增大输出电压摆幅。

备选一级放大器电路结构有:套筒式共源共栅和折叠式共源共栅,其电路图如下。

图2 折叠式共源共栅电路结构图3 套筒式共源共栅电路结构两种运放结构特性对比如下:表1 运放结构特性对比综上,设计中选择增益较高的传统的套筒式共源共栅结构运放作第一级,选择简单的共源结构作第二级,提供髙的输出摆幅和大的驱动电流。

筒单的两级运放的直流增益比较小,因此我们采用共源共栅结构的增益更大。

总体设计由输入级、输出级、共模反馈电路、频路补偿电路和偏置电路组成。

其中,输入级采用套筒式共源共栅放大器,输出级采用共源放大器,偏置电路选用偏置在饱和区的MOS管作为尾电流源,频率补偿电路采用密勒电容跨接在第一级和第二级放大器之间。

电路拓扑图如下图所示图4 电路结构图五、电路设计过程及仿真结果1、第一级电路设计根据直流增益90dB 的要求,一般第二级运放(共源级)的增益只有10 左右,所以第一级运放的增益至少要达到1000,即60dB。

(1)参数计算完成了电路图的基本结构之后,接下来就是给每个元件加入设计量,这样就需要对各个器件的参数进行分配和计算。

I. 电流的分配由于VDD=1.8V,总的电流为8mA。

给第一级分配4mA电流,第二级分配2mA电流,共模反馈2mA的电流。

对于第一级而言两条支路是完全对称,所以给每条之路分配2mA的电流,即所有mos管(除尾电流源外)的电流均为2mA;而对于尾电流源的电流值为两个输入支路电流之和,即为4mA。

II. 过驱动电压的分配由于题目没有要求输出摆幅的大小,可以从流过mos管的电流的大小来确定分配给它们的过驱动电压的大小,以此为标准分配过驱动电压。

此处给所有mos管分配0.2V过驱动电压。

III. 宽长比的确定通过电流与过驱动电压的关系式确定宽长比,由于所有mos 管都必须工作在饱和区,所以使用饱和区的电流-过驱动电压的关系:Nmos管:I DS=1/2u n C OX(W/L)(V GS-V th)2=1/2u n C OX V OD2=>(W/L)= (2 I DS)/ ( u n C OX V OD2)Pmos管:I DS=1/2u p C OX(W/L)(V GS-V th)2=1/2u p C OX V OD2=>(W/L)=(2 I DS)/ (u p C OX V OD2)根据公式可得所有mos 管的宽长比,分别为:(W/L)p=980;(W/L)n=259。

根据上面求出的宽长比确定宽度和长度。

由于使用工艺库,取L=350nm,同样可以得到各种W值W p=177.65um,W n=63.9umIV. 分配初始偏置电压值mos管阈值电压的初始值由工艺库中给定,给定的pmos管的阈值电压为V th =-0.45V左右,nmos管的阈值电压为V th=0.45V左右,这些值将在仿真过程中修正。

pmos管M0,M1,的过驱动电压为V OD0=V OD1=0.2V,而|V th|=0.45V,则偏置电压源电压为V b1=1.8V-(0.45V+0.2V)=1.15V。

pmos管M2,M3的过驱动电压为V OD2=V OD3=0.2V,而|V th|=0.45V,则偏置电压源电压为V0=1.8V-(0.45V+0.2V+0.2V)=0.95V。

nmos管M6,M7的过驱动电压(输入管的偏置直流电压部分)为V OD6=V OD7=02V,而V th=0.45V,则偏置电压源电压为V0=0.45V+0.2V=0.65V。

nmos管M4,M5的过驱动电压为V OD4=V OD5=0.2V,而V th=0.45V,则偏置电压源电压为V0=0.45V+0.2V+0.2V=0.85V。

根据给定的初始的偏置电压给各个偏置电压源加值。

(2)绘制原理图电路参数确定完之后进行电路原理图的绘制,绘制过程中注意:所有的pmos 管的衬底都必须接电源;所有nmos 管的衬底都必须接地;直接用电压源给出了偏置电压。

图5 第一级放大器电路原理图(3)生成symbol图形Symbol的生成过成:我们选择在已经制作好的cell view 中建立它的symbol,点击Create->Symbol View,这样就可以直接从已经建好的cell view 的schematic 中建立了它的symbol 文件。

建立的symbol 的图形(可以改变图形形状),如下图所示:图6 第一级放大器symbol图形2、第一级电路仿真对于已经生成symbol 的图形,需要给输入端加入激励之后才能够进行仿真。

需要生成一个新的cell view 作仿真。

(1)绘制测试电路图Cell view 的生成同上所述,在cell view 的设计过程中加入刚刚设计的第一级套筒式共源共栅放大器作为仿真模型,对其输入端加激励。

第一级放大器测试电路图,如下图所示:图7 第一级放大器测试电路图(2)设定仿真类型对第一级放大器的直流工作点(OP)、交流特性(AC)和瞬态特性(Tran)进行仿真,其中AC仿真扫描频率范围1Hz—1GHz,瞬态仿真范围0—2ms。

(3)仿真及其参量修正进行完以上分析之后,就可以对第一级电路进行仿真了。

仿真的方法有两种,可以通过点击菜单中的Simulation-Netlist and Run 进行网表的提取和仿真;第二种方法是通过快捷方式。

根据打印出的mos管状态图中的Vth值,通过V0=V OD+V th+V s来修正偏置电压的值,再进行仿真。

在此过程中,由于M0,M1,M8不存在衬偏效应所以他们的阈值电压值的改变可能会小一些,所以先调整这些管子的偏置电压值比较合适;而对于M2,M3,M4,M5,M6,M7这些mos管而言,都存在衬偏效应,所以他们的值改变的比较大,需要不断的修正仿真,直到这些值都基本不变化即可。

这样就完全确定了偏置电压的值。

下来要做的工作是考虑所有的mos管是否工作在饱和区,同样是通过打印mos管的状态来确定的。

需要考虑V DS≥V GS-V th才能使mos管工作在饱和区。

从打印的图中察看电压V DS,V GS-V th的大小,如果不满足V DS≥V GS-V th,那么mos 管不饱和,需要通过调节mos管的宽长比来改变它的饱和状态。

只有当所有的mos管都达到饱和时,放大器的增益才能达到最大。

注意:a) 在调节mos 管的宽长比时,只能在原来的宽长比的基础上对宽度作适当调整,不能不考虑原来的值,大幅度调整,这样将会和你的设计完全不符的情况。

b) 如果当所有的mos管都已达到饱和,但是对于放大器的增益还是不满足时可以将输出端两端的mos管的宽长同时加大,这样可以使增益大幅度增加。

这是由于当宽长同时加大时,电流、跨导等量由于宽长比的值没有变化,所以它们的值也不改变。

但是由于长度L增大,使λ值减小,从而使这个mos管的输出电阻增大,输出两端的mos管的宽长同时加大,即M2,M3,M4,M5的宽长同时加大,使输出电阻r o2,r o3,r o4,r o5增大,从而使增益加大。

|A v|=G m R out=g m10*{[ g m3r o3 ( r o10// r o1)]//( g m5r o5 r o7)}(4)仿真结果由于我们是对差动电路进行分析,所以输出需要分析两个输出端的差动值,需要使用计算器,将两个单端的输出的tran值相减得到差动电路的tran值。

①Tran仿真结果图8 第一级放大器Tran仿真图形②AC仿真结果图9 第一级放大器AC仿真图形3、第二级电路设计第二级采用共源放大器,提供高的输出摆幅。

(1)参数计算完成了电路图的基本结构之后,接下来就是设计每个元件的参数,这样就需要对各个器件的参数进行分配和计算。

I. 电流的分配总的电流为I DS=8mA。

给第一级分配4mA电流,第二级分配2mA电流。

对于第二级而言两条支路也是完全对称,所以给每条支路分配1mA的电流,即所有mos的电流均为1mA。

II. 过驱动电压的分配由于所有mos 管流过的电流是相等的,均为1mA,所以考虑给pmos 管分配0.2V 过驱动电压,而给nmos 管分配0.2V 过驱动电压。

III . 宽长比的确定使用饱和区的电流-过驱动电压的关系:Nmos管:I DS=1/2u n C OX(W/L)(V GS-V th)2=1/2u n C OX V OD2=>(W/L)= (2 I DS)/ ( u n C OX V OD2)Pmos管:I DS=1/2u p C OX(W/L)(V GS-V th)2=1/2u p C OX V OD2=>(W/L)=(2 I DS)/ (u p C OX V OD2)根据公式可得所有mos 管的宽长比,分别为:(W/L)n=162;(W/L)p=452。