集成电路刻蚀用硅部件加工及最新发展

反应离子刻蚀氮化硅与二氧化硅工艺的研究

反应离子刻蚀(RIE)是一种常见的微纳加工技术,广泛应用于半导体、MEMS(微机电系统)和光学器件制造。

在RIE过程中,气体放电产生的离子和化学反应共同作用于物理表面,实现对材料的微纳加工。

氮化硅和二氧化硅是常见的半导体材料,在半导体器件制造和微纳加工领域具有重要的应用价值。

1. 反应离子刻蚀氮化硅与二氧化硅工艺的研究背景在当今微纳加工技术中,氮化硅和二氧化硅的刻蚀工艺研究具有重要的意义。

氮化硅具有优异的机械性能和光学性能,是MEMS和光学器件中常用的材料。

而二氧化硅作为传统的半导体材料,在集成电路和微纳加工中具有广泛的应用。

研究氮化硅与二氧化硅的反应离子刻蚀工艺,对于推动微纳加工技术的发展具有重要的意义。

2. 反应离子刻蚀氮化硅与二氧化硅工艺的基本原理反应离子刻蚀氮化硅与二氧化硅的工艺基本原理是利用气体放电产生的离子轰击材料表面,同时在离子轰击的同时进行化学反应,从而实现对材料的刻蚀。

在RIE过程中,气体放电产生的离子加速到表面并与材料发生碰撞,从而引发表面的化学反应。

通过选择合适的反应气体和控制工艺参数,可以实现对氮化硅和二氧化硅的高效刻蚀。

3. 反应离子刻蚀氮化硅与二氧化硅工艺的研究现状目前,针对氮化硅与二氧化硅的刻蚀工艺研究已经取得了一定的进展。

研究者通过优化反应气体的组成、调节工艺参数和改进刻蚀设备,实现了对氮化硅和二氧化硅的高质量刻蚀。

还有一些研究致力于在RIE 过程中减小残留应力、改善表面粗糙度和控制刻蚀剩余物等问题,以满足不同领域对于氮化硅和二氧化硅材料加工的要求。

4. 反应离子刻蚀氮化硅与二氧化硅工艺的发展趋势随着微纳加工技术的不断发展,反应离子刻蚀氮化硅与二氧化硅工艺将会朝着更加高效、精密和可控的方向发展。

未来的研究重点可能集中在以下几个方面:一是针对特定器件和应用领域的工艺优化,提高刻蚀质量和加工效率;二是开发新型的反应气体和刻蚀设备,拓展氮化硅与二氧化硅的刻蚀工艺窗口;三是结合表面修饰技术,实现对氮化硅和二氧化硅表面特性的精细调控。

一种fdsoi器件及其制造方法与流程

一种fdsoi器件及其制造方法与流程本文将为您详细介绍一种基于FDSOI(Fully Depleted Silicon-on-Insulator)技术的器件,以及其制造方法和流程。

FDSOI技术作为一种先进的半导体工艺,具有低功耗、高速度等优点,广泛应用于集成电路领域。

一、FDSOI器件简介FDSOI(Fully Depleted Silicon-on-Insulator)器件是一种基于SOI (Silicon-on-Insulator)技术的器件。

与传统的CMOS器件相比,FDSOI器件具有以下优势:1.低功耗:由于SOI结构具有绝缘埋层,可以有效降低漏电流,从而降低功耗。

2.高速度:SOI结构减少了器件的寄生电容,提高了电路的开关速度。

3.优良的短沟道效应抑制能力:FDSOI器件在短沟道条件下,具有较好的阈值电压控制能力。

二、FDSOI器件的制造方法与流程1.制造方法:FDSOI器件的制造主要采用以下两种方法:a.晶圆键合技术:将SOI晶圆与handle晶圆(含有绝缘埋层)进行键合,然后进行研磨、刻蚀等工艺,制备出FDSON器件。

b.分子束外延(MBE)技术:在绝缘埋层上直接生长硅薄膜,然后进行后续的器件制备工艺。

2.制造流程:a.晶圆准备:选择合适的SOI晶圆和handle晶圆,进行清洗、抛光等预处理。

b.键合:将SOI晶圆与handle晶圆进行键合,键合过程中需确保键合界面无缺陷。

c.研磨与刻蚀:将键合后的晶圆进行研磨,去除多余的硅材料,然后进行刻蚀,制备出所需的器件结构。

d.器件隔离:采用局部氧化或离子注入等方法,实现器件之间的电学隔离。

e.源漏极注入:在器件的有源区进行磷或硼注入,形成源漏极。

f.金属接触:在源漏极区域沉积金属,形成接触,同时进行金属化布线。

g.封装:将制备好的FDSOI器件进行封装,完成器件制造。

三、总结FDSOI器件作为一种先进的半导体器件,具有低功耗、高速度等优点,在集成电路领域具有广泛的应用前景。

刻蚀技术和微加工

刻蚀技术和微加工随着人类科技的不断发展,刻蚀技术和微加工逐渐成为了人们关注的热点。

这两个技术都涉及到微小尺度下的加工和处理,具有非常重要的应用价值。

从基础研究到应用的制造业,刻蚀技术和微加工都有着广泛的使用场景和潜在的发展前景。

一、刻蚀技术刻蚀技术是一种通过化学反应或者物理反应来去除或者形成某些材料表面的方法。

它在电子学、光学、包装技术、微机电系统(MEMS)、生物医学器械制造和重要光学设施等领域中得到广泛的应用。

石英、氮化硅和氧化硅等材料他们有一个共同点都是难以用机械切割直接制成所需的结构,但可以使用刻蚀的方法。

主要的刻蚀方法有化学刻蚀和物理刻蚀两种。

化学刻蚀以介质加热或者光照的方式作用于表层化学反应,去掉被刻蚀的区域。

通常使用的介质是酸、碱、高温蒸汽和溶液。

物理刻蚀方法主要由离子束刻蚀、磨损刻蚀和放电刻蚀。

其中离子束刻蚀使用电子束或离子束的方式改变表面形貌;磨损刻蚀是通过机械磨损的方式去掉材料表面的某部分;放电刻蚀是通过电子的放电使得表面溶解和脱落。

刻蚀技术在半导体制造、微加工、生物医学、纳米领域等方面有着广泛的应用。

在半导体上刻蚀出不同的材料,可以形成电路结构和互联器件;在生物医学领域中,像视网膜植入物和神经系统刺激器等,需要使用到非常精细的刻蚀技术;而在微纳制造和纳米科技领域中,刻蚀技术被广泛应用于建设微型器件和结构。

二、微加工微加工通常涉及到对于微米及以下级别的物质进行加工处理。

跟刻蚀技术一样,在微加工领域,同时也存在着许多的技术方法,比如化学机械抛光、电化学加工、激光蚀刻等等,由于涉及到微米甚至更小的精度,呢,必须对于操作人员的技术素质有着非常高的要求。

有了微加工技术,就可以实现制造出一系列的微型元件、微型传感器、以及其他各种微型装置等等,由此显然可以看出在微加工领域具有着重要的应用价值。

另外,在纳米技术、生物医学、半导体等领域中也都有微加工技术的应用。

例如在微电子学领域中,通过微加工可以制造出各种晶体管、电容和电感等组成的电路器件。

sinx干法刻蚀工艺

sinx干法刻蚀工艺一、引言干法刻蚀工艺是一种常用于微电子制造中的重要工艺,被广泛应用于半导体器件、光电子器件以及微纳加工领域。

其中,sinx干法刻蚀工艺是一种常见且重要的技术,本文将对其原理、工艺流程以及应用进行介绍。

sinx干法刻蚀工艺是基于化学气相刻蚀技术实现的。

其主要原理是通过将硅表面暴露于含有氟气和氧气的刻蚀气体环境中,形成硅氧化物(SiOx)层,而后使用氟气将其刻蚀去除。

由于刻蚀速率与刻蚀气体的浓度、温度、压力等因素相关,因此可以通过调节这些参数来控制刻蚀速率和刻蚀深度,从而实现对硅表面的精确刻蚀。

三、sinx干法刻蚀工艺流程sinx干法刻蚀工艺主要包括前处理、刻蚀和后处理三个步骤。

1. 前处理:首先需要对待刻蚀的硅表面进行清洗,以去除表面的杂质和有机物。

常用的清洗方法包括酸洗、碱洗和超声清洗等。

清洗后,将硅片放入刻蚀室中,进行真空抽取和预热处理。

2. 刻蚀:在刻蚀室中,加入刻蚀气体,常用的刻蚀气体有氟化氢(HF)和氟化氮(NF3)等。

调节刻蚀气体的流量、温度和压力等参数,控制刻蚀速率和刻蚀深度。

刻蚀过程中,通过监测刻蚀速率以及表面形貌等参数,进行实时调节和控制。

3. 后处理:刻蚀完成后,需要对刻蚀后的硅片进行清洗和去除刻蚀残留物。

然后,进行表面抛光和再清洗等步骤,以保证硅片表面的光洁度和无尘污。

最后,进行检测和质量控制,确保刻蚀工艺的稳定性和一致性。

四、sinx干法刻蚀工艺应用sinx干法刻蚀工艺在微电子制造中有着广泛的应用。

主要应用于制备硅氧化物(SiOx)薄膜,用于制作MOS场效应晶体管、光电子器件和微纳加工等领域。

此外,sinx干法刻蚀工艺还可以用于制备硅纳米线、纳米孔洞和微纳结构等,用于研究和应用于纳米器件和生物传感器等领域。

五、总结sinx干法刻蚀工艺是一种重要的微电子制造工艺,通过调节刻蚀气体的浓度、温度和压力等参数,可以实现对硅表面的精确刻蚀。

该工艺应用广泛,可用于制备硅氧化物薄膜和制作各种微纳器件。

光刻湿法刻蚀研究

THANKS FOR WATCHING

感谢您的观看

04 光刻湿法刻蚀技术未来展 望

技术发展趋势

纳米精度控制

随着光刻技术的不断进步,湿法刻蚀技术将向纳米精度控制方向 发展,实现更精细的刻蚀效果。

干湿法结合

干法刻蚀和湿法刻蚀各有优缺点,未来光刻湿法刻蚀技术将与干法 刻蚀技术相结合,发挥各自优势,提高刻蚀效率和精度。

环保与可持续发展

随着环保意识的提高,光刻湿法刻蚀技术将更加注重环保和可持续 发展,减少对环境的负面影响。

VS

详细描述

优化刻蚀条件和后处理工艺可以有效降低 表面粗糙度。例如,采用低能电子束轰击 技术可以减小表面粗糙度,提高器件性能 。此外,适当的退火处理也可以改善表面 质量。

刻蚀速率提升

总结词

提高刻蚀速率是提高生产效率和降低成本的关键因素。

详细描述

通过优化刻蚀气体组成、压力和温度等工艺参数,可以显著提高刻蚀速率。此外,采用高活性的刻蚀气体和先进 的反应器设计也是提高刻蚀速率的有效途径。

涂胶与预烘

涂胶

将光刻胶涂覆在硅片表面,形成 一层均匀的光刻胶膜。

预烘

通过烘烤使光刻胶中的溶剂挥发 ,增强光刻胶与硅片之间的附着 性。

曝光与显影

曝光

通过紫外光照射使光刻胶中的特定分子发生化学反应,形成图案。

显影

将曝光后的光刻胶浸泡在显影液中,溶解未反应的光刻胶分子,形成所需图案。

刻蚀与退胶

刻蚀

使用化学或物理方法将硅片表面未被 光刻胶覆盖的区域去除,形成微结构。

总结词

刻蚀精度是光刻湿法刻蚀技术的关键指标,直接影响到器件性能和成品率。

详细描述

刻蚀精度受到多种因素的影响,如光刻胶厚度、曝光能量、刻蚀气体流量和压力等。为了提高刻蚀精 度,可以采用先进的工艺控制技术,如实时监测和反馈控制系统,以确保刻蚀深度和形状符合设计要 求。

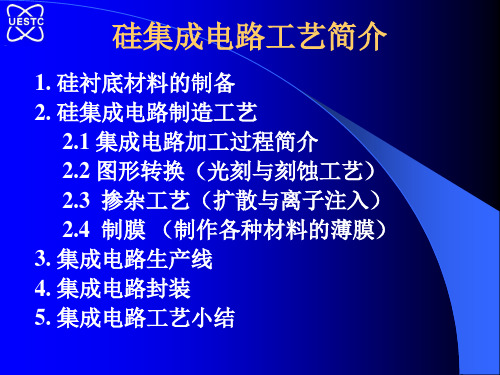

硅集成电路工艺简介

负胶:分辨率差,适于加工线宽≥3m的

线条

几种常见的光刻方法

接触式光刻、接近式曝光、投影式曝光

光学曝光的各种曝光方式及其利弊

接成品率低。

优点:掩模版寿命长,成本低。

接近式

非

缺点:衍射效应严重,影响分辨率。

接

优点:无像差,无驻波效应影响。

D

G

S

G

D

S

Al

SiO2

N

N

P-si

掺杂:将需要的杂质掺入特定的 半导体区域中,以达到改变半导 体电学性质,形成PN结、电阻、 欧姆接触

磷(P)、砷(As) — N型硅

硼(B) — P型硅

掺杂工艺:扩散、离子注入

扩散

替位式扩散:杂质离子占据硅原子的位:

– Ⅲ、Ⅴ族元素 – 一般要在很高的温度(950~1280℃)下进行,

蚀。具有溅射刻蚀和等离子刻蚀两者的优点,同 时兼有各向异性和选择性好的优点。目前,RIE 已成为VLSI工艺中应用最广泛的主流刻蚀技术。

2.3 掺杂工艺(扩散与离子注入)

通过掺杂可以在硅衬底上形成不同类型的半导体区

域,构成各种器件结构。掺杂工艺的基本思想就是通过 某种技术措施,将一定浓度的Ⅲ价元素,如硼,或Ⅴ价 元素,如磷、砷等掺入半导体衬底。

2. 集成电路制造工艺

2.1 集成电路加工过程简介

一、硅片制备(切、磨、抛)

*圆片(Wafer)尺寸与衬底厚度: 3— 0.4mm 5— 0.625mm 4— 0.525mm 6— 0.75mm

硅片的大部分用于机械支撑。

晶圆退火工艺流程

晶体生长

Crystal Growth

硅晶体

Si Crystal

芯片蚀刻工艺流程

芯片蚀刻工艺流程

芯片蚀刻是集成电路制造过程中的一个重要步骤,用于在硅片上形成电路图案。

下面是一般的芯片蚀刻工艺流程的概述:

1. 准备硅片:选择合适的硅片,并对其进行清洗和处理,以确保表面的干净和平整。

2. 感光胶涂覆:在硅片表面涂覆一层感光胶,然后利用旋涂机或类似设备将胶液均匀地涂覆在整个硅片表面上。

3. 感光胶曝光:将硅片放在光刻机上,并通过掩膜对感光胶进行曝光。

掩膜上的图案允许光照射到感光胶的特定区域,形成所需的电路图案。

4. 显影:将曝光后的硅片放入显影机中,显影液将溶解未曝光区域的感光胶。

这样,在曝光过的区域,感光胶会保留下来形成保护层,而未曝光区域的感光胶会被溶解掉。

5. 蚀刻:将经过显影的硅片放入蚀刻机中,利用蚀刻液去除未被保护的硅片表面。

蚀刻液的成分根据需要进行调整,以实现所需的蚀刻深度和形状。

6. 清洗:在蚀刻后,需要将硅片进行清洗,以去除蚀刻液和感光胶残留物。

常见的清洗方法包括浸泡在溶剂中、超声波清洗和喷洗。

7. 检验:经过清洗后,芯片需要进行检验,以确保蚀刻过程正确完成。

常见的检验方法包括光学显微镜、扫描电子显微镜和电气测试。

上述步骤只是芯片蚀刻的一般流程,实际的工艺流程可能会根据具体的芯片制造需求和技术发展而有所不同。

硅的干法刻蚀

硅的干法刻蚀

硅的干法刻蚀是指在不使用任何化学试剂或溶液的情况下,通过加热和压力来破坏材料表面的氧化层,从而获得所需要的物质。

这种方法通常被称为“空气刻蚀”或“空气刀片”。

干法刻蚀技术已经广泛应用于各个领域,包括半导体、光伏电池等。

它可以用于制造芯片上的多晶硅(Si)层,也可以用于清除表面的杂质和污染物,如氧化物、金属残留物等。

此外,干法刻蚀还能够提高器件性能并降低生产成本。

然而,由于缺乏实验室测试设备,人们对于干法刻蚀技术的了解仍然有限。

因此,在进行干法刻蚀操作之前,建议先进行实验室测试,确保其安全性和可靠性。

同时,在操作过程中,应严格遵守相关规范和标准,避免出现意外事故。

《集成电路制造工艺与工程应用》第三章第五节金属硅化物技术

《集成电路制造工艺与工程应用》第三章第五节:金属硅化物技术金属硅化物工艺技术内容简述:随着集成电路工艺制程技术的不断发展,为了提高集成电路的集成度,同时提升器件的工作速度和降低它的功耗,半导体工艺的特征尺寸不断缩小,晶体管的栅、源和漏有源区的尺寸也会相应缩小,而它们的等效串联电阻会相应变大,从而影响电路的速度。

为了改善等效串联电阻,半导体业界先后发展出金属硅化物工艺技术Polycide和Salicide。

最先出现的金属硅化物工艺技术是Polycide工艺技术,Polycide工艺技术是为了改善多晶硅栅的等效串联电阻和接触孔的接触电阻,Polycide工艺技术仅仅在多晶硅栅上形成金属硅化物,源和漏有源区不会形成金属硅化物,所以它没有办法改善晶体管源和漏有源区的等效串联电阻和接触孔的接触电阻。

为了改善晶体管源和漏有源区的等效串联电阻和接触孔的接触电阻而发展出Salicide工艺技术,Salicide工艺技术不仅在多晶硅栅上形成金属硅化物,而且在源和漏有源区也会形成金属硅化物,它同时改善晶体管的栅、源和漏有源区的等效串联电阻和接触孔的接触电阻。

本文摘选自《集成电路制造工艺与工程应用》第三章第五节的内容,这部分内容简单介绍了Polycide工艺技术、Salicide工艺技术和SAB工艺技术的原理,并以纳米级工艺形成ESD器件和Non-Salicide器件为例介绍SAB和Salicide工艺技术的工程应用。

3.5 金属硅化物技术-------------------------------------------------------------------------------------------------3.5.1 Polycide工艺技术--------------------------------------------------------------------------------------3.5.2 Salicide工艺技术---------------------------------------------------------------------------------------3.5.3 SAB工艺技术--------------------------------------------------------------------------------------------3.5.4 SAB和Salicide工艺技术的工程应用------------------------------------------------------------3.5 金属硅化物技术当半导体工艺的特征尺寸缩小到亚微米以下时,晶体管的栅、源和漏有源区的尺寸宽度也会相应缩小,而它们的等效串联电阻会相应变大,从而影响电路的速度。

等离子体蚀刻及其在大规模集成电路制造中的应用

等离子体蚀刻及其在大规模集成电路制造中的应用

等离子体蚀刻是一种通过离子化气体产生的等离子体来加工材

料的方法。

它在大规模集成电路制造中具有重要的应用价值。

首先,等离子体蚀刻能够实现非常高的加工精度和加工速度,这对于微细电路的制造非常重要。

其次,等离子体蚀刻过程中的反应物可以被完全清除,不会对电路性能造成影响。

此外,等离子体蚀刻还可以用于制造纳米材料和微型传感器等领域。

在大规模集成电路制造中,等离子体蚀刻主要用于图形化加工硅片和构造微细电路。

在这个过程中,需要精确控制等离子体参数以及加工过程中的温度、压力等因素,以确保加工质量和稳定性。

同时,还需要使用复杂的掩模技术和光刻技术来实现精细的加工形状和结构。

总之,等离子体蚀刻在大规模集成电路制造中有着广泛的应用和重要的地位。

随着技术的不断发展,相信它将会在微电子制造中发挥更为重要的作用。

- 1 -。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Material Sciences 材料科学, 2020, 10(7), 588-594Published Online July 2020 in Hans. /journal/mshttps:///10.12677/ms.2020.107071Silicon Parts Used in Ic Etching Manufacture and New DevelopmentLiming Ku, Qinfa Zhu, Haibin Chen, Dujuan Bai, Qinghua Xiao, Zhirui YanGRINM Semiconductor Materials Co., Ltd., General Research Institute for Nonferrous Metals, BeijingReceived: Jul. 9th, 2020; accepted: Jul. 22nd, 2020; published: Jul. 29th, 2020AbstractThe line width below 28 nm, especially 7 nm, not only requires higher performance of large silicon wafers, but also puts forward higher requirements for silicon parts used in etching tool, such as the uniformity of the surface of silicon ring, mechanical damage and morphology of silicon elec-trode hole, etc. Silicon parts for 7 nm line width will need more refined process, and multi-step precision grinding instead of lapping, which can not only improve the flatness and roughness, but also reduce the damage layer on the surface, especially the sub-surface. We can use an improved drilling method to solve the problem of mechanical damage. This paper discusses the processing flow of silicon parts and points out the latest development of silicon parts.KeywordsEtch, Silicon Parts, Silicon Ring, Silicon Electrode, Grinding, Mechanical Damage集成电路刻蚀用硅部件加工及最新发展库黎明,朱秦发,陈海滨,白杜娟,肖清华,闫志瑞北京有研科技集团有研半导体材料有限公司,北京收稿日期:2020年7月9日;录用日期:2020年7月22日;发布日期:2020年7月29日摘要集成电路芯片28 nm以下特别是7 nm线宽不仅对大硅片各项性能要求越来越高,对刻蚀机上用的硅部件也提出了更严格的要求,例如硅环表面的均匀性,硅电极微孔内壁机械损伤和微孔表面形貌等。

在加工方法上,7 nm线宽用硅部件将采取更精细化的加工,用多步精磨削代替磨片,不仅可以提高平面度和粗库黎明 等糙度,还可以减少表面特别是亚表面的损伤层;硅电极采用改进后的打孔方式,解决微孔内壁机械损伤的问题,同时采取特殊的损伤检测方法来指导制造工艺的优化。

本文对硅部件产品的加工流程进行了论述,指出了硅部件加工的最新发展趋势。

关键词刻蚀,硅部件,硅环,硅电极,磨削,机械损伤Copyright © 2020 by author(s) and Hans Publishers Inc. This work is licensed under the Creative Commons Attribution International License (CC BY 4.0)./licenses/by/4.0/1. 引言集成电路芯片是信息技术产业最重要的基础性部件,被誉为电子信息产品的“心脏”[1]。

伴随5G 通讯、人工智能、大数据、自动驾驶、物联网、工业自动化等新兴产业的崛起,近年来我国半导体产业投融资热潮持续高涨,大硅片需求旺盛,在供给方面,实现硅材料国产化、保障关键核心材料供应安全获得产业内大力支持。

我国集成电路发展势头迅猛,带动半导体硅材料的发展,例如12英寸大硅片、刻蚀用硅部件制品等。

刻蚀用硅部件包括硅环和硅电极,主要用于8~12英寸等离子刻蚀机上。

在集成电路制造过程中,刻蚀晶圆的同时也对硅部件进行刻蚀,高纯硅部件和晶圆均为硅材料,刻蚀电学性能更加均匀,因此硅部件制品广泛用于半导体刻蚀机中。

硅部件制品周期性消耗,成为晶圆加工过程的重要零部件耗材,比如一个硅环在加工约200片晶圆后就需要更换,直接影响晶圆的电学性能。

硅部件制品市场需求主要受芯片厂晶圆加工能力驱动,按全球目前晶圆生产情况,全球年需求8寸硅环和硅电极数量分别约30万片和7万多片,12寸环片硅电极数量分别约50万片和10万片,市场规模总计约40亿人民币。

目前硅部件制品市场主要依靠进口,现有市场日本和韩国制造厂商为主,占据市场80%以上份额。

刻蚀机示意图如图1:Figure 1. Schematic diagram of the etching machine图1. 刻蚀机原理示意图库黎明 等现阶段12英寸硅片技术正在向极端精细化发展,全球大尺寸硅片的领先水平已达到7 nm ,主流应用在28~16 nm ,7 nm 商业需求已显现,未来几年7 nm 需求将成为主流。

线宽的不断变小给硅部件加工提出了越来越高的要求,更小线宽对硅部件制品的要求主要体现在参数精确控制上,如表面及边缘粗糙度、真圆度、硅电极微孔内部机械损伤厚度和微孔边缘形貌等,这就要求硅部件厂家不断优化工艺,从更微观的方面进行思考如何加工过程工艺的控制。

2. 硅部件制品加工流程通过对大直径硅单晶棒进行精密加工来获得所要求的硅制品,加工工序主要分为单晶拉制和机械成型两部分。

硅环加工流程如下图2:Figure 2. Manufacturing process of silicon ring图2. 硅环加工流程图硅电极和硅环的加工基本相同,主要是增加了打孔工序。

硅电极打孔时硅电极安装到打孔机上,使用金刚石钻头打孔,打孔后再对电极表面进行研磨和腐蚀,去除表面的机械损伤。

钻头直径一般为0.4 mm ,钻头部分喷涂金刚石颗粒,提高钻头寿命,加工后的微孔直径一般要求0.4~0.6 mm ,微孔的质量好坏直接决定电极的成品率。

硅电极加工流程如下图3:Figure 3. Manufacturing process of silicon electrode图3. 硅电极加工流程图图2和图3中,每道加工工序后均有清洗工序去除机械加工带来的油污和硅渣残留。

在单晶拉制过程中,主要是通过设计热场结构和拓宽晶体生长工艺窗口,控制滑移缺陷和电阻率参数,拉制出无滑移位错的单晶,电阻率一般要求1~5欧姆·厘米和60~80欧姆·厘米,使之满足集成电路刻蚀机用硅部件制造的要求。

机械成型主要是通过滚磨、截断、线切割、磨床和加工中心对硅晶棒进行机械处理,加工成硅环或硅电极需要的环状或圆片状,然后通过平面研磨来去除线切割带来的表面切割纹和降低表面机械损伤和微裂纹,研磨后平面度 < 10 um,再通过腐蚀和抛光处理来降低表面粗糙度,进一步去除因机库黎明 等械加工带来的机械损伤。

加工中心主要加工内外径的形状,如内外径R/C 倒角、内径台阶、内径参考面等,尺寸精度要求±0.1 mm 。

腐蚀工序使用混酸腐蚀(HF 55%:HNO 3 60%:CH 3COOH 99.5%),去除硅部件表面和硅电极微孔内壁的机械损伤。

抛光一般采用双面抛光,使表面达到一定的粗糙度和光洁度。

3. 7 nm 线宽用硅部件技术的发展趋势3.1. 平面研磨因线切割的本身原因,硅部件半成品表面会有线切割带来的波纹以及较大的损伤层,线切割后需要进行表面研磨。

为了去除表面的线切割纹,一般采用磨片进行加工,研磨后平面度小于20微米。

随着集成电路进入7 nm 技术水平,对硅部件表面的粗糙度和内径台阶尺寸要求越来越高,磨片因同时加工正面和背面,不能精确控制正面台阶的尺寸,因此到7 nm 技术水平及以下,磨片将被磨削代替,一般采用粗磨削(300~600#金刚石砂轮)和精磨削(1200#),在加工中心工序后再采用二次精磨削(2000#),在去除表面加工中心工序带来的划伤的同时,进一步降低表面粗糙度,磨削后表面光洁度较好,更有利于腐蚀的均匀性[2]。

磨片和磨削后表面粗糙度如图4,磨片后表面粗糙度一般在0.4微米。

损伤层深度可以通过化学方法进行测试[3],损伤层深度大约24微米[4],并且在磨片过程中磨砂对表面是刚性去除,很容易在次表面产生微细裂纹[5]。

经过三次磨削后表面粗糙度约为0.02微米,采用多步磨削后的表面相比磨片表面粗糙度水平有较大的提高。

加工后表面显微镜图如图5,磨削后表面更加均匀,磨削后损伤小于5微米[6],损伤层在后续腐蚀过程中能被去除。

(a) 磨片后粗糙度图 (b) 磨削后粗糙度图Figure 4. Surface roughness chart of silicon parts after lapping and grinding图4. 磨片和磨削后表面粗糙度图(a) 磨片后显微镜图 (b) 磨削后显微镜图Figure 5. Surface morphology image of silicon parts after lapping and grinding图5. 磨片和磨削后表面形貌库黎明 等3.2. 硅电极打孔技术在刻蚀过程中,硅电极的主要作用是用于反应体气体通过微孔均匀进入反应腔体内,微孔尺寸、分布和内壁质量对刻蚀产品电学性能有直接的影响。

硅电极表面分布有300~900个微孔,打孔时使用直径为0.4 mm 、长度为11.5 mm 的金刚石钻头,而硅电极一般厚度10 mm ,长径比L/D = 28.75:1,这就导致深孔加工排屑困难、冷却效果差、刀具的磨损大、使用寿命短和微孔直径偏差大的问题,特别是打孔深度大,钻头部分到底端时抖动幅度大,导致微孔尺寸不规则,机械损伤深,为了克服这些问题,打孔工序采取双面打孔技术,如下图6:Figure 6. Schematic diagram of double side drilling图6. 硅电极双面打孔示意图双面打孔技术难点是如何控制第二次打孔时所有微孔的偏移量,偏移量要求小于0.1 mm ,为了解决这一问题,需要使用特殊的工装,并且在打孔前安装半成品时要保证电极平面度、刀具跳动和设备加工工位的XY 轴同心度。