FPGA先进先出存储器 FIFO

fpga缓存数据的方法

fpga缓存数据的方法

在FPGA中,缓存数据的常用方法有以下几种:

1. 分布式RAM缓存:FPGA通常包含大量的分布式RAM资源,可以将数据存储在RAM中进行缓存。

这种方法通过编写硬件描述语言代码来实现,将数据存储在分布式RAM中,并通过适当的地址控制来读取和写入数据。

2. 块RAM缓存:除了分布式RAM,FPGA还通常包含一些较大的块RAM资源,这些块RAM通常具有更高的容量和性能。

可以将数据存储在块RAM中进行缓存。

与分布式RAM 不同,块RAM具有更高的带宽和更低的延迟。

3. FIFO缓存:FPGA中的FIFO(First-In-First-Out)模块可以用作数据缓存。

通过使用FIFO模块,可以实现数据的有序读取和写入,并且具有先进先出的特性。

FIFO模块通常用于数据的临时存储和数据流的调整。

4. 内部寄存器缓存:FPGA内部一般会有大量的可用寄存器资源,可以使用这些寄存器作为数据的缓存。

通过在逻辑电路中添加寄存器,可以实现数据的存储和缓存。

这种方法通常适用于较小的数据量和低延迟要求的应用。

需要注意的是,FPGA的缓存策略和实现方法会因具体应用和需求而有所不同。

选择合适的缓存方法需要综合考虑数据量、性能、延迟和资源利用等因素。

fifo读写

fifo读写

FIFO,全称为First In First Out,即先进先出,是一种常见的数据结构。

在计算机领域中,FIFO通常指的是一种管道(pipe)的实现方式,也称为命名管道(named pipe),用于进程间通信。

在FIFO中,数据的读取和写入都是按照先进先出的原则进行的。

当一个进程向FIFO中写入数据时,数据会被存储在FIFO的尾部,而当另一个进程从FIFO中读取数据时,数据会从FIFO的头部开始读取。

FIFO的读写操作可以分为阻塞和非阻塞两种方式。

在阻塞模式下,当FIFO中没有数据可读时,读取进程会被阻塞,直到有数据可读为止;当FIFO已满时,写入进程会被阻塞,直到有空间可写为止。

在非阻塞模式下,读取进程和写入进程不会被阻塞,而是会立即返回一个错误码。

FIFO的实现方式可以基于内存或磁盘。

在基于内存的实现方式中,FIFO的数据存储在内核缓冲区中,因此读写速度较快;而在基于磁盘的实现方式中,FIFO 的数据存储在磁盘文件中,因此读写速度较慢。

FIFO的应用场景非常广泛,例如在Linux系统中,FIFO常用于进程间通信、日志记录等方面。

在多线程编程中,FIFO也可以用于线程间通信,实现线程安全的数据传输。

总之,FIFO作为一种先进先出的数据结构,在计算机领域中有着广泛的应用,其读写操作的实现方式和应用场景也非常丰富。

fifo电路结构结构

fifo电路结构结构

FIFO电路结构是一种特殊的存储器结构,主要用于数据的缓存和传输。

FIFO,即First In First Out,意为先入先出,其特性是数据按照进入的顺序依次被读出。

这种特性使得FIFO在数据传输和缓冲中扮演着重要的角色。

FIFO电路结构主要由两部分组成:输入部分和输出部分。

输入部分负责接收数据并将其存储到FIFO中,而输出部分则负责从FIFO中读取数据并将其输出。

这种结构使得数据在FIFO中的流动呈现出一种线性、有序的状态。

在FIFO中,数据的存储和读取都是通过指针来实现的。

指针是一个地址指示器,它指向FIFO中当前要读取或写入的数据的位置。

当数据被写入FIFO时,写指针会向前移动,指向下一个可用的存储位置。

当数据被从FIFO中读取时,读指针会向前移动,指向下一个要读取的数据位置。

由于FIFO的先入先出特性,写指针和读指针的移动方向是一致的,都是从FIFO的一端向另一端移动。

FIFO电路结构有两种主要类型:触发导向结构和零导向传输结构。

触发导向结构的FIFO 由寄存器阵列构成,当满足一定条件时,数据会被写入或读取。

而零导向传输结构的FIFO 则是由具有读和写地址指针的双口RAM构成,数据的读写操作是通过地址指针来完成的。

FIFO电路结构在许多领域都有广泛的应用,如计算机系统中的缓存、数据传输、图像处理等。

由于其先入先出的特性,FIFO能够有效地缓解数据传输和处理过程中的速度不匹配问题,提高系统的整体性能。

异步FIFO及verilog原码

异步FIFO及verilog原码_1异步FIFO及verilog原码这几天看了Clifford E. Cummings的两篇大作《Simulation and Synthesis Techniques for Asynchronous FIFO Design》and 《Simulation and Synthesis Techniques for Asynchronous FIFO Design with Asynchronous Pointer Comparisons》颇有感想,真可谓经典之作,不可错过。

1.什么是FIFO?FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

2.什么情况下用FIFO?FIFO一般用于不同时钟域之间的数据传输,比如FIFO的一端是AD数据采集,另一端是计算机的PCI总线,假设其AD采集的速率为16位100K SPS,那么每秒的数据量为100K×16bit=1.6Mbps,而PCI总线的速度为33MHz,总线宽度32bit,其最大传输速率为1056Mbps,在两个不同的时钟域间就可以采用FIFO来作为数据缓冲。

另外对于不同宽度的数据接口也可以用FIFO,例如单片机位8位数据输出,而DSP可能是16位数据输入,在单片机与DSP连接时就可以使用FIFO来达到数据匹配的目的。

3.FIFO的一些重要参数FIFO的宽度:也就是英文资料里常看到的THE WIDTH,它只的是FIFO一次读写操作的数据位,就像MCU有8位和16位,ARM 32位等等,FIFO的宽度在单片成品IC中是固定的,也有可选择的,如果用FPGA自己实现一个FIFO,其数据位,也就是宽度是可以自己定义的。

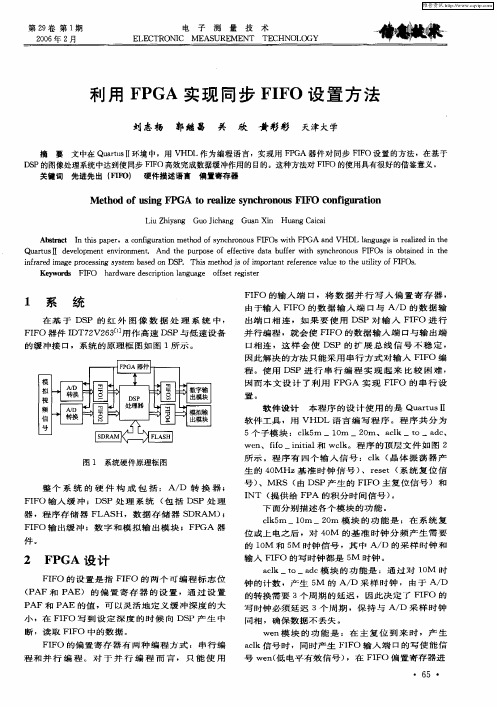

利用FPGA实现同步FIFO设置方法

一

1 m 一2 m 模 块 的 功 能 是 : 在 系 统 复 0 0

位或上 电之后 ,对 4 M 的 基 准 时 钟 分 频 产 生需 要 0 的 1 M 和 5 时 钟 信 号 ,其 中 A/ 的 采 样 时 钟 和 0 M D

2 F PGA 设 计

F F 的 设 置 是 指 FI 的 两 个 可 编 程 标 志 位 IO Fo ( AF 和 P P AE) 的 偏 置 寄 存 器 的 设 置 ,通 过 设 置 P AF 和 PAE 的 值 ,可 以 灵 活 地 定 义 缓 冲 深 度 的 大 小 ,在 F F 写 到 设 定 深 度 的 时 候 向 DS 产 生 中 IO P

Ab ta t I hsp p r ac n iu ain meh do y c r n u I Oswih F GA n sr c nt i a e , o f rt to fs n h o o sF F t P g o a d VHDL a g a ei raie h ln u g s e l d i t e z n

we n、 ff io

—

iiil wck。 程 序 的顶 层 文 件 如 图 2 nta 和 l

图 1 系统硬件 原理 框图

整 个 系 统 的 硬 件 构 成 包 括 : A/ 转 换 器 ; D FI )输 入 缓 冲 ;DS 处 理 系 统 F( P ( 括 DS 处 理 包 P 器 ・程 序 存 储 器 F LAS , 数 据 存 储 器 S H DRAM ); F FO 输 出 缓 冲 ; 数 字 和 模 拟 输 出 模 块 ;FP I GA 器

程 。使 用 DS 进 行 串 行 编 程 实 现 起 来 比 较 困 难 , P 因而 本 文 设 计 了利 用 F PGA 实 现 FI O 的 串 行 设 F

FPGA异步FIFO设计中的问题与解决办法

TECHNOLO GY REVIEW 技术纵横 FPGA异步FIFO设计中的问题与解决办法■太原科技大学 谢文华 高文华 摘 要通过分析异步FIFO的基本结构和工作原理,以降低亚稳态的出现频率、充分利用异步FIFO的内存资源为主要目的,提出一种在FP GA内部实现的异步FIFO设计方法。

本文在传统设计的基础上提出一种新颖的电路结构来准确判断空/满标志位的产生,即检测加计数器的方法;并用QuartusII对其进行仿真,得到了比较好的性能。

关键词异步FIFO 亚稳态 FP GA 随着数字电子系统设计规模的扩大,一些实际应用系统中往往含有多个时钟,数据不可避免地要在不同的时钟域之间传递。

如何在异步时钟之间传输数据,是数据传输中一个至关重要的问题,而采用FIFO正是解决这一问题的有效方法。

异步FIFO是一种在电子系统中得到广泛应用的器件,多数情况下它都是以一个独立芯片的方式在系统中应用。

本文介绍一种充分利用FPG A内部的RAM资源,在FPG A内部实现异步FIFO模块的设计方法。

这种异步FIFO比外部FIFO芯片更能提高系统的稳定性。

1 FIFO的基本结构和工作原理FIFO(First In First Out)是一种采用环形存储结构的先进先出存储器。

其使用一个双端口存储器存放数据,数据发送方在一端写入数据,接收方在另一端读出数据,能够协调好两个时钟域的工作,满足高时钟频率的要求。

FIFO在FP GA设计中主要用来缓冲数据和隔离时钟或相位差异。

访问FIFO时不需要地址线,只需要数据线和读写控制信号线,且数据地址由内部读写指针自动加1完成,因此利用FIFO实现数据的缓存具有接口简单、读写方便的优点。

根据FIFO的工作时钟,可将FIFO分为同步FIFO 和异步FIFO[1]。

同步FIFO是指读时钟和写时钟为同一个时钟,在时钟沿来临时同时进行读写操作;异步FIFO 是指读写时钟不是同一个时钟,而是相互独立的。

verilog fifo原理

verilog fifo原理FIFO(FirstInFirstOut)是一种常用的存储器结构,用于在数据传输过程中暂存数据。

在数字电路和系统设计中,FIFO被广泛应用于数据缓存、接口通信等领域。

本文将介绍VerilogFIFO的基本原理和设计方法。

一、FIFO的结构FIFO通常由输入端、输出端和存储器组成。

输入端和输出端分别对应数据的输入和输出,而存储器则用于暂存数据。

FIFO的读写操作遵循FIFO的先进先出(FIFO)原则,即最早进入FIFO的数据最先被读取。

在Verilog中,可以使用模块(module)和语句(statement)来实现FIFO。

常见的VerilogFIFO结构包括数据寄存器(dataregister)、读写指针(read/writepointer)、存储器单元(memorycell)和控制逻辑(controllogic)等部分。

二、FIFO的工作原理1.读写操作FIFO的读写操作遵循FIFO的基本原则。

在写操作时,新数据被写入存储器;在读操作时,最早进入FIFO的数据最先被读取。

控制逻辑负责管理读写指针,以确保正确的读写操作顺序。

2.缓冲作用FIFO的主要作用是缓冲数据,即在数据传输过程中,将输入端的数据存储到FIFO中,待FIFO满后再从输出端输出数据。

这样可以在一定程度上缓解数据传输的时序问题,提高数据传输的可靠性和效率。

3.溢出和欠流控制当FIFO满时,控制逻辑会停止新的写操作,以避免数据溢出。

同样地,当FIFO空时,控制逻辑会暂停新的读操作,以防止欠流(underflow)现象的发生。

这些控制逻辑的实现通常需要借助状态机(statemachine)和条件语句(conditionstatement)等Verilog语言特性。

以下是一个简单的VerilogFIFO设计示例:modulefifo(inputwireclk,reset,en_write,en_read,outputwire [7:0]data_out);reg[7:0]data_reg[15:0];//数据寄存器regread_pointer,write_pointer;//读写指针integeri;parameterSIZE=16;//FIFO容量//控制逻辑和状态机always@(posedgeclkorposedgereset)beginif(reset)beginread_pointer<=0;//复位时读写指针都归零write_pointer<=0;for(i=0;i<SIZE;i=i+1)begindata_reg[i]<=8'h00;//清空FIFOendendelseif(en_write)begindata_reg[write_pointer]<={data_reg[write_pointer],data_in };//新数据写入FIFOwrite_pointer<=write_pointer+1;//写指针加一if(write_pointer==SIZE)write_pointer<=0;//FIFO满时归零写指针endelseif(en_read)begindata_out<=data_reg[read_pointer];//读出最早进入FIFO的数据read_pointer<=read_pointer+1;//读指针加一if(read_pointer==SIZE)read_pointer<=0;//FIFO空时归零读指针endelsebegin//其他情况不做处理endendendmodule以上示例中,我们使用了一个16位的数据寄存器和两个指针(read_pointer和write_pointer)来管理FIFO的读写操作。

fifo芯片

fifo芯片FIFO(First-In-First-Out)芯片是一种常见的数据缓冲器,用于在数据读取和写入之间进行临时存储和排队操作的集成电路。

它按照数据进入的顺序进行排列,首先进入的数据首先被读取或输出。

FIFO芯片的主要功能是解决输入和输出设备之间速度不匹配的问题。

例如,当一个设备以较快的速度产生数据,而另一个设备以较慢的速度接收数据时,使用FIFO芯片可以临时存储数据并使其按照正确的顺序进行传输。

FIFO芯片通常由读取和写入指针组成,用于指示读取和写入操作的位置。

当数据写入FIFO时,写入指针会自动增加。

当数据被读取或输出时,读取指针会自动增加。

这种方式可以保证数据按照正确的顺序进行读取和输出。

FIFO芯片具有以下特点和优势:1. 数据存储和传输的稳定性:FIFO芯片通过临时存储数据,可以确保数据传输的稳定性和可靠性。

当输入设备和输出设备速度不一致时,FIFO芯片可以自动调整数据的传输速度,避免数据丢失或错误。

2. 简化数据处理:FIFO芯片可以作为缓冲器,存储大量的数据,并且在需要时按照正确的顺序进行传输。

这样可以减轻主处理器的负担,简化数据处理的复杂性。

3. 异步数据传输:FIFO芯片可以实现异步数据传输,不同设备之间的数据传输可以按照各自的节奏进行,不需要进行时钟同步或控制信号的干扰。

4. 灵活性和可扩展性:FIFO芯片可以根据系统需求进行配置和扩展。

可以根据需要选择不同的存储容量,以满足数据处理的要求。

5. 低功耗和高性能:FIFO芯片通常采用CMOS技术制造,具有低功耗和高性能的特点。

因此,在各种电子设备中广泛应用,例如通信设备、计算机、工业自动化等。

总的来说,FIFO芯片作为一种常见的数据缓冲器,可以提供稳定可靠的数据传输和处理功能,解决输入和输出设备之间速度不匹配的问题。

它在现代电子设备中具有重要的应用和意义,促进了数据处理和通信技术的发展。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.什么是FIFO?FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

2.什么情况下用FIFO?FIFO一般用于不同时钟域之间的数据传输,比如FIFO的一端时AD数据采集,另一端时计算机的PCI总线,假设其AD采集的速率为16位 100K SPS,那么每秒的数据量为100K×16bit=1.6Mbps,而PCI总线的速度为33MHz,总线宽度32bit,其最大传输速率为1056Mbps,在两个不同的时钟域间就可以采用FIFO来作为数据缓冲。

另外对于不同宽度的数据接口也可以用FIFO,例如单片机位8位数据输出,而DSP可能是16位数据输入,在单片机与DSP连接时就可以使用FIFO来达到数据匹配的目的。

3.FIFO的一些重要参数FIFO的宽度:也就是英文资料里常看到的THE WIDTH,它只的是FIFO一次读写操作的数据位,就像MCU有8位和16位,ARM 32位等等,FIFO的宽度在单片成品IC中是固定的,也有可选择的,如果用FPGA自己实现一个FIFO,其数据位,也就是宽度是可以自己定义的。

FIFO的深度:THE DEEPTH,它指的是FIFO可以存储多少个N位的数据(如果宽度为N)。

如一个8位的FIFO,若深度为8,它可以存储8个8位的数据,深度为12 ,就可以存储12个8位的数据,FIFO的深度可大可小,个人认为FIFO深度的计算并无一个固定的公式。

在FIFO实际工作中,其数据的满/空标志可以控制数据的继续写入或读出。

在一个具体的应用中也不可能由一些参数算数精确的所需FIFO深度为多少,这在写速度大于读速度的理想状态下是可行的,但在实际中用到的FIFO深度往往要大于计算值。

一般来说根据电路的具体情况,在兼顾系统性能和FIFO成本的情况下估算一个大概的宽度和深度就可以了。

而对于写速度慢于读速度的应用,FIFO的深度要根据读出的数据结构和读出数据的由那些具体的要求来确定。

满标志:FIFO已满或将要满时由FIFO的状态电路送出的一个信号,以阻止FIFO的写操作继续向FIFO中写数据而造成溢出(overflow)。

空标志:FIFO已空或将要空时由FIFO的状态电路送出的一个信号,以阻止FIFO的读操作继续从FIFO中读出数据而造成无效数据的读出(underflow)。

读时钟:读操作所遵循的时钟,在每个时钟沿来临时读数据。

写时钟:写操作所遵循的时钟,在每个时钟沿来临时写数据。

读指针:指向下一个读出地址。

读完后自动加1。

写指针:指向下一个要写入的地址的,写完自动加1。

读写指针其实就是读写的地址,只不过这个地址不能任意选择,而是连续的。

4.FIFO的分类根均FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。

同步FIFO是指读时钟和写时钟为同一个时钟。

在时钟沿来临时同时发生读写操作。

异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

5.FIFO设计的难点FIFO设计的难点在于怎样判断FIFO的空/满状态。

为了保证数据正确的写入或读出,而不发生益处或读空的状态出现,必须保证FIFO在满的情况下,不能进行写操作。

在空的状态下不能进行读操作。

怎样判断FIFO的满/空就成了FIFO设计的核心问题。

由于同步FIFO 几乎很少用到,这里只描述异步FIFO的空/满标志产生问题。

在用到触发器的设计中,不可避免的会遇到亚稳态的问题(关于亚稳态这里不作介绍,可查看相关资料)。

在涉及到触发器的电路中,亚稳态无法彻底消除,只能想办法将其发生的概率将到最低。

其中的一个方法就是使用格雷码。

格雷码在相邻的两个码元之间只由一位变换(二进制码在很多情况下是很多码元在同时变化)。

这就会避免计数器与时钟同步的时候发生亚稳态现象。

但是格雷码有个缺点就是只能定义2^n的深度,而不能像二进制码那样随意的定义FIFO的深度,因为格雷码必须循环一个2^n,否则就不能保证两个相邻码元之间相差一位的条件,因此也就不是真正的各雷码了。

第二就是使用冗余的触发器,假设一个触发器发生亚稳态的概率为P,那么两个及联的触发器发生亚稳态的概率就为P的平方。

但这回导致延时的增加。

亚稳态的发生会使得FIFO出现错误,读/写时钟采样的地址指针会与真实的值之间不同,这就导致写入或读出的地址错误。

由于考虑延时的作用,空/满标志的产生并不一定出现在FIFO真的空/满时才出现。

可能FIFO还未空/满时就出现了空/满标志。

这并没有什么不好,只要保证FIFO不出现overflow or underflow 就OK了。

很多关于FIFO的文章其实讨论的都是空/满标志的不同算法问题。

在Vijay A. Nebhrajani的《异步FIFO结构》一文中,作者提出了两个关于FIFO空/满标志的算法。

第一个算法:构造一个指针宽度为N+1,深度为2^N字节的FIFO(为便方比较将格雷码指针转换为二进制指针)。

当指针的二进制码中最高位不一致而其它N位都相等时,FIFO 为满(在Clifford E. Cummings的文章中以格雷码表示是前两位均不相同,而后两位LSB 相同为满,这与换成二进制表示的MSB不同其他相同为满是一样的)。

当指针完全相等时,FIFO为空。

这也许不容易看出,举个例子说明一下:一个深度为8字节的FIFO怎样工作(使用已转换为二进制的指针)。

FIFO_WIDTH=8,FIFO_DEPTH= 2^N = 8,N = 3,指针宽度为N+1=4。

起初rd_ptr_bin和wr_ptr_bin均为“0000”。

此时FIFO中写入8个字节的数据。

wr_ptr_bin =“1000”,rd_ptr_bin=“0000”。

当然,这就是满条件。

现在,假设执行了8次的读操作,使得rd_ptr_bin =“1000”,这就是空条件。

另外的8次写操作将使wr_ptr_bin 等于“0000”,但rd_ptr_bin 仍然等于“1000”,因此FIFO为满条件。

显然起始指针无需为“0000”。

假设它为“0100”,并且FIFO为空,那么8个字节会使wr_ptr_bin =“1100”,, rd_ptr_bin 仍然为“0100”。

这又说明FIFO为满。

在Vijay A. Nebhrajani的这篇《异步FIFO结构》文章中说明了怎样运用格雷码来设置空满的条件,但没有说清为什么深度为8的FIFO其读写指针要用3+1位的格雷码来实现,而3+1位的格雷码可以表示16位的深度,而真实的FIFO只有8位,这是怎么回事?而这个问题在Clifford E. Cummings的文章中得以解释。

三位格雷码可表示8位的深度,若在加一位最为MSB,则这一位加其他三位组成的格雷码并不代表新的地址,也就是说格雷码的0100表示表示7,而1100仍然表示7,只不过格雷码在经过一个以0位MSB的循环后进入一个以1为MSB的循环,然后又进入一个以0位MSB的循环,其他的三位码仍然是格雷码,但这就带来一个问题,在0100的循环完成后,进入1000,他们之间有两位发生了变换,而不是1位,所以增加一位MSB的做法使得该码在两处:0100~1000,1100~0000有两位码元发生变化,故该码以不是真正的格雷码。

增加的MSB是为了实现空满标志的计算。

Vijay A. Nebhrajani的文章用格雷码转二进制,再转格雷码的情况下提出空满条件,仅过两次转换,而Clifford E. Cummings的文章中直接在格雷码条件下得出空满条件。

其实二者是一样的,只是实现方式不同罢了。

第二种算法:Clifford E. Cummings的文章中提到的STYLE #2。

它将FIFO地址分成了4部分,每部分分别用高两位的MSB 00 、01、 11、 10决定FIFO是否为going full 或going empty (即将满或空)。

如果写指针的高两位MSB小于读指针的高两位MSB则FIFO为“几乎满”,若写指针的高两位MSB大于读指针的高两位MSB则FIFO为“几乎空”。

在Vijay A. Nebhrajani的《异步FIFO结构》第三部分的文章中也提到了一种方法,那就是方向标志与门限。

设定了FIFO容量的75%作为上限,设定FIFO容量的25%为下限。

当方向标志超过门限便输出满/空标志,这与Clifford E. Cummings的文章中提到的STYLE #2可谓是异曲同工。

他们都属于保守的空满判断。

其实这时输出空满标志FIFO并不一定真的空/满。

说到此,我们已经清楚地看到,FIFO设计最关键的就是产生空/满标志的算法的不同产生了不同的FIFO。

但无论是精确的空满还是保守的空满都是为了保证FIFO工作的可靠。

6.关于FIFO的一点的思考关于FIFO丢数据的问题,其实各位对同一个问题的理解有偏差,才造成了相互误解。

如果在理想状况下(时钟同步不回出现错码),FIFO由读写指针控制是不会丢数的,(这不是废话吗,现实中哪来的理想状况!)且慢,我的意思是说丢数据并不是读写谁快谁慢造成的,在正确的设置空满标志算法的情况下,数据overflow 和underflow 是不会发生的。

而往往现实中因为亚稳态的存在,才出现了丢数的情况,也就是说是只要读写时钟不同步,在采样的过程中采样出错,使得本该是0100的变成了1101等等,就会出现读写的错误,我们称其为丢数,其原因就是在时钟同步指针的时候出现亚稳态,由于二进制码加1的时候很多位同时变化,所以很容易出现亚稳态。

因此才用格雷码将此问题发生的概率比降到最小,其次用多余的触发器使其概率进一步降低,也就是说错误难免,但我们可以将其发生的概率降到最低,并且在出现错误时也不会错的态离谱(详见Vijay A. Nebhrajani的《异步FIFO 结构》第二篇)。

二进制码指针并非不好用,在前面也提到了它有自身的优势,由于通过设置握手信号,指针可以有多位同时变化,二进制指针每次移动可以跳跃过任意的长度,这样给FIFO的某些功能的实现带来了方便(例如,硬件直接控制FIFO从缓存的数据流中丢弃一个出错的包);而格雷码指针一般只能做递增或递减的移动。

设置握手信号虽然可以保证指针不出错,但这样你来我往的经过三四个回合才能开始传数据,所以对于高速的场合就不适用了。