第十讲 8086 8088 CPU 中断

8086-6-中断

8086-6-中断中断(8086)中断就是打断处理器当前的执⾏流程,去执⾏⼀些和当前⼯作不相⼲的指令,执⾏完之后,还可以返回到原来的程序流程继续执⾏。

就好⽐你在打游戏突然⽼板来电话了,你不得不先停⽌打游戏然后来处理这件更为重要的事件,然后打完电话之后继续打游戏。

中断的⼀些概念:中断号:由于CPU需要通过对不同类型的中断进⾏不同处理,所以每种类型的中断都被统⼀编号,这称为中断类型号、中断向量或者中断号。

Intel处理器允许256 个中断,中断号的范围是0~255中断源:中断信号的来源,或者说产⽣中断的设备,被称为中断源。

中断嵌套:当⼀个中断事件正在处理时,如果来了⼀个优先级更⾼的中断事件时,允许暂时中⽌当前的中断处理,先为优先级较⾼的中断事件服务,这称为中断嵌套。

实模式下的中断向量表(Interrupt Vector Table,IVT):所谓中断处理,其实就是处理器要执⾏⼀段与该中断有关的程序(指令)你也可以将其当作⼀个函数。

处理器可以识别256 个中断,那么理论上就需要256 段代码。

这些代码实际存放的位置并不重要,重要的是,在实模式下,处理器要求将它们的⼊⼝点也就是起始地址集中存放到内存中从物理地址0x00000 开始,到0x003ff 结束,共1KB 的空间内,这就是所谓的中断向量表。

每个中断的⼊⼝点地址在中断向量表中占2 个字,分别是中断处理代码的偏移地址和段地址。

中断0的⼊⼝点位于物理地址0x00000 处,也就是逻辑地址0x0000:0x0000;中断1 的⼊⼝点位于物理地址0x00004 处,即逻辑地址0x0000:0x0004;其他中断⼊⼝点地址以此类推。

中断分类:中断⼤致上可以分为硬件中断和软件中断(简称为软中断)。

顾名思义,硬件中断由硬件来提供,⽐如说:CPU,⿏标键盘等。

⽽软件键盘由内部的代码来定义。

硬件中断:硬件中断还可以分为外部硬件中断和内部硬件中断,外部硬件中断是指除CPU以外的硬件对应的中断,⽽内部硬件中断是内部CPU对应的中断。

第3章 8086 8088指令系统

字节2

6 5 4 3 2 1 0 7· · · 0 7· · · · ·0 7· · · · · 0 7· · · · · 0 DISPH DATAL DATAH

OP code

D w MOD REG R/M DISPL

操作码字节 寻址方式字节 位移量 立即数 •OP code为操作码,表示该指令要完成的操作。 为操作码, OP code为操作码 表示该指令要完成的操作。 •D=0:第一个操作数是目的操作数, 1:第二个操作数是目的操作数 D=0: 是目的操作数, 第二个操作数是目的操作数 D=0 第一个操作数是目的操作数 •W=0:8位操作数, 1:16位操作数 W=0: 位操作数, 16位操作数 W=0 •MOD指明寻址方式: MOD=11 寄存器寻址 MOD指明寻址方式 MOD指明寻址方式: MOD= MOD≠11存储器寻址 MOD≠11存储器寻址 00没有偏移量 1016 16位偏移量 00没有偏移量 01 8位偏移量 1016位偏移量 •REG用编码方式指明操作中所使用的寄存器。 REG用编码方式指明操作中所使用的寄存器 REG用编码方式指明操作中所使用的寄存器。 •R/M用编码方式指出存储器有效地址计算方法。 R/M用编码方式指出存储器有效地址计算方法 R/M用编码方式指出存储器有效地址计算方法。 •DISP表示地址偏移量。DATA则指明立即数。 DISP表示地址偏移量 则指明立即数。 DISP表示地址偏移量。DATA则指明立即数

DATA

操作码 00 02

DS : 80000 BX: 1000 DI: + 2000 DATA: + 0200 83200H

AX 30 40

码 段

40 30

83200 83201

数 据 段

第03-1章. 80868088微处理器及其系统

3.1.1、8086/8088CPU的内部结构

执行单元( Execute Unit ) 总线接口单元 ( Bus Interface Unit )

8088的内部结构

AH BH CH DH AL BL CL DL SP BP SI DI

16位

地址 加法 器

∑

20位

通用 寄存器

CS DS SS ES IP 内部暂存器

PA的书写方式:

段地址:段内偏移

如:1121H : 2200H=11210+2200=13410H

已知CS=1055H,DS=250AH,ES=2EF0H, SS=8FF0H,DS段有一操作数,其偏移地址=0204H, 1)画出各段在内存中的分布 2)指出各段首地址 10550H CS 3)该操作数的物理地址=?

2.地址加法器和段寄存器

BIU中的地址加法器用来实现逻辑地址到物理地址的变换 8086采用了 “段加偏移”的技术。

15 0 15 0

逻辑地址

段基值

3 0

偏移量

0000

各段寄存器分别来存放确定各段的 起始地址的16位段地址信息

寻址单元的16位偏移地址

Σ

19 0

物理地址

物理地址

左移4位后的段寄存器的内容同时 送到地址加法器进行相加

CH DH CL DL

地址 加法 器

∑

20位

CS DS SS ES IP 内部暂存器

16位

输入/输出 控制电路 外 部 总 线

1 2

8位

3 4

把EU的操作结果存储 标志寄存器 到指定的M或I/O口。

执行部件 (EU)

指令队列

总线接口部件 (BIU)

8086中断和-存储器习题PPT课件

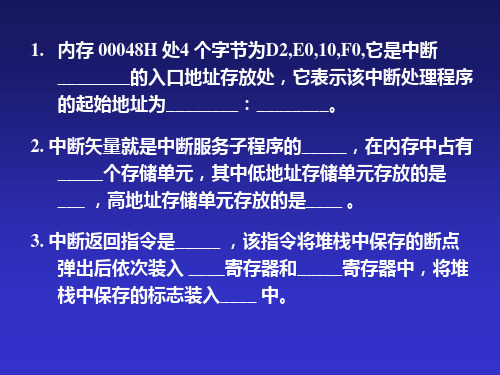

7. 8086CPU的每个中断向量占____个字节

8. 非屏蔽中断的中断类型号是________ 9. 中断类型号为______的中断向量存储在以0000:0070H

地址开始的连续4 个单元中。

10. 中断类型号为 1CH 的中断向量存储在以 __________ 地址开始的连续4 个单元中。

8086如何响应一个可屏蔽中断请求?简述响应过程。

答:当8086收到INTR的高电平信号时,在当前指令执行 完且IF=1的条件下,8086在两个总线周期中分别发出 INTA#有效信号;

在第二个INTA#期间,8086收到中断源发来的一字节 中断类型码;

8086完成保护现场的操作,CS、IP内容进入堆栈,请 除IF、TF;

3. 中断返回指令是_____ ,该指令将堆栈中保存的断点 弹出后依次装入 ____寄存器和_____寄存器中,将堆 栈中保存的标志装入____ 中。

4. 8086中断分为_____和_____两类。8086可处理____ 种中断。

5. 中断处理子程序的入口地址存储在内存的存放区域 为_______

假如此时内存的存放情况 如图所示,则此中断对应 的中断处理子程序的入 口地址CS:IP分别为?

15H 0000FH

20H 0000EH 13H 0000DH 58H 0000CH 24H 0000BH 6AH 0000AH

1.8086可屏蔽中断请求输入线是什么?“可屏蔽” 的涵义是什么?

答:可屏蔽中断请求输入线为INTR;“可屏蔽”是 指该请求可经软件清除标志寄存器中IF位而被禁止。

总线提供给CPU的,可以改变。

第2章-8086 8088微处理器

大多数算术和逻辑运算指令都可以使用这些数据寄 存器。

17

通用寄存器

指针寄存器和变址寄存器

用于堆栈操作

SP (Stack Pointer), BP (Base Pointer), SI (Source Index), DI (Destination Index)

NUIST

第2章 8086/8088 微处理器

教学目标

掌握微处理器的内部功能结构组成。 理解和掌握微处理器的寄存器结构,明确各寄 存器的用法。 理解“段加偏移”的存储器寻址方法,掌握 物理地址和逻辑地址的关系。 掌握微处理器的总线周期的概念,理解微机 系统在时序作用下的工作过程。

2

主要内容

1 8086/8088微处理器特点 2 8086/8088微处理器结构 3 8086/8088 CPU工作模式和引脚 4 8086的总线时序

CX,DX • 堆栈指针寄存器SP(16位) • 基址指针寄存器BP(16位) • 目的变址寄存器DI(16位) • 源变址寄存器SI(16位)

11

指令执行部件EU(Execution Unit)

通用 寄存器

AH BH CH

AL BL CL

DH DL

指针 SP

和变址 BP 寄存器 DI

SI

AX BX CX DX

FLAGS IP

目的变址寄存器 变址寄存器 源变址寄存器

基址指针寄存器 栈指针寄存器

指针寄存器 CS

标志寄存器 指令指针寄存器

DS SS ES

16

通Hale Waihona Puke 寄存器代码段寄存器 数据段寄存器 堆栈段寄存器 附加段寄存器

第3章 8086(8088)CPU指令系统

20H 00H

00H 34H 12H

3000H:0000H

注: ◆基址因子BP访问默认为堆栈段 ◆不能同时取两个基址因子;也不 能同时去两个变址因子

16

+

3000H:3000H

AH

AL

第3章 8086/8088CPU指令系统

4.1.4 操作数寻址方式

●存储器寻址之相对基址加变址寻址(Base

9

第3章 8086/8088CPU指令系统

3.1.3 操作数寻址方式

4.1操作数寻址方式

所谓操作数的寻址方式,是在指令格式中怎样有效的表示出操 作数的存放位臵,CPU在执行该指令时,按照指令格式中的表示找 到并对数据进行存取。 1.立即寻址(Immediate Addressing) 立即寻址中的操作数作为指令的一 部分存放在代码段中,在取指阶段数据 随指令一起被取到CPU,这种数据在指 令格式中的直接表现为常数。 如:MOV AL,34H

2

第3章 8086/8088CPU指令系统

汇编语言指令或符号指令:用字母和其它一些符 号组成的“助记符”与操作数等表示的指令称为汇编 语言指令或符号指令。 例如: MOV AX, BX ; AX←BX 而其二进制代码(机器代码)为89D8H,就是 1000 1001 1101 1000 B 不易理解,不易记忆。助记符是MOV。

操作码

操作数

4

第3章 8086/8088CPU指令系统

3.1.1 8086/8088指令格式

4.1操作数寻址方式

8086/8088机器指令格式通常1-6个字节组成。典型的指令格式 由2个字节组成,如下图所示。

操作码 D W MOD REG R/M

第4章 8086,88汇编语言程序设计

第4章 8086/8088汇编语言程序设计

本章主要讲述8086/8088微处理器的

汇编语言源程序的结构

汇编语言语句格式

伪指令

汇编语言程序设计方法 DOS和BIOS功能调用 软件调试方法

19

汇 编 语 言 程 序 设 计

8086/8088

4.1 程序设计语言概述 4.2 8086/8088汇编语言的 基本语法 4.3 8086/8088汇编语言程序 设计基本方法 4.4 软件调试技术

23

汇编语言程序的上机与处理过程

编辑程序 edit.exe

prog.asm 文件

汇编程序 masm.exe

prog.obj 文件

prog.exe 文件

连接程序

link.exe

24

第一步:汇编

汇编源程序需翻译成机器语言,变成可执行文件,机器才能 执行,这个翻译过程叫汇编。 高级语言中称该过程为‚解释‛或‚编译‛。执行翻译的程 序称为‚汇编程序‛。 汇编程序分两种,一种是基本汇编(ASM.EXE),一种是 宏汇编(MASM.EXE),宏汇编功能比较强。

003ffh

CS IP CS IP 00004 00002

1KB

00000h

5

返回断点 中断服务程序结束时执行中断返回指令 IRET:使IP、CS、PSW按顺序出栈。 …… …… …… …… CPU返回断点继续执行后续程序

如:INT 2AH,类型号为2AH,为获取它的中断服务程 序入口地址在向量表中存放的首地址,需将类型号*4。 1)2AH=0010 1010B;化成二进制数 2)0010 1010 00B=1010 1000B;左移2位 中断服务程序入口地址在向量表中存放的首地址即为: 000A8H。

第2章8086、8088CPU体系结构

Intel 8282

具有三态输出的 TTL电平锁存器 STB 电平锁存引脚 OE* 输出允许引脚

每一位都是一个三态锁存器, 8个三态锁存器的控制端连在一起

74LS373

具有三态输出的 TTL电平锁存器 LE 电平锁存引脚 OE* 输出允许引脚

74LS373与Intel 8282功能一样

以Intel8086/8088、Z8000和MC68000 为代表的16位微处理器是第3代产品,以它们 为核心部件组成的微机系统,其性能已达到中、 高档小型计算机的水平。20多年来,Intel系 列CPU一直占着主导地位。尽管8086/8088后 续的80286、80386、80486以及Pentium系列 CPU结构与功能已经发生很大变化,但从基本 概念与结构以及指令格式上来讲,它们仍然是 经典的8086/8088CPU的延续与提升。并且, 其他系列流行的CPU(如AMD公司的6X86MX/MⅡ 等)也与80x86CPU兼容。

补充:三态门和D触发器

• 三态门和以D触发器形成的锁存器是微机 接口电路中最常使用的两类逻辑电路 • 三态门:功率放大、导通开关 • 器件共用总线时,一般使用三态电路:

– 需要使用总线的时候打开三态门; – 不使用的时候关闭三态门,使之处于高阻

• D触发器:信号保持,也可用作导通开关

三态

锁存

三态缓冲器(三态门)

具有单向导通和三态的特性

A T

A T F A T

F

T为低平时: 输出为高阻抗(三态) T为高电平时: 输出为输入的反相

F

A

T

F

表示反相或低电平有效

74LS244

双4位单向缓冲器 • 分成4位的两组 • 每组的控制端连 接在一起 • 控制端低电平有 效 • 输出与入同相

微型计算机原理及应用教程第3章 8088 8086MPU的指令系统

3.1.2 指令的分类

从用到的操作数个数区分,可能有如下4种情况:

1.无操作数指令

有的指令不涉及操作数,或使用约定的某个(些)操作 数,既已约定则没有必要再在指令中加以表示,称这类指令 为无操作数指令,它仅有操作码部分,例如停机指令、空操 作指令、关中断指令、堆栈结构的计算机系统中对堆栈中数

据运算的指令等。

的操作数(如被加数、被减数等)和保存计算结果都使用唯

一的那个累加器,指令中只需表示另一个源操作数即可。称 这类指令为单操作数指令。.3 Nhomakorabea双操作数指令

对于常用的算术和逻辑运算指令,往往要求使用两个操

作数,一个叫做原操作数/地址,另一个叫做目的操作数/地

址,需分别给出目的操作数和源操作数的地址,其中目的操 作数地址还用于保存本次的运算结果。称这类指令为双操作 数指令。

3.1 指令与指令系统

要确定一台计算机的指令系统并评价其优劣,通常应从如下4个方 面考虑: 1、指令系统的完备性,常用指令齐全,编程方便。 2、指令系统的高效性,程序占内存空间少,运行速度快。

3、指令系统的规整性,指令和数据使用规则统一简单,易学易记。

4、指令系统的兼容性,同一系列的低档计算机的程序能在高档机 上直接运行。

否是读、写内存或读、写外设操作功能,是否是程序转移和子程序调用

或返回操作功能等,计算机需要为每条指令分配一个确定的操作码。 第二部分,是指令的操作数 opd/ 地址 addr ,用于给出被操作的信

息(数据)或操作数的地址,包括参加运算的一或多个操作数所在的地

址,运算结果的保存地址,程序的转移地址、被调用的子程序的入口地 址等。

操作数也可以存放在存储器中,这种寻址方式叫做存储器寻址, 存储器寻址的关键是如何给出存储器的地址,给出方式不同,寻址方式 也有多种。 1.直接寻址方式:指令中给出操作数所在存储单元的偏移地址

80868088CPU寄存器组

80868088CPU寄存器组今天来回顾⼀下8086/8088 CPU寄存器组的知识。

其实8086汇编还是很久以前学过的,Win32汇编也接触过⼀些,但是由于长时间不碰,⽣疏了不少。

今后可以花点时间总结总结,梳理⼀下以前学习过的知识,尽管暂时还⽤不上,但这样就便于以后需要⽤到的时候很容易捡起来。

我知道博客园⾥⼤多数⼈都是搞Web或者⼿机开发的,相信⽤汇编的⼈也不多,不过⼯作之余学⼀学汇编,了解⼀些计算机底层的知识,对⾃⼰的“⾝⼼”是有帮助的。

希望⾃⼰能坚持把8086汇编完整地写完,如果有精⼒还可以写⼀写win32汇编。

这⼀节先从8086/8088 CPU寄存器组开始说起。

说到8086/8088 CPU寄存器组,它们的特点就是都是16位的,不论是通⽤寄存器、段寄存器还是标志寄存器。

8086/8088包括四个16位数据寄存器,两个16位指针寄存器,两个16位变址寄存器,⼀个16位指令指针寄存器,四个16位段寄存器,⼀个16位标志寄存器。

总共有14个寄存器,这14个寄存器分成四组。

我从《80x86汇编语⾔程序设计教程》电⼦版上截了⼀张图,它描绘了这14个寄存器的名称和分组情况。

通⽤寄存器何谓通⽤寄存器,简单来说就是经常⽤到的寄存器。

按照上图我们不难发现,数据寄存器、指针寄存器和变址寄存器统称为通⽤寄存器。

这些寄存器除了各⾃规定的专门⽤途外,它们均可⽤于传送和暂存数据,可以保存算术逻辑运算中的操作数和运算结果。

数据寄存器数据寄存器主要⽤来保存操作数或运算结果等信息,它们的存在节省了为存取操作数所需占⽤总线和访问存储器的时间。

四个16位的数据寄存器均可分解成⼋个独⽴的8位寄存器,这⼋个8位的寄存器有各⾃的名称,均可独⽴存取。

⽐如:AX寄存器可以分解为AH寄存器和AL寄存器,其中AH寄存器就是AX寄存器的⾼8位,AL寄存器就是AX寄存器的低8位。

其他寄存器类推。

这四个数据寄存器除了它们通⽤的功能以外,还有其他专门的⽤途。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• 开中断(STI)

• 进行中断处理

• 恢复现场(POP reg’s)

• 中断返回(IRET)

18

5)中断返回

▪ 执行中断返回指令IRET

• IRET指令将使CPU把堆栈内保存的断点信息弹 出到IP、CS和FLAG中,保证被中断的程序从断 点处能够继续往下执行。

SP

进入中断服 务程序时

IPL IPH CSL CSH FLAGL FLAGH

≥1 INTAout

15

3)中断响应

▪ 在每条指令的最后一个时钟周期,CPU检测 INTR或NMI信号。若以下条件成立,则CPU 响应中断:

• 当前指令执行完。

▪ 对INTR,还应满足以下条件 • 当前指令是STI和IRET,则下条指令也要执行完。 • 当前指令带有LOCK、REP等指令前缀时,则把它们看成一

定时时间到等

▪ 中断源分为:外部中断、内部中断

5

中断源

▪ 8086/8088的外部中断信号:INTR、NMI

• INTR——可屏蔽中断请求,高电平有效,受IF标 志的控制。

• NMI——非屏蔽中断请求,上升沿有效,任何时 候CPU都要响应此中断请求信号。

6

中断过程

▪ 五个步骤:

• 中断请求 • 中断判优(有时还要进行中断源识别) • 中断响应 • 中断服务 • 中断返回

9

2.2)中断判优

▪ 多个中断源产生中断,CPU首先为谁服务?

——中断优先级排队问题。

▪ 中断优先级控制要处理两种情况:

• 对同时产生的中断:应首先处理优先级别较高的 中断;若优先级别相同,则按先来先服务的原则 处理;

• 对非同时产生的中断:低优先级别的中断处理程 序允许被高优先级别的中断源所中断——即允许 中断嵌套。

• 外部中断

▪ 非屏蔽中断NMI:类型号2,不可用软件屏蔽,CPU必须响应它。 ▪ 可屏蔽中断INTR:类型号由PIC提供。IF=1时CPU才能响应。

中断返回后

SP

IPL IPH CSL CSH FLAGL FLAGH

IP CS FLAG

19

8086/8088的中断系统

▪ 与中断有关的控制线为:NMI、INTR、INTA

▪ 8086系统的中断源(256个)

• 内部中断

▪ 软件中断:即INT n指令,类型号n(0-255)。 • 除法溢出:类型号0,商大于目的操作数所能表达的范围时产生。 • 单步中断:类型号1,TF=1时产生(当前指令需执行完) • 断点中断:类型号3,这是一个软件中断,即INT 3指令。 • 溢出中断:类型号4,这是一个软件中断,即INTO指令。

(I/O接口) n→ PIC → CPU

1

8

2.1)中断源识别

▪ 计算机中的中断源有很多,CPU必须识别是 哪一个设备产生中断。识别中断源有两个方 法:

• 软件查询。将中断信号从数据总线读入,用程序 进行判别。

• 中断矢量法。由中断源提供中断类型号,CPU根 据类型确定中断源。(8086/8088)

外设3

外设接口1

外设接口2

外设接口3

中断确认

IREQ 中断确认

IREQ 中断确认

IREQ

INTAin

菊花链 逻辑电路

INTAin

菊花链 逻辑电路

INTAin

菊花链 逻辑电路

INTR

≥1

┇

14

菊花链逻辑电路

三态门

DB

E

中断确认 &

=1 INTAin

INTR

外设接口

中 断 向 量 码

菊花链 逻辑电路

IREQ

10

中断判优

▪ 中断优先级的控制方法

• 硬件判优——链式判优、并行判优(中断向量法) • 软件判优——顺序查询中断请求,先查询的先服

务(即先查询的优先级别高)

▪ 通常将中断判优与中断源识别合并在一起进 行处理。

• x86系统中,这项任务由PIC和CPU共同完成。

11

软件判优

A1: 结束后能返回被中断的程序。 • 获得中断服务程序首地址(入口)。

如何得到中断处理程序的首地址? ▪ 固定入口法 ▪ 中断向量法——常用

17

4)中断处理(中断服务)

▪ 中断服务子程序特点

• 为”远”过程(类型为FAR)

• 要用IRET指令返回

▪ 中断服务子程序要做的工作

• 保护现场(PUSH reg’s)

IN AL, PORT_R ; PORT_R是锁存器地址

CLC

RCR AL, 1

JC INTS01

; 转向故障处理

RCR AL, 1

JC INTS02

; 转向告警处理

……

……

……

JMP

A1

……

JMP

A2

……

12

硬件优先权排队电路

13

硬件优先权排队-----链式判优电路原理图

CPU

INTA

外设1

外设2

第10讲 中断系统

苏放 sufang@ 北京邮电大学 信息与通信工程学院

1

中断的基本概念

▪ 什么是中断? CPU

外 发申请

设

发申请

中断服务程 序

中断服务程 序

2

中断的定义

▪ CPU执行程序时,由于发生了某种随机 的事件(外部或内部),引起CPU暂时中断 正在运行的程序,转去执行一段特殊的 服务程序(中断服务子程序或中断处理程 序),以处理该事件,该事件处理完后又 返回被中断的程序继续执行,这一过程 称为中断。

3

为何要引入中断?

▪ 提高数据传输率; ▪ 避免了CPU不断检测外设状态的过程,提

高了CPU的利用率。 ▪ 实现对特殊事件的实时响应。如多任务系统

操作系统中:

• 缺页中断 • 设备中断 • 各类异常 • 实时钟,。。。等

4

中断源

▪ 引起CPU中断的事件——中断源。

• 外设——请求输入输出数据,报告故障等 • 事件——掉电、硬件故障、软件错误、非法操作、

个整体,要求完整地执行完;

• 对INTR,CPU应处于开中断状态,即IF=1; • 当前没有复位(RESET)和保持(HOLD)信号。

▪ 若NMI和 INTR 同时发生,则首先响应NMI。

16

3)中断响应(续)

▪ CPU中断响应时,要做下述三项工作:

• 向中断源发出INTA中断响应信号; • 断点保护,包括CS、IP和PSW(FLAGS)。这

7

1)中断请求

▪ 外设接口(中断源)发出中断请求信号,送到CPU 的INTR或NMI引脚;

• 中断请求信号:边沿请求,电平请求 例如,NMI为边沿请求,INTR为电平请求

▪ 中断请求信号应保持到中断被处理为止; ▪ CPU响应中断后,中断请求信号应及时撤销。

• 在8086/8088系统中,外设的中断要经过8259A可编程 中断控制器(PIC)的排队判优后向CPU发出: