基于fpga的多速率滤波器的设计与实现

基于FPGA的多速率信号处理系统的设计

基于FPGA的多速率信号处理系统的设计徐涛【摘要】多速率信号处理系统是数字上变频处理的核心技术之一.多速率信号处理技术在解决匹配信号数据速率和保持传输信号波形有着明显优势.本文介绍一种利用基带成形滤波器和多级半带插值滤波器组成的多速率信号处理系统.通过FPGA 设计系统,利用modelsim仿真验证系统,得出结论,设计的多速率信号处理系统满足信号速率匹配和保持传输信号波形的设计要求.%Multi-rate signal processing system is one of the core technology of digital up conversion processing. Multi-rate signal processing techniques in solving the match signal data rate and maintaining the transmission signal waveform has obvious advantages. This paper describes a multi-rate signal processing system which uses baseband shaping filter and multi-level half-band interpolation filter. By FPGA design system, using modelsim simulation system, concluded that, multi-rate signal processing satisfies systems signaling rate matching and maintain the transmission signal waveform.【期刊名称】《电子设计工程》【年(卷),期】2017(025)010【总页数】4页(P170-173)【关键词】多速率信号处理;基带成形滤波器;半带滤波器;FPGA【作者】徐涛【作者单位】北京化工大学信息科学与技术学院,北京 100029【正文语种】中文【中图分类】TN713多速率信号处理技术是上世纪70年代提出的,该技术是数字信号处理领域的重要研究方向,尤其是在软件无线电的数字中频处理中有着广泛应用[1-2]。

基于FPGA的高速FIR数字滤波器的设计

基于FPGA的高速FIR数字滤波器的设计目前FIR的实现办法主要有3种:利用单片通用数字滤波器、器件和可编程规律器件实现。

单片通用数字滤波器用法便利,但因为字长和阶数的规格较少,不能彻低满足实际需要。

用法DSP器件实现虽然容易,但因为程序挨次执行,执行速度必定不快。

有着规整的内部规律阵列和丰盛的连线资源,特殊适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好。

但长久以来,FPGA向来被用于系统规律或时序控制上,很少有信号处理方面的应用,其缘由主要是由于在FPGA中缺乏实现乘法运算的有效结构。

本文利用FPGA乘累加的迅速算法,可以设计出高速的FIR数字滤波器,使FPGA在数字信号处理方面有了长足的进展。

2 Matlab设计滤波器参数

利用Matlab为设计FIR滤波器提供的工具箱,挑选滤波器类型为低通FIR,设计办法为窗口法,阶数为16,窗口类型为Hamming,Beta为0.5,Fs为8.6 kHz,FC为3.4 kHz,导出的滤波器系数如下:

3 迅速FIR滤波器算法的基本原理

(1) 分布式算法

分布式算法在完成乘加功能时是通过将各输入数据每一对应位产生的部分积预先相加形成相应的部分积,然后再对各部分积举行累加得到终于结果。

对于一个N(N为偶数)阶线性相位FIR数字滤波器,输出可由式(1)表示:

(2) 乘法器设计

高性能乘法器是实现高性能的FIR运算的关键,分析乘法器的运算过

第1页共6页。

CIC插值滤波器的FPGA设计与实现

CIC插值滤波器的FPGA设计与实现摘要:基于多速率信号处理原理,设计了用于下变频的CIC插值滤波器,由于CIC 滤波器结构只用到加法器和延迟器,没有乘法器,很适合用FPGA来实现,所以本文分析了CIC滤波器的原理,性能及影响参数,借助MATLAB设计符合系统要求CIC 滤波器,并利用Modelsim软件建模仿真,验证CIC滤波器性能是否达到要求。

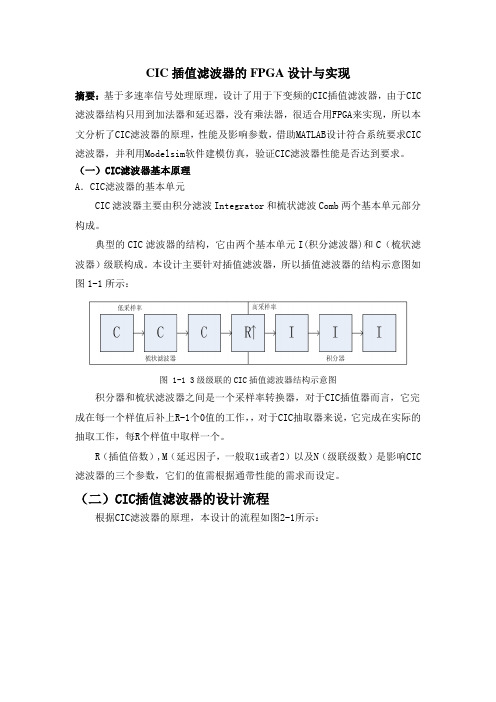

(一)CIC滤波器基本原理A.CIC滤波器的基本单元CIC滤波器主要由积分滤波Integrator和梳状滤波Comb两个基本单元部分构成。

典型的CIC滤波器的结构,它由两个基本单元I(积分滤波器)和C(梳状滤波器)级联构成。

本设计主要针对插值滤波器,所以插值滤波器的结构示意图如图1-1所示:图 1-1 3级级联的CIC插值滤波器结构示意图积分器和梳状滤波器之间是一个采样率转换器,对于CIC插值器而言,它完成在每一个样值后补上R-1个0值的工作,,对于CIC抽取器来说,它完成在实际的抽取工作,每R个样值中取样一个。

R(插值倍数),M(延迟因子,一般取1或者2)以及N(级联级数)是影响CIC 滤波器的三个参数,它们的值需根据通带性能的需求而设定。

(二)CIC插值滤波器的设计流程根据CIC滤波器的原理,本设计的流程如图2-1所示:图2-1 CIC 插值滤波器的设计流程图(三)模型的建立和测试A .位宽策略对于数字滤波器,一个不得不考虑的问题是为防止溢出每一级所需的位宽。

对于抽取器来说,CIC 滤波器的输出增益为(*)NG R M = (3-1)所以,在全精度的情况下,最后一级输出的位宽为2log (*)out in B B N R M =+ (3-2)其中in B 表示输入数据的宽度,为了保证精度,每一个积分器和梳状滤波器的输入输出位宽都为out B 。

对于插值器而言,输出增益为212,1,2,....2(*)/,1, 2......2i i N i N i N G R M R i N N N --⎛⎫== ⎪ ⎪=++⎝⎭ (3-3)因此,第i 级为避免溢出所需要的位宽为2log ()i in i W B G =+ (3-4)最后一级输出位宽为22log (*)log out in B B N R M R =+- (3-5)在实际当中,当差分延时M=1时,为保证稳定,所有积分器的位宽在理论值的基础上加一。

FPGA数字滤波器设计方案与实现

封面作者:PanHongliang仅供个人学习基于FPGA的数字滤波器的设计与实现来源:现代电子技术作者:齐海兵刘雄飞等在信息信号处理过程中,如对信号的过滤、检测、预测等,都要使用到滤波器,数字滤波器是数字信号处理中使用最广泛的一种方法,常用的数字滤波器有无限长单位脉冲响应(IIR)滤波器和有限长单位脉冲响应(FIR)滤波器两种[1]。

对于应用设计者,由于开发速度和效率的要求很高,短期内不可能全面了解数字滤波器相关的优化技术,需要花费很大的精力才能使设计出的滤波器在速度、资源利用、性能上趋于较优。

而采用调试好的IP核需要向Altera公司购买。

本文采用了一种基于DSP Builder的FPGA设计方法,以一个低通的16阶FIR滤波器的实现为例,通过生成的滤波器顶层模块文件与A/D模块文件设计,在联星科技的NC-EDA-2000C实验箱上验证了利用该方法设计的数字滤波器电路工作正确可靠,能满足设计要求。

1、FIR滤波器的参数设计1.1 设计要求数字滤波器实际上是一个采用有限精度算法实现的线性非时变离散系统,它的设计步骤为先根据需要确定其性能指标,设计一个系统函数H(z)逼近所需要的技术指标,最后采用有限精度算法实现。

本系统的设计指标为:设计一个16阶的低通FIR滤波器,对模拟信号的采样频率Fs为48KHz,要求信号的截止频率Fc=10.8kHz,输入序列为宽为9位(最宽位为符号位)。

1.2 FIR滤波器的参数选取设计频率选择性数字滤波器时,通常希望能有近似恒定的频响幅度,并尽量减小通带内的相位失真,斜率为整数的线性相位对应于时域中简单的延时,他在频域中可将相位失真降低到最小的程度[2],用Matlab提供的滤波器设计的专门工具箱--FDAtool仿真设计滤波器,满足要求的FIR滤波器幅频特性,如图1所示。

2、数字滤波器的DSP Builder设计2.1 DSP Builder介绍DSP Builer是Altera推出的一个数字信号处理(DSP)开发工具,他在Quartus II FPGA设计环境中集成了Mathworks的Matlab和Simulink DSP开发软件[3]。

课程设计报告基于FPGA的FIR滤波器设计

目录1 概述 (3)2 课程设计要求及注意事项 (4)3 课程设计内容 (5)3.1 课程设计题目及要求 (5)3.1.1 设计题目 (5)3.1.2 设计要求 (5)3.1.3 设计指标 (5)3.2 课程设计内容 (6)3.2.1 数字滤波器简介 (6)3.2.2 FIR滤波器的基本结构 (7)3.2.3 数字滤波器的设计原理 (8)3.2.4 滤波器的性能指标 (9)3.2.5 FIR数字滤波器的设计方法 (10)4 基于FPGA的FIR滤波器设计 (12)4.1 基于Matlab的FIR数字低通滤波器抽头系数的提取 (12)4.1.1 滤波器的具体设计方法 (12)4.1.2 参数提取与量化 (14)4.2 FIR滤波器的FPGA实现 (15)4.2.1 FIR数字滤波器的实现方法 (15)4.2.2 模块划分 (18)14.2.3 FIR滤波器各模块的实现 (20)4.2.4 FIR滤波器的顶层设计 (35)4.3 FIR滤波器的系统仿真验证 (36)5 教学教材与参考文献 (39)21 概述为了帮助学生深入理解和消化基本理论、进一步提高综合应用能力并且锻炼独立解决问题的能力,电子系统设计方向老师将《数字信号处理》、《集成电路原理与应用》和《FPGA系统设计与应用》几门课程融合在一起开设的FPGA综合实验课程设计。

主要从以下两方面考虑:一:设计内容突出FPGA及信号处理的理论和技术的综合应用。

如在数字滤波实验中,要求学生能够熟悉数字滤波器的基本原理,并能运用VHDL语言实现数字滤波。

并采用MATLAB软件实现的结果与运用VHDL 实现的仿真结果进行,来验证其正确性。

最后通过实验装置进行硬件实现,并对结果进行综合分析。

二:如何将《数字信号处理》、《集成电路原理与应用》和《《FPGA系统设计与应用》三门课程有机的结合起来,设计一实际的系统。

由学生在所学知识的基础上,查阅相关资料,自主设计,通过实验装置进行实现,并对结果进行综合分析,寻找最佳设计方案。

基于FPGA的FIR滤波器设计与实现

目录引言 (4)第一章FPGA的设计流程 (5)1.1 FPGA概述 (5)1.2 FPGA设计流程 (9)1.3硬件描述语言HDL(Hardware Description Language) (10)1.4 FPGA开发工具Quartus Ⅱ软件设计流程 (13)第二章有限冲激响应(FIR)滤波器的原理及设计 (16)2.1数字信号处理基础原理 (16)2.2 FIR滤波器背影知识 (19)2.3 FIR数字滤波器原理 (21)2.4 利用窗函数法设计FIR滤波器 (26)第三章FIR 数字滤波器的FPGA实现 (31)3.1串行FIR滤波器原理 (31)3.2分布式算法基础 (32)3.3直接型FIR滤波器的原理结构图 (34)3.4具有转置结构的FIR滤波器 (36)第四章结论与总结 (40)谢辞 (42)参考文献 (43)摘要:本论文课题是《基于FPGA的FIR滤波器设计与实现》。

数字滤波器是语音与图象处理、模式识别、雷达信号处理、频谱分析等应用中的一种基本的处理部件,它能满足滤波器对幅度和线性相位的严格要求,避免模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。

有限冲激响应(FIR)滤波器能在设计任意幅频特性的同时保证严格的线性相位特性。

因此在许多应用领域都显示了强大的生命力,具有重要应用意义。

本文介绍了用VHDL实现线性相位FIR(有限长单位冲激响应)滤波器。

提出了一种基于FPGA的FIR滤波器设计方案。

介绍了基于FPGA的FIR滤波器的数字信号处理的算法设计,采用直接型和转置型的基本结构来设计,其运算效率明显提高,并结合先进的EDA软件进行高效的设计和实现,并给出了用Quartus Ⅱ运行的仿真结果。

该设计对FPGA硬件资源的利用高效合理,用VHDL编程,在PFGA中实现了高采样率的FIR滤波器。

关键字:FIR滤波器;FPGA;VHDL;MATLAB;Quartus ⅡAbstract:Digital filter is a fundamental device used in pronunciation &pattern process, pattern-recognition, radar signal processand spectral analysis. It can meet the high needs to range andphase, and can avoid such problems as voltage drifting,temperature drifting and noise that analogue filters cannotovercome. FIR filter can assure a strict linear phase identitywhile designing any range and frequency. Therefore, FIR filterhas shown its strong vitality in many fields and its importancein using. In the paper, the way to use VHDL to design linearphase FIR filter is introduced and its importance in using. Inthe paper, the way to use VHDL to design linear phase FIRfilter is introduced and its designing thoughts are expounded.This paper introduces the design scheme of FIR filter based onFPGA, introduces that the design technology of FIR filterbased on FPGA about digital system processing arithmetic.FIR filter adopts the basic structure of direct type, the resultare shifting and adding. Integrating advanced software of EDAto design and achieve, and giving some emulator results. Thisdesign makes high use of hardware resource about FPGA,programming with VHDL language, achieving FIR filter withhigh sampling level based on PDGA.Keywords: Finite Impulse Response Digital Filter(FIR)、FieldProgrammable Gate、Array(FPGA)、VHDL、Quartus Ⅱ引言在数字信号处理技术不断发展的今天,数字滤波器正在迅速地代替传统的模拟滤波器,所以有越来越多的人们在研究数字滤波器的结构以及其实现。

基于LV FPGA设计滤波器步骤详解

基于LV FPGA设计滤波器步骤详解

对于NI很多专注于数据采集领域的客户来说,对采集到的信号在前端加

入滤波功能是非常常见的需求。

但是,可能由于他们对NI产品不够了解,不知道这部分功能完全可以由FPGA来完成,从而让NI错失应有的订单和机会。

例如,客户原本的系统构建是在传感器与NI cDAQ之间再外加滤波电路。

明了这个需求以后,我们完全可以向客户推荐具有FPGA终端的cRIO,这样的解决方案即简化了客户的系统构建方案,同时帮NI增加了销售额,两全其美!那幺问题就来了,我们要如何在LV FPGA中实现一个靠谱的滤波器功能呢?

第一步:创建项目

创建任何一个具有FPGA终端的设备和LV 项目。

本文中利用cRIO 9036为例。

注:本文中所有内容均可以利用仿真模式实现,包括FPGA中的滤波

器算法,读者可以在没有硬件资源的情况下模拟本文中的操作。

实际体会IP CORE的使用。

第二步:生成滤波器系数文件.coe

在LabVIEW范例查找器中搜索:coe。

并将:Export FIR Coefficients to Xilinx COE File.vi添加至项目的我的电脑终端下方,以待后续使用。

(Coe是指coefficient,也就是系数。

在Xilinx FIR滤波器中分为很多阶数,每一阶都。

基于FPGA的成型滤波器设计

基于FPGA的成型滤波器设计在数字信号处理(DSP)中,成型滤波器是一种常见的信号处理器件,用于滤除不需要的频率分量并增强所需的频率分量。

而基于现场可编程门阵列(FPGA)的成型滤波器设计,具有高度的灵活性和可重配置性,能够满足不同应用需求。

FPGA是一种可编程逻辑芯片,可用于实现数字电路的硬件加速。

成型滤波器通常由滤波器系数和延迟线构成,而FPGA提供了许多实现这些功能的资源,如多输入多输出(MIMO)乘法器和存储单元。

在基于FPGA的成型滤波器设计中,可以通过编程的方式将这些资源分配给滤波器模块,以实现滤波器操作。

滤波器系数是成型滤波器设计中的关键参数,用于确定滤波器的频率响应。

通过在FPGA上实现的乘法器和加法器,可以将滤波器系数与输入信号进行卷积运算,从而实现对信号频谱的调整。

FPGA的乘法器和加法器资源通常具有高度的并行性,可以支持多通道和高速信号处理。

延迟线是另一个重要的成型滤波器设计参数,在FPGA中可以通过使用存储单元来实现。

延迟线的作用是延迟输入信号的到达时间,以便与滤波器系数进行数学运算。

FPGA的存储单元资源通常具有高速和高密度特性,可以满足滤波器设计中的延迟线需求。

除了滤波器系数和延迟线外,基于FPGA的成型滤波器设计还可以通过添加其他功能来增强滤波器性能。

例如,可以添加乘法器和加法器以实现自适应滤波器,通过动态调整滤波器系数来适应输入信号的变化。

还可以添加输入和输出接口,以实现与其他设备或系统的接口。

在实际应用中,基于FPGA的成型滤波器设计可以用于各种领域,如通信、音频处理和图像处理等。

由于FPGA的可编程性,可以根据应用需求进行优化和升级。

此外,FPGA还具有低功耗、低延迟和高可靠性等特点,适合于对性能要求较高的应用场景。

总之,基于FPGA的成型滤波器设计具有灵活性、可重配置性和性能优势等特点,适用于各种数字信号处理应用。

通过合理设计滤波器系数、延迟线和其他功能,可以实现满足不同应用需求的成型滤波器设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于fpga的多速率滤波器的设计与实现

基于FPGA的多速率滤波器的设计与实现

随着数字信号处理技术的不断发展,多速率滤波器在信号处理中的应用越来越广泛。

多速率滤波器可以将信号分成不同的频带,从而实现对信号的不同频段进行处理。

本文将介绍基于FPGA的多速率滤波器的设计与实现。

一、多速率滤波器的原理

多速率滤波器是一种将信号分成不同频带进行处理的滤波器。

其基本原理是通过不同的抽取和插值操作,将信号分成不同的频带,然后对不同频带的信号进行滤波处理。

多速率滤波器通常由两个部分组成:抽取和插值滤波器。

抽取滤波器是将信号从高采样率降到低采样率的滤波器,其作用是将信号分成不同的频带。

插值滤波器是将信号从低采样率升到高采样率的滤波器,其作用是对不同频带的信号进行滤波处理。

二、基于FPGA的多速率滤波器的设计

基于FPGA的多速率滤波器的设计需要考虑以下几个方面:

1. 选择合适的FPGA芯片

FPGA芯片的选择需要考虑其资源和性能。

对于多速率滤波器的设计,需要选择具有足够的DSP资源和高速IO接口的FPGA芯片。

2. 设计抽取和插值滤波器

抽取和插值滤波器的设计需要考虑其滤波器类型、滤波器阶数、滤波器系数等参数。

可以使用MATLAB等工具进行滤波器设计和优化。

3. 实现滤波器的硬件电路

将抽取和插值滤波器的算法转化为硬件电路需要使用HDL语言进行描述。

可以使用Verilog或VHDL等语言进行描述。

4. 进行仿真和验证

设计完成后需要进行仿真和验证,以确保滤波器的性能和正确性。

可以使用ModelSim等仿真工具进行仿真和验证。

三、基于FPGA的多速率滤波器的实现

基于FPGA的多速率滤波器的实现需要进行以下几个步骤:

1. 编写HDL代码

根据设计完成的抽取和插值滤波器的算法,编写Verilog或VHDL代码。

2. 进行综合和布局布线

使用Quartus等工具进行综合和布局布线,生成bit文件。

3. 下载到FPGA芯片

将生成的bit文件下载到FPGA芯片中,完成多速率滤波器的实现。

四、总结

基于FPGA的多速率滤波器是一种高效的数字信号处理技术,可以实现对信号的不同频段进行处理。

其设计和实现需要考虑FPGA芯片的资源和性能、滤波器的设计和优化、硬件电路的实现以及仿真和验证等方面。

通过合理的设计和实现,可以实现高性能的多速率滤波器。