dsp builder 使用方法

第11章DSP Builder设计规则

第11章

DSP Builder设计规则

应该注意,每一个DSP Builder模块都有自身的设计

规则。在每一模块的使用说明中都包含了其位宽增长 的规则。DSP Builder具有双位字类型,这种类型能支 持的最大数据位宽是51位。如果希望位宽超过51位, 则必须将数据总线分成多套,每套都不超过51位。如 11-1所示的是一个60位加法器设计系统,分成了两个 30位总线。

产生的<file-name>pll.vhd文件,从而在VHDL的顶层设

计中对PLL作必要的修改。

第11章

DSP Builder设计规则

11.3 DSP Builder设计的取名规则

DSP Builder模块的命名必须遵循VHDL的命名规则。 以下的一些规则是必须遵循的: (1) 必须注意大小写的一致性,但模块名的大小写不一 致是没有关系的,例如实体名Mydesign与MYDESIGN是 相同的。

11.1 位宽设计规则

在设计中,必须根据具体情况规定输入和输出数据 口的位宽,即源端口与目标端口的数据位宽。一旦确 定了输入端的数据位宽,SignalCompiler就会通过各中 间模块把数据位宽从源端口向目标端口传递。在一定 条件下,设计者也可以对所通过的各模块中的数据位 宽作一定的设定。例如,在第三章中介绍的调幅设计 中 , Sinln 和 SinDelay 模 块 的 位 宽 是 16 , 所 以 SignalCompiler就自动将这16位宽的数据类型赋予了中 间模块Delay。

无符号二 进制整数

[L],是无符号总线的 位数

单 个 二 进 制位

取值1或0 的整数

[1]

Simulink 单 一 位 信 号 对 应 VHDL的STD_LOGIC

利用DSPBuilder搭建基于CORDIC算法的QDDS系统

厂 — — 一

,

合 V S 实现 。 LI 2 CoRDI 原理及改进方案 C

2.,时 据 角 式 得 c √ , ) 根 三 公 可 到。 . 同 ・ s 0

,

ac n ± 总在 一 2~仃/ rt a 2一 仃/ 2内 , cs 终是正值 。则 故 oO始 ( ) ( ) 的正切项 的乘 法就演变 成二进制 的一位运 算 , 3 ,4 式 每

度、 简单性和高 效实 现方 面 的综 合要 求 , 而用 C R I O D C算 法 实现 D S或 Q D D D S系统则 能很 好的兼顾这些方面 , 并且极适

X l=X 0・c s — 0 ・ i O oO Y sn Y y ・ o O+ l 0 c s o。 i O sn

J n2 0 u .0 8

利 用 D P u dr 建基 于 C R I 法 的 Q D SBie搭 l O DC算 D S系统

张琦 郑 小平 苏 国强

( 兰州交 通大学光 电技术与智能控制 教育部重 点实验室 ) ( 兰州 交通 大学 国家绿色镀膜技术与装备工 程技 术研 究 中心 ) 摘要 : 于直接数 字频 率合成 器( i c D ga Snhs e) 基 Dr t iil ytei r 原理 , e t z 采用 A ea 司的 D P ule 软件 , 建 了基于 C R I hr公 S Bi r d 搭 O DC算 法的 Q D D S系统 , 不仅 比传统查找表式 的 D S系统 节省 了大量 R M 资源 , D O 达到较 高的运 算速 度 , 而且利 用较 新的 D P工具 S

基于DSP Builder的14阶FIR滤波器的设计

基于DSP Builder的14阶FIR滤波器的设计数字在数字信号处理的各种应用中发挥着非常重要的作用,他是通过对采样数据信号举行数学运算处理来达到频域滤波的目的。

数字滤波器既可以是有限长单脉冲响应(FIR)滤波器也可以是无限长单脉冲响应(IIR)滤波器。

在维纳滤波器理论发明的早期,人们用法IIR滤波器,但现在更多是用法FIR滤波器。

本文根据Matlab/Simulink/ Builder/Ⅱ流程,设计一个FIR滤波器。

DSP Builder是衔接Simulink和Quartus Ⅱ开发软件的DSP开发工具。

在DSP Builder的无缝设计流程中,首先在Matlab软件中举行算法设计,然后在Simulink软件中举行系统集成,最后将设计输出为硬件描述语言(HDL)文件,以便在QuartusⅡ软件中用法。

1 FIR滤波器介绍1.1 FIR滤波器原理对于一个FIR滤波器系统,他的冲激响应总是有限长的,其系统函数可以记为:其中:x(n)是输入采样序列;h(n)是滤波器系数;L是滤波器的阶数;y(n)表示滤波器的输出序列。

也可以用卷积来表示输出序列y(n)与x(n),h(n)的关系。

y(n)=x(n)*h(n)典型的挺直I型FIR滤波器1所示,其输出序列y(n)满足下式:1.2 设计要求数字滤波器事实上是一个采纳有限精度算法实现的线性非时变离散系统,他的设计步骤是先按照需要确定其性能指标,设计一个系统函数h(n)靠近所需要的性能指标,滤波器的系数的计算可以借助Matlab强大的计算能力和现成的滤波器设计工具来完成,最后采纳有限的精度算法实现。

本系统的设计指标为,设计一个14阶的FIR滤波器。

1 MHz和16 MHz的两个正弦波的合成波形,经过这个滤波器,滤除16 MHz 的成分。

2 DSP Builder设计流程用法DSP Builder完成设计时,首先在Matlab/Simulink软件中建立模型文件(.mdl),DSP Builder SignalCom-piler模块读取由DSP Builder和MegaCore模块构建的Simulink建模文件(.mdl),生成文件和工具指令语言(Tcl)脚本,举行综合、硬件实施和。

基于DSP Builder的双曲正切函数的FPGA实现

莨

2 、 图3 所示 。 显然 , 分段数为 1 0 2 4时误差明显低于分段 数为 2 5 6时 , 其最 大绝 对误差约为 4 e 一 6 , 高于文献[ 6 ] 中

所述 的神经网络的精 度要求 。

输 入x

图2 分 段 数 目为 2 5 6时 的绝对 误差 散点 图

6 7

基于 D S P B u i l d e r 的双曲正切 函数 的 F P G A实 现

电 子质 量 ( 2 0 1 5 第0 8 期)

用浮点数或定点数进行表示 。 使用浮点数可 以获得很高

的精度和很宽 的动态 范 围, 但是在 F P G A上进行 浮点数

的运算会消耗大量硬件资源 , 而很 多情 况下需要 的精度 和数据 的范 围都 是有 限的 ,满 足设计 的需 求 即可 。在 D S P B u i l d e r 中, 数 据采用 二进制定 点数表 示方法 , 数据 可 以设 置 成 无 符 号 整 数 、有 符 号 整 数 和 有 符 号 小 数 等 。 其 中, 有符号小数 由符号位 、 整数位 和小数位 组成 , 位宽 根据需要灵活设定 。 整数部分 的位数决定数据可 以表达 的范 围, 小数部分的位数决定数据 的表达精 度 。采用定 点数进行数值运算 ,其操作数一般采用整 型数来表示 。

要将 转化为 查表地址 ,以得到该输 入所在 分段 的系

令 分敬 阀 为O 2

数, 并 先后 进行乘法 和加法运算 , 得到 双曲正切 函数 的

近似计算值 。 各分 段系 数 的定 义和求 解方 法如 下 :在 区 间 , b ] 上, 若 ) ∈C [ a , 6 】 , 且存在 一个 C [ a , 6 ] 的子集  ̄ P = s p a n {  ̄ o , ) , 其中 C [ a , 6 ] 是 区间 a , 6 】 上所有实连续 函数组成

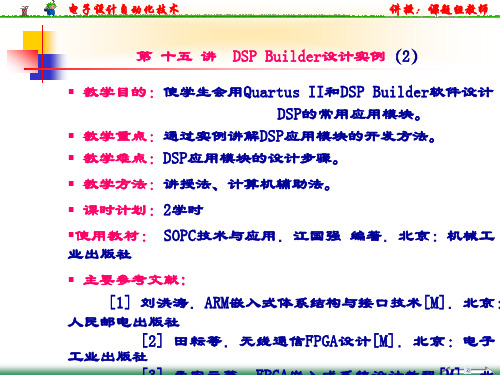

精品课件-EDA技术应用基础-第15讲 DSP Builder设计实例(2)

电子设计自动化技术

Al tBu s8 106

Al tBu s9 46

Al tBu s1 0 -12

Al tBu s1 1 -22

Al tBu s1 2 1

Al tBu s1 3 14

Al tBu s1 4 3

Al tBu s1 5 -9

Al tBu s1 6

x_in[8:0] In1[8:0] In2[8:0] In3[8:0] In4[8:0]

y _out[19:0] Out2[8:0]

fi r4 _ b l o ck2

x_in[8:0] In1[8:0] In2[8:0] In3[8:0] In4[8:0]

y _out[19:0] Out2[8:0]

fi r4 _ b l o ck3

+

+

+

19:0

17:8

+ Bu sCo n ve rsi o n 1

+

Pa ra l l e l Adder Subtractor

512 Al tBu s1 7

+ +

+

Pa ra l l e l Adder Subtractor1

o9:0 y

Si g n a l Co m p i l e r

➢16个常数端口设置滤 波器的系数,可根据具 体要求进行计算而确定。

o8:0 x2

L1

y(n) x(n i)h(i) i0

➢直接I型FIR滤波器:可理解为一个分节的延时线,把每 一节的输出加权累加,可得到滤波器的输出。但滤波器的

阶数越高,占用的运算时间就越多,因此在满足指标要求

电子设计自动化技术

讲授:课题组教师

基于DSP Builder的四维时滞混沌系统数字电路设计与仿真

号 【 F GA指 现 场 可 编 程 门 阵 列 ( il rga l P l 。 FedP o rmme d

为对 自身参 数 扰 动 非 常敏 感 . 系统 配置 不 灵 活 、 备 运 设

行 与维 护都 比较 麻 烦 .从 而 限制 了模 拟 电路 混 沌 系统

的 实 际 应 用 现 在 多 数 算 法 都 能 在 数 字 系 统 ( 如 例

基 于 D P B i e 的 四维 时滞 混沌 系统 S ul r d 数 字 电路 设计 与 仿 真

张之 光 一 , 杨 杰 。 。 李 明

(. 1 中国 人 民解 放 军 6 7 9部 队 , 原 0 2 0 ; . 西理 工 大 学 信 息 _ 学 院 , 州 3 1 0 ; 16 太 3 10 2 江 T程 赣 4 0 0 3 中国 人 民解 放 军 6 9 2部 队 ,I I . 10  ̄J 宜宾 6 4 0 ; . 州 广 播 电 视 大学 , 州 3 10 ) t I 4 00 4 赣 赣 4 0 0

设 计 混 沌 系统 的 固有 缺 陷 . 混 沌 系统 进行 离散 化 处理 . 出基 于 DS ule 软 件 设 计 时 将 提 PB i r d 滞 混 沌 吸 引子 的 方 法 。 通过 数 字 电路 的优 化 设 计 . 数 的 合理 配 置 . 系统 的信 号 幅 度 控 制 参 该

基于DSP Builder的DDS设

基于DSP Builder的DDS设

基于DSP Builder的DDS设计及其FPGA实现

直接数字合成器,是采用数字技术的一种新型频率合成技术,他通过控

制频率、相位增量的步长,产生各种不同频率的信号。

他具有一系列的优点;较高的频率分辨率;可以实现快速的频率切换;在频率改变时能够保持相位

的连续;很容易实现频率、相位和幅度的数控调制等。

目前可采用专用芯片

或可编程逻辑芯片实现DDS[1],专用的DDS芯片产生的信号波形、功能和

控制方式固定,常不能满足具体需要[2]。

可编程逻辑器件具有器件规模大、

工作速度快及可编程的硬件特点,并且开发周期短,易于升级,因为非常适

合用于实现DDS。

1 DDS的工作原理

DDS的结构原理图如图1所示,DDS以数控振荡器的方式,产生频率、相位和幅度可控的正弦波[3]。

电路包括了相位累加器、相位调制器、正弦ROM查找表、基准时钟源、D/A转换器等组成。

其中前三者是DDS结构中

的数字部分,具有数控频率合成的功能。

DDS系统的核心是相位累加器,完成相位累加过程。

在基准时钟的控。

基于DSP Builder的16阶FIR滤波器实现

基于DSP Builder的16阶FIR滤波器实现作者:范寒柏,司加祯来源:《现代电子技术》2009年第20期摘要:现场可编程门阵列(FPGA)器件广泛用于数字信号处理领域,而使用VHDL或VerilogHDL语言进行设计的难度较大。

提出一种采用DSP Builder实现FIR滤波器的设计方案,按照Matlab/Simulink/DSP Builder/Modelsim /Quartus Ⅱ的设计流程,设计一个16阶的FIR低通滤波器,并完成了软硬件的仿真与验证。

结果表明,该方法简单易行,可满足设计要求,它验证了采用DSP Builder实现滤波器设计的独特优势。

关键词:FIR 滤波器;Simulink;DSP Builder;Quartus Ⅱ中图分类号:TN713文献标识码:A文章编号:1004-373X(2009)20-193-03Design of 16-taps FIR Filter Based on DSP BuilderFAN Hanbai,SI Jiazhen(North China Electric Power University,Baoding,071003,China)Abstract:Field Programmable Gate Array(FPGA)devices is widely used in the field of digital signal processing,it is difficult to design using VHDL or VerilogHDL.A model development technology of DSP Builder is adopted to design FIR filter,according to the flow ofMatlab/Simulink/DSP Builder/Modelsim /Quartus Ⅱ,a 16-taps low-pass FIR filter is designed,which is simulated and verified in the digital signal process circuit,the results show that the method is simple,feasible and the advantage of designing digital filter by the use of DSP builder are verified.Keywords:FIR filter;Simulink;DSP Builder;Quartus ⅡFIR数字滤波器在数字信号处理的各种应用中发挥着十分重要的作用,它能够提供理想的线性相位响应,在整个频带上获得常数群时延,从而得到零失真输出信号,同时它可以采用十分简单的算法予以实现。

基于DSP Builder的快速整数离散余弦变换的实现

基于DSP Builder的快速整数离散余弦变换的实现梁东云【摘要】提出了基于DSP Builder平台的快速整数离散余弦变换(DCT)的实现方法.首先介绍了整数DCT的原理,然后基于DSP Builder平台、Simulink平台以及电子设计自动化(EDA)平台Modelsim构建了整数DCT的蝶形运算模型.最后,对完整的测试电路进行仿真.结果表明:该方法简单可行,缩短了开发周期,可方便地应用于相关领域.【期刊名称】《系统仿真技术》【年(卷),期】2018(014)004【总页数】5页(P314-318)【关键词】离散余弦变换(DCT);运算电路;DSP Builder平台【作者】梁东云【作者单位】商洛学院电子信息与电气工程学院,陕西商洛726000【正文语种】中文【中图分类】G642;TP391离散余弦变换(DCT)是一种常用的信号处理变换,具有很强的“能量集中”特性,而且当信号具有接近马尔科夫过程的统计特性时,DCT的去相关性接近K-L变换的性能,因此它被广泛应用于视频信号处理和音频信号处理等领域[1-3]。

常见的H.264视频编码就利用了整数DCT[4-5]。

实际应用中,相关算法的实现需要硬件的支撑。

现代电子设计自动化(EDA)技术的迅速发展,使得常见算法可以通过硬件描述语言并利用现场可编程门阵列(FPGA)的逻辑资源实现,但代码编写、硬件调试比较复杂,开发周期长[6-8]。

使用调试好的知识产权(IP)核可显著减小工作量,但许多IP核需要单独购买[9]。

本文利用DSP Builder平台,在Simulink工作环境下采用图形模型构建整数DCT的蝶形运算模型,并对其进行仿真。

由于该模型将多个EDA工具联合起来,避开了复杂的代码设计,因此降低了开发难度。

1 整数DCT变换传统二维DCT及其逆变换如下所示[3]:在H.264频频编码过程中,采用了4×4整数DCT,在不损害图像精度的前提下,减少了数据运算量,避免了传统浮点运算带来的数据失配问题。

全相位FRM陷波原理及其DSP Builder实现

率响应表 达式,证 明了在平移参数 取 非 1 / 2整数倍 的情况下 ,提 出的 陷波结构无需任何补偿和校正措施 ,其陷波

深度高达约 一2 0d .借助 A t a开发3 具 D P B i e 对所提 出的陷波结构进行 建模 、仿真 ,产生 Q ats I能够 0 B lr e - S ul r d ur I u 识别的 V L源程序 ,利用 Mo e i HD d l m进行 R L级仿真 ,综合 、适配并下栽 至 F GA芯片.实验 结果验证 了设计方 S T P

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第9章DSP Builder设计初步利用EDA技术完成硬件设计的途径有多种,前面介绍的是利用QuartusII来完成的,最为典型的设计流程,包括设计项目编辑(如用VHDL)、综合、仿真、适配、编程。

但是对于一些特定的设计项目,这个流程就会显得很不方便,甚至无能为力。

例如涉及算法类(如DSP模块)及模拟信号处理与产生方面的系统设计。

Altera自2002年推出的DSP Builder则很好地解决了这些问题。

DSP Builder可以帮助设计者完成基于FPGA的不同类型的应用系统设计。

除了图形化的系统建模外,DSP Builder还可以自动完成大部分的设计过程和仿真,直至把设计文件下载至FPGA开发板上。

利用Matlab与DSP Builder进行模块设计也是SOPC技术的一个组成部分。

本章以两个简单的电路模型设计为示例,详细介绍Matlab、DSP Builder、QuartusII 三个工具软件联合开发的设计流程。

9.1 Matlab/DSP Builder及其设计流程DSP Builder是一个系统级(或算法级)设计工具,它架构在多个软件工具之上,并把系统级(算法仿真建模)和RTL级(硬件实现)两个设计领域的设计工具连接起来,都放在了Matlab/Simlink图形设计平台上,而将QuartusII作为底层设计工具置于后台,最大程度地发挥了对种工具的优势。

DSP Builder依赖于MathWorks公司的数学分析工具Matlab/Simlink,以Simulink的Blockset出现。

可以在Simulink中进行图形化设计和仿真,同时又通过SignalCompiler把Matlab/Simulink的模型设计文件(.mdl)转成相应的硬件描述语言VHDL设计文件(.vhd),以及用于控制综合与编译的tcl脚本。

对于综合以及此后的处理都由QuartusII来完成。

由于在FPGA上设计一个算法模型的复杂性,设计的性能(包括面积、速度、可靠性、设计周期)对于不同的应用目标将有不同的要求,涉及的软件工具也不仅仅是Simulink和QuartusII,DSP Builder针对不同情况提供了两套设计流程,即自动流程和手动流程。

图9-1是基于Matlab、DSP Builder、QuartusII等工具完成设计的流程框图。

如图9-1所示,设计流程的第一步是在Matlab/Simulink中进行设计输入。

即在Matlab的Simulink 环境中建立一个mdl模型文件,用图形方式调用DSP Builder和其他Simulink库中的图形模块,构成系统级或算法级设计框图,或称Simulink设计模型。

在第二步,是利用Simulink 的图形化仿真、分析功能,分析此设计模型的正确性,完成模型仿真。

在这两步中,与一般的Matlab Simulink建模过程几乎没有什么区别,所不同的是,设计模型库采用DSPBuilder 的Simulink库而已,同样也涉及到其他EDA软件。

第9章 DSP Builder设计初步309图9-1 基于Matlab、DSP Builder、QuartusII等工具第三步是DSP Builder设计实现的关键一步。

由于EDA工具软件(诸如QuartusII、ModelSim)不能直接处理Matlab的.mdl文件,这就需要一个转换过程。

通过SignalCompiler 把Simulink的模型文件(后缀为.mdl)转化成通用的硬件描述语言,VHDL文件。

转换获得的HDL文件是基于RTL级的,即可综合的VHDL描述。

此后的步骤是对以上顶层设计产生的VHDL的RTL代码和仿真文件进行综合、编译适配以及仿真。

为了针对不同用户的设计目的和设计要求,DSP Builder提供了两种不同的设计流程,主要可以分为自动流程和手动流程。

如果采用自动流程,几乎可以忽略硬件的具体实现过程,选择让DSP Builder自动调用QuartusII等EDA软件,完成综合(Synthesis)、网表(ATOM Netlist)生成和QuartusII适配,直至在Matlab中完成FPGA的配置下载过程。

但是,如果希望使用其它第3方的VHDL综合器和仿真器(除Synplify、LeonardoSpectrum和 QuartusII综合器及ModelSim外),或是希望完成特定的适配设置,如逻辑锁定、时序驱动编译、ESB特定功能应用等,可以选用手动流程设计。

在此流程中,设计者可以灵活地指定综合、适配条件;手动地调用VHDL综合器进行综合,调用QuartusII 进行适配,调用ModelSim或者QuartusII进行仿真,最后用QuartusII产生相应的编程文件用于FPGA的配置。

EDA技术与VHDL310采用手动流程时,除了行为级仿真验证和设计输入外,其它过程与标准的基于VHDL 的EDA设计流程是完全一致的。

首先由基于Matlab的DSP Builder设计流程得到 VHDL 文件(由Simulink模型文件*.mdl通过SignalCompilder转换而成),送入综合器进行综合。

综合器可以是Synplify Pro,也可以是LeonardoSpectrum,或者采用Altera自己的QuartusII 综合器。

在综合时,可能需要对综合器进行配置或者提供综合的约束条件,由于这个过程操作可能比较繁琐,所以DSP Builder的SignalCompiler相应提供了一个接口,针对设计,自动产生一个TCL脚本与综合器Synplify或者LeonardoSpectrum相接。

综合器在综合操作后,会产生一个网表文件,以供下一个流程使用。

这里产生的网表文件称为ATOM网表文件,主要是EDIF网表文件(.edf 电子设计交换格式文件)或VQM(.vqm Verilog Quartus Mapping File),它们是一种参数可设置的,并含有具体器件系列硬件特征(如逻辑宏单元LCs、I/O单元、乘积项、M4K、嵌入式系统块ESB等)的网表文件。

QuartusII可以利用这些ATOM网表文件针对选定的具体器件进行适配,包括布线、布局、结构优化等操作,最后产生时序仿真文件和FPGA目标器件的编程与配置文件。

在这一步,设计者可以在QuartusII中完成对Pin(引脚)的锁定,更改一些约束条件等。

如果用DSP Builder产生的设计模型只是庞大设计中的一个子模块,可以在设计中调用DSP Builder产生的VHDL文件,以构成完整的设计。

同时,还可以使用QuartusII强大的LogicLock功能和SignalTap测试技术。

在DSP Builder设计流程的最后一步,可以在DSP Builder中直接下载到FPGA用户开发板上,或者通过QuartusII完成硬件的下载、测试。

在图9-1的流程中,其中的VHDL仿真流程在设计中是不可或缺的。

与DSP Builder 可以配合使用的HDL仿真器是ModelSim。

DSP Builder在生成VHDL代码时,可以同时生成用于测试DSP模块的TestBench(测试平台)文件,DSP Builder生成的TestBench文件采用VHDL语言,测试向量与该DSP模块在Simulink中的仿真激励相一致。

通过ModelSim 仿真生成的TestBench可以验证生成的VHDL代码与Simulink中设计模型的一致性。

另外,DSP Builder在产生TestBench的同时,还产生了针对ModelSim仿真的Tcl脚本来简化用户的操作,如包含了来自Simulink平台上进行仿真的激励信号信息等,从而掩盖ModelSim 仿真时的复杂性。

在大部分情况下,QuartusII对来自DSP Builder的设计模块适配后,需要再次验证适配后网表与Simulink中建立的DSP模型的一致性。

这就需要再次使用ModelSim进行仿真,这时仿真采用QuartusII适配后带延时信息的网表文件(EDIF格式、或者VHDL、Verilog 格式),即为时序仿真。

两种设计流程归纳起来有如下几个步骤:自动流程:1、MATLAB/Simulink建模;2、系统仿真;3、DSP Builder完成VHDL转换、综合、适配、下载。

4、嵌入式逻辑分析仪实时测试手动流程:1、MATLAB/Simulink建模;2、系统仿真;3、DSP Builder完成VHDL 转换、综合、适配;4、Modelsim对TestBench功能仿真;5、QuartusII直接完成适配(进第9章 DSP Builder设计初步311行优化设置);6、QuartusII完成时序仿真;7、引脚锁定;8、下载/配置与嵌入式逻辑分析仪等实时测试;9、对配置器件编程,设计完成。

考虑到实用的目的,本章重点介绍手动设计流程。

9.2 正弦信号发生器设计本节中,以一个简单的可控正弦波发生模块的设计为例,详细介绍DSP Builder基于手动流程的的使用方法。

图9-2所示是一个简单的正弦波发生器,主要由4个部分构成:InCount 是阶梯信号发生模块,产生一个按时钟线性递增的地址信号,送往SinLUT。

SinLUT是一个正弦函数值的查找表(LUT:Look Up Table)模块,由递增的地址获得正弦波的量化值输出。

由SinLUT输出的8位正弦波数据经过一个延时模块Delay后送往Product乘法模块,与SinCtrl相乘。

由于SinCtrl是1位(bit)输入,SinCtrl通过Product就完成了对正弦波输出有无的控制。

SinOut是整个正弦波发生器模块的输出,送往D/A即可获得正弦波的输出模拟信号。

设计者在利用DSP Builder来进行相关设计时,关键的设计过程大都在Matlab 的图形仿真环境Simulink中进行。

图9-2 正弦波发生模块原理图9.2.1 建立设计模型首先需要建立一个新的设计模型,步骤如下:1、打开Matlab环境Matlab环境界面如图9-3所示。

可以看到,Matlab的主窗口界面被分割成三个窗口:命令窗口(Command Window)、工作区(Workspace)、命令历史(Command History)。

在命令窗口中,可以键入Matlab命令,同时获得Matlab对命令的响应信息、出错警告提示等。

EDA技术与VHDL 312工作区命令历史记录命令窗口工作目录图9-3 Matlab界面2、建立工作库在建立一个新的设计模型前,最好先建立一个新的文件夹,作为work(工作)目录,并把Matlab当前的work目录切换到新建的文件夹下。

可以使用Windows在外部建立,也可以使用Matlab命令来直接完成这些操作,例如在Matlab主窗口中的命令窗口中键入:cd e:/mkdir /myprj/sinwavecd /myprj/sinwave其中e:/myprj/sinwave是新建的文件夹,是用作Matlab工作目录的。