CPLD和虚拟仪器的频率计综合设计

基于CPLD的简易数字频率计的设计

184

现代电子技术

2011 年 第 34 卷

控 制 电 路 是 对 计 数 电 路 、锁 存 电 路 和 译 码 电 路 进 行 时序的控制。其控制要求为:先使计数电路 在 1s内 进 行计数,接着在下 一 个 1s内 锁 存 计 数 的 结 果,最 后 将 锁存的数据进行译码和显示。在第一个测量显示周期 结束后,控制电路将再 次 发 出 控 制 信 号,先 对 功 能 电 路 清 零 ,然 后 使 系 统 开 始 第 二 个 测 量 周 期 的 工 作 。

译码电路的功能是将锁存器保存并将输出的4位 二 进 制 代 码 表 示 的 十 进 制 数 进 行 译 码 转 换 ,将 其 转 换 为 能直接驱动数码管显示的十进制数字字符的输出信号。

显示电路由共阴数码管电路构成。由于被测信号 的频率测频范 围 为 1 Hz~1 MHz,因 此 需 要 6 个 数 码 管对其进行显示。

基于CPLD和单片机的频率计设计

正文:

一、实验设计原理

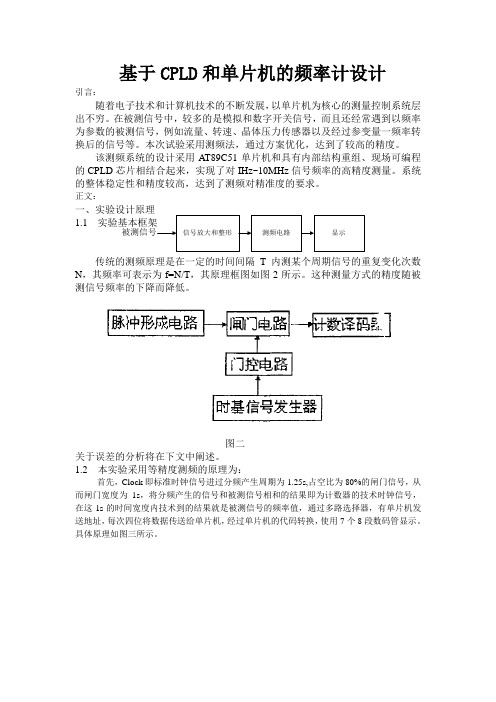

1.1实验基本框架

图一

传统的测频原理是在一定的时间间隔T内测某个周期信号的重复变化次数N,其频率可表示为f=N/T,其原理框图如图2所示。这种测量方式的精度随被测信号频率的下降而降低。

{

Counter = 0;

TMOD = 0x11; //定时器工作方式

TH0 = T0_High_Init;

TL0 = T0_Low_Init; //设置定时器初值

TR0 = 1; //启动定时器

ET0 = 1; //允许定时器中断

EA = 1; //开中断

}

//延时

void delay()

{

int ti;

基于CPLD和单片机的频率计设计

引言:

随着电子技术和计算机技术的不断发展,以单片机为核心的测量控制系统层出不穷。在被测信号中,较多的是模拟和数字开关信号,而且还经常遇到以频率为参数的被测信号,例如流量、转速、晶体压力传感器以及经过参变量一频率转换后的信号等。本次试验采用测频法,通过方案优化,达到了较高的精度。

Dig_sel1 = 0;

Dig_sel0 = 0;

delay();

indata = P0;

Digit7 = indata & 0x0f;

Dig_sel0 = 1;

delay();

indata = P0;

Digit6 = indata & 0x0f;

Dig_sel1 = 1;

基于CPLD的频率计设计

基于CPLD的频率计设计摘要本文介绍了一种基于复杂可编程逻辑器件(CPLD)的频率计设计。

频率计是一种测量信号频率的仪器,广泛应用于电子工程、通信工程等领域。

本文首先简要介绍了频率计的原理和应用场景,然后详细阐述了基于CPLD的频率计的设计思路和实现步骤。

最后,通过实验验证了设计的可行性和准确性。

本文通过Markdown文本格式输出,便于阅读和理解。

引言频率计作为一种常用的测量设备,广泛应用于各个领域。

传统上,频率计主要使用模拟电路实现。

然而,随着数字电子技术的发展,CPLD逐渐成为一种流行的可编程逻辑器件,其具有体积小、功耗低和灵活性高等优点。

本文将介绍如何利用CPLD设计出一种精确可靠的频率计。

频率计原理频率计的基本原理是测量信号周期的倒数,即计算出信号的频率。

实现频率计需要以下几个步骤:1.输入信号经过滤波器,去除噪音和干扰。

2.使用计数器模块对输入信号进行频率计数。

3.使用定时器模块来确定计数的时间窗口。

4.根据计数结果和时间窗口的长度计算出信号的频率。

基于CPLD的频率计设计思路基于CPLD的频率计设计可以分为以下几个关键步骤:1.确定输入信号的范围和要求。

根据应用的具体需求,确定输入信号的频率范围和精度要求。

2.选择合适的CPLD芯片。

根据输入信号的要求,选择具有足够的计数器和定时器资源的CPLD芯片。

3.编写计数器和定时器的Verilog代码。

根据选定的CPLD芯片的特性,使用Verilog语言编写计数器和定时器的逻辑代码。

4.设计输入和输出接口。

根据具体的应用场景,设计CPLD芯片的输入和输出接口。

基于CPLD的频率计设计实现步骤1:确定输入信号的范围和要求在本设计中,假设输入信号的频率范围为1Hz到10MHz,要求测量精度为0.1Hz。

步骤2:选择合适的CPLD芯片根据步骤1的要求,选择支持至少10MHz频率计数的CPLD芯片。

步骤3:编写计数器和定时器的Verilog代码在这一步骤中,我们使用Verilog语言编写计数器和定时器的逻辑代码。

基于CPLD直接测频法的数字频率计设计

图( 3. 图 ) 此测 量模 块 的测量 位数 为 6 , 位 若想 改变频 率计 的测量位 数 , 可适 当 的改变 计数 器 的个数 , 则 并且 相 应模 块更 改相应 的参 数 , 如此就 可 以增 加或 者减 少频率计 的测量 范 围. 其顶层 电路仿 真 图见 图 4 .

器、 测频 控 制 信 号 发 生器 、 带有 时钟 使 能 端 的 计数 器 、 锁存 器 D G、 码 器 EN ODE 串联 动 态 扫描 模 块 RE 译 C 、

D MI 以及 6个 L D 显示 管组 成. 4 TS AO E 用 OMHz 的有 源 晶振作 为 F GA 的测 试标 准 频率 , P 经分 频 电 路最

过 计 算 在 一 定 时 间 内通 过 的 周 期 数 . 就 要 求 该模 块 的 能 产 生 一 个 周 期 为 1s的 技 术 使 能 信 号 E 这 NA,

并 且 还 要 同 步 对 每 一 个 计 数 器 的 使 能 端 进 行 控 制 . 数 器 在 使 能 端 为 高 电平 时 开 始 计 数 , 低 电 平 时 计 在 停 止 计 数 , 且 还要 保 持 计 数值 . 此 期 间 , 存 器 的 使 能 端 接 收 到 一 个 锁 存 的 上 升 信 号 , 且 将 计 数 并 在 锁 并 值 送 到 锁存 器 中 , 过 译 码 电路 译 码 再 经 显示 模 块 最 终 在 七 段 数 码 管 上 显 示 计 数 结 果 . 过 锁 存 器来 通 通

终得 到 1Hz 频率 . 信 号作 为 测频 控制 信 号发 生器 的输 入信 号 , 到 1s的 闸 门信号 用 来 控制 计 数 器计 1Hz 得

基于CPLD实现的DDS&频率计

基于STC89C51和CPLD实现的DDS与频率计系统框图功能描述:以STC89C51为控制核心,实现任意频率值fa(小于10KHz)的输入,经单片机出来后,生成相应的频率字,然后送给DDS模块,DDS模块开始工作,生成以频率值fs;但键盘测频键按下后,单片机控制频率计,让其开始控制,频率计输出值送回单片机处理,得出测量到的频率值fc,最后单片机控制LCD1602显示人为输入的频率值fa和频率计测得的频率值fc,两个值的差异可以直观的显示出系统的误差。

基于CPLD/FPGA的DDS原理图如下:基于CPLD/FPGA的频率计的原理图如下:DDS模块代码:(1)MUX832LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX832 ISPORT( DATAINN : IN STD_LOGIC_VECTOR(7 DOWNTO 0);clk : in std_logic;DATAOUTT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0);SELL :IN STD_LOGIC_VECTOR(1 DOWNTO 0));END MUX832;ARCHITECTURE behav OF MUX832 ISBEGINPROCESS(SELL,DATAINN,clk)BEGINif clk'event and clk='1' thenCASE SELL ISWHEN "00" => DATAOUTT(7 DOWNTO 0) <= DATAINN;WHEN "01" => DATAOUTT(15 DOWNTO 8) <= DATAINN;WHEN "10" => DATAOUTT(23 DOWNTO 16) <= DATAINN;WHEN "11" => DATAOUTT(31 DOWNTO 24) <= DATAINN;END CASE;end if;END PROCESS;END behav;(2)32位加法器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER32B ISPORT ( A: IN STD_LOGIC_VECTOR(31 DOWNTO 0);B: IN STD_LOGIC_VECTOR(31 DOWNTO 0);S: OUT STD_LOGIC_VECTOR(31 DOWNTO 0));END ADDER32B;ARCHITECTURE behav OF ADDER32B ISBEGINS<=A+B;END behav;(3)32位寄存器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY REG32B ISPORT( LOAD : IN STD_LOGIC;DIN : IN STD_LOGIC_VECTOR(31 DOWNTO 0);DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0));END REG32B;ARCHITECTURE behav OF REG32B ISBEGINPROCESS(LOAD,DIN)beginIF LOAD'EVENT AND LOAD ='1' THENDOUT<=DIN;END IF;END PROCESS;END behav;频率计模块代码:(1)标准频率计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY BZHH ISPORT (BCLK: IN STD_LOGIC; --FsBENA: IN STD_LOGIC;CLR : IN STD_LOGIC; --清零BZQ : inOUT STD_LOGIC_VECTOR(31 DOWNTO 0));END BZHH;ARCHITECTURE behav OF BZHH ISBEGINPROCESS(BCLK, CLR) --标准频率计数开始BEGINIF CLR = '1' THEN BZQ <= (OTHERS=>'0');ELSIF BCLK'EVENT AND BCLK ='1' THENIF BENA ='1' THEN BZQ <= BZQ + 1;END IF;END IF;END PROCESS;END behav;(2)待测频率计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TTFF ISPORT (TCLK: IN STD_LOGIC; --FsENA: IN STD_LOGIC;CLR : IN STD_LOGIC; --清零TSQ : inOUT STD_LOGIC_VECTOR(31 DOWNTO 0));END TTFF;ARCHITECTURE behav OF TTFF ISBEGINPROCESS(TCLK, CLR,ENA)BEGINIF CLR = '1' THEN TSQ <= (OTHERS=>'0');ELSIF TCLK'EVENT AND TCLK ='1' THENIF ENA ='1' THEN TSQ <= TSQ + 1;END IF;END IF;END PROCESS;END behav;(3)MUX648LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX648 ISPORT( DATAIN1 : IN STD_LOGIC_VECTOR(31 DOWNTO 0);DATAIN2 : IN STD_LOGIC_VECTOR(31 DOWNTO 0);DATAOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);SEL :IN STD_LOGIC_VECTOR(2 DOWNTO 0));END MUX648;ARCHITECTURE behav OF MUX648 ISBEGINDATAOUT <= DATAIN1(7 DOWNTO 0) WHEN SEL="000" ELSE --标准频率计低八位输出DATAIN1(15 DOWNTO 8) WHEN SEL="001" ELSEDATAIN1(23 DOWNTO 16) WHEN SEL="010" ELSEDATAIN1(31 DOWNTO 24) WHEN SEL="011" ELSE --标准频率计最高八位输出DATAIN2(7 DOWNTO 0) WHEN SEL="100" ELSE --待测频率计数值低八位输出DATAIN2(15 DOWNTO 8) WHEN SEL="101" ELSEDATAIN2(23 DOWNTO 16) WHEN SEL="110" ELSEDATAIN2(31 DOWNTO 24) WHEN SEL="111" ELSE --待测频率计数值最高八位输出DATAIN2(31 DOWNTO 24) ;END behav;单片机程序如下:主程序#include<reg52.h>#include<intrins.h>#include"key.h" //scankey(); keyexe(); setfre(); testfre(); #include"lcd1602.h" //display();void main(void){lcd_init();bena=0;clr=1;load_dds=0;oe=0;start=1;lcd_str(0,2,"dds.and.testfre!");while(1){keyexe();}}键盘程序:#ifndef __KEY_H__#define __KEY_H__#include<reg52.h>#include<intrins.h>#include "lcd1602.h"#define dinout P3;unsigned char keybuffer[8],longtochar[4],recieve[8];unsigned long freword,setdispbuf;unsigned long tfrecount,bfrecount; //Fs、Fx计数值unsigned long tfreword;//-----------pin define for dds and testfre------sbit sel2=P1^2;sbit sel1=P1^1;sbit sel0=P1^0;sbit oe=P2^3;//-----------pin define for dds loading ----------sbit load_dds=P2^4;//-----------pin define for testfre--------------sbit clr=P2^0;sbit bena=P2^1;sbit start=P2^2;//-----------delay programm----------------------void delay(unsigned int n){while(n--) _nop_();}//-----------format exchange---------------------void keytofreword(void){freword=keybuffer[0]*10000000+keybuffer[1]*1000000+keybuffer[2]*100000+k eybuffer[3]*10000+keybuffer[4]*1000+keybuffer[5]*100+keybuffer[6]*10+keybuffer [7];//合成输入频率值setdispbuf=freword;freword=(unsigned long)(freword*214.7493648);//计算相应的频率字longtochar[0]=(freword>>24)&0xff; //频率字最高八位longtochar[1]=(freword>>16)&0xff; //频率字次高八位longtochar[2]=(freword>> 8)&0xff; //频率字次低八位longtochar[3]=(freword) &0xff; //频率字最低八位}//-----------select channel-----------------------void select(unsigned char sel){unsigned char i,j;j=sel;sel=sel&0x07;i=P1;i=i&0xf8;i=i|sel;P1=i;}//-----------setting frequency--------------------void setfre(void){unsigned char i;keytofreword();display(setdispbuf,1); //显示输入的频率值lcd_str(0,2,"--setting.fre!-");oe=0;load_dds=0;for(i=0;i<4;i++){select(i);P3=longtochar[i];_nop_();_nop_();_nop_();load_dds=1;_nop_();_nop_();_nop_();load_dds=0;}lcd_str(0,2,"--setting.succ!-");}//----------test frequency------------------------void testfre(void){unsigned char i;unsigned int j;lcd_str(0,2,"--testing.fre---");bena=0;clr=0;_nop_();_nop_();_nop_();_nop_();clr=1; //-----clear register--------清零bena=1; //允许频率计开始工作delay1ms_x(1000); //门控时间2Sdelay1ms_x(1000);bena=0; //------count until start equals 0------------j=10000;while((start==1)&&(j--)); //----wait for end of testting or time out--- if(j==0)lcd_str(0,2,"--test.fre.err!-");elselcd_str(0,2,"-test.fre.succ!-");oe=1; //双向口for(i=0;i<8;i++){select(i);P3=0xff; //P3作为输入口_nop_();_nop_();_nop_();_nop_();recieve[i]=P3; //读取频率计计数值}oe=0;bfrecount=0;tfrecount=0;for(i=0;i<4;i++){bfrecount=(bfrecount<<8)+recieve[i]; //合成标准频率计数值tfrecount=(tfrecount<<8)+recieve[i+4]; //合成待测频率计数值}tfrecount=(unsigned long)tfrecount/3.5200886+1;//??????display(tfrecount,0);}//-------------------scan key value-------------------------unsigned char scankey(void) //键盘扫描{unsigned char i=0xff,k=0xfe,buf;unsigned code table[4]={0xfe,0xfd,0xfb,0xf7};for(i=0;i<4;i++){P1=table[i];buf=P1;if(buf!=table[i]){delay(1000);if(buf==P1){while(buf==P1);break;}}}switch(buf){case 0xee: return 1;case 0xed: return 2;case 0xeb: return 3;case 0xe7: return 10; //4case 0xde: return 4;//5case 0xdd: return 5;//6case 0xdb: return 6;//7case 0xd7: return 11; //8case 0xbe: return 7;//9case 0xbd: return 8;//0case 0xbb: return 9;//11case 0xb7: return 12;//12case 0x7e: return 13;//13case 0x7d: return 0;//14case 0x7b: return 14;//15case 0x77: return 15;//16default : return 16;//10}P1=0xff;}//-----------------key execution----------------------- void keyexe(void){unsigned char i,buf;buf=scankey(); //调键盘扫描,读取键值switch(buf){case 0:case 1:case 2:case 3:case 4:case 5:case 6:case 7:case 8:case 9: for(i=0;i<7;i++)keybuffer[i]=keybuffer[i+1];keybuffer[7]=buf;lcd_data1(0,1,'i');lcd_data1(1,1,'n');lcd_data1(2,1,'p');lcd_data1(3,1,'u');lcd_data1(4,1,'t');lcd_data1(5,1,':');lcd_data1(6,1,keybuffer[0]+'0');lcd_data1(7,1,keybuffer[1]+'0');lcd_data1(8,1,keybuffer[2]+'0');lcd_data1(9,1,keybuffer[3]+'0');lcd_data1(10,1,keybuffer[4]+'0');lcd_data1(11,1,keybuffer[5]+'0');lcd_data1(12,1,keybuffer[6]+'0');lcd_data1(13,1,keybuffer[7]+'0');lcd_data1(14,1,'H');lcd_data1(15,1,'z');break;case 10: lcd_cmd(clear);setfre();break;case 11: testfre();break;case 12: for(i=0;i<8;i++){keybuffer[i]=0;lcd_data1(i+6,1,keybuffer[i]+'0');}lcd_data1(14,1,'H');lcd_data1(15,1,'z');break;default: break;}}#endif。

基于cpld的简易数字频率计的设计

基于cpld的简易数字频率计的设计

基于CPLD的简易数字频率计的设计如下:

首先,将CPLD作为主控芯片,实现信号的采集、处理和控制。

通过输入的信号,经过滤波器去除噪音和干扰,然后使用计数器模块对输入信号的频率进行测量。

计数器模块将信号的周期转换成相应的脉冲数,再通过单片机进行数据处理,计算出信号的频率。

其次,利用单片机进行数据处理和显示。

单片机通过接收计数器模块的脉冲数,根据测量公式计算出信号的频率,并将结果显示在LCD屏幕上。

同时,单片机还负责控制CPLD的工作流程,实现整个系统的协调工作。

最后,通过仿真和测试验证设计的正确性和可行性。

测试结果表明,该数字频率计具有测量精度高、抗干扰能力强、稳定性好等优点,可以广泛应用于各种需要测量频率的场合。

基于CPLD的简易数字频率计的设计方法包括硬件设计和软件设计两部分。

硬件设计主要是利用CPLD和单片机等芯片进行电路设计和搭建;软件设计主要是利用CPLD编程语言和单片机编程语言进行程序编写和调试。

在实际应用中,需要根据具体需求和条件进行选择和调整。

cpld频率计课程设计

cpld频率计课程设计一、课程目标知识目标:1. 理解 CPLD 的基本概念、结构和工作原理;2. 掌握频率计的设计原理和实现方法;3. 学会运用 CPLD 技术设计简单的数字电路系统。

技能目标:1. 能够运用 CPLD 设计并实现一个功能完整的频率计;2. 培养学生动手实践能力,提高电路搭建和调试技巧;3. 提高学生分析问题、解决问题的能力。

情感态度价值观目标:1. 培养学生热爱科学,积极探索的精神;2. 培养团队合作意识,增强沟通与协作能力;3. 提高学生的创新意识,激发创新潜能。

课程性质:本课程为电子信息类专业的实践课程,旨在让学生通过实际操作,掌握 CPLD 技术及其在数字电路设计中的应用。

学生特点:学生已具备一定的电子技术和数字电路基础知识,具有一定的动手能力和探究精神。

教学要求:结合课程特点和学生实际情况,注重理论与实践相结合,强调实践操作和创新能力培养,确保学生能够达到课程目标所要求的知识和技能水平。

通过课程学习,使学生能够将所学知识应用于实际工程设计中,提高学生的职业素养和综合能力。

二、教学内容1. CPLD 基础知识回顾:CPLD 的基本概念、结构、工作原理及其特点,涉及课本第三章第一、二节内容。

2. 频率计设计原理:频率计的工作原理、电路组成和设计方法,包括课本第四章第三节内容。

3. CPLD 设计流程:设计输入、综合、布局布线、仿真和下载等步骤,参考课本第五章内容。

4. 频率计电路设计:使用 CPLD 设计频率计电路,包括时钟信号产生、计数器、显示驱动等模块,结合课本实例进行讲解。

5. 实践操作:分组进行频率计电路的搭建、调试和测试,培养学生动手实践能力。

6. 教学大纲:(1)第1周:CPLD 基础知识回顾,频率计设计原理学习。

(2)第2周:CPLD 设计流程讲解,频率计电路设计方法学习。

(3)第3周:分组进行频率计电路设计,教师指导与答疑。

(4)第4周:实践操作,完成频率计电路搭建、调试和测试。

基于CPLD的数字频率计的设计实现

基于 C L P D的 数 字 频 率计 的 设 计 实现

耿兴 隆, 李振川 , 马晓涛

( 北 软 件 职 业技 术 学 院 。 北 保 定 0 10 ) 河 河 7 0 0

摘要 : 频率计是常用的测量仪器 , 它通过对单位 时间内的信 号脉冲进行计 数测量 出信 号的频率。 L tc 用 ai t e公司生产 的

种 , 设 计介 绍 了使 用 一 片 IP S13 本 S L I02芯 片来

2 软 件 设 计

频率计工作时 , 先要产生一个计数允许信号 , 即闸门信号 , 闸门信号的宽度为单位时间, 例如 1 S 或 10m 。 闸门信号有效 的时 间内对被测信号 0 s 在 计数 , 即为信号频率 。 测量过程结束 , 需要锁存计

设 计数 字频率 计 的硬件 电路 和软 件设 计方 法 。 本设 计 为一 个 6位 数 字 频 率 计 , 以 测 量 1 9 9 可 9999

H 的信号频率。 z 设计过程主要分为 : 硬件设计 、 软 件设 计两 部分 。

收稿 日期 :0 0 0 — 2 2 1— 5 1

作者简介 : 耿兴隆(9 2 ) 男, 1 8一 , 河北衡水人 , 助教 , 在读工程硕士 , 要从 事嵌 入式系统、 主 数据 库和计算机控制等方 面的研 究; 李振川(9 0 )男 , 18 一 , 河北 辛集人 , 助教, 主要从事建筑工程 、 计算机 等方面的研 究。

5 2

河 北 软 件 职 业 技 术 学 院 学 报

语言 生成 相应的 目标 文件 , 过下载 电缆将代 码传送 到 目 通 标芯片 中进而完成设计的数字 系统 。 该方法设计灵活 , 便于

实现 。

为 1M z 脉冲发生器芯 片采用 C 4 6 。 D 00 0 h, D 0 0 C 46

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

wae c ru t e in i u i gt e C L e h oo y w i e d sg f n— ma h n n efc n ot r rg a o efe u n y me r i i d s s sn P D tc n lg hl t e in o c g h eh ma ・ c i ei tra e a d s f wa ep o r m f h r q e c - t -

Abs r t te e tng o r wae a ot r rs a c m p e o tac :Af rtsi fhad r nd s fwae pat , o lx c mprh nsv x e me sc mp ee n t i p r e e ie e p r nti o l td i h spa i e ,wh s a d oe h r—

维普资讯

第 6卷

第 2期

实 验 科 学 与 技 术

・l 3・

CL P D和 虚 拟 仪 器 的 频 率 计 综 合 设 计

詹 惠琴 ,古 军

( 电子科技大学 自动化工程学院 ,成都 6 05 ) 10 4

摘 要 :在 自制 的 虚 拟 仪 器 实验 箱 和 C L 实验 板及 通 用计 算 机 上 ,采 用 C L 技 术 设 计 了测 量 频 率 的 硬 件 电路 和 虚 拟 仪 器 PD PD 的 Lb IW 图形 语 言 开发 平 台 ,设 计 了频 率计 的 人 机 界 面 和软 件 程 序 ;通 过 软 硬 件 调 试 和 测试 , 完成 了一 个 较 复 杂 的 综 合 aV E 性 、设 计 性 实验 。 文 中的 实验 综合 应 用 了电子 测 量 原 理 、数 字 电路 技 术 、C L 术 、虚 拟仪 器 、程 序 设 计 等 课 程 的 知 识 P D技

s n n s in v t e ne si g d a c d e p o aie fe e u i g o u d a hn ,ah e a c ia n d l rd sg sa i i g i n o a v ,i tr t ,a v e a x l rt .A t r sn fg i et c i g ir rh c a d mo u a e in i - g i e n n d n v h t e l d pe o td,w ih ma e t e e p r n r p r t e a d o ih p bi i . h c d h x i e me tmo e o ai hs u l t e v n f cy Ke r s:s n e i x rme t y wo d y t sse p i n ;CP D d s n;vr a n t me t me u rq e c h e L ei g i u i sr tl u n; s e a r fe u n y

中图分类号 :T 9 ;T 3 1 M33 P 1

文献标识码 :A

文章编号 :17 45 (0 8 0 0 1 0 62— 5 0 2 0 )2— 0 3— 4

A e u n y M e e p rm e twih S n h ss a d De i n Fr q e c t r Ex e i n t y t e i n sg

Ba e o s n CPLD n ru lI sr m e t a d Vit a n tu n

Z N Hu— i ,GU J n HA iqn u

( ol eo uo ai ,U i ri fEet ncSineadTc nl yo hn ,C egu 6  ̄ 5 C lg f tm t n nv syo l r i c c n ehoo f ia hnd 1 4,C ia e A o e t co e g C hn )

和技 术,理论结合 实际,其设计思想新颖 ,具有启发性 、设计性 、趣味性 、先进性 、探 索性 等特点。分析过程 中应 用引导

式教 学 ,进 行 了层 次 化 、模 块 化 设 计 ,使 实验 更 具 可 操 作 性 和 推 广 意 义 。 关 键 词 :综 合 实验 ;C L P D设 计 ;虚 拟 仪 器 ;频 率测 量

me u m n , i t i ut C L Vr a isu n , r a ei ig e . hoy on t i rc c , i t u h o — se a r et D ga c ci, P D, iu t met Po m D s nn , t T er cn e e wt pat e t sh gt f e i lr tl n r s r g g c cd h i h o d

t ra eba e n t e G a g a e La e r s d o l n u g bVI h EW fv ru lisr me t .Th se p rme s b s d o h o it a n tu n s i x i nti a e n t e CPLD h p o h it a n tu nt e c i rt e v ru li sr me s e pe me tb x a d g ne a o utr The e e rme ti e ae ai u n wl g n e hn lg e s c s Prn i l f ee to i x r i n o n e rlc mp e . xp i n ntg td v ro s k o e e a d t c oo is. u h a i c p e o l cr n c r d