Xilinx All Programmable SoC Zynq7000 总结(2)PPT课件

ZYNQ_嵌入式软件开发

Example: Xapp1078 : Linux / Bare-metal AMP Xapp1079 : Bare-metal / Bare-metal AMP More info Refer to:

/Multi-OS+Support+(AMP+%26+Hypervisor)

FSBL工程根据XPS的XML文档选择需要的BSP驱动,并生 成ps7_init.c文件

相关文档: /support/documentation/user_g uides/ug821-zynq-7000-swdev.pdf

Page 8

Zynq-7000 Bootgen and BIF file format

Bootgen

A standalone tool for creating a bootable image suitable for the Zynq7000 AP SoC processor. The program assembles the boot image by prefixing a header block to a list of partitions. Each partition can be optionally encrypted and authenticated.

Page 3

Zynq-7000 开发工具 ---- XPS

XPS 可实现完整 的配置和定制操 作

管理 Zynq-7000 AP SoC 外设 IO 引脚启动配置和 初始化

器件安全、回读引 导和比特流管理 措施 项目专用配置感 知 无需用户掌握具 体硬件知识 利用可展开的软 件图自动构建一 级引导载入程序

Page 13

Zynq-7000 Power Management

基于Zynq—7000的多种以太网实现方案

基于Zynq—7000的多种以太网实现方案作者:刘佳钱瑞杰李洋来源:《中国科技纵横》2017年第09期摘要:Zynq是Xilinx公司推出的第一个可扩展处理平台,将双核ARMCortex A9处理器与可编程逻辑架构结合,充分体现软硬件协同设计。

以太网是当今通信领域广泛应用的接口,在Zynq中提供了两路千兆以太网控制器,结合MIO、EMIO、AXI、PL等资源,可提供多种以太网实现方案。

关键词:Zynq可扩展处理平台;软硬件协同设计;以太网中图分类号:TP391.41 文献标识码:A 文章编号:1671-2064(2017)09-0040-021 引言随着技术的发展,SOC受到了更多人的关注和推行,Xilinx公司的Zynq作为该领域的领跑者,已被运用到许多场合。

Zynq-7000 系列基于 Xilinx 的可扩展处理平台结构,在单芯片内集成了具有丰富特点的双核 ARM Cortex A9处理器系统(Processing System,PS)和 Xilinx可编程逻辑(Programmable Logic,PL)。

其中,Cortex A9 双核处理器是整个架构的核心,外部存储器接口、及丰富的外设资源都挂载在 ARM上,PL可看做完全可编程的外设。

本文基于以太网接口的大量使用,充分考虑到不同应用场景接口形态的差异,如光口以太网、电口以太网。

结合Zynq所具备的丰富设计资源,提出了基于Zynq-7000的多种以太网实现方案。

2 方案原理Zynq-7000内部有很多常见的I/O外设和存储器接口,是PS的重要组成部分。

这些外设包括GPIO、USB控制器、SPI控制器、UART控制器、千兆以太网控制器等。

这些外设除具备通用功能外,还针对Zynq-7000做了改动。

使其能很好的支持PS+PL的架构,灵活使用PL。

Zynq-7000中还提出了两个新概念,MIO(Multiuse I/O)和EMIO(Extendable Multiplexed I/O)。

XilinxZYNQ-7000平台简介

XilinxZYNQ-7000平台简介平台介绍Zynq7000是赛灵思公司(Xilinx)推出的⾏业第⼀个可扩展处理平台Zynq系列。

旨在为视频监视、汽车驾驶员辅助以及⼯⼚⾃动化等⾼端嵌⼊式应⽤提供所需的处理与计算性能⽔平。

在2010年4⽉硅⾕举⾏的嵌⼊式系统⼤会上,赛灵思发布了可扩展处理平台的架构详情,这款基于⽆处不在的ARM处理器的SoC可满⾜复杂嵌⼊式系统的⾼性能、低功耗和多核处理能⼒要求。

赛灵思可扩展处理平台芯⽚硬件的核⼼本质就是将通⽤基础双ARMCortex-A9MPCore 处理器系统作为“主系统”,结合低功耗28nm⼯艺技术,以实现⾼度的灵活性、强⼤的配置功能和⾼性能。

由于该新型器件的可编程逻辑部分基于赛灵思28nm7系列FPGA,因此该系列产品的名称中添加了“7000”,以保持与7系列FPGA的⼀致性,同时也⽅便⽇后本系列新产品的命名。

Zynq-7000系列的可编程逻辑完全基于赛灵思7系列FPGA架构来设计,可确保28nm系列器件的IP核、⼯具和性能100%兼容。

最⼩型的Zynq-7000、Zynq-7010和Zynq-7020均基于专门针对低成本和低功耗优化的Artix-7系列;较⼤型的Zynq-7030和Zynq-7040器件基于包括4⾄12个10.3Gbps收发器通道,可⽀持⾼速⽚外连接的中端Kintex-7系列。

所有四款产品均采⽤基于2个12位1MspsADC(模数转换器)模块的新型模拟混合信号模块。

Zynq®-7000 SoC 系列集成 ARM® 处理器的软件可编程性与 FPGA 的硬件可编程性,不仅可实现重要分析与硬件加速,同时还在单个器件上⾼度集成 CPU、DSP、ASSP 以及混合信号功能。

Zynq-7000 系列包括单核 Zynq-7000S 器件和双核 Zynq-7000 器件,是单位功耗性价⽐最⾼的全⾯可扩展的 SoC 平台,可充分满⾜您的独特应⽤需求。

ZYNQ7000开发平台用户手册说明书

文档版本控制目录文档版本控制 (2)一、开发板简介 (6)二、AC7Z020核心板 (8)(一)简介 (8)(二)ZYNQ芯片 (9)(三)DDR3 DRAM (11)(四)QSPI Flash (14)(五)时钟配置 (16)(六)电源 (17)(七)结构图 (18)(八)连接器管脚定义 (19)三、扩展板 (23)(一)简介 (23)(二)CAN通信接口 (24)(三)485通信接口 (24)(四)千兆以太网接口 (25)(五)USB2.0 Host接口 (27)(六)USB转串口 (28)(七)AD输入接口 (29)(八)HDMI输出接口 (30)(九)MIPI摄像头接口(仅AX7Z020使用) (32)(十)SD卡槽 (33)(十一)EEPROM (34)(十二)实时时钟 (34)(十三)温度传感器 (35)(十四)JTAG接口 (36)(十五)用户LED灯 (36)(十六)用户按键 (37)(十七)扩展口 (38)(十八)供电电源 (40)(十九)底板结构图 (41)芯驿电子科技(上海)有限公司 基于XILINX ZYNQ7000开发平台的开发板(型号: AX7Z020B )2022款正式发布了,为了让您对此开发平台可以快速了解,我们编写了此用户手册。

这款ZYNQ7000 FPGA 开发平台采用核心板加扩展板的模式,方便用户对核心板的二次开发利用。

核心板使用XILINX 的Zynq7000 SOC 芯片的解决方案,它采用ARM+FPGA SOC 技术将双核ARM Cortex-A9 和FPGA 可编程逻辑集成在一颗芯片上。

另外核心板上含有2片共512MB 高速DDR3 SDRAM 芯片和1片256Mb 的QSPI FLASH 芯片。

在底板设计上我们为用户扩展了丰富的外围接口,比如2路CAN 通信接口,2路485通信接口,2路XADC 输入接口, 1路千兆以太网接口,1路USB2.0 HOST 接口,1路HDMI输出接口,Uart 通信接口,SD 卡座,40针扩展接口等等。

无线应用AMP与SMP的区别以及赛灵思Zynq 7000的应用

无线应用AMP与SMP的区别以及赛灵思Zynq 7000

的应用

随着无线数据吞吐量的爆炸式增长,数字信号处理技术和无线电设备在改进方面面临着巨大压力。

目前的重点放在4G LTE。

4G网络正在世界各地大规模部署。

而且现在我们看到5G网络的早期研发工作也已经展开,其目标

是在4G网络的基础上将数据容量再提升上千倍。

这种新兴的技术发展给系

统厂商提出了不断发展变化的新要求他们必须提升系统集成度和系统性能,

降低系统材料清单(BOM)成本,提高设计灵活性,并加速产品上市进程等。

传统ASIC器件支持的硬件解决方案虽然可以实现功耗和成本目标,但偶生工程成本(NRE)极高、灵活性差且产品上市进程非常缓慢。

为了满足这

些要求并应对这些挑战,赛灵思向行业推出了All Programmable SoC架构,并将其成功实现在Zynq-7000产品系列中。

Zynq-7000器件采用赛灵思SoC架构并通过硬件、软件和I/O可重编程功能可实现更大的系统级差异化、更高的集成度和灵活性(图1)。

Zynq-7000

器件自2011年12月推出以来,已广泛应用于通信、数据中心、汽车、工业、航空航天与国防等众多市场领域。

对通信市场(尤其是无线应用领域)而言,Zynq-7000带来了独特的优势:其集成式可编程逻辑(PL)专门针对数字信

号处理进行了精心优化;其ARM Cortex A9处理子系统(PS)能够高效实现。

Xilinx Vivado zynq7000 入门笔记

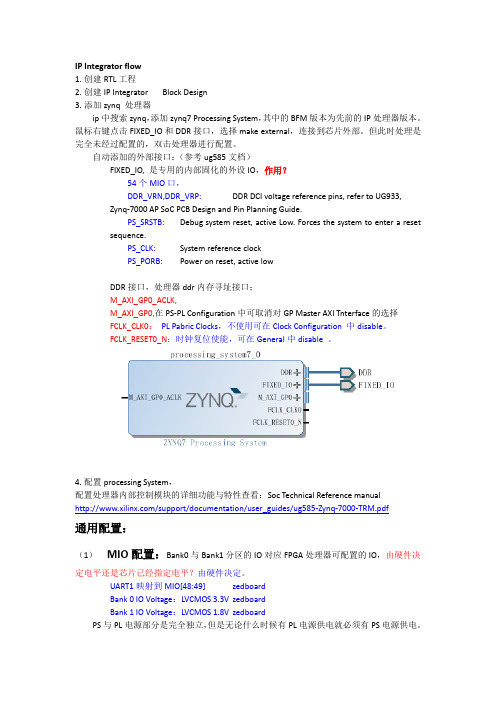

IP Integrator flow1.创建RTL工程2.创建IP Integrator Block Design3.添加zynq 处理器ip中搜索zynq,添加zynq7 Processing System,其中的BFM版本为先前的IP处理器版本。

鼠标右键点击FIXED_IO和DDR接口,选择make external,连接到芯片外部。

但此时处理是完全未经过配置的,双击处理器进行配置。

自动添加的外部接口:(参考ug585文档)FIXED_IO, 是专用的内部固化的外设IO,作用?54个MIO口,DDR_VRN,DDR_VRP: DDR DCI voltage reference pins, refer to UG933, Zynq-7000 AP SoC PCB Design and Pin Planning Guide.PS_SRSTB: Debug system reset, active Low. Forces the system to enter a reset sequence.PS_CLK: System reference clockPS_PORB: Power on reset, active lowDDR接口,处理器ddr内存寻址接口;M_AXI_GP0_ACLK,M_AXI_GP0,在PS-PL Configuration中可取消对GP Master AXI Tnterface的选择FCLK_CLK0:PL Pabric Clocks,不使用可在Clock Configuration 中disable。

FCLK_RESET0_N:时钟复位使能,可在General中disable 。

4.配置processing System,配置处理器内部控制模块的详细功能与特性查看:Soc Technical Reference manual/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf通用配置:(1)MIO配置:Bank0与Bank1分区的IO对应FPGA处理器可配置的IO,由硬件决定电平还是芯片已经指定电平?由硬件决定。

Zynq7000系列之芯片引脚功能综述

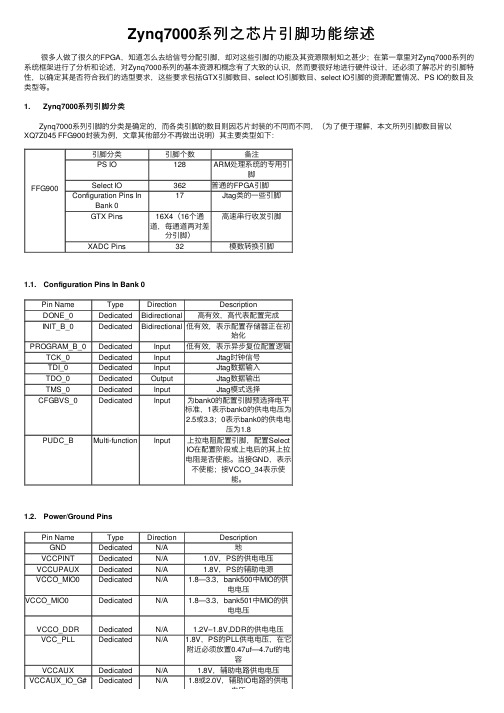

Zynq7000系列之芯⽚引脚功能综述很多⼈做了很久的FPGA,知道怎么去给信号分配引脚,却对这些引脚的功能及其资源限制知之甚少;在第⼀章⾥对Zynq7000系列的系统框架进⾏了分析和论述,对Zynq7000系列的基本资源和概念有了⼤致的认识,然⽽要很好地进⾏硬件设计,还必须了解芯⽚的引脚特性,以确定其是否符合我们的选型要求,这些要求包括GTX引脚数⽬、select IO引脚数⽬、select IO引脚的资源配置情况、PS IO的数⽬及类型等。

1. Zynq7000系列引脚分类 Zynq7000系列引脚的分类是确定的,⽽各类引脚的数⽬则因芯⽚封装的不同⽽不同,(为了便于理解,本⽂所列引脚数⽬皆以XQ7Z045 FFG900封装为例,⽂章其他部分不再做出说明)其主要类型如下:FFG900引脚分类引脚个数备注PS IO128ARM处理系统的专⽤引脚Select IO362普通的FPGA引脚Configuration Pins InBank 017Jtag类的⼀些引脚GTX Pins16X4(16个通道,每通道两对差分引脚)⾼速串⾏收发引脚XADC Pins32模数转换引脚1.1. Configuration Pins In Bank 0Pin Name Type Direction DescriptionDONE_0Dedicated Bidirectional⾼有效,⾼代表配置完成INIT_B_0Dedicated Bidirectional低有效,表⽰配置存储器正在初始化PROGRAM_B_0Dedicated Input低有效,表⽰异步复位配置逻辑TCK_0Dedicated Input Jtag时钟信号TDI_0Dedicated Input Jtag数据输⼊TDO_0Dedicated Output Jtag数据输出TMS_0Dedicated Input Jtag模式选择CFGBVS_0Dedicated Input为bank0的配置引脚预选择电平标准,1表⽰bank0的供电电压为2.5或3.3;0表⽰bank0的供电电压为1.8 PUDC_B Multi-function Input上拉电阻配置引脚,配置SelectIO在配置阶段或上电后的其上拉电阻是否使能。

Zynq-7000最小系统设计及无DDR3固化运行方法

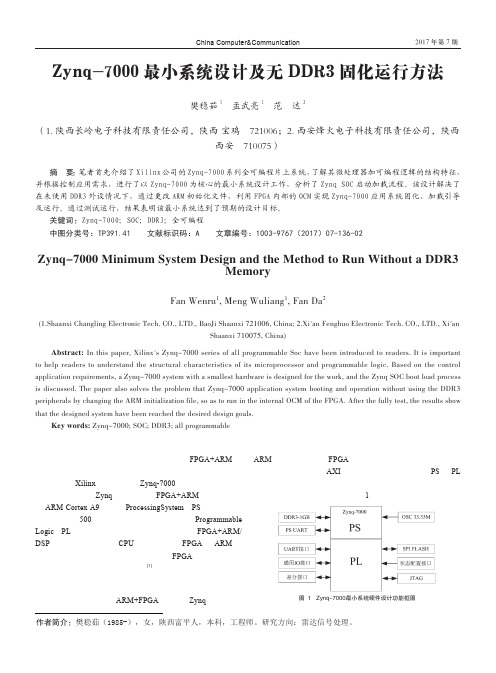

图1 Zynq-7000最小系统硬件设计功能框图樊稳茹(1985-),女,陕西富平人,本科,工程师。

研究方向:雷达信号处理。

2017年第7期信息与电脑China Computer&Communication软件开发与应用该最小系统PS部分结合用户应用程序用于实现控制功能,PL部分包括UART接口、时序产生、地址译码、片上存储和外设控制等逻辑功能模块。

主要的功能芯片为X7Z045、MT41K256M16HA、MAX3160E、MAX3096、MAX3045、W25Q128、ADG3308等,为了降低硬件成本,在满足使用需求的条件下,该最小系统设计时取消了图1中虚线框中的DDR3存储器。

2 基本启动配置流程分析Zynq是一个可扩展处理平台,简单地说就是有个FPGA 做外设的A9双核处理器,所以它的启动流程与FPGA完全不同,而与ARM处理器类似。

Zynq支持JTAG、NAND、Parallel NOR、QSPI以及SD卡等启动方式。

Zynq有效利用了片上的CPU来帮助配置,在没有外部JTAG的情况下,处理器系统(PS)与可编程逻辑(PL)都必须依靠PS来完成芯片的初始化配置,内部的启动存储区(BootROM)和芯片配置单元可实现Zynq从BootROM主动启动或者从JTAG被动启动[2]。

与其他XILINX 7系列的器件不同的是,Zynq并不支持从PL端直接进行启动配置,Zynq的启动配置是分多级进行的,配置过程最少需要两步,但通常是按如下三个阶段进行。

阶段0(Stage0):简称BootROM,控制着整个芯片的初始化过程。

该部分代码是不可修改的,处理器核在上电或者热启动时自动执行这部分代码,并对外部的NAND、NOR、SD等外设控制器进行初始化,同时还负责将阶段1的启动镜像(FSBL镜像)加载到OCM(Zynq片上一个256K的RAM,但在FSBL运行前只能使用其中的192K,所以FSBL要小于192K),然后运行FSBL,FSBL镜像来源由板上MIO[5:3]引脚选择的启动方式决定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Zc702定制IP的设计流程

基于产生的IP模板,需要修改处理器外设定义MPD文件、IP RTL 文件 led_ip.hdl 和user_logic.v

MPD在pcores\lcd_ip_v1_00_a\data子目录

led_ip.hdl在 pcores\lcd_ip_v1_00_a\hdl\vhdl子目录

6

创建LED_IP

Zc702定制IP的设计流程

Create Peripheral-(Optional)Peripheral Simulation Support界面,用默认配置,Next 出现如下图所示的界面,使用Verilog编辑代码,要选中Verilog instead VHDL 出现如下图所示的Create Peripheral-Congratulations界面,点 “Finish”完成

Language :C OS Platform:Standalone; 选择Create New:empty_application_0_bsp; 选择Empty Application模板。 Finish 。

主要内容

Zynq 7000平台简介 Zc702基本系统的建立和运行 Zc702定制IP的设计流程 基于Zc702的linux3.3系统移植

基于Zc702的 Android2.3系统移植

1

Zc702 定制IP设计

Zc702定制IP的设计流程

目标

介绍定制IP核的设计流程 基于定制IP核应用程序的设计方法

将LED_IP作为外设添加到AXI总线,需要以下几步:

添加和连接LED_IP外设到AXI总线。 使led_ip的用户定义的逻辑端口和外部端口连接。 并给led_ip定制外设分配地址。 在system.ucf中添加PL引脚约束

11

Zc702定制IP的设计流程

修改外设LED_IP的软件驱动

在\drivers\led_ip_v1_00_a\src 目录下,打开led_ip_selftest.c文件,将#include “xio.h”改成#include “xil_io.h”

Create Peripheral-Bus Interface界面,在该界面下选择AXI-Lite:Simpler,non-burst control register style interfaceLeabharlann 4创建LED_IP

Zc702定制IP的设计流程

端口说明

AXI-Lite:为简单的,非猝发控制器类型的接口。 AXI4:有猝发能力,高吞吐量、存储器映射类型的 接口。 AXI-Stream:有猝发能力,高吞吐量的流接口。 Processor Local Bus(PLB v4.6):处理器本地接口。 Fast Simplex Link(FSL):快速简单连接接口。

具

出现Select a workspace界面,在该界面内给出软件设计的路径。

新建测试软件主要步骤:

在SDK主界面下选择File->New->Application Project选项,创建新工程

New Project界面,按如下设置参数

Project name:empty_application_0;

步骤

通过使用Create and Import Peripheral Wizard设计工具,定制一个基于AXI-Lite规范 的 IP核模板

基于IP核模板,添加自定义AXI_LED_IP核,并编译 添加定制的AXI LED IP到处理器系统中,用该IP核控制Zc702板子上的8个LED实现不

同的闪烁效果 为该定制的IP核添加BSP,并编写应用程序

2

创建LED_IP

Zc702定制IP的设计流程

定制LED_IP包括

产生LED_IP设计模板 修改LED_IP设计模板

创建LED_IP模板

XPS主界面主菜单下,选择Hardware->Create or Import Peripheral启动向导 选Create and Import Peripheral Wizard对话框界面,-> Create templates for a new

在下界面中不选择Include data phase timer

5

创建LED_IP

Zc702定制IP的设计流程

在下图的Create Peripheral-User S/W Register界面,按下面设置AXI寄存器个数: 软件可访问寄存器个数为2

出现下图所示的Create Peripheral-IP Interconnect界面,显示了默认的接口信号,使用 这些默认信号即可,Next

User_logic.v在 pcores\lcd_ip_v1_00_a\hdl\verilog子目录

9

完善LED_IP

Zc702定制IP的设计流程

user_logic.v

10

添加AXI外设LED_IP

Zc702定制IP的设计流程

LED_IP的修改后,需Rescan

在XPS主界面,选择Project->Rescan User Repositories。

添加#define LED_IP_USER_NUM_REG 2定义

12

Zc702定制IP的设计流程

导入硬件设计到SDK及软件设计

导入硬件设计主要步骤:

在XPS主界面下,选择Project-> Export Hardware Design to SDK.. 点击“Export & Launch SDK”,将XPS的硬件设计导入到SDK,并启动SDK软件工

peripheral , -> To an XPS project ,next

3

创建LED_IP

Zc702定制IP的设计流程

在Create Peripheral-Name and Version,在name后面输入led_ip(该名字为IP核的名字, 即led_ip_v1.00a),其它使用默认配置,点 “Next”

7

创建LED_IP

Zc702定制IP的设计流程

LED_IP模板设计完成,在XPS主界面内,点击IP Catalog标签,在该标签界面下,可以 找到LED_IP如下图所示:

在./pcores/ed_ip_v1_00_a目录下保存LED_IP信息,文件结构如图

vhdl verilog

8

完善LED_IP