KBP206 KBP 系列规格书推荐

ASEMI整流桥KBP206参数,KBP206规格,KBP206应用

ASEMI整流桥KBP206参数,KBP206规格,KBP206应⽤编辑-Z

ASEMI整流桥KBP206参数:

型号:KBP206

最⼤重复峰值反向电压(VRRM):600V

最⼤RMS电桥输⼊电压(VRMS):420V

最⼤直流阻断电压(VDC):600V

最⼤平均正向整流输出电流(IF(AV)):2.0A

峰值正向浪涌电流(IFSM):60A

每个元件的典型热阻(ReJA):10℃/W

每个元件的典型结电容(Cj):25pF

⼯作结和储存温度范围(TJ, TSTG):-55 to +150℃

最⼤瞬时正向压降(VF):1.1V

最⼤直流反向电流(IR):10uA

KBP206规格尺⼨:

总长度:23.9mm

本体长度:11.2mm

引脚长度:12.7mm

宽度:14.7mm

⾼度:3.73mm

脚间距:3.85mm

KBP206特征:

印刷电路板安装的理想选择

使⽤的塑料材料带有美国保险商实验室可燃性识别94V-0

内置印刷电路板⽀架

⾼外壳介电强度

⾼温焊接保证265/10秒

KBP206机械数据:

外壳:利⽤可靠的低成本建设模塑技术

端⼦:根据MIL-STD-202可焊接的电镀引线

安装位置:任意

重量:0.065盎司,2.2克(约)。

整流桥KBL08 KBL封装系列规格书推荐

深圳理悠科技有限公司

KBL005 THRU KBL10

SILICON BRIDGE RECTIFIERS

Reverse Voltage - 50 to 1000 Volts Forward Current - 4.0 Amperes

KBL

0.768(19.5) 0.728(18.5)

RθJA

Operating junction temperature range

TJ

storage temperature range

TSTG

10 1.0 105 20 -65 to +150 -55 to +150

NOTES: 1.Measured at 1.0 MHz and applied reverse voltage of 4.0 Volts. 2.Unit mounted on 3.0” x 3.0” x 0.11” thick(7.5x7.5x0.3cm) Al. plate. 3.P.C.Board mounted with 0.5” x0.5”(12x12mm) copper pads,0.375”(9.5mm) lead length.

Dimensions in inches and (millimeters)

MECHANICAL DATA

Case: Molded plastic body Terminals: Plated leads solderable per MIL-STD-750, Method 2026 Polarity: Polarity symbols marked on case Mounting Position: Any Weight:0.22 ounce, 6.21 grams

常见集成整流桥的各种封装以及型号

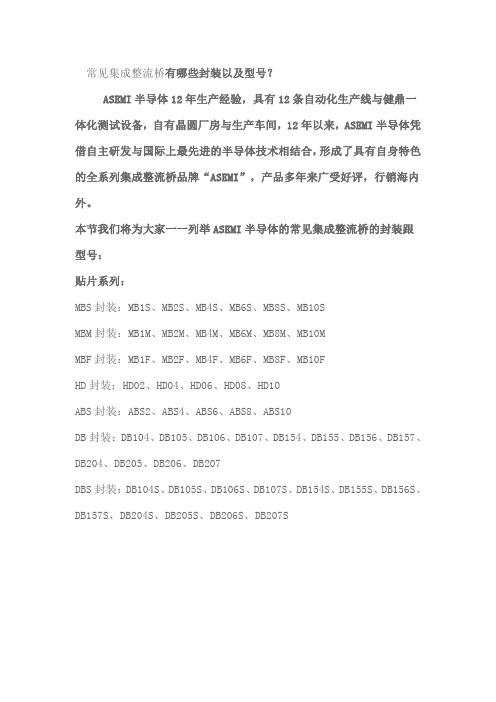

常见集成整流桥有哪些封装以及型号?ASEMI半导体12年生产经验,具有12条自动化生产线与健鼎一体化测试设备,自有晶圆厂房与生产车间,12年以来,ASEMI半导体凭借自主研发与国际上最先进的半导体技术相结合,形成了具有自身特色的全系列集成整流桥品牌“ASEMI”,产品多年来广受好评,行销海内外。

本节我们将为大家一一列举ASEMI半导体的常见集成整流桥的封装跟型号:贴片系列:MBS封装:MB1S、MB2S、MB4S、MB6S、MB8S、MB10SMBM封装:MB1M、MB2M、MB4M、MB6M、MB8M、MB10MMBF封装:MB1F、MB2F、MB4F、MB6F、MB8F、MB10FHD封装:HD02、HD04、HD06、HD08、HD10ABS封装:ABS2、ABS4、ABS6、ABS8、ABS10DB封装:DB104、DB105、DB106、DB107、DB154、DB155、DB156、DB157、DB204、DB205、DB206、DB207DBS封装:DB104S、DB105S、DB106S、DB107S、DB154S、DB155S、DB156S、DB157S、DB204S、DB205S、DB206S、DB207S圆桥系列:WOB封装:W04、W06、W08、W10、2W04,2W06,2W08,2W10RB封装:RB154、RB155、RB156、RB157扁桥系列:KBP封装:KBP2005、KBP201、KBP202、KBP204、KBP206、KBP208、KBP210 RS封装:RS201、RS202、RS203、RS204、RS205、RS206、RS207KBP封装:RS301、RS302、RS303、RS304、RS305、RS306、RS307KBL封装:KBL4005、KBL401、KBL402、KBL404、KBL406、KBL408、KBL410 GBU封装:GBU4005、GBU401、GBU402、GBU404、GBU406、GBU408、GBU410 KBJ封装:KBJ4005、KBJ401、KBJ402、KBJ404、KBJ406、KBJ408、KBJ410 KBU封装:KBU6005、KBU601、KBU602、KBU604、KBU606、KBU608、KBU610 GBU封装:GBU6005、GBU601、GBU602、GBU604、GBU606、GBU608、GBU610 KBJ封装:KBJ6005、KBJ601、KBJ602、KBJ604、KBJ606、KBJ608、KBJ610 KBU封装:KBU8005、KBU801、KBU802、KBU804、KBU806、KBU808、KBU810 GBU封装:GBU8005、GBU801、GBU802、GBU804、GBU806、GBU808、GBU810 KBJ封装:KBJ8005、KBJ801、KBJ802、KBJ804、KBJ806、KBJ808、KBJ810 KBU封装:KBU10005、KBU1001、KBU1002、KBU1004、KBU1006、KBU1008、KBU1010GBU封装:GBU10005、GBU1001、GBU1002、GBU1004、GBU1006、GBU1008、GBU1010KBJ封装:KBJ10005、KBJ1001、KBJ1002、KBJ1004、KBJ1006、KBJ1008、KBJ1010GBJ封装:GBJ15005、GBJ1501、GBJ1502、GBJ1504、GBJ1506、GBJ1508、GBJ1510GBJ封装:GBJ25005、、GBJ2502、GBJ2504、GBJ2506、GBJ2508、GBJ2510方桥系列:GBPC15A封装:GBPC15005、GBPC1501、GBPC1502、GBPC1504、GBPC1506、GBPC1508、GBPC1510GBPC15A-W封装:GBPC15005W、GBPC1501W、GBPC1502W、GBPC1504W、GBPC1506W、GBPC1508W、GBPC1510WKBPC25A封装:KBPC25005、KBPC2501、KBPC2502、KBPC2504、KBPC2506、KBPC2508、KBPC2510KBPC25A-W封装:KBPC25005W、KBPC2501W、KBPC2502W、KBPC2504W、KBPC2506W、KBPC2508W、KBPC2510WGBPC25A封装:GBPC25005、GBPC2501、GBPC2502、GBPC2504、GBPC2506、GBPC2508、GBPC2510GBPC25A-W封装:GBPC25005W、GBPC2501W、GBPC2502W、GBPC2504W、GBPC2506W、GBPC2508W、GBPC2510WKBPC35A封装:KBPC35005、KBPC3501、KBPC3502、KBPC3504、KBPC3506、KBPC3508、KBPC3510KBPC35A-W封装:KBPC35005W、KBPC3501W、KBPC3502W、KBPC3504W、KBPC3506W、KBPC3508W、KBPC3510W。

KBP204G;KBP2005G;KBP201G;KBP206G;KBP202G;中文规格书,Datasheet资料

e 3KBP2005G - KBP210G2.0A GLASS PASSIVATED BRIDGE RECTIFIERJ·Case:KBP·Case Material: Molded Plastic. UL Flammability Classification Rating 94V-0·Moisture Sensitivity: Level 1 per J-STD-020C ·Terminals: Finish - Tin. Plated Leads,Solderable per MIL-STD-202, Method 208·Polarity: Marked on Body·Ordering Information: See Last Page ·Marking: Type Number·Weight: 1.52 grams (approximate)Mechanical Data·Glass Passivated Die Construction ·High Case Dielectric Strength of 1500V RMS ·Low Reverse Leakage Current ·Surge Overload Rating to 65A Peak ·Ideal for Printed Circuit Board Applications·UL Listed Under Recognized Component Index, File Number E94661·Lead Free Finish,RoHS Compliant (Note 3)Single phase, 60Hz, resistive or inductive load.For capacitive load, derate current by 20%.Maximum Ratings and Electrical Characteristics@ T A = 25°C unless otherwise specifiedNotes: 1. Thermal resistance from junction to case per element. Unit mounted on 75 x 75 x 1.6mm aluminum plate heat sink.2. Measured at 1.0 MHz and applied reverse voltage of 4.0V DC.3.RoHS revision 13.2.2003. Glass and High Temperature Solder Exemptions Applied, see EU Directive Annex Notes 5 and 7.Features00.11.0100.20.40.60.81.01.21.4I ,I N S T A N T A N E O U S F O R W A R D C U R R E N T (A )F V ,INSTANTANEOUS FORWARD VOLTAGE (V)Fig.2Typical Forward CharacteristicsF080206040100110100I ,P E A K F O R W A R D S U R G E C U R R E N T (A )F S M NUMBER OF CYCLES AT60Hz Fig.3Max Non-Repetitive Peak ForwardSurge Current110100110100C ,T O T A L C A P A C I T A N C E (p F )T V ,REVERSEVOLTAGE (V)Fig.4Typical Total Capacitance,Per ElementR 0.010.11.010100100010,000020406080100120140I ,I N S T A N T A N E O U S R E V E R S E C U R R E N T (m A )R PERCENT OF RATED PEAK REVERSE VOLTAGE (%)Fig.5Typical Reverse Characteristics00.51.01.52.050100150I O ,A V E R A G E R E C T I F I E D C U R R E N T (A)T,TEMPERATURE(°C)Fig.1Forward Current Derating CurveNotes:4.For Packaging Details, go to our website at /datasheets/ap02008.pdf.Ordering Information (Note 4)IMPORTANT NOTICELIFE SUPPORTDiodes Incorporated and its subsidiaries reserve the right to make modifications,enhancements,improvements,corrections or other changes without further notice to any product herein.Diodes Incorporated does not assume any liability arising out of the application or use of any product described herein;neither does it convey any license under its patent rights,nor the rights of others.The user of products in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on our website,harmless against all damages.Diodes Incorporated products are not authorized for use as critical components in life support devices or systems without the expressed written approval of the President of Diodes Incorporated.分销商库存信息:DIODESKBP204G KBP2005G KBP201G KBP206G KBP202G KBP210G KBP208G。

整流桥 KBL04 KBL封装系列规格书推荐

100

10 TJ=100 C

1

0.1

TJ=25 C

0.01 0

20

40

60

80

100

PERCENT OF PEAK REVERSE VOLTAGE,%

TRANSIENT THERMAL IMPEDANCE, C/W

FIG. 5-TYPICAL JUNCTION CAPACITANCE

400

MAXIMUM RATINGS AND ELECTRICAL CHARACTERISTICS

Ratings at 25 C ambient temperature unless otherwise specified. Single phase half-wave 60Hz,resistive or inductive load,for capacitive load current derate by 20%.

深圳理悠科技有限公司

KBL005 THRU KBL10

SILICON BRIDGE RECTIFIERS

Reverse Voltage - 50 to 1000 Volts Forward Current - 4.0 Amperes

KBL

0.768(19.5) 0.728(18.5)

深圳理悠科技有限公司

RATINGS AND CHARACTERISTIC CURVES KBL005 THRU KBL10

PEAK FORWARD SURGE CURRENT, AMPERES

FIG. 1- FORWARD CURRENT DERATING CURVE

4.0

Part Number

SYMBOLS

CS5532-BSZR;CS5534-BSZR;CDB5532U;中文规格书,Datasheet资料

Copyright © Cirrus Logic, Inc. 2008CS5532/34-BS24-bit ∆Σ ADCs with Ultra-low-noise PGIAFeaturesChopper-stabilized PGIA (ProgrammableGain Instrumentation Amplifier, 1x to 64x)– 6 nV/√Hz @ 0.1 Hz (No 1/f noise) at 64x –1200pA Input Current with Gains >1 Delta-sigma Analog-to-digital Converter –Linearity Error: 0.0007% FS–Noise-free Resolution: Up to 23 bits Two- or Four-channel Differential MUX Scalable Input Span via Calibration –±5 mV to differential ±2.5VScalable V REF Input: Up to Analog Supply Simple Three-wire Serial Interface –SPI™ and Microwire™ Compatible –Schmitt Trigger on Serial Clock (SCLK) R/W Calibration Registers Per Channel Selectable Word Rates: 6.25 to 3,840 Sps Selectable 50 or 60 Hz RejectionPower Supply Configurations–VA+ = +5 V; VA- = 0 V; VD+ = +3 V to +5 V–VA+ = +2.5 V; VA- = -2.5 V; VD+ = +3 V to +5 V –VA+ = +3 V; VA- = -3 V; VD+ = +3 VGeneral DescriptionThe CS5532/34 are highly integrated ∆Σ Analog-to-Digi-tal Converters (ADCs) which use charge-balance techniques to achieve 24-bit performance. The ADCs are optimized for measuring low-level unipolar or bipolar signals in weigh scale, process control, scientific, and medical applications.To accommodate these applications, the ADCs come as either two-channel (CS5532) or four-channel (CS5534)devices and include a very low-noise, chopper-stabilized instrumentation amplifier (6 nV/√Hz @ 0.1 Hz) with se-lectable gains of 1×, 2×, 4×, 8×, 16×, 32×, and 64×.These ADCs also include a fourth-order ∆Σ modulator followed by a digital filter which provides twenty selectable output word rates of 6.25, 7.5, 12.5, 15, 25, 30, 50, 60, 100,120, 200, 240, 400, 480, 800, 960, 1600, 1920, 3200, and 3840 Sps (MCLK =4.9152MHz).To ease communication between the ADCs and a micro-controller, the converters include a simple three-wire se-rial interface which is SPI™ and Microwire™ compatible with a Schmitt-trigger input on the serial clock (SCLK).High dynamic range, programmable output rates, and flexible power supply options makes these ADCs ideal solutions for weigh scale and process control applications.ORDERING INFORMATIONSee page 47VA+C1C2VREF+VREF-VD+DIFFERENTIAL 4TH ORDER ∆ΣMODULATORPGIA 1,2,4,8,16PROGRAMMABLE SINC FIR FILTERMUX(CS5534SHOWN)AIN1+AIN1-AIN2+AIN2-AIN3+AIN3-AIN4+AIN4-SERIAL INTERFACELATCHCLOCK GENERATORCALIBRATION SRAM/CONTROLLOGICDGNDCSSDI SDO SCLKOSC2OSC1A1A0/GUARD VA-32,64OCT ‘08TABLE OF CONTENTS1.CHARACTERISTICS AND SPECIFICATIONS (4)ANALOG CHARACTERISTICS (4)TYPICAL RMS NOISE (NV) (7)TYPICAL NOISE-FREE RESOLUTION(BITS) (7)5 V DIGITAL CHARACTERISTICS (8)3 V DIGITAL CHARACTERISTICS (8)DYNAMIC CHARACTERISTICS (9)ABSOLUTE MAXIMUM RATINGS (9)SWITCHING CHARACTERISTICS (10)2.GENERAL DESCRIPTION (12)2.1.Analog Input (12)2.1.1. Analog Input Span (13)2.1.2. Multiplexed Settling Limitations (13)2.1.3. Voltage Noise Density Performance (13)2.1.4. No Offset DAC (14)2.2.Overview of ADC Register Structure and Operating Modes (14)2.2.1. System Initialization (15)2.2.2. Serial Port Interface (22)2.2.3. Reading/Writing On-Chip Registers (23)2.3.Configuration Register (23)2.3.1. Power Consumption (23)2.3.2. System Reset Sequence (23)2.3.3. Input Short (24)2.3.4. Guard Signal (24)2.3.5. Voltage Reference Select (24)2.3.6. Output Latch Pins (24)2.3.7. Offset and Gain Select (25)2.3.8. Filter Rate Select (25)2.4.Setting up the CSRs for a Measurement (27)2.5.Calibration (30)2.5.1. Calibration Registers (30)2.5.2. Performing Calibrations (31)2.5.3. Self Calibration (31)2.5.4. System Calibration (32)2.5.5. Calibration Tips (32)2.5.6. Limitations in Calibration Range (33)2.6.Performing Conversions (33)2.6.1. Single Conversion Mode (33)2.6.2. Continuous Conversion Mode (34)2.6.3. Examples of Using CSRs to Perform Conversions and Calibrations (35)ing Multiple ADCs Synchronously (36)2.8.Conversion Output Coding (36)2.9.Digital Filter (38)2.10.Clock Generator (39)2.11.Power Supply Arrangements (39)2.12.Getting Started (43)2.13.PCB Layout (43)3.PIN DESCRIPTIONS (44)4.SPECIFICATION DEFINITIONS (46)5.ORDERING INFORMATION (47)6.ENVIRONMENTAL, MANUFACTURING, & HANDLING INFORMATION (47)7.PACKAGE DRAWINGS (48)LIST OF FIGURESFigure 1. SDI Write Timing (Not to Scale) (11)Figure 2. SDO Read Timing (Not to Scale) (11)Figure 3. Multiplexer Configuration (12)Figure 4. Input models for AIN+ and AIN- pins (13)Figure 5. Measured Voltage Noise Density (13)Figure 6. CS5532/34 Register Diagram (14)Figure 7. Command and Data Word Timing (22)Figure 8. Guard Signal Shielding Scheme (24)Figure 9. Input Reference Model when VRS = 1 (25)Figure 10. Input Reference Model when VRS = 0 (25)Figure 11. Self Calibration of Offset (32)Figure 12. Self Calibration of Gain (32)Figure 13. System Calibration of Offset (32)Figure 14. System Calibration of Gain (32)Figure 15. Synchronizing Multiple ADCs (36)Figure 16. Digital Filter Response (WR = 60 Sps) (38)Figure 18. 120 Sps Filter Phase Plot to 120 Hz (38)Figure 17. 120 Sps Filter Magnitude Plot to 120 Hz (38)Figure 19. Z-Transforms of Digital Filters (38)Figure 20. On-chip Oscillator Model (39)Figure 21. CS5532 Configured with a Single +5 V Supply (40)Figure 22. CS5532 Configured with ±2.5 V Analog Supplies (41)Figure 23. CS5532 Configured with ±3 V Analog Supplies (41)Figure 24. CS5532 Configured for Thermocouple Measurement (42)Figure 25. Bridge with Series Resistors (42)LIST OF TABLESTable 1. Conversion Timing – Single Mode (34)Table 2. Conversion Timing – Continuous Mode (35)Table 3. Command Byte Pointer (35)Table 4. Output Coding for 24-bit CS5532 and CS5534 (37)1. CHARACTERISTICS AND SPECIFICATIONSANALOG CHARACTERISTICS(VA+, VD+ = 5 V ±5%; VREF+ = 5 V; VA-, VREF-, DGND = 0 V; MCLK = 4.9152 MHz; OWR (Output Word Rate) = 60 Sps; Bipolar Mode; Gain = 32)(See Notes 1 and 2.)Notes: 1.Applies after system calibration at any temperature within -40 °C ~ +85 °C.2.Specifications guaranteed by design, characterization, and/or test. LSB is 24 bits.3. This specification applies to the device only and does not include any effects by external parasiticthermocouples. The PGIA contributes 5 nV of offset drift, and the modulator contributes 640/G nV of offset drift, where G is the amplifier gain setting.4.Drift over specified temperature range after calibration at power-up at 25 °C.ParameterMin Typ Max Unit Accuracy Linearity Error -±0.0007±0.0015%FS No Missing Codes 24--Bits Bipolar Offset -±16±32LSB 24Unipolar Offset-±32±64LSB 24Offset Drift(Notes 3 and 4)-640/G +5-nV/°C Bipolar Full-scale Error -±8±31ppm Unipolar Full-scale Error -±16±62ppm Full-scale Drift(Note 4)-2-ppm/°CANALOG CHARACTERISTICS (Continued)(See Notes 1 and 2.)Notes: 5.The voltage on the analog inputs is amplified by the PGIA, and becomes V CM ± Gain*(AIN+ - AIN-)/2 atthe differential outputs of the amplifier. In addition to the input common mode + signal requirements for the analog input pins, the differential outputs of the amplifier must remain between (VA- + 0.1 V) and (VA+ - 0.1 V) to avoid saturation of the output stage.6.See the section of the data sheet which discusses input models.7.Input current on AIN+ or AIN- (with Gain =1), or VREF+ or VREF- may increase to 250nA if operatedwithin 50mV of VA+ or VA-. This is due to the rough charge buffer being saturated under these conditions.ParameterMin TypMaxUnitAnalog InputCommon Mode + Signal on AIN+ or AIN-Bipolar/Unipolar ModeGain = 1 Gain = 2, 4, 8, 16, 32, 64(Note 5)VA-VA- + 0.7--VA+VA+ - 1.7V V CVF Current on AIN+ or AIN-Gain = 1 (Note 6, 7)Gain = 2, 4, 8, 16, 32, 64--501200--nA pA Input Current Noise Gain = 1 Gain = 2, 4, 8, 16, 32, 64--2001--pA/√Hz pA/√Hz Input Leakage for Mux when Off (at 25 °C)-10-pA Off-channel Mux Isolation -120-dB Open Circuit Detect Current 100300-nA Common Mode Rejection dc, Gain = 1dc, Gain = 6450, 60 Hz ---90130120---dB dB dB Input Capacitance -60-pF Guard Drive Output -20-µA Voltage Reference Input Range (VREF+) - (VREF-)1 2.5(VA+)-(VA-)V CVF Current (Note 6, 7)-50-nA Common Mode Rejection dc 50, 60 Hz --120120--dB dB Input Capacitance 11-22pF System Calibration Specifications Full-scale Calibration Range Bipolar/Unipolar Mode 3-110%FS Offset Calibration Range Bipolar Mode -100-100%FS Offset Calibration Range Unipolar Mode -90-90%FSANALOG CHARACTERISTICS (Continued)(See Notes 1 and 2.)8.All outputs unloaded. All input CMOS levels.9.Power is specified when the instrumentation amplifier (Gain ≥ 2) is on. Analog supply current is reducedby approximately 1/2 when the instrumentation amplifier is off (Gain = 1).10.Tested with 100 mV change on VA+ or VA-.ParameterMinTypMaxUnitPower SuppliesDC Power Supply Currents (Normal Mode)I A+, I A-I D+- - 130.5151mA mA Power ConsumptionNormal Mode (Notes 8 and 9)Standby Sleep---70450080--mW mW µW Power Supply Rejection (Note 10)dc Positive Supplies dc Negative Supply--115115--dB dBTYPICAL RMS NOISE (nV)(See notes 11, 12, 13 and 14)Notes:11.The -B devices provide the best noise specifications.12.Wideband noise aliased into the baseband. Referred to the input. Typical values shown for 25 °C.13.For Peak-to-Peak Noise multiply by 6.6 for all ranges and output rates.14.Word rates and -3dB points with FRS = 0. When FRS = 1, word rates and -3dB points scale by 5/6.TYPICAL NOISE-FREE RESOLUTION(BITS)(See Notes 15 and 16)15.Noise-free resolution listed is for bipolar operation, and is calculated as LOG((Input Span)/(6.6xRMSNoise))/LOG(2) rounded to the nearest bit. For unipolar operation, the input span is 1/2 as large, so one bit is lost. The input span is calculated in the analog input span section of the data sheet. The noise-free resolution table is computed with a value of 1.0 in the gain register. Values other than 1.0 will scale the noise, and change the noise-free resolution accordingly.16.“Noise-free resolution” is not the same as “effective resolution”. Effective resolution is based on theRMS noise value, while noise-free resolution is based on a peak-to-peak noise value specified as 6.6 times the RMS noise value. Effective resolution is calculated as LOG((Input Span)/(RMS Noise))/LOG(2).Specifications are subject to change without notice.Output Word Rate (Sps)-3 dB Filter Frequency (Hz)Instrumentation Amplifier Gain x64x32x16x8x4x2x17.5 1.948.59101526509915 3.88121315213770139307.751718213052991966015.524252942731402771203134364259103198392240628013626051410202050409048012211319436973014502900581096023015927452310302060411082301,920390260470912181036207230145003,84078013602690538010800215004300086000Output Word Rate (Sps)-3 dB Filter Frequency (Hz)Instrumentation Amplifier Gainx64x32x16x8x4x2x17.5 1.942021222323232315 3.8820212222222222307.75192021222222226015.5192021212121211203118192021212121240621717181818181848012217171717171717960230161617171717171,920390161616161616163,840780131313131313135 V DIGITAL CHARACTERISTICS(VA+, VD+ = 5 V ±5%; VA-, DGND = 0 V; See Notes 2 and 17.)3 V DIGITAL CHARACTERISTICS(T A = 25 °C; VA+ = 5V ±5%; VD+ = 3.0V±10%; VA-, DGND = 0V; See Notes 2 and 17.)17.All measurements performed under static conditions.ParameterSymbol Min Typ Max Unit High-level Input Voltage All Pins Except SCLKSCLK V IH 0.6 VD+(VD+) - 0.45--VD+VD+V Low-level Input Voltage All Pins Except SCLKSCLK V IL 0.00.0-0.80.6V High-level Output Voltage A0 and A1, I out = -1.0 mASDO, I out = -5.0 mA V OH (VA+) - 1.0(VD+) - 1.0--V Low-level Output Voltage A0 and A1, I out = 1.0 mASDO, I out = 5.0 mAV OL --(VA-) + 0.40.4V Input Leakage Current I in -±1±10µA SDO Tri-State Leakage Current I OZ --±10µA Digital Output Pin CapacitanceC out-9-pFParameterSymbol Min Typ Max Unit High-level Input Voltage All Pins Except SCLKSCLK V IH 0.6 VD+(VD+) - 0.45-VD+VD+V Low-level Input Voltage All Pins Except SCLKSCLK V IL 0.00.0-0.80.6V High-level Output Voltage A0 and A1, I out = -1.0 mASDO, I out = -5.0 mA V OH (VA+) - 1.0(VD+) - 1.0--V Low-level Output Voltage A0 and A1, I out = 1.0 mASDO, I out = 5.0 mAV OL --(VA-) + 0.40.4V Input Leakage Current I in -±1±10µA SDO Tri-State Leakage Current I OZ --±10µA Digital Output Pin CapacitanceC out-9-pFDYNAMIC CHARACTERISTICS18.The ADCs use a Sinc 5 filter for the 3200 Sps and 3840 Sps output word rate (OWR) and a Sinc 5 filterfollowed by a Sinc 3 filter for the other OWRs. OWR sinc5 refers to the 3200 Sps (FRS = 1) or 3840 Sps (FRS = 0) word rate associated with the Sinc 5 filter.19.The single conversion mode only outputs fully settled conversions. See Table 1 for more details aboutsingle conversion mode timing. OWR SC is used here to designate the different conversion time associated with single conversions.20.The continuous conversion mode outputs every conversion. This means that the filter’s settling timewith a full scale step input in the continuous conversion mode is dictated by the OWR.ABSOLUTE MAXIMUM RATINGS(DGND = 0 V; See Note 21.)Notes:21.All voltages with respect to ground.22.VA+ and VA- must satisfy {(VA+) - (VA-)} ≤ +6.6 V.23.VD+ and VA- must satisfy {(VD+) - (VA-)} ≤ +7.5 V.24.Applies to all pins including continuous overvoltage conditions at the analog input (AIN) pins.25.Transient current of up to 100 mA will not cause SCR latch-up. Maximum input current for a power supply pin is ±50 mA.26.Total power dissipation, including all input currents and output currents.WARNING:Operation at or beyond these limits may result in permanent damage to the device.Normal operation is not guaranteed at these extremes.ParameterSymbol Ratio Unit Modulator Sampling Ratef s MCLK/16Sps Filter Settling Time to 1/2 LSB (Full Scale Step Input)Single Conversion mode (Notes 18, 19, and 20)Continuous Conversion mode, OWR < 3200 Sps Continuous Conversion mode, OWR ≥ 3200 Spst s t s t s1/OWR SC5/OWR sinc5 + 3/OWR5/OWRs s sParameterSymbol Min Typ Max Unit DC Power Supplies(Notes 22 and 23)Positive Digital Positive Analog Negative Analog VD+VA+VA--0.3-0.3+0.3---+6.0+6.0-3.75V V V Input Current, Any Pin Except Supplies (Notes 24 and 25)I IN --±10mA Output Current I OUT--±25mA Power Dissipation (Note 26)PDN --500mW Analog Input Voltage VREF pins AIN PinsV INR V INA (VA-) -0.3(VA-) -0.3--(VA+) + 0.3(VA+) + 0.3V V Digital Input VoltageV IND -0.3-(VD+) + 0.3V Ambient Operating Temperature T A -40-85°C Storage Temperature T stg-65-150°CSWITCHING CHARACTERISTICS(VA+ = 2.5 V or 5 V ±5%; VA- = -2.5V±5% or 0 V; VD+ = 3.0 V ±10% or 5 V ±5%;DGND = 0 V; Levels: Logic 0 = 0 V, Logic 1 = VD+; C L = 50 pF; See Figures 1 and 2.)Notes:27.Device parameters are specified with a 4.9152 MHz clock.28.Specified using 10% and 90% points on waveform of interest. Output loaded with 50pF.29.Oscillator start-up time varies with crystal parameters. This specification does not apply when using anexternal clock source.ParameterSymbol Min Typ MaxUnitMaster Clock Frequency (Note 27)External Clock or Crystal OscillatorMCLK1 4.91525MHz Master Clock Duty Cycle 40-60%Rise Times(Note 28)Any Digital Input Except SCLKSCLKAny Digital Output t rise-----50 1.0100-µs µs ns Fall Times(Note 28)Any Digital Input Except SCLKSCLKAny Digital Output t fall-----50 1.0100-µs µs ns Start-upOscillator Start-up Time XTAL = 4.9152 MHz(Note 29)t ost-20-ms Serial Port Timing Serial Clock Frequency SCLK 0-2MHz Serial Clock Pulse Width High Pulse Width Lowt 1t 2250250----ns nsSDI Write TimingCS Enable to Valid Latch Clock t 350--ns Data Set-up Time prior to SCLK rising t 450--ns Data Hold Time After SCLK Rising t 5100--ns SCLK Falling Prior to CS Disable t 6100--nsSDO Read Timing CS to Data Validt 7--150ns SCLK Falling to New Data Bit t 8--150ns CS Rising to SDO Hi-Zt 9--150ns分销商库存信息:CIRRUS-LOGICCS5532-BSZR CS5534-BSZR CDB5532U。

整流桥 KBL10 KBL封装系列规格书推荐

深圳理悠科技有限公司

RATINGS AND CHARACTERISTIC CURVES KBL005 THRU KBL10

PEAK FORWARD SURGE CURRENT, AMPERES

FIG. 1- FORWARD CURRENT DERATING CURVE

4.0

Maximum DC blocking voltage

VDC

50 100 200 400 600 800

Maximum average forward TC=50 C(Note 2)

output rectified current at TA=50 C(Note 3)

I(AV)

4.0 3.0

Peak forward surge current

深圳理悠科技有限公司

KBL005 THRU KBL10

SILICON BRIDGE RECTIFIERS

Reverse Voltage - 50 to 1000 Volts Forward Current - 4.0 Amperes

KBL

0.768(19.5) 0.728(18.5)

200

20

TJ=25 C

2

0.1

1.0

10

100

REVERSE VOLTAGE,VOLTS

FIG. 6-TYPICAL TRANSIENT THERMAL IMPEDANCE

100

10

1

0.1

0.01

0.1

1

10

100

t,PULSE DURATION,sec.

JUNCTION CAPACITANCE, pF

0.580(14.7) 0.540(13.7)

kbp标准尺寸

kbp标准尺寸

KBP标准尺寸是指俄罗斯国家标准(GOST)中规定的纸张尺寸。

KBP 是俄语“Кабинетный бумаги”的缩写,意为办公室用纸。

KBP标准尺寸有多种,以下是其中一些常见的尺寸:

1. KBP-A4:210mm x 297mm,与国际标准的A4纸尺寸相同。

2. KBP-A5:148mm x 210mm,比A4纸稍小,常用于便签和名片。

3. KBP-A6:105mm x 148mm,比A5纸更小,常用于明信片和贺卡。

4. KBP-A3:297mm x 420mm,比A4纸大一倍,常用于海报、宣传册等大幅面打印。

5. KBP-A2:420mm x 594mm,比A3纸大一倍,常用于展览展示、地图等大幅面打印。

6. KBP-A1:594mm x 841mm,比A2纸大一倍,常用于大型海报、广告等大幅面打印。

需要注意的是,KBP标准尺寸并非全球通用,不同国家和地区可能有不同的纸张尺寸标准。

在设计文档或印刷品时,应根据目标市场选择合适的纸张尺寸。

二极管、整流桥参数简介

编带TB 散装BP1N400150 1.0 5.0DO-411N4004400 1.0 5.0DO-411N40071000 1.0 5.0DO-4151M71000 1.0 5.0SMA/DO-214AC 5LM40071000 1.0 5.0MINIMELF 10A71000 1.0 5.0SOD-1233*51N5394300 1.5 5.0DO-151N53965001.55.0DO-151N53991000 1.5 5.0DO-1530.51N5401100 3.0 5.0DO-201AD 1N5402200 3.0 5.0DO-201AD 1N5404400 3.0 5.0DO-201AD 1N5406600 3.0 5.0DO-201AD 1N54081000 3.0 5.0DO-201AD 1.250.25RL20150 2.0 5.0DO-15RL205600 2.0 5.0DO-15RL2071000 2.0 5.0DO-1530.56A101000 6.010.0R-60.50.18A1010008.010.0R-610A10100010.010.0R-6FR10150 1.0 5.0DO-41FR102100 1.0 5.0DO-41FR103200 1.0 5.0DO-41FR104400 1.0 5.0DO-41FR105600 1.0 5.0DO-41FR106800 1.0 5.0DO-41FR1071000 1.0 5.0DO-4151FR15150 1.5 5.0DO-15FR154400 1.5 5.0DO-15FR155600 1.5 5.0DO-15FR1571000 1.5 5.0DO-1530.5FR2071000 2.0 5.0DO-1530.5FR30150 3.010.0DO-201AD FR302100 3.010.0DO-201AD FR303200 3.010.0DO-201AD FR304400 3.010.0DO-201AD FR305600 3.010.0DO-201AD FR306800 3.010.0DO-201AD FR3071000 3.010.0DO-201AD 1.250.25FR6071000 6.010.0R-60.50.1BA157400 1.0 5.0DO-41BA1591000 1.0 5.0DO-411N493350 1.0 5.0DO-411N4934100 1.0 5.0DO-411N4935200 1.0 5.0DO-411N4937600 1.0 5.0DO-41511N49422001.05.0DO-41MUR系列8A-60A 200V-1200VMUR1660TO-220AB普通整流二极管快恢复整流二极管包装数量(Kpcs)分类型号反向电压正向电流反向电流封装形式UF4005600 1.010.0DO-415UF2G 400 2.0 5.0DO-214AA/SMB UF2J 600 2.0 5.0DO-214AA/SMB HER10150 1.0 5.0DO-41HER102100 1.0 5.0DO-41HER103200 1.0 5.0DO-41HER104300 1.0 5.0DO-41HER105400 1.0 5.0DO-4151HER106600 1.0 5.0DO-41HER107800 1.0 5.0DO-41HER20150 2.0 5.0DO-15HER202100 2.0 5.0DO-153HER203200 2.0 5.0DO-15HER204300 2.0 5.0DO-15HER205400 2.0 5.0DO-15HER206600 2.0 5.0DO-15HER207800 2.0 5.0DO-1530.5HER30150 3.010.0DO-201AD HER302100 3.010.0DO-201AD HER304300 3.010.0DO-201AD 1.250.25HER305400 3.010.0DO-201AD HER307800 3.010.0DO-201AD 1N581720 1.0 1.0DO-411N581830 1.0 1.0DO-411N581940 1.0 1.0DO-41511N582020 3.0 2.0DO-201AD 1N582130 3.0 2.0DO-201AD 1N582240 3.0 2.0DO-201AD 1.250.25SR1606030.01.0DO-415SR120~SR115SR220~SR215SR320~SR315SR520~SR515SR820~SR8A0SR1020~SR10A0SR2020~SR20A0MBR1020~MBR 10100MBR2020~MBR 20100SMD系列SS12~SS110SS22~SS210(SMA)SS32~SS310(SMB)SS1440 1.00.5DO-214AC/SMA 10SS2440 2.00.5DO-214AA/SMB1N60、1N60P9(I F =30BAT85(I F =200mA,V R =30V,C J =10p F) (DO-35)MA700(I F =30mA,V R =30v,C J =1.3p E)(DO-35)1SS106(I F =30mA,V R =10V,C J =1.5pF)(DO-35)小信号肖特基二极管高效率整流二极管肖特基势垒二极管特快恢复3击穿电压动态恢复电压击穿电流DB-328、32、36 5.0100μA DO-35(玻封,大功率和长寿命节能灯使用)/A-405(塑封)51DB-435、40、45 5.0100μADO-35/A-405DB-656、60、7010.0100μADO-35K105K120K130K150K200K240K300K140双向触发二极管备注BP、TB 分类有 0.6*58,0.6*52,压5mm 低成本 低漏 低正向压降 高电流容量 容易清洗(氟利昂、氯乙烷、酒精和类似的溶剂)其DIP(双列直插封装)对应型号为1N40071N4007的贴片对应型号有大芯片和普通的两种高效率的快速切换 高电流能力和低正向压降 低反向漏电流 塑料材料-UL 可燃也有大小芯片之分Trr=150ns,f极限=6.7MHZ Trr=150ns,f极限=6.7MHZ Trr=150ns,f极限=6.7MHZ Trr=150ns,f极限=6.7MHZ Trr=250ns,f极限=64MHZTrr=500ns,f极限=2MHZ高电流能力 高可靠性 高浪涌电流能力 低正向压降Trr=500ns,f极限=2MHZ反向恢复时间和极限工作频率是成反比的Trr=200nsTrr=50nsTrr=75nsTrr=50ns,f极限=20MHZTrr=50ns,f极限=20MHZTrr=50ns,f极限=20MHZTrr=50ns,f极限=20MHZTrr=50ns,f极限=20MHZTrr=75ns,f极限=13.3MHZ Trr=75ns,f极限=13.3MHZ 反向恢复时间和极限工作频率不会因为电流的变化而发生变化贴片封装有玻封/塑封/中性,蓝管、TB/BP,用于节能灯、镇流器DO-35玻封适合于自动表面安装1N4148的贴片封装形式贴片测试电流1mA双向吸收有编带和散装两种包装。

整流桥KBL06 KBL封装系列规格书推荐

PULSE WIDTH=300 µs

1%DUTY CYCLE

0.01

0.6

0.8

1.0

1.2

1.4 1.5

INSTANTANEOUS FORWARD VOLTAGE, VOLTS

INSTANTANEOUS REVERSE CURRENT, MICROAMPERES

FIG. 4-TYPICAL REVERSE CHARACTERISTICS

KBL 10

1000 700 1000

UNITS

VOLTS VOLTS VOLTS

Amps

Amps

A2s

Volts

µA mA pF C/W

C C

1 of 2

AVERAGE FORWARD RECTIFIED CURRENT, AMPERES

INSTANTANEOUS FORWARD CURRENT,AMPERES

Maximum DC blocking voltage

VDC

50 100 200 400 600 800

Maximum average forward TC=50 C(Note 2)

output rectified current at TA=50 C(Note 3)

I(AV)

4.0 3.0

Peak forward surge current

8.3ms single half sine-wave superimposed on

IFSM

200

rated load (JEDEC Method)

Rating for Fusing(t<8.3ms)

I2t

166

Maximum instantaneous forward voltage drop

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Part Number

SYMBOLS

KBP 2005

KBP 201

KBP 202

KBP 204

KBP 206

KBP 208

Maximum repetitive peak reverse voltage

VRRM

50

100 200

400 600 800

Maximum RMS voltage

VRMS

35

70 140 280 420 560

0.153(3.9) 0.146(3.7)

Dimensions in inches and (millimeters)

MECHANICAL DATA

Case: Molded plastic body Terminals: Plated leads solderable per MIL-STD-750, Method 2026 Polarity: Polarity symbols marked on case Mounting Position: Any Weight:0.069 ounce, 1.95 grams

深圳理悠科技有限公司

KBP2005 THRU KBP210

SILICON BRIDGE RECTIFIERS

Reverse Voltage - 50 to 1000 Volts Forward Current - 2.0 Amperes

KBP

0.600(15.24) 0.560(14.22)

MAXIMUM RATINGS AND ELECTRICAL CHARACTERISTICS

Ratings at 25 C ambient temperature unless otherwise specified. Single phase half-wave 60Hz,resistive or inductive load,for capacitive load current derate by 20%.

1,000

100

10 TJ=100 C

1

0.1

TJ=25 C

0.01 0

20

40

60

80

100

PERCENT OF PEAK REVERSE VOLTAGE,%

FIG. 6-TYPICAL TRANSIENT THERMAL IMPEDANCE

100

10

1

TRANSIENT THERMAL IMPEDANCE, C/W

0.460(11.68) 0.420(10.6)

0.460(11.68) 0.420(10.67)

+

AC

-

FEATURES

The plastic package carries Underwriters Laboratory Flammability Classification 94V-0 Ideal for printed circuit boards Low reverse leakage High forward surge current capability High temperature soldering guaranteed:

0.8

1.0

1.2

1.4 1.5

INSTANTANEOUS FORWARD VOLTAGE, VOLTS

FIG. 5-TYPICAL JUNCTION CAPACITANCE

200

100

TJ=25 C

10

INSTANTANEOUS REVERSE CURRENT, MICROAMPERES

PEAK FORWARD SURGE CURRENT, AMPERES

260 C/10 seconds,0.375”(9.5mm) lead length, 5 lbs. (2.3kg) tension

0.035(0.9)DIA. 0.028(0.7)TPY.

0.50(12.7) 0.640(16.25)

MIN MIN

0.05(1.27)

0.160(4.1) 0.140(3.6)

8.3ms single half sine-wave superimposed on

IFSM

60.0

rated load (JEDEC Method)

Maximum instantaneous forward voltage drop

per birdge element at 1.0A

VF

1.0

Maximum DC reverse current TJ =25 C

TJ

storage temperature range

TSTG

10 0.5 20 28 -55 to +125 -55 to +150

NOTES: 1.Measured at 1.0 MHz and applied reverse voltage of 4.0 Volts. 2.Unit mounted on P.C. board with 0.47” x 0.47”(12x12mm) copper pads,0.375”(9.5mm) lead length.

KBP 210 1000 700 1000

UNITS

VOLTS VOLTS VOLTS

Amps

Amps

Volts

µA mA pF C/W

C C

1 of 2

深圳理悠科技有限公司

AVERAGE FORWARD RECTIFIED CURRENT, AMPERES

INSTANTANEOUS FORWARD CURRENT,AMPERES

RATINGS AND CHARACTERISTIC CURVES KBP2005 THRU KBP210

FIG. 1- FORWARD CURRENT DERATING CURVE

2.0

1.6

1.2

0.8

Single Phase

Half Wave 60Hz

Resistive or

inductive Load

at rated DC blocking voltage TJ =100 C

IR

Typical Junction Capacitance (Note 1)

CJ

Typical Thermal Resistance (Note 2)

RθJA

Operating junction temperature range

FIG. 2-MAXIMUM NON-REPETITIVE PEAK FORWARD SURGE CURRENT

60

40

30

20

10 8.3ms SINGLE HALF SINE-WAVE (JEDEC Method)

0

1

10

100

NUMBER OF CYCLES AT 60 Hz

FIG. 4-TYPICAL REVERSE CHARACTERISTICS

Maximum DC blocking voltage

VDC

50 100 200 400 600 800

Maximum average forward output rectified current

at TC=50 C(Note 2)

I(AV)

2.0

Peak forward surge current

0.6

0

0

25

50

75

100 125 150

175

AMBIENT TEMPERATURE, C

FIG. 3-TYPICAL INSTANTANEOUS FORWARD CHARACTERISTICS

20

10

1

TJ=25 C

0.1

PULSE WIDTH=300 µs

1%DUTY CYCLE

0.01

0.6

1

0.1

1.0

10

100

REVERSE VOLTAGE,VOLTS

0.1

0.01

0.1

1

10

100

t,PULSE DURATION,sec.

ห้องสมุดไป่ตู้

2 of 2

JUNCTION CAPACITANCE, pF