集成无源元件对PCB发展影响

0201元件对制造工艺的影响-1精

0201元件对制造工艺的影响-11、0201元件对PCB设计的影响0201元件的应用对印制电路板的设计与制造有着很大的影响。

其主要影响方面是设计的方面,主要包括焊盘设计、元件间距和布线设计。

0201元件要求更小的焊盘,更细更密的布线,以及更小的元件间距。

对于这些方面的改变,从技术上都是可行的,但是直接影响到了PCB的生产成本,是成本大幅提升。

下面我们详细的讨论一下 0201对PCB元件间距和布线设计的影响。

1.1元件间距与布线设计使用0201元件的最主要原因就是节省PCB上的空间。

这样可以将更多的元件设计到 PCB上,以增加产品的功能和减小产品的体积。

0201元件带来的好处除了本身体积减小之外,还包括元件间距的减少。

这样进一步节省了空间。

一些制造商和研究机构做过这方面的研究,结果显示,使用0201元件的PCB和使用0402的PCB相比节省了 60%以上的空间。

研究结果还显示,元件的间距最小可以小到6mil。

当前,针对0201元件的应用,对合同制造商的元件间距的要求是16mil。

我们可以见到的经常使用的间距是8mil、12mil、16mil、20mil。

当然,元件的间距越小,所节省的空间就越多。

但是更小的间距对贴片设备的精度,模板的精度以及PCB布线的设计都有很大影响。

元件间距越小,贴片机的精度应该越高,模板上的开口的间距也越小,模板就越难制作。

如果要实现8mil的间距,则需要在 PCB的布线方面作一些改进。

首先先看一下PCB布线的线宽和线距的标准,参见表 1.1-1.3表1.1线宽和线距线宽/英寸线间距/英寸备注线宽/英寸线间距/英寸备注0.10 0.010 简便0.005 0.005 困难0.007 0.008 标准0.002 0.002 极困难表1.2外层线宽和线距线宽 /英寸0.012 0.010 0.010 0.010焊盘间距 /英寸0.008 0.008 0.008 0.008线间距/英寸0.008 0.0080.006 0.006线-焊盘间距 /英寸0.006 0.006 0.007 0.005环形图 */ 英寸0.005 0.005 0.005 0.006*为孔边缘到焊盘边缘的距离表 1.3 内层线路线宽和线距功能 0.012/0.10 0.008/0.008 0.006/0.006 0.005/0.005线宽 /英寸0.012 0.008 0.006 0.005焊盘间距 /英寸0.010 0.0080.0060.005线间距/英寸0.010 0.0080.0060.005线-焊盘间距 /英寸 0.010 0.006 0.006 0.005环形图 / 英寸0.008 0.008 0.0070.006线 - 孔边缘 / 英寸0.0180.016 0.013 0.016板- 孔边缘 /英寸0.018 0.016 0.013 0.016我们这里一般讨论的是外层线路,所以可以看到线宽和线间距都有一个范围。

PCB发展迎来新高峰 行业洗牌不可避免

要 ,导体 图形 微 细 化 技 术 将 朝 着 最 小 线 宽 / 间距 为2 5

m/ 5um 布 线 中心 距5 m、导体 厚 度 5 下 的 方 2 0u m以 u

向发 展 。6激 光 导 通孔 工 艺是 积层 法 多层 板 导通  ̄ l br J 工 ]

复苏 。整个 电子 电路 产 业的 发展 ,尤 其是 在 中 国大 陆的 发展 ,迎 来 了一 个新 的 高峰 。中 国在 国 内需 求及 国外 产 业 持续 转 移 的 推 动下 ,己 经 逐 步形 成P BC L C ,C 生产 产 值 最 大的 、技术 发展 最 活跃 的中心 地 区 。

面 ,纳米 技 术的 广 泛使 用将 对 降 低 P B 电常 数 、提 高 c介

力 学性 质 、提 升产 品的 耐热 性 以及 对产 业 环保 的应 用等

从 世 界 P B 品 结 构 来 看 ,下 一 代 的 电子 系 统 对 方 面产 生积 极影 响 。 C产

P B 要求 突 出表 现 在 更加 高 密 度 化 。随 着 电 子整 机产 C的 品的多 功 能化 、小 型化 、轻量 化的 发展 ,多 层 板 、挠 性

手段 的 主 流 ,C 激 光 和 u 激 光 加工 机 将 成 为适 用于 实 O, V

用化 工 艺 的 发 展 主 流 ,其最 小 导 通 孔 孔 径 将 由 目 前 的

5 m~8 m降  ̄3 u 0u 0u J l0 m,孔径 精 度和 导通 孔位 置 精 度

提 高 到 ±1 5um。7内部嵌 人 薄 型无 源 元件 的P B 已在 . C板

印 制 电路 板 F C 刚挠 结 合 板 、H I U P、 D/ M基 板 、I ̄ 装 B cg . 基板等 品种 已成 为需 求量 大 的产 品 。 近年 来世 界 P BI 术 发展 集 中 表现 在 无 源( C f技  ̄ J 即埋人

2024年无源元器件市场规模分析

2024年无源元器件市场规模分析概述无源元器件是指不需要外部能量驱动的电子元件,如电阻器、电容器、电感器等。

这些元器件在电子设备的各个领域中起着重要的作用。

本文将对无源元器件市场规模进行分析,旨在了解该市场的发展趋势和潜在机会。

市场规模分析无源元器件市场取决于电子行业的需求和发展情况。

随着数字化转型的加速和5G 技术的普及,电子设备的市场需求量不断增加,从而推动了无源元器件市场的发展。

市场份额根据市场调研公司的数据,无源元器件市场具有巨大的潜力。

预计在未来几年内,该市场的年均增长率将保持在5%以上。

当前,全球无源元器件市场规模已达到数十亿美元。

产品细分无源元器件市场涵盖了多种产品,其中包括电阻器、电容器、电感器等。

以电阻器为例,根据材料和功能的不同,它可以细分为碳膜电阻器、金属膜电阻器、热敏电阻器等。

各类产品在电子设备中的应用场景不尽相同。

市场驱动因素1.技术进步:随着科技的不断进步和创新,无源元器件的设计和制造技术也在不断提升,使其性能更加稳定和可靠。

2.电子设备需求增长:包括通信设备、消费电子、汽车电子等领域对无源元器件的需求持续增加,推动了市场的发展。

3.5G技术的普及:5G技术的商用将带动无源元器件市场的增长。

5G网络的高速传输和低时延要求,需要大量的无源元器件来支持。

市场挑战尽管无源元器件市场具有巨大的潜力,但仍面临一些挑战:1.厂商竞争激烈:市场上有许多无源元器件供应商,竞争异常激烈。

厂商需要通过不断改进产品质量和提供差异化服务来争取市场份额。

2.价格压力:由于有源元器件市场的竞争,无源元器件市场价格较低,导致利润空间有限。

市场前景随着数字化转型和5G技术的进一步普及,无源元器件市场的前景仍然充满机会。

未来几年内,新兴技术的应用将进一步推动市场的增长。

同时,电子设备持续增长的趋势将为无源元器件市场带来更多机会。

结论通过本文的分析可以看出,无源元器件市场具有较大的市场规模和潜在机会。

技术进步、电子设备需求的增长以及5G技术的普及将是推动市场发展的关键因素。

埋置元件PCB的发展和无源元件结构的变化

以采用 迄今 的树 脂系P B C 的微 细 图形化 技术 ,因此 出 现 了驱伎 半导 体微 细加 上技术 的S基板 的绝缘 t i 肜 成铜 / 酰 亚胺 等 微 细 多层 线路 的互 连板 的趋 向,如 聚

图2 ( )和 图3( )所示 。但 是这 些 构造 中需 要住 s 2 a i 背面 上 引 出电极 ,而最近 采 用半 导体 开发 的S芯 片上 i

现 1 m以下 的节距 。因此 目前 对硅 基互 连板 寄 予很 0p

而 降 低 去耦 效 果 。因 此去 耦 电容 迎 接 附着 在 I 芯 片 c 上 或 者 在I 芯 片 内 的 多层 线 路 层 内形 成 去 耦 电容 。 C

大期 望 。今后 还有 必要 确 定不使 用S且 可形 成 同样微 i

的 电 容 的线 路 图形 还 是会 产 生 寄 生 成 份 的 影 响 ,从

或 者L w K 层绝 缘层 技术 等进 展 显著 的S上的材 料 o —多 i 和 工艺 。特别 是与I 芯片组合 的硅 上硅 ( inS)结 C S o i 构 , 由于没 有 芯片与 互连板 之 间的热膨 胀 系数差 而产 生 的可 靠 性 问题 连接 两 者 的 凸块 ( u ) 可以实 B mp

化和融合化 。尤其出现了I 芯片内和P B的多层布线 c C

的一 体 化 和 融 合 化 的 动 向。本 文 就 新 的安 装 结 构 的 变 化 以及在 此背 景 下P B内埋 置 的无 源元 件 正在 发生 C 的 显著 构造变 化和 今 后 的方 向加 以叙述 。

元 件 连接 点等 。

S 板 i 基

邶昔 p + 罾 邶 罟 , 目

, 飘 ■

I 片球 C 的 芯

嘲

即使 在 I 芯 片 内 的多 层 线 路 中也 存 在 同样 深刻 的 问 C

什么是无源元件?分立元件的局限性

什么是无源元件?分立元件的局限性集成无源器件在我们的行业中并不是什么新事物——它们由来已久且众所周知。

实际上,ADI公司过去曾为市场生产过这类元件。

当芯片组将独立的分立无源器件或者是集成无源网络作为其一部分包含在内时,需要对走线寄生效应、器件兼容性和电路板组装等考虑因素进行仔细的设计管理。

虽然集成无源器件继续在业界占据重要地位,但只有当它们被集成到系统级封装应用中时才能实现其最重要的价值。

几年前,ADI开始推出新的集成无源技术计划(iPassives™)。

ADI 旨在通过这项计划提供二极管、电阻、电感和电容等无源元件,从而能够更广泛地涵盖信号链设计,同时克服现有采用无源元件方法的局限性和复杂性。

ADI 的客户群对具有高效空间尺寸的更完整解决方案的需求,也推动了这项计划的发展。

从设计人员的角度来看,iPassives可以被视为一种灵活的设计工具,能够在极短的开发周期内设计出具有同类最佳性能和鲁棒性的系统解决方案。

ADI 拥有许多信号调理IC,独特硅制造工艺使这些IC 能够实现卓越的性能。

ADI 可以充分利用其现有产品的多样性来生产具有卓越性能特征的即插即用系统,而无需开发高度复杂的集成流程。

在高度可定制的网络中将集成无源技术与所有这些现有技术紧密结合,并利用系统级封装技术进行封装,从而可创建完全经过认证、测试和表征的Module® 器件。

以前采用板级解决方案的系统现在可以简化为单个器件。

从我们的客户角度来看,他们现在可以获得完整的解决方案,具有出色的开箱即用性能,可缩短开发周期并节约成本,而且所有这些都在非常紧凑的封装内实现。

什么是无源元件?无源元件是无需电源供电的器件,它们的电流和电压之间的关系相对简单。

这些元件包括电阻、电容、电感、变压器(即有效耦合电感)和二极管。

有时电流-电压之间的关系非常简单,就像电阻中电流随电压线性变化一样。

对于二极管来说,电流和电压之间也存在直接关系,只是这种关系是指数关系。

3_无源元件(第三章)

集成无源元件 — 电阻

电阻的匹配

- 不匹配的原因是由集成电路工艺中的不 一致性引起的,例如掩模制作中的尺 寸和对齐误差,注入、扩散和刻蚀过 程中的不均匀性等 - 叉指形 (Interdigitized, Fingered)的结构 可以提高元件之间的匹配程度 - 中 心 对 称 (Common-centeroid, symmetrical)的结构具有更好的匹配特 性,但是走线比较复杂,并且可能引 起寄生量的失配 R□ - 使用 Dummy Layout 保护边缘元件 distance

问题:电源滤波电容起什么作用?如何选择电源滤波电容?

第三章 Z. Q. LI 11

分立无源元件

高频电感

─ 主要作用:偏置网络 (又称高频扼流圈, RFC)、谐振电路和匹配网络等。 ─ 高频电感等效电路 自谐振频率

L

RS

CS

问题:如何选择电源滤波电感?

第三章

RFC阻抗绝对值与频率的关系

12

Z. Q. LI

Sheet Resistance Polysilicon Diffusion (silicide) Well 20-50Ω/sq (non-silicide) 1-5 Ω/sq (silicide) 15-30Ω/sq (N+) 40-200Ω/sq (P+) 1-5kΩ/sq (N-Well) Tolerance Absolute: ±10% Matching: 2% Absolute: ±2-10% Matching: 0.1-0.5% Absolute: ±30% Matching: 5% Temperature Coefficient 500-1500ppm/℃ 500-1500ppm/℃ 3000 ppm/℃

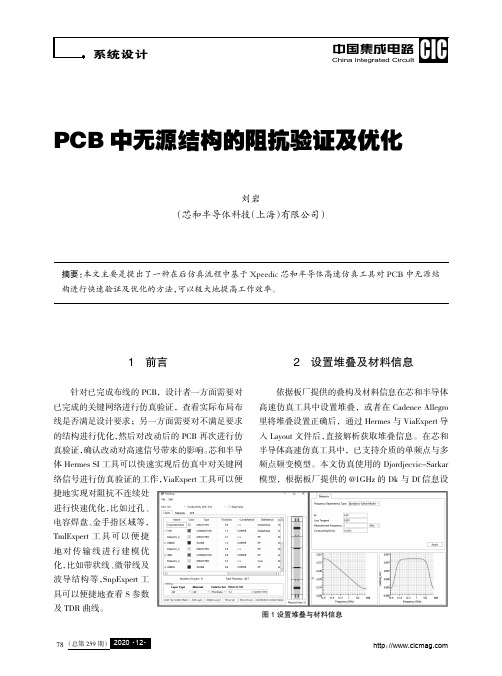

PCB中无源结构的阻抗验证及优化

http ://1前言针对已完成布线的PCB,设计者一方面需要对已完成的关键网络进行仿真验证,查看实际布局布线是否满足设计要求;另一方面需要对不满足要求的结构进行优化,然后对改动后的PCB 再次进行仿真验证,确认改动对高速信号带来的影响。

芯和半导体Hermes SI 工具可以快速实现后仿真中对关键网络信号进行仿真验证的工作,ViaExpert 工具可以便捷地实现对阻抗不连续处进行快速优化,比如过孔、电容焊盘、金手指区域等,TmlExpert 工具可以便捷地对传输线进行建模优化,比如带状线、微带线及波导结构等,SnpExpert 工具可以便捷地查看S 参数及TDR 曲线。

2设置堆叠及材料信息依据板厂提供的叠构及材料信息在芯和半导体高速仿真工具中设置堆叠,或者在Cadence Allegro 里将堆叠设置正确后,通过Hermes 与ViaExpert 导入Layout 文件后,直接解析获取堆叠信息。

在芯和半导体高速仿真工具中,已支持介质的单频点与多频点频变模型。

本文仿真使用的Djordjecvic-Sarkar 模型,根据板厂提供的@1GHz 的Dk 与Df 信息设PCB 中无源结构的阻抗验证及优化刘岩(芯和半导体科技(上海)有限公司)摘要:本文主要是提出了一种在后仿真流程中基于Xpeedic 芯和半导体高速仿真工具对PCB 中无源结构进行快速验证及优化的方法,可以极大地提高工作效率。

图1设置堆叠与材料信息78http ://图3差分对2的模型及TDR 结果图2差分对1的模型及TDR 结果图4金手指处FootPrint、3D 模型及TDR 结果置仿真参数。

Layout 工程师已按照板厂建议的差分线100Ohm 阻抗要求的线宽与间距布线。

下面通过导入Layout 文件进行仿真验证当前设计是否满足阻抗要求,若不满足,则需进一步优化。

3仿真验证关键网络的阻抗由于当前Layout 设计中的关键网络布局一致性较好,可以取具有代表性的网络进行仿真验证。

印制电路板基板材料之BT树脂-深联电路板

印制电路板基板材料之BT树脂-深联电路板作者:深圳市深联电路有限公司BT(Bismaleimide Triazine)板,全称BT树脂基板材料,如:BT树脂基覆铜板,是重要的用于PCB(印制电路板)的一种特殊的高性能基板材料。

BT树脂具有以下列优点:1、Tg点高达180℃,耐热性非常好,BT制成覆铜箔板材,同箔的抗撕强度(P eel Strength)、挠性强度也非常理想,钻孔后的胶渣(Smear)甚少。

2、可进行难燃处理,以达到UL94V-0的要求。

3、介质常数及散逸因子小,因此对于高频和高速传输的电路板非常有利;4、耐化学腐蚀性、搞溶剂性好;绝缘性能高。

BT树脂覆铜箔板的应用有以下几个方面:1、BT树脂基板可作为COB设计的电路板COB的芯片内,电极与基板焊盘的互连是用20-40um的金丝或硅铝丝,通过金丝球焊或超声压焊工艺完成的,这种互连工艺在英文中被称为ware bonding。

由于ware bonding过程的高温,会使基板表面变软而造成打线失败。

BT/EPOX Y高性能板材可克服此缺点。

2、BT树脂基板可作为BGA、PGA、MCM-Ls等半导体封装的载板半导体封装测试中,有两个很重要的常见问题,一是漏电现象,或称CAF(co nductive anodic filament),一是爆米花现象(受湿气及高温冲击)。

这两点也是BT/EPOXY基板可以避免的。

3、BT树脂基板可作为IPD(集成无源元件)的基板IPD(集成无源元件)是在基板内置无源元件的新技术。

电子设备的功能越来越强,而体积和重量越来越小,势必造成元件越来越小,组装密度越来越高,使组装难度达到设备和工艺的极限程度,而且可靠性也受到严重威胁。

最近几年,台湾和日本通过基板与组装工艺之间的结合,在多层板中预埋R、C、L元件,开发出IP D(集成无源元件),这样既减少了外贴元件的数量,又实现了高密度组装,同时还提高了可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

关键字:集成无源元件 PCB技术

集成无源元件技术可以集成多种电子功能,具有小型化和提高系统性能的优势,以取代体积庞大的分立无源元件。

文章主要介绍了集成无源元件技术的发展情况,以及采用IPD薄膜技术实现电容、电阻和电感的加工,并探讨了IPD对PC B技术发展的影响。

1 引言

随着电子技术的发展,半导体从微米制程进入纳米制程后,主动式电子元件的集成度随之大幅提升,相对搭配主动元件的无源元件需求量更是大幅增长。

电子产品的市场发展趋势为轻薄短小,所以半导体制程能力的提升,使相同体积内的主动元件数大增,除了配套的无源元件数量大幅增加,也需要有较多的空间来放置这些无源元件,因此必然增加整体封装器件的体积大小,这与市场的发展趋势大相径庭。

从成本角度来看,总成本与无源元件数量成正比关系,因此在大量无源元件使用的前提下,如何去降低无源元件的成本及空间,甚至提高无源元件的性能,是当前最重要的课题之一。

IPD(Integrated Passiv e Dev ices集成无源元件)技术,可以集成多种电子功能,如传感器、射频收发器、微机电系统MEMS、功率放大器、电源管理单元和数字处理器等,提供紧凑的集成无源器件IPD产品,具有小型化和提高系统性能的优势。

因此,无论是减小整个产品的尺寸与重量,还是在现有的产品体积内增加功能,集成无源元件技术都能发挥很大的作用。

在过去的几年中,IPD技术已经成为系统级封装(SiP)的一个重要实现方式,IPD技术将为“超越穆尔定律”的集成多功能化铺平道路;同时,PC B的加工可以引入IPD技术,通过IPD技术的集成优势,可以弥合封装技术和PC B技术之间不断扩大的差距。

IPD集成无源元件技术,从最初的商用技术已经发展到目前以取代分立无源元件,在ESD/EMI、RF、高亮度LED和数字混合电路等行业带动下稳步增长。

2 薄膜IPD技术介绍

IPD技术,根据制程技术可分为厚膜制程和薄膜制程,其中厚膜制程技术中有使用陶瓷为基板的低温共烧陶瓷LTCC(Low Temperature Co-f iredCeramics)技术和基于HDI高密度互连的PCB印制电路板埋入式无源元件(Embedded Passiv es)技术;而薄膜IPD技术,采用常用的半导体技术制作线路及电容、电阻和电感。

LTCC技术利用陶瓷材料作为基板,将电容。

电阻等被动元件埋入陶瓷基板中,通过烧结形成集成的陶瓷元件,可大幅度缩小元件的空间,但随着层数的增加,制作难度及成本越高,因此LTCC元件大多是为了某一特定功能的电路;HDI埋入式元器件的PCB技术通常用于数字系统,在这种系统里只适用于分布装焊的电容与中低等精度的电阻,随着元件体积的缩小,SMT设备不易处理过小元件。

虽然埋入式印刷电路板技术最为成熟,但产品特性较差,公差无法准确把握,因为元件是被埋藏在多层板之内,出现问题后难以进行替换或修补调整。

相比LTCC技术和PCB埋置元器件技术,集成电路的薄膜IPD技术,具有高精度、高重复性、尺寸小、高可靠度及低成本等优点,未来势必成为IPD主流,本文将主要就薄膜IPD技术进行介绍。

3 薄膜集成无源元件技术的发展现况

薄膜IPD技术采用曝光、显影、镀膜、扩散、刻蚀等薄膜制程,一个有代表性的薄膜集成无源工艺的剖面示意图如图1所示,这个工艺能制作各种电阻。

电容和电感元件,以及低电感接地板和连接无源元件的传输线走线。

薄膜结构在合适的载体衬底材料上制造,工艺既要能满足所要求的元件性能和精度指标,还不能复杂,需要掩模数较少(一般为6~10张)。

每个无源元件通常占据不到1 mm2的面积,以便能在面积和成本方面与表面贴装技术的分立元件竞争。

根据现有的IPD结构,以发展厂商分别介绍如下:

(1)Telephus

Telephus发展的IPD采用厚铜制程,该制程可以为只具有无源元件线路提高性能。

降低成本以及减小尺寸,如滤波器和分工器,厚铜金属层(10 mm)和硅绝缘表面使无线通信系统和集成RF模组具有高性能表现,而低介电常数材料适用于减少金属层间的寄生电容,其IPD结构如图2所示。

(2)IMEC

IMEC的薄膜技术也是采用电镀铜做为连接线路,BC B做为介电层,Ni/Au层做为最终连接面金属,使用多达4层的金属层。

其IPD结构如图3所示。

(3)Dai Nippon

Dai Nippon发展的IPD电阻以Ti/Cr为主,电容采用阳极氧化形成Ta2O5的制程,电感设计为有微带线和螺旋电感,线路以铜为主。

其IPD结构如图4所示。

(4)Sy Chip

Sy Chip发展的IPD以TaSi为电阻材料,电容的介电材料为Si3N4,上电极为Al,下电极为TaSi,电感和线路材料都采用铝。

其IPD结构如图5所示。

有一些公司正在采用MEMS工艺来发展IPD,如PHS MEMS公司,据该公司解释,制造MEMS元件的方法基本上来自IC产业。

同时,一些老牌公司在开发相关技术的同时,也通过收购等手段获得市场和技术,如村田(Murata)就收购了Sy Chip公司,期望通过该次收购扩张其在射频应用市场的份额。

4 薄膜集成无源元件技术的结构与制程

薄膜制程与厚膜制程最大的差异就在于产生的膜厚,一般所谓的厚膜厚度多在5μm ~ 10μm以上,而薄膜制程产生的膜厚约在0.01μm ~ 1μm之间。

如果利用薄膜制程同时形成电阻、电容、电感的元件,需要用不同的制程与材料来制作。

薄膜技术应用在半导体集成电路制程,技术发展已经相当成熟,所以在进行制程整合时,只需注意不同元件间材料的相容性,即可达成制程的设计。

整体而言,薄膜IPD集成无源元件,可因不同的产品应用,制作在不同的基板上,基板可选择硅晶片。

氧化铝陶瓷基板、玻璃基板、薄膜IPD集成无源元件技术可以集成薄膜电阻。

电容和电感于一体,其制程技术开发,包括:微影加工技术、薄膜沉积加工技术、蚀刻加工技术、电镀加工技术、无电极电镀加工技术,整个加工流程如图6所示。

除了无源元件的整合,在硅晶片上也可以结合主动元件的制程,将无源元件与主动元件电路整合以达到多功能化的需求。

下面就薄膜电阻。

电容和电感的加工分别作简单介绍。

(1)薄膜电阻加工

薄膜电阻的制作方式通常利用溅射制程,电阻材料电镀于绝缘基材上,再利用光阻与刻蚀的技术,加工出电阻图形以获得设计的电阻值,其制程示意图如图7所示。

在材料的运用上,需要考虑电阻材料的TCR即不同温度下的电阻变化率。

薄膜电阻的形成方式有真空蒸镀、溅射、热分解以及电镀,而常用的电阻材料则包含有单一成分金属。

合金及金属陶瓷三类。

(2)薄膜电容加工

因为MIS(Metal-Insulator-Semiconductor金属-绝缘体-半导体结构)薄膜电容利用半导体作为底电极,使电容本身具有寄生电阻,造成元件的共振频率降低,无法应用于200 MH z以上的率,所以高频的应用就必须要选择MI M(Metal-Insulator-Metal金属-绝缘体-半导体结构)薄膜电容,MI M电容可降低寄生电阻值,进而提高元件共振频率,而共振频率则是取决于介电材料的自振频率。

与薄膜电阻一样,薄膜电容需要考虑电容变化率,并且介电常数也需要考虑。

另外,需要注意基材的表面粗糙度Ra<0.3 μm,若粗糙度Ra值超过规定范围,介电层容易被下底电极的突丘(Hill Lock)穿透,形成短路.

(3)薄膜电感加工

薄膜电感制程与电阻制程相似,但主要的设计考虑在于如何降低其寄生电容和提高元件的品质因子(Q),由于电感特性比率,考虑到降低其直流阻抗以提高Q值的需求,所以电感导线的膜厚必须要在5 μm ~10 μm之间,所以制程上通常采用电镀方式形成电感导线以符合需求.

基材的表面粗糙度会影响薄膜电感的特性,尤其在高频时,过高的表面粗糙度容易造成杂讯的升高,造成高频特性降低,所以基材的选择、制作及加工都会影响到整个薄膜元件的效能.

5 IPD技术对PCB技术发展的影响

随着技术的进步,PC B印制电路板朝着更高精度和更高密度的方向发展,而且逐步和IC封装领域高度集成,无源元件集成符合当今电子系统的发展趋势,IPD技术已经成为系统级封装(SiP)的一个重要实现方式.

IPD集成无源元件技术具有布线密度高、体积小、重量轻;集成度高,可以埋置电阻、电感、电容等无源器件及有源芯片;高频特性好,可用于微波及毫米波领域等优点。

将薄膜IPD集成无源元件技术应用于PC B加工,达到节约封装面积、提高信号的传输性能、降低成本、

提高可靠性等目的;通过IPD技术的集成优势,弥合封装技术和PCB技术之间不断扩大的差距,可以有效减小电子整机与系统的体积和重量,具有广阔的市场前景.

对IPD集成无源元件应用PCB加工,可选用高导热的金属、金刚石、陶瓷或铝-炭化硅复合材料等作基板,制造高密度高功率多层电路基板,同时应加强IPD无源集成PCB基板的工艺提升、材料特性的提高以及低成本化,以及加快在微波通讯、高密度集成和大功率等领域的应用.

6 结论

薄膜IPD集成无源元件技术可以集成多种电子功能,具有小型化和提高系统性能的优势,可以取代体积庞大的分立无源元件.同时,PCB 的加工可以引入IPD技术,通过IPD技术的集成优势,可以弥合封装技术和PCB技术之间不断扩大的差距.

薄膜IPD集成无源元件技术的迅速发展,使无源集成技术进入了实用化和产业化阶段,新一代无源元件和相关的集成技术,将被广泛应用于航空航天、军工、医疗、工控和通讯等各个领域的电子行业,因此发展IPD技术,无论是对企业本身的发展还是提升国内行业的竞争力都具有重要的意义.。