vhdl加法计数器

vhdl BCD码加法器

实验一BCD码加法器一、实验目的了解BCD 码的构成。

了解BCD 码加法器的原理和设计实现方法。

巩固Quartus II 的使用。

二、实验内容与要求通过键盘输入两组4BIT的二进制数据,按照二进制加法器原理进行加和,求出和合进位,并通过电路静态数码LED显示灯输出显示,完成编译、综合、适配、仿真、实验箱上的硬件测试。

三、实验平台(1)硬件:计算机、GX-SOC/SOPC-DEV-LABCycloneII EP2C35F672C8核心板(2)软件:Quartus II四、实验原理BCD码是二进制编码的十进制码,也就是用4位二进制数来表示十进制中的0~9这十个数。

由于4位二进制数有0000~1111共16种组合,而十进制数只需对应4位二进制数的10种组合,故从4位二进制数的16种组合中取出10种组合来分别表示十进制中的0~9,则有许多不同的取舍方式,于是变形成了不同类型的BCD码。

当BCD码相加的值小于等于9时,结果仍旧是正确的BCD码;当两个码相加的结果大于9时,必须作加6的修正处理,对于大于19的值作加12的修正处理,对于大于29的值作加18的修正处理。

然后根据仿真进行实验及验证。

六、仿真截图七、硬件实现八、程序代码1LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY f_ADDER IsPort (x: In Std_Logic;y: In Std_Logic;cin: In Std_Logic;cout: Out Std_Logic;sum: Out Std_Logic);END f_ADDER;ARCHITECTURE fd1 Of f_ADDER Is Component HADDERPort( a,b: In Std_Logic;co,so: Out Std_Logic);END Component;Component oraPort(a,b: In Std_Logic;c: Out Std_Logic);END Component;Signal d,e,f: Std_Logic;BeginU1: HADDERPort Map(a=>X,b=>Y,Co=>d,so=>e);U2:HADDERPort Map(a=>e,b=>cin,Co=>f,so=>sum);U3:ora Port Map(a=>d,b=>f,c=>cout);END ARCHITECTURE fd1;2LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY HADDER IsPort (a,b: In Bit;Co, So: Out Bit);END HADDER;ARCHITECTURE fh1 Of HADDER Is BEGINSo <= (a Xor b);Co <= (a And b);END fh1;3LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY ora IsPort ( a: in Std_Logic;b: in Std_Logic;c: out Std_Logic);END ora;ARCHITECTURE org OF ora ISBEGINc <= a Or b;END org;4Library ieee;Use ieee.std_logic_1164.all;Entity Qadd isPort (a:in std_logic_VECTOR(7 DOWNTO 0);b:in std_logic_VECTOR(7 DOWNTO 0);--cin:in std_logic;s:out std_logic_VECTOR(7 DOWNTO 0));End Qadd;Architecture one of Qadd isSignal c0,c1,c2,c3,c4,c5,c6,c7 : std_logic;Component f_ADDERPort (x: In Std_Logic;y: In Std_Logic;cin: In Std_Logic;cout: Out Std_Logic;sum: Out Std_Logic);END Component;Beginu1 :F_ADDERPort map(sum=>s(0),cout=>c0,X=>a(0),Y=>b(0),cin=>'0'); u2 :F_ADDERPort map(sum=>s(1),cout=>c1,X=>a(1),Y=>b(1),cin=>c0 ); u3 : F_ADDERPort map(sum=>s(2),cout=>c2,X=>a(2),Y=>b(2),cin=>c1 ); u4 : F_ADDERPort map(sum=>s(3),cout=>c3,X=>a(3),Y=>b(3),cin=>c2 ); u5 : F_ADDERPort map(sum=>s(4),cout=>c4,X=>a(4),Y=>b(4),cin=>c3 ); u6 : F_ADDERPort map(sum=>s(5),cout=>c5,X=>a(5),Y=>b(5),cin=>c4 ); u7 :F_ADDERPort map(sum=>s(6),cout=>c6,X=>a(6),Y=>b(6),cin=>c5 ); u8 : F_ADDERPort map(sum=>s(7),cout=>c7,X=>a(7),Y=>b(7),cin=>c6 ); END;九、实验总结。

VHDL各种计数器程序全新

1. 具有CLK,Q端口的简单加法计数器,要程序和最后的RTL图;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT4 ISPORT ( CLK : IN STD_LOGIC;Q : OUT INTEGER RANGE 15 DOWNTO 0);END;ARCHITECTURE behav OF CNT4 ISSIGNAL D,Q1 : INTEGER RANGE 15 DOWNTO 0;BEGINPROCESS (CLK)BEGINIF CLK'EVENT AND CLK='1'THEN Q1<=D;END IF;END PROCESS;D<=Q1+1;Q<=Q1;END behav;2. 具有异步清零aclr,CLK,Q端口的加法计数器,要程序和最后的RTL图;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL ;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT4 ISPORT ( CLK,ACLR : IN STD_LOGIC;Q : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)); END ;ARCHITECTURE behav OF CNT4 ISSIGNAL Q1 : STD_LOGIC_VECTOR(15 DOWNTO 0);BEGINPROCESS (CLK,ACLR)BEGINIF ACLR='0' THENQ1<=(OTHERS=>'0');ELSIF CLK'EVENT AND CLK='1' THENQ1<=Q1+1;END IF;END PROCESS;Q<=Q1;END behav;3. 具有同步清零sclr,CLK,Q端口的加法计数器,要程序和最后的RTL图;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL ;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT4 ISPORT ( CLK,SCLR : IN STD_LOGIC;Q : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)); END ;ARCHITECTURE behav OF CNT4 ISSIGNAL Q1 : STD_LOGIC_VECTOR(15 DOWNTO 0);BEGINPROCESS (CLK,SCLR)BEGINIF CLK'EVENT AND CLK='1' THENIF SCLR='1' THENQ1<=(OTHERS=>'0');ELSEQ1<=Q1+1;END IF;END IF;END PROCESS;Q<=Q1;END behav;4. 具有异步置位apre,CLK,Q端口的加法计数器,要程序和最后的RTL图;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT4 ISPORT(CLK :IN STD_LOGIC;APRE:IN STD_LOGIC;Q :OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END;ARCHITECTURE behav OF CNT4 ISSIGNAL Q1 :STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,APRE)BEGINIF APRE='1' THENQ1<="0001";ELSIF CLK'EVENT AND CLK='1' THENQ1<=Q1+1;END IF;END PROCESS;Q<=Q1;END behav;5. 具有同步置位spre,CLK,Q端口的加法计数器,要程序和最后的RTL图;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT4 ISPORT(CLK :IN STD_LOGIC;SPRE:IN STD_LOGIC;Q :OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END;ARCHITECTURE behav OF CNT4 ISSIGNAL Q1 :STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,SPRE)BEGINIF CLK'EVENT AND CLK='1' THENIF SPRE='1' THENQ1<="0001";ELSEQ1<=Q1+1;END IF;END IF;Q<=Q1;END behav;6. 具有异步清零aclr,异步置位apre,CLK,Q端口的加法计数器,要程序和最后的RTL 图;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT4 ISPORT(CLK :IN STD_LOGIC;ACLR:IN STD_LOGIC;APRE:IN STD_LOGIC;Q :OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END;ARCHITECTURE behav OF CNT4 ISSIGNAL Q1 :STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,APRE,ACLR)BEGINIF ACLR='1' THENQ1<="0000";ELSEIF APRE='1' THENQ1<="0001";ELSIF CLK'EVENT AND CLK='1' THENQ1<=Q1+1;END IF;END PROCESS;Q<=Q1;END behav;7. 具有同步使能ENB,CLK,Q端口的加法计数器,要程序和最后的RTL图;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT4 ISPORT(CLK :IN STD_LOGIC;ENB :IN STD_LOGIC;Q :OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END;ARCHITECTURE behav OF CNT4 ISSIGNAL Q1 :STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,ENB)BEGINIF CLK'EVENT AND CLK='1' THENIF ENB='1' THENQ1<=Q1+1;END IF;END IF;END PROCESS;Q<=Q1;END behav;8. 具有异步清零aclr,异步置位apre,同步使能ENB,CLK,Q端口的加法计数器,要程序和最后的RTL图;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT4 ISPORT(CLK :IN STD_LOGIC;ACLR:IN STD_LOGIC;ENB :IN STD_LOGIC;APRE:IN STD_LOGIC;Q :OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END;ARCHITECTURE behav OF CNT4 ISSIGNAL Q1 :STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,APRE,ACLR,ENB)BEGINIF ACLR='1' THENQ1<="0000";ELSEIF APRE='1' THENQ1<="0001";ELSIF CLK'EVENT AND CLK='1' THENIF ENB='1' THENQ1<=Q1+1;END IF;END IF;END IF;END PROCESS;Q<=Q1;END behav;1.生活如意,事业高升。

vhdl通用十进制加法器

湖南人文科技学院课程设计报告课程名称:VHDL语言与EDA课程设计设计题目:通用十进制加法器系别:通信与控制工程系专业:电子信息工程班级:学生姓名:学号:起止日期:指导教师:教研室主任:指导教师评语:指导教师签名:年月日成绩评定项目权重成绩1、设计过程中出勤、学习态度等方面0.22、课程设计质量与答辩0.53、设计报告书写及图纸规范程度0.3总成绩教研室审核意见:教研室主任签字:年月日教学系审核意见:主任签字:年月日摘要随着科技的发展,通用十进制加法器的应用已广泛融入到现实生活中。

EDA 技术的应用引起电子产品及系统开发的革命性变革。

本文采用EDA技术设计,并以VHDL语言为基础制作的通用十进制加法器。

该系统借助于强大的EDA工具和硬件描述语言可实现两个一位以上的十进制数的加法,在输入两个十进制数之后,给出两个数的相加结果。

本设计充分利用VHDL“自顶向下”的设计优点以及层次化的设计概念,提高了设计的效率。

设计主要步骤:首先利用QUARTUS‖来编辑、编译、仿真各个模块;然后以原理图为顶层文件建立工程,再进行引脚锁定、编译、下载,最后采用杭州康芯电子有限公司生产的GW48系列/SOPC/EDA实验开发系统,进行硬件测试。

关键词:通用十进制加法器;EDA技术;VHDL语言; QUARTUS‖目录设计要求 (1)1、方案论证与对比 (1)1.1方案一 (1)1.2方案二 (1)1.3 方案的对比与选择 (2)2、设计原理 (2)3、通用十进制加法器的主要硬件模块 (3)3.1 4位BCD码全加器模块 (3)3.2八加法器的实现框图 (3)4、调试与操作 (4)4.1通用十进制加法器的功能仿真 (4)4.2模式选择与引脚锁定 (4)4.2.1模式选择 (4)4.2.2引脚锁定 (5)4.3设备与器件明细表 (6)4.4调试 (6)4.4.1软件调试 (6)4.4.2硬件调试 (6)5、总结与致谢 (7)5.1总结与思考 (7)5.2致谢 (7)附录 (8)附录一 (8)附录二 (9)参考文献 (11)通用十进制加法器设计要求1、用VHDL 硬件描述语言设计4位的BCD 码全加器;2、以4位BCD 码全加器为模块设计两位十进制数的加法。

VHDL设计FPGA数字系统:计算器.docx

1.3文章小结

本章介绍这几世纪以来的计算器发展,还有本次设计的研究任务,为后续的设计打下基础。

第二章项目基础

2.1软件与硬件介绍

2.1.1 EDA

电子设计自动化(英语:Electronic design automation,缩写:EDA)即电子设计自动化技术,是利用计算机工作平台,从事电子系统和电路设计的一项技术[3]。

硬件描述语言HDL (Hardware Description Language )是一种用于设计硬件电子系统的计算机语言,它用软件编程的方式来描述电子系统的逻辑功能、电路结构和连接形式,与传统的门级描述方式相比,它更适合大规模系统的设计[4]。

2.1.2 EDA的特点及发展

现在人类社会已经步入了信息时代,各种各样的信息技术在我们的生活当中发挥着越来越重要的作用。信息时代的高速发展离不开电子设计技术的发展和相关电子产品的进步,而他们的核心就是EDA技术。

This design studied Digital System is composed of added and subtracted of module to complete, including the keyboard input module, decoding module, calculate the main control module and a digital tube display module. When the keyboard input signal passes through these modules, complete data display computing requirements. This calculation control system Math four computing module is the core.

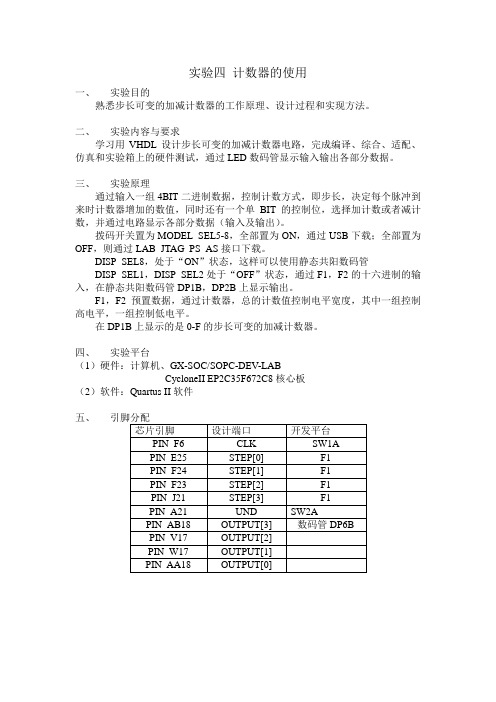

vhdl 计数器的使用

实验四计数器的使用一、实验目的熟悉步长可变的加减计数器的工作原理、设计过程和实现方法。

二、实验内容与要求学习用VHDL设计步长可变的加减计数器电路,完成编译、综合、适配、仿真和实验箱上的硬件测试,通过LED数码管显示输入输出各部分数据。

三、实验原理通过输入一组4BIT二进制数据,控制计数方式,即步长,决定每个脉冲到来时计数器增加的数值,同时还有一个单BIT的控制位,选择加计数或者减计数,并通过电路显示各部分数据(输入及输出)。

拨码开关置为MODEL_SEL5-8,全部置为ON,通过USB下载;全部置为OFF,则通过LAB_JTAG_PS_AS接口下载。

DISP_SEL8,处于“ON”状态,这样可以使用静态共阳数码管DISP_SEL1,DISP_SEL2处于“OFF”状态,通过F1,F2的十六进制的输入,在静态共阳数码管DP1B,DP2B上显示输出。

F1,F2预置数据,通过计数器,总的计数值控制电平宽度,其中一组控制高电平,一组控制低电平。

在DP1B上显示的是0-F的步长可变的加减计数器。

四、实验平台(1)硬件:计算机、GX-SOC/SOPC-DEV-LABCycloneII EP2C35F672C8核心板(2)软件:Quartus II软件五、六、仿真截图七、硬件实现八、程序代码1--10 位计数SCAN TOP_LEVEL程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;use ieee.std_logic_unsigned.all;ENTITY ACOUNT100 ISPORT(clk,clr,en,en6:IN STD_LOGIC ;count1 : out std_logic ;ledseg : out std_logic_vector(6 downto 0);ledcom :out std_logic_vector(5 downto 0)); END;ARCHITECTURE ONE OF ACOUNT100 IS COMPONENT clkgen ISPORT(clkin:IN STD_LOGIC ;clkout: OUT STD_LOGIC);END COMPONENT;COMPONENT COUNT10a ISPORT(clk,clr,en:IN STD_LOGIC ;q:OUT STD_LOGIC_vector(3 downto 0);count1:OUT STD_LOGIC);end COMPONENT;COMPONENT bcd_7seg isport(bcd_led :in std_logic_vector(3 downto 0);--input bcdledseg : out std_logic_vector(6 downto 0));--output to 7 segmentend COMPONENT;COMPONENT mx isport(s:in std_logic;a,b:in std_logic_vector(3 downto 0);q:out std_logic_vector(3 downto 0));end COMPONENT;COMPONENT comcoun isport(clk : in std_logic;--synchronouse clockenable : in std_logic;--scan clockcomclk : out std_logic_vector(2 downto 0));--output countend COMPONENT;COMPONENT com_encode isport(s :in std_logic;--input countledcom :out std_logic_vector(5 downto 0));--output encodeend COMPONENT ;signal clk1,c10: std_logic;signal q1,q2,bcd: std_logic_vector(3 downto 0);BEGINU1:clkgen PORT MAP(CLKIN=>CLK,CLKOUT=>CLK1);U2:COUNT10a PORT MAP(clk=>CLK1,clr=>clr,en=>en,q=>q1,count1=>c10);U3:COUNT10a PORT MAP(clk=>CLK1,clr=>clr,en=>c10,q=>q2,count1=>count1); U4:MX PORT MAP(S=>CLK1,A=>q1,b=>q2,q=>bcd);U5:bcd_7seg PORT MAP(bcd_led=>bcd,ledseg=>ledseg);U6:com_encode PORT MAP(s=>clk1,ledcom=>ledcom );end;2---clkgen.vhdLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;use ieee.std_logic_unsigned.all;ENTITY clkgen ISPORT(clkin:IN STD_LOGIC ;clkout: OUT STD_LOGIC);END;ARCHITECTURE even OF clkgen ISconstant N:Integer:=50000000;--constant N:Integer:=10;SIGNAL coun:integer range 0 to N;SIGNAL clk1:STD_LOGIC;BEGINPROCESS(clkin)BEGINIF(clkin'EVENT AND clkin='1')THENIF(coun=N)THENcoun<=0;clk1<=Not clk1;elsecoun<=coun+1;END IF;END IF;END PROCESS;clkout<=clk1;END even;3--10 位计数器程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY COUNT10a ISPORT(clk,clr,en:IN STD_LOGIC;count1:OUT STD_LOGIC;q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END COUNT10a ;ARCHITECTURE rtl OF COUNT10a ISSIGNAL qs:STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL ca:STD_LOGIC;BEGINPROCESS(clk)BEGINIF(clk'EVENT AND clk='1')THENIF(clr='1')THENqs<="0000";ELSIF(en='1')THENIF(qs="1001")THENqs<="0000";ca<='0';ELSIF(qs="1000")THEN --在计数到8时,即让进位赋值1,--由于信号会产生一个滞后,使得实际ca在9时出现qs<=qs+1;ca<='1';ELSEqs<=qs+1;ca<='0';END IF;END IF;END IF;END PROCESS;PROCESS(ca,en)BEGINq<=qs;count1<=ca AND en;END PROCESS;END rtl;4library ieee;use ieee.std_logic_1164.all;entity mx isport(s:in std_logic;a,b:in std_logic_vector(3 downto 0);q:out std_logic_vector(3 downto 0));end mx;architecture rtl of mx isbeginq<= a WHEN s = '0' ELSE b ;end rtl;5--七段显示扫描电路--comcoun.vhd 7 segment com scan counterlibrary ieee ;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity comcoun isport(clk : in std_logic;--synchronouse clockenable : in std_logic;--scan clockcomclk : out std_logic_vector(2 downto 0));--output countend comcoun;architecture behavior of comcoun issignal q : std_logic_vector(2 downto 0);--internal counted signal beginfscan:process(clk)beginif (clk'event and clk='1') thenif (enable='1') thenif q>=1 thenq<="000";--initial counterelseq<=q+1;--countingend if;end if;end if;end process fscan;comclk<=q; --output internal countend behavior;6library ieee ;use ieee.std_logic_1164.all;entity bcd_7seg isport(bcd_led :in std_logic_vector(3 downto 0);--input bcdledseg : out std_logic_vector(6 downto 0));--output to 7 segment end bcd_7seg;architecture behavior of bcd_7seg isbeginwith bcd_led selectledseg<="0111111" when "0000",--0,3f"0000110" when "0001",--1,06"1011011" when "0010",--2,5b"1001111" when "0011",--3,4f"1100110" when "0100",--4,66"1101101" when "0101",--5,6d"1111101" when "0110",--6,7d"0100111" when "0111",--7,27"1111111" when "1000",--8,7f"1101111" when "1001",--9,6f"1110111" when "1010",--A"1111100"when "1011", --b"0111001"when "1100",--c"1011110" when "1101",--d"1111001"when "1110",--E"1110001" when "1111",--F"0000000" when others;end behavior;7--计数译码电路-- 6 共阴--com_encode.vhd 7 segment com encoderlibrary ieee ;use ieee.std_logic_1164.all;entity com_encode isport(s :in std_logic;--input countledcom :out std_logic_vector(5 downto 0));--output encode end com_encode;architecture behavior of com_encode isbeginledcom<="000001" when s='0' else"000010" ;end behavior;九、实验总结。

VHDL加法器设计1

VHDL 加法器设计设计要求:采用QuartusII 集成开发环境利用VHDL 硬件描述语言设计传播进位加法器,直接进位加法器,线形进位加法器,平方根进位加法器,并比较这四种加法器的性能。

为了便于比较性能,将四种加法器都设定为28位。

一、全加器设计全加器是上述四种加法器的基础部件,首先应当设计一位全加器。

设计原理:i i i iS ABC ABC ABC ABC A B C=+++=⊕⊕0i i C AB BC AC =++VHDL 程序:仿真结果:--一位全加器设计library ieee;use ieee.std_logic_1164.all; entity fulladd isport ( A: in std_logic;B: in std_logic; cin:in std_logic; sumbit:out std_logic; cout:out std_logic );end fulladd;architecture behav of fulladd is beginsumbit<=(A xor B) xor cin;cout<=(a and b) or (cin and a) or (cin and b); end behav;二、传播进位加法器设计实际上加法器就是是全加器的级联,其中的每个FA网络为一个全加器(采用上文所述的全加器)VHDL代码:--传播进位加法器library ieee;use ieee.std_logic_1164.all;use work.all;entity carry_propogate_adder isport (A: in std_logic_vector(27 downto 0);B: in std_logic_vector(27 downto 0);cin:in std_logic;sum:out std_logic_vector(27 downto 0);cout:out std_logic);end carry_propogate_adder;architecture behav of carry_propogate_adder issignal ct:std_logic_vector(28 downto 0);component fulladd isport (A: in std_logic;B: in std_logic;cin:in std_logic;sumbit:out std_logic;cout:out std_logic);end component;beginct(0)<=cin;cout<=ct(28);G1: for i in 0 to 27 generatel1:fulladd port map (A(i),B(i),ct(i),sum(i),ct(i+1));end generate G1;end behav;功能仿真:延时测定:由图中的两个时间bar 的差值可看出,sum 值和cout 值几乎同时计算出,其Tdelay=28.332ns (cin 无关)三、直接进位加法器设计 设计原理:首先将AB 输入转换为PG 输入,若每级的P 输入都是‘1’则直接将Ci 传给Co ,否则像传播进位加法器一样计算其AB-PG 转换网络原理:Fa 全加器原理:P A B G AB=⊕=o i iC G PC S P C =+=⊕VHDL 代码:-- FA 子单元 library ieee;use ieee.std_logic_1164.all;entity Fa isport (Pi,Gi,Ci:in std_logic; Coi,Si:out std_logic); end Fa;architecture Fabehav of Fa is beginCoi<=Gi or (Pi and Ci);Si<=Pi xor Ci; end Fabehav; --ABtoPG 转换网络 library ieee;use ieee.std_logic_1164.all;entity PGNet isport(Ai,Bi:in std_logic; Pi,Gi:out std_logic); end PGNet;architecture PGbehav of PGNet is beginPi<=Ai xor Bi;Gi<=Ai and Bi; end PGbehav; --传播进位加法器 library ieee;use ieee.std_logic_1164.all; entity bypass_adder is port(A,B:in std_logic_vector(27 downto 0); Ci:in std_logic; Sum:out std_logic_vector(27 downto 0); Co:out std_logic );end bypass_adder;architecture adderbehav of bypass_adder is component Fa is port (Pi,Gi,Ci:in std_logic; Coi,Si:out std_logic ); end component; component PGNet is port(Ai,Bi:in std_logic; Pi,Gi:out std_logic ); end component;signal P,G:std_logic_vector(27 downto 0); signal C:std_logic_vector(28 downto 0); signal BP:std_logic; begin C(0)<=Ci; G1: for i in 0 to 27 generate l1: PGNet port map(A(i),B(i),P(i),G(i)); end generate G1; G2: for i in 0 to 27 generate l2:Fa port map (P(i),G(i),C(i),C(i+1),Sum(i)); end generate G2; BP<='1' when P="11111111111111111111111111111111" else '0'; Co<=Ci when BP='1' else C(8); end adderbehav;功能仿真:延时仿真:当通过直接进位网络(图中testp值全部为1时),进位信号有一定提前,但由于计算所有的P值本身也需要一定时间,所以改善并不明显。

vhdl加法器二位BCD码加法器的VHDL源程序如下

vhdl加法器二位BCD码加法器的VHDL源程序如下导读:就爱阅读网友为您分享以下“二位BCD码加法器的VHDL源程序如下”资讯,希望对您有所帮助,感谢您对的支持!二位BCD码加法器的VHDL源程序如下:ibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity bcdadd is ---------------------实体部分port(key:in std_logic;---------------定义key输入口a0,a1,b0,b1:in integer range 0 to 9; -----定义两个加数的输入口a0l,a1l,b0l,b1l,s0l,s1l,s2l:out std_logic_vector(6 downto 0);----定义七个输出数码管s:out std_logic);----定义Key指示灯输出口end;architecture one of bcdadd is ----------结构体部分signal one:integer range 0 to 18; ----定义两个数的个位相加之后的信号signal ten:integer range 0 to 19; -----定义两个数的十位相加之后的信号signal co1,co2:integer range 0 to 1; ----定义个位和十位的进位信号signal s0,s1:integer range 0 to 15;beginp1:process(one,ten,a0,b0,a1,b1,co1)----第一个进程,进行加运算beginone<=a0+b0; --------------------个位相加之和if one>9 then --------------------和大于9,进位为1 co1<=1;s0<=one-10; -----------------------个位的值else -----------------------和小于9,进位为0co1<=0;s0<=one; -------------------------个位的值end if;ten<=a1+b1+co1;----------------------十位相加值和,加数包括个位来的进位if ten>9 then -------------------和大于9,进位为1co2<=1;s1<=ten-10;-------------------十位的值else ----------------------------------和小于9,进位为0co2<=0;s1<=ten;-----------------------十位的值end if;end process p1;p2:process(a0,a1,b0,b1) ----------第二个进程,两个加数的输出数码管显示译码begincase a0 is ----------------------被加数的个位显示译码when 0=>a0l<=“1000000”;when 1=>a0l<=“1111001”;when 2=>a0l<=“0100100”;when 3=>a0l<=“0110000”;when 4=>a0l<=“0011001”;第1页共4页when 5=>a0l<=“0010010”; when 6=>a0l<=“0000010”; when 7=>a0l<=“1111000”; when 8=>a0l<=“0000000”; whenothers=>a0l<=“ZZZZZZZ”; end case; case a1 is ------------------------------被加数的十位显示译码when 0=>a1l<=“1000000”; when 1=>a1l<=“1111001”; when 2=>a1l<=“0100100”; when 3=>a1l<=“0110000”; when 4=>a1l<=“0011001”; when 5=>a1l<=“0010010”; when 6=>a1l<=“0000010”; when 7=>a1l<=“1111000”; when 8=>a1l<=“0000000”; when 9=>a1l<=“0010000”; when others=>a1l<=“ZZZZZZZ”; end case; case b0 is-----------------------------加数的个位显示译码when 0=>b0l<=“1000000”; when 1=>b0l<=“1111001”; when 2=>b0l<=“0100100”; when 3=>b0l<=“0110000”; when 4=>b0l<=“0011001”; when 5=>b0l<=“0010010”; when 6=>b0l<=“0000010”; when8=>b0l<=“0000000”; when 9=>b0l<=“0010000”; when others=>b0l<=“ZZZZZZZ”; end case; case b1 is ----------------------------加数的十位显示译码when 0=>b1l<=“1000000”; when 1=>b1l<=“1111001”; when 2=>b1l<=“0100100”; when 3=>b1l<=“0110000”; when 4=>b1l<=“0011001”; when 5=>b1l<=“0010010”; when 6=>b1l<=“0000010”; when 7=>b1l<=“1111000”; when 8=>b1l<=“0000000”; when 9=>b1l<=“0010000”; when others=>b1l<=“ZZZZZZZ”;第2页共4页end case;end process p2;p3:process(key,s0,s1,co2,a0,a1,b0,b1) --------第三个进程,和的显示译码以及输入大于9是的出beginif key=…0‟ or a0>9 or b0>9 o r a1>9 or b1>9 then --当key等于0或者两个输入中的任何一个位大于9,和的数码显示均为“Z”状态s0l<=“ZZZZZZZ”;s1l<=“ZZZZZZZ”;s2l<=“ZZZZZZZ”;elsecase s0 is-------------------------------和的个位显示译码when 0=>s0l<=“1000000”;when 1=>s0l<=“1111001”;when 2=>s0l<=“0100100”;when 3=>s0l<=“0110000”;when 4=>s0l<=“0011001”;when 5=>s0l<=“0010010”;when 6=>s0l<=“0000010”;when 7=>s0l<=“1111000”;when 8=>s0l<=“0000000”;when 9=>s0l<=“0010000”;wh en others=>s0l<=“ZZZZZZZ”; end case;case s1 is--------------------------------和的十位显示译码when 0=>s1l<=“1000000”;when 1=>s1l<=“1111001”;when 2=>s1l<=“0100100”;when 3=>s1l<=“0110000”;when 4=>s1l<=“0011001”;when 5=>s1l<=“0010010”;when 6=>s1l<=“0000010”;when 7=>s1l<=“1111000”;when 8=>s1l<=“0000000”;when 9=>s1l<=“0010000”;when others=>s1l<=“ZZZZZZZ”; end case;case co2 is --------------------------和的百位显示译码when 0=>s2l<=“1000000”;when 1=>s2l<=“1111001”;end case;end if;end process p3;第3页共4页p4:process(key) -------------第四个进程,设置key的指示灯beginif key=…1‟ then s<=…1‟ ; else s<=…0‟;end if;end process p4;end;第4页共4页百度搜索“就爱阅读”,专业资料,生活学习,尽在就爱阅读网,您的在线图书馆。

maxplus2 cpld vhdl 流水灯的设计 十进制加法计数器的设计 奇偶校验电路的

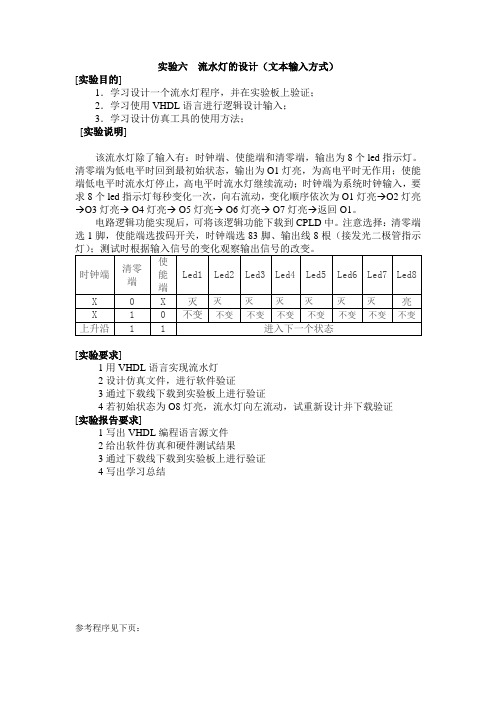

实验六流水灯的设计(文本输入方式)[实验目的]1.学习设计一个流水灯程序,并在实验板上验证;2.学习使用VHDL语言进行逻辑设计输入;3.学习设计仿真工具的使用方法;[实验说明]该流水灯除了输入有:时钟端、使能端和清零端,输出为8个led指示灯。

清零端为低电平时回到最初始状态,输出为O1灯亮,为高电平时无作用;使能端低电平时流水灯停止,高电平时流水灯继续流动;时钟端为系统时钟输入,要求8个led指示灯每秒变化一次,向右流动,变化顺序依次为O1灯亮→O2灯亮→O3灯亮→ O4灯亮→ O5灯亮→ O6灯亮→ O7灯亮→返回O1。

电路逻辑功能实现后,可将该逻辑功能下载到CPLD中。

注意选择:清零端选1脚,使能端选拨码开关,时钟端选83脚、输出线8根(接发光二极管指示[实验要求]1用VHDL语言实现流水灯2设计仿真文件,进行软件验证3通过下载线下载到实验板上进行验证4若初始状态为O8灯亮,流水灯向左流动,试重新设计并下载验证[实验报告要求]1写出VHDL编程语言源文件2给出软件仿真和硬件测试结果3通过下载线下载到实验板上进行验证4写出学习总结参考程序见下页:library ieee;use ieee.std_logic_1164.all;entity liushuideng isport(ena,clk_in,clr: in std_logic;y: out std_logic_vector(7 downto 0));end liushuideng;architecture a of liushuideng issignal clk: std_logic;beginclock:process(clk_in) --输入的时钟为4Mvariable clock_buffer:std_logic; ----定义一个标准逻辑变量clock_buffervariable count_time:integer range 0 to 1999999; ---定义一个整型变量count_time beginif clk_in'event and clk_in='1' thenif count_time=1999999 thencount_time:=0;clock_buffer:=not clock_buffer; --每计2M次数时翻转一次elsecount_time:=count_time+1;end if;end if;clk<=clock_buffer; --输出的时钟为1HZend process;process(clr,clk,ena)variable q: std_logic_vector(7 downto 0); ----定义一个标准逻辑矢量的变量qbeginif(clr='0')thenq:="11111110"; ----按下清零键让它回到O1灯亮elseif clk'event and clk='1' then ---时钟的上升沿if ena='1' then ---ena为高开始移位,ena为低停止移位q:=q(6 downto 0)&q(7); --向右移动移位end if;end if;end if;y<=q;end process;end a;实验七十进制加法计数器的设计(文本输入方式)[实验目的]1.学习设计一个十进制加法计数器程序,并在实验板上验证;2.熟练掌握VHDL语言进行逻辑设计输入;3.学习设计仿真工具的使用方法;[实验说明]该计数器输入有:时钟端、使能端和清零端,输出为1个数码管。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

6、编写一个4位加法计数器VHDL源程序,要求:复位信号reset低电平清零,变高后在clk上升沿开始工作,输入时钟信号为clk,输出为q。

(以十二进制为例)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY counter ISPORT(clk,reset:IN STD_LOGIC;q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END ENTITY priorityencoderARCHITECTURE rtl OF counter ISSIGNAL count: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINq<=cout;PROCESS(clk,reset)ISBEGINIF(reset=’0’)THENcout<="0000";ELSIF(clk’EVENT AND clk=’1’)THENIF(cout="1011")THENcout<="0000"ELSEcout<=cout+’1’;END IF;END IF;END PROCESS;END ARCHITECTURE rtl;4位二进制并行加法器的源程序ADDER4B.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER4B IS --4位二进制并行加法器PORT(CIN:IN STD_LOGIC;--低位进位A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);--4位加数B:IN STD_LOGIC_VECTOR(3 DOWNTO 0);--4位被加数S:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--4位和CONT:OUT STD_LOGIC);END ADDER4B;ARCHITECTURE ART OF ADDER4B ISSIGNAL SINT:STD_LOGIC_VECTOR(4 DOWNTO 0);SIGNAL AA,BB:STD_LOGIC_VECTOR(4 DOWNTO 0);BEGINAA<='0'& A;--将4位加数矢量扩为5位,为进位提供空间BB<='0'& B;--将4位被加数矢量扩为5位,为进位提供空间SINT<=AA+BB+CIN ;S<=SINT(3 DOWNTO 0);CONT<=SINT(4);END ART;8位二进制加法器的源程序ADDER8B.VHDLIBRARY IEEE;USE IEEE_STD.LOGIC_1164.ALL;USE IEEE_STD.LOGIC_UNSIGNED.ALL:ENTITY ADDER8B IS--由4位二进制并行加法器级联而成的8位二进制加法器PORT(CIN:IN STD_LOGIC;A:IN STD_LOGIC_VECTOR(7 DOWNTO 0);B:IN STD_LOGIC_VECTOR(7 DOWNTO 0);S:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);COUT:OUT STD_LOGIC);END ADDER8B;ARCHICTURE ART OF ADDER8B ISCOMPONENET ADDER4B--对要调用的元件ADDER4B的界面端口进行定义PORT(CIN:IN STD_LOGIC;A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);B:IN STD_LOGIC_VECTOR(3 DOWNTO 0);S:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CONT:OUT STD_LOGIC);END COMPONENT ;SIGNAL CARRY_OUT:STD_LOGIC;--4位加法器的进位标志BEGINU1:ADDER4B --例化(安装)一个4位二进制加法器U1PORT MAP(CIN=>CIN,A=>A(3 DOWNTO 0),B=>B(3DOWNTO0),S=>S(3 DOWNTO 0),COUT=>CARRY_OUT);U2:ADDER4B --例化(安装)一个4位二进制加法器U2PORT MAP(CIN=>CARRY_OUT,A=>A(7 DOWNTO 4),B=>B(7 DOWNTO 4),S=>S (7 DOWNTO 4);CONT=>CONT);END ART;六进制计数器的源程序CNT6.VHD(十进制计数器的源程序CNT10.VHD与此类似)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT6 ISPORT (CLK:IN STD_LOGIC;CLR:IN STD_LOGIC;ENA:IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CARRY_OUT:OUT STD_LOGIC );END CNT6;ARCHITECTURE ART OF CNT6 ISSIGNAL CQI:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,CLR,ENA)BEGINIF CLR='1' THEN CQI<="0000";ELSIF CLK'EVENT AND CLK='1' THENIF ENA='1' THENIF CQI=“0101” THEN CQI<=“0000”;ELSE CQI<=CQI+'1';END IF;END IF;END IF;END PROCESS;PROCESS(CQI)BEGINIF CQI=“0000” THEN CARRY_OUT<='1';ELSE CARRY_OUT<='0';END IF;END PROCESS;CQ<=CQI;END ART;十进制计数器LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_unsigned.ALL;ENTITY count10 ISPORT(clk: IN STD_LOGIC;seg: OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END count10;ARCHITECTURE a1 OF count10 ISsignal sec: STD_LOGIC; signal q : STD_LOGIC_VECTOR(21 DOWNTO 0);signal num: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINprocess(clk) ----get 1 hz clock pulsebeginif clk'event and clk='1' then q<=q+1; end if;sec<=q(21); --get 1 hz clock pulseend process;timing: process(sec) beginif sec'event and sec='1' thenif num<9 then num<=num+1; else num<="0000"; end if;end if;end process;B1: block --bcd-7segsBegin --gfedcbaseg<= "0111111" when num=0 else"0000110" when num=1 else"1011011" when num=2 else"1001111" when num=3 else"1100110" when num=4 else"1101101" when num=5 else"1111101" when num=6 else"0000111" when num=7 else"1111111" when num=8 else"1101111" when num=9 else"0000000";end block;END a1;四位全加器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity add isport(a,b:in std_logic_vector(3 downto 0);cin:in std_logic;s:out std_logic_vector(3 downto 0);cout:out std_logic);end add;architecture beh of add isbeginprocess(a,b,cin)ariable x:std_logic_vector(3 downto 0);variable m,n,l:integer;beginm:=conv_integer(a);n:=conv_integer(b);l:=m+n+conv_integer(cin);x:=conv_std_logic_vector(l,4);s<=x(3 downto 0);cout<=x(3);end process;end beh;10位计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT ( CLK ,clr : IN STD_LOGIC ;CQ : OUT STD_LOGIC_VECTOR ( 3 DOWNTO 0 ));END ENTITY CNT10;ARCHITECTURE ONE OF CNT10 ISBEGINPROCESS ( CLK , clr )V ARIABLE LCQ : STD_LOGIC_VECTOR ( 3 DOWNTO 0 ); BEGINIF RST = …1‟ THEN LCQ := “0000”;ELSIF CLK‟EVENT AND CLK = …1‟ THENIF LCQ < 9 THEN LCQ := LCQ + 1;ELSE LCQ := “0000” ;END IF; END IF;CQ <= LCQ ;END PROCESS;END ARCHITECTURE ONE;八位串行二进制全加器use ieee.std_logic_1164.all;entity product_adder_subtracter isport(a,b:in std_logic_vector(7 downto 0);s:out std_logic_vector(8 downto 0));end;architecture behavioral of product_adder_subtracter isbeginbehavior:process(a,b) isvariable carry_in:std_logic;variable carry_out:std_logic;variable op2:std_logic_vector(b'range);beginop2:=b;end if;for index in 0 to 7 loopcarry_in:=carry_out;s(index)<=a(index) xor op2(index)xor carry_in ;carry_out:=(a(index)and op2(index))or(carry_in and (a(index) xor op2(index)));end loop;s(8)<=a(7) xor op2(7) xor carry_out;end process;end;8、根据已给出全加器VHDL程序,试写出一个四位逐位进位加法器的VHDL源程序。