超大规模集成电路设计

超大规模集成电路设计 集成电路制作工艺:CMOS工艺

通过改进制程技术和优化工艺参数,降低芯片静 态功耗,提高能效比。

新型CMOS工艺的研究与开发

新型材料的应用

异构集成技术

研究新型半导体材料,如碳纳米管、 二维材料等,以实现更高的性能和更 低的功耗。

研究将不同类型的器件集成在同一芯 片上的技术,以提高芯片的功能多样 性和集成度。

新型制程技术

探索新型制程技术,如自对准技术、 无源元件集成技术等,以提高芯片集 成度和降低制造成本。

高可靠性

CMOS电路的开关速度较 慢,减少了电路中的瞬态 电流和电压尖峰,提高了 电路的可靠性。

集成度高

CMOS工艺可以实现高密 度的集成电路,使得芯片 上可以集成更多的器件和 功能。

稳定性好

CMOS工艺的输出电压与 输入电压的关系较为稳定, 具有较好的线性度。

CMOS工艺的应用领域

计算机处理器

CMOS工艺广泛应用于计 算机处理器的制造,如中 央处理器(CPU)和图形 处理器(GPU)。

可靠性挑战

随着集成电路集成度的提高,CMOS工艺面临着 可靠性方面的挑战,如热稳定性、电气性能、可 靠性等。

解决方案

采用先进的材料和制程技术,如高k介质材料、金 属栅极材料、应力引入技术等,以提高集成电路 的可靠性和稳定性。

环境问题与解决方案

环境问题

CMOS工艺中使用的化学物质和制程过程中产生的废弃物对环境造成了影响。

同性的刻蚀。

反应离子刻蚀(RIE)

02

结合等离子体和化学反应,实现各向异性刻蚀,特别适合于微

细线条的加工。

深反应离子刻蚀(DRIE)

03

一种更先进的刻蚀技术,能够实现深孔和槽的加工,广泛应用

于三维集成电路制造。

《超大规模集成电路设计》考试习题(含答案)完整版分析

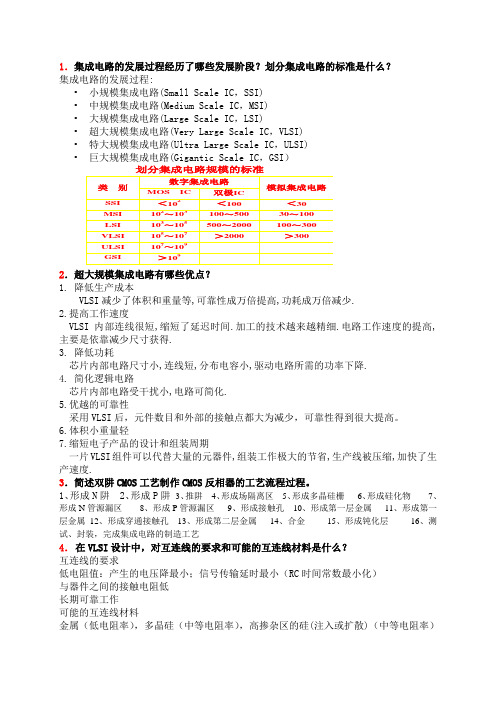

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

超大规模集成电路CAD 第一章 VLSI设计的概述教材

差))

1952 年,英国皇家雷达研究所的达默第一次提出“集成电 路”的设想; 1958年美国德克萨斯仪器公司基尔比为首的小组研制出世 界上第一块集成电路了双极性晶体管(由12个器件组成的 相移振荡和触发器集成电路),并于1959年公布—这就是 世界上最早的集成电路,是现代集成电路的雏形或先驱 ; (基尔比于2000年获得诺贝尔物理学奖) 1960年成功制造出MOS管集成电路; 1965年戈登· 摩尔发表预测未来集成电路发展趋势的文章, 就是“摩尔定律”的前身; 1968年Intel公司诞生。

2019/4/12 4

第1章 VLSI概述

集成电路的发展除了物理原理外还得益于许多新工艺的 发明:

50年美国人奥尔和肖克莱发明的离子注入工艺; 56年美国人富勒发明的扩散工艺; 60年卢尔和克里斯坦森发明的外延生长工艺; 60年kang和Atalla研制出第一个硅MOS管; 70年斯皮勒和卡斯特兰尼发明的光刻工艺,使晶体管从点接触 结构向平面结构过渡并给集成电路工艺提供了基本的技术支持。 因此,从70年代开始,第一代集成电路才开始发展并迅速成熟。

图1 – 1 “点接晶体管放大器” 2019/4/12 3

路 漫 漫 其 修 远 兮 吾 将 上 下 而 求 索

第1章 VLSI概述

1948年,威廉· 肖克莱(William Shockley)—“晶体管之 父” ,提出结型晶体管的想法; 1951年,威廉· 肖克莱领导的研究小组成功研制出第一个可 靠的单晶锗NPN结型晶体管;(温度特性差、提纯度差、表面防护能力差(稳定性

路 漫 漫 其 修 远 兮 吾 将 上 下 而 求 索

数字超大规模集成电路设计

数字超大规模集成电路设计数字超大规模集成电路设计数字超大规模集成电路(VLSI)是一种特殊类型的集成电路,由数百万个晶体管构成,可用于各种应用,例如计算机处理器、数字信号处理器、存储器和网络芯片。

设计数字超大规模集成电路需要专业的知识和技术,严格的设计过程和流程可以确保电路的性能和可靠性达到最佳水平。

数字超大规模集成电路设计的主要步骤包括电路规划、逻辑设计、物理设计和验证等四个阶段。

下面将对这四个过程分别详细介绍。

1. 电路规划电路规划是设计数字超大规模集成电路的第一步,它需要确定电路的总体结构和功能。

在这个阶段,设计师需要与客户或团队成员讨论需求和预期的目标,以确定应满足的功能和性能要求。

电路规划需要在不同的层次上考虑电路的结构,例如芯片层、宏单元层、模块层和单元层,以确保整个电路都经过了全面的思考和验证。

2. 逻辑设计在电路规划阶段完成后,设计师需要开始进行逻辑设计,这是将电路的功能和结构转化为数字逻辑块的过程。

设计师可以使用各种电子设计自动化(EDA)工具来实现逻辑设计,通常使用硬件描述语言(HDL)来表示电路的行为和结构。

逻辑设计包括几个不同的步骤,例如:逻辑合成:将高层次的行为描述转化为门级或寄存器传输级别的等效电路。

时序分析:确保电路满足时序约束和时钟周期。

优化布局和布线:通过逻辑综合和布局布线工具优化电路,以实现更好的性能和功耗。

3. 物理设计物理设计阶段是将逻辑电路实现为实际电路的过程,包括立即设计、布局规划、布线、物理验证等。

立即设计:确定电路各个模块的精确位置,以及电路的层次和结构。

布局规划:根据立即设计结果生成电路的初始布局方案,包括放置模块、布线规划以及时钟树设计等。

布线:将布局好的模块进行线路连接,生成物理电路,并进行布线优化、电容和电感提取,确定线路的延迟等等。

物理验证:设计师对所生成的物理电路进行验证,包括逻辑验证、时序验证、数据库校验等,以确保电路的功能与预期相符,而且其性能达到标准。

《超大规模集成电路物理设计:从图分割到时序收敛》随笔

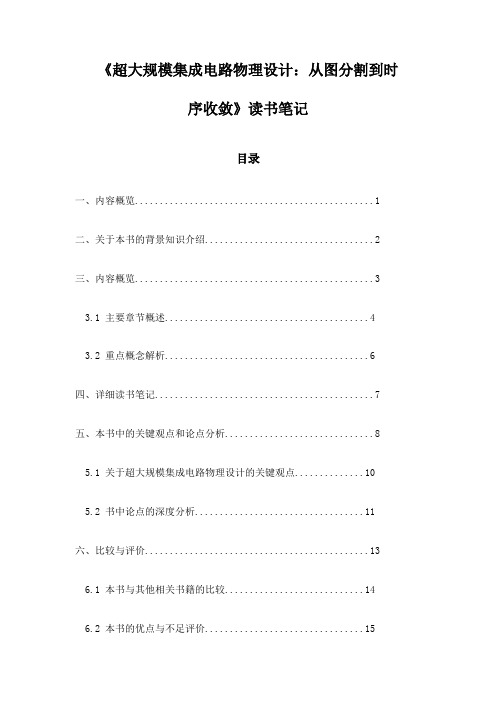

《超大规模集成电路物理设计:从图分割到时序收敛》读书笔记目录一、内容概览 (1)二、关于本书的背景知识介绍 (2)三、内容概览 (3)3.1 主要章节概述 (4)3.2 重点概念解析 (6)四、详细读书笔记 (7)五、本书中的关键观点和论点分析 (8)5.1 关于超大规模集成电路物理设计的关键观点 (10)5.2 书中论点的深度分析 (11)六、比较与评价 (13)6.1 本书与其他相关书籍的比较 (14)6.2 本书的优点与不足评价 (15)七、实践应用与案例分析 (16)7.1 书中理论在实际设计中的应用 (18)7.2 案例分析 (19)八、总结与心得体会 (21)8.1 本书的主要收获和启示 (22)8.2 个人对超大规模集成电路物理设计的未来展望 (23)一、内容概览《超大规模集成电路物理设计:从图分割到时序收敛》是一本深入探讨超大规模集成电路(VLSI)物理设计过程的著作。

本书从图分割的基本原理出发,详细阐述了集成电路设计的各个阶段,包括布局、布线、时序分析和验证等。

在图分割部分,本书介绍了如何将复杂的集成电路设计问题简化为更易于处理的子问题。

通过图论和计算机辅助设计(CAD)技术,作者提出了一系列高效的图分割算法,从而为后续的物理设计过程奠定了坚实的基础。

在布局阶段,本书重点讨论了如何根据电路结构和约束条件选择合适的布局算法。

作者详细分析了不同布局策略的优缺点,并提出了针对复杂电路的优化方法。

布线是集成电路设计中的关键步骤之一,本书介绍了多种布线算法,包括基于启发式的布线方法、基于物理约束的布线方法和基于人工智能技术的布线方法等。

作者还探讨了布线过程中的优化问题和挑战。

时序分析是确保集成电路正常工作的关键环节,本书详细阐述了时序分析的基本原理和方法,包括静态时序分析、动态时序分析和时序收敛等。

作者通过理论分析和实例验证,介绍了如何有效地进行时序分析和优化,以确保设计的集成电路具有良好的时序性能。

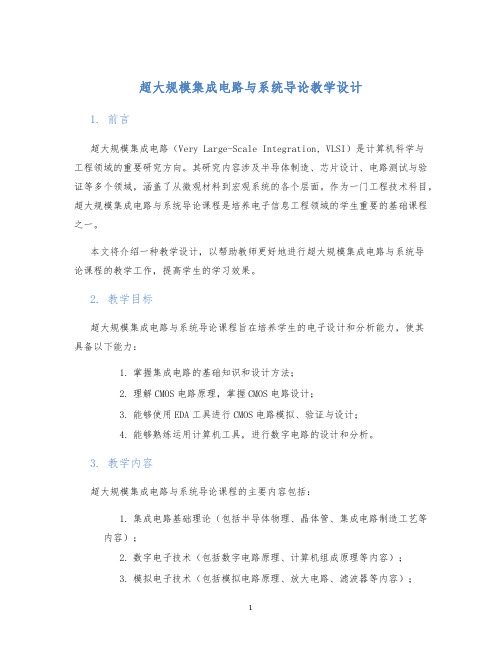

超大规模集成电路与系统导论教学设计

超大规模集成电路与系统导论教学设计

1. 前言

超大规模集成电路(Very Large-Scale Integration, VLSI)是计算机科学与

工程领域的重要研究方向。

其研究内容涉及半导体制造、芯片设计、电路测试与验证等多个领域,涵盖了从微观材料到宏观系统的各个层面。

作为一门工程技术科目,超大规模集成电路与系统导论课程是培养电子信息工程领域的学生重要的基础课程之一。

本文将介绍一种教学设计,以帮助教师更好地进行超大规模集成电路与系统导

论课程的教学工作,提高学生的学习效果。

2. 教学目标

超大规模集成电路与系统导论课程旨在培养学生的电子设计和分析能力,使其

具备以下能力:

1.掌握集成电路的基础知识和设计方法;

2.理解CMOS电路原理,掌握CMOS电路设计;

3.能够使用EDA工具进行CMOS电路模拟、验证与设计;

4.能够熟练运用计算机工具,进行数字电路的设计和分析。

3. 教学内容

超大规模集成电路与系统导论课程的主要内容包括:

1.集成电路基础理论(包括半导体物理、晶体管、集成电路制造工艺等

内容);

2.数字电子技术(包括数字电路原理、计算机组成原理等内容);

3.模拟电子技术(包括模拟电路原理、放大电路、滤波器等内容);

1。

超大规模集成电路设计 作业 问题解答

Lcrit 2 =

t pgate1 0.38rc

=

20 ×10−9 = 8cm 0.38 × 0.075 ×110 × 10−18

tpw=0.38rcL2=0.38x0.075x110x(0.1x106μm)2=31.4ns tp= tpw + tpgate2=31.4+20=51.4ns

7. Q:a) 用互补 CMOS 门实现逻辑功能为 Out = AB + AC + BC 的电路; b) 用由 NMOS 构成下拉网络的多米诺门实现逻辑功能为 Out = AB + AC + BC 的电 路; c) 写出下面 CMOS 电路的逻辑函数功能。

A: VSB 2 = VS 2 − VB 2 = 2 − 0 = 2 V ,

VT = VT 0 + γ

(

−2φF + VSB −

−2φF ,

)

VT 2 = 0.6 + 0.4

(

0.6 + 2 − 0.6 = 0.94 V ,

)

VDS 2 = VGS 2 > VGS 2 − VT 2 ,所以 M2 可能处于夹断饱和工作区,还有可能发生速度饱和,因

PPຫໍສະໝຸດ A:a)b) Out = AB + AC + BC = AB ⋅ AC ⋅ BC = ( A + B ) ⋅ ( A + C ) ⋅ ( B + C )

= ( A + AC + AB + BC ) ⋅ ( B + C ) = ( A + BC ) ⋅ ( B + C )

C

A

B

C

B

c) Out = C i P + Ai B i P 8. Q:在下图中 x 点电容 Cx=50fF,PMOS 管 Mr 的尺寸是 W/L=0.5/0.5,Mn 的尺寸是 W/L=0.5/0.25,如果静态 CMOS 反相器的阈值电压为 VM=VDD/2,VDD=2.5V

超大规模集成电路

目录摘要 (1)关键词 (1)Abstract (1)Key words (1)1 引言 (1)2 超大规模集成电路的设计要求 (1)3 超大规模集成电路的设计策略 (2)3.1层次性 (2)3.2模块化 (2)3.3规则化 (2)3.4局部化 (2)4 超大规模集成电路的设计方法 (3)4.1 全定制设计方法 (3)4.2 半定制设计方法 (4)4.3 不同设计方法的比较 (5)5 超大规模集成电路的设计步骤 (6)5.1 系统设计 (7)5.2 功能设计 (7)5.3 逻辑设计 (7)5.4 电路设计 (7)5.5 版图设计 (7)5.6 设计验证 (8)5.7 制造 (8)5.8 封装和测试 (8)6 超大规模集成电路的设计流程 (8)6.1 总体的设计流程 (8)6.1.1高层次综合 (8)6.1.2逻辑综合 (8)6.1.3 物理综合 (9)6.2 详细的设计流程 (9)7 超大规模集成电路的验证方法 (9)7.1 动态验证 (9)7.2 静态验证 (9)7.3 物理验证 (9)8 总结 (9)致谢 (10)参考文献 (10)超大规模集成电路网络工程专业学生孙守勇指导教师吴俊华摘要:随着集成电路的高速发展,集成电路的设计显得越来越重要,目前设计能力滞后于制造工艺已成为世界集成电路产业的发展现状之一。

为了明确超大规模集成电路设计的理想方法,首先对超大规模集成电路的设计要求进行了调查,然后对超大规模集成电路的设计策略进行了研究,探讨了超大规模集成电路的不同设计方法,并对不同的设计方法做出了比较,明确了超大规模集成电路的设计步骤及设计流程,最后探讨了超大规模集成电路的验证方法。

关键词:集成电路设计方法步骤Very Large Scale IntegrationStudent Majoring in Network Engineering Sun ShouyongTutor Wu JunhuaAbstract:With the high speed development of integrated circuit, the design of integrated circuit is becoming more and more important. At present, the design capacity behind manufacture technology has become one of the world's integrated circuit industry development current situation. In order to specify the ideal method of VLSI design, first of all, the requirements of VLSI was investigated, then, the design strategy of VLSI is studied. Discuss different methods of VLSI, and made a comparison of different methods. Clear and definite the design steps of very large scale integrated circuit and the design process, finally, discuss the validation method of very large scale integrated circuit.Key words:integrated circuit; design; method; step1引言自从1959年集成电路诞生以来,经历了小规模(SSI)、中规模(MSI)、大规模(LSI)的发展历程,目前已进入超大个规模(VLSI)和甚大规模集成电路(ULSI)阶段,集成电路技术的发展已日臻完善,集成电路芯片的应用也渗透到国民经济的各个部门和科学技术的各个领域之中,对当代经济发展和科技进步起到了不可估计的推动作用。

VLSI设计课程

课程安排

1. 2. 3. 4. 5. 6. 电路仿真(一部分) : 20学时 VHDL设计(二部分): 25学时 VSLI系统设计(三部分): 10学时 HDL设计综合(三部分): 5学时 VSLI自动布局布线(三部分): 10学时 VSLI物理验证(三部分): 10时 共80学时

学习VLSI设计工具

1. 电路仿真工具Cadence -spectre 2. VHDL编译及仿真工具ALTER- MaxPlusII

3. 应用软件设计工具-Keil51 4. 数字系统功能验工具-Mento Modelsim

5. 设计综合工具-Synopsys dc(Design Compiler) 6. 自动布局布线工具- Cadence SE(Silicon Ensemble) 7. VLSI物理验证工具Cadence Dracula

4.

5.

6.

SOC的芯片实现 -基于M210core的例子

《VLSI设计》教材

1. 主要教材:

《超大规模集成电路设计技术》三册 电路模拟spectre仿真; 《超大规模集成电路设计技术》四册 VSLI设计系列;

2. 建议参考书:

《IC设计基础》任艳颖等 西安电子科技出版社2009; 《现代VLSI电路设计》 Wayn.e 科学出版社2012; 《数学集成电路设计》 Ven.Martin 电子工业2012; 《电子系统-集成电路设计技术》李玉山等 电子工2012;

《超大规模集成电路 (VLSI)设计》

《VLSI设计》课程简介

1. 2. 3. 课程主要讲授数字超大规模集成电路(VSLI)设计的概念 及方法。 课程以一个0.18微米工艺30万门规模的数字系统芯片设计 项目为实例. 学习电路仿真; VHDL设计; VSLI系统软硬件协同设计; 设计 综合; 时序分析;VSLI自动布局布线; VSLI物理验证;全芯 片后仿真。 学习spectre电路模拟工具、数字电路仿真工具Modelsim、 DC设计综合工具及SE自动布局布线工具的使用。 课程采取课堂教学和实验相结合的方式,含盖超大规模集 成电路(VSLI)设计全流程.。 通过学习和实验,要求完成30万门的数/字系统芯片项目设 计,从而具备VSLI芯片设计基本能力。

超大规模集成电路技术的研究与应用

超大规模集成电路技术的研究与应用随着电子信息技术的快速发展,超大规模集成电路(VLSI)技术作为微电子学中的一支重要力量,其研究与应用逐渐得到广泛关注。

本文将对超大规模集成电路技术的研究与应用进行探讨。

一、超大规模集成电路技术的概念超大规模集成电路是将大量的晶体管、电容、电感、电阻等元器件以微米级别的线路集成在一起,组成复杂功能电路的技术。

这种技术不仅解决了元器件数量的增加所导致的电路局部布线和对外部接口不断增加的问题,而且还大幅度提高了电路的速度和可靠性,使得电子设备体积更小,功耗更低。

二、超大规模集成电路技术的研究方向在超大规模集成电路技术的研究方向上,主要包括以下几个方面:1. 芯片设计技术芯片设计技术是研究超大规模集成电路设计方法和技术的一门学科。

在芯片设计技术的研究中,需要考虑在不同应用领域需求下,如何设计出满足高性能、低功耗要求的芯片。

为此,需要研究各种设计算法,同时掌握复杂设计工具的使用,如EDA工具、EDA流、设计仿真等。

2. 工艺技术超大规模集成电路工艺技术是构建芯片物理结构的一项技术领域。

在此技术研究中,主要需要解决的是在工艺过程中的误差和不确定性问题。

需要掌握先进的微纳米加工技术,如氧化、光刻、电镀、蒸发、离子注入等。

同时,还需对各种特殊材料的特性了解,以满足各种设计要求。

3. 测试技术在超大规模集成电路测试过程中,需要进行真实性、可测性和可靠性的测试。

目的是验证芯片的性能、正确性和可靠性,并且提取出失效的部件以确认故障的原因。

该技术领域对于超大规模集成电路技术的发展和应用至关重要。

三、超大规模集成电路技术的应用领域超大规模集成电路技术在信息产业、通信、计算机、车载电子、医疗、航空航天、民用电器、军事等领域都具有广泛的应用。

在通信领域,超大规模集成电路技术被广泛应用于移动通信、卫星通信、数据通信等方面。

在医疗领域,超大规模集成电路技术被应用于医疗设备控制、成像等方面。

在智能制造领域,超大规模集成电路技术的应用也日益增长。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2020年4月22日星期三

课艺、器件/连线 – 逻辑门单元电路、组合/时序逻辑电路 – 功能块/子系统(控制逻辑、数据通道、存储器、总线)

• Part 2 超大规模集成电路设计方法

– 设计流程 – 系统设计与验证 – RTL设计与仿真 – 逻辑综合与时序分析 – 可测试性设计 – 版图设计与验证 – SoC设计概述

Die

Package

封装(3)

封装方式

– DIP双列直插式 – PLCC塑料有引线芯片

载体 – QFP塑料方型扁平式 – PGA插针网格阵列 – BGA球栅阵列 – MCM、SIP的多芯片

封装方式

我国知名的封装厂

– 长电 – 南通富士通

DIP

PLCC

QFP

LQFP

TQFP

PGA

BGA

测试(1)

• 中测(晶圆测试、 Wafer Testing、CP测试):晶圆制造完成后 的测试

制造(2)

• 制造工艺的发展趋势 – 特征尺寸越来越小:1, 0.8, 0.6, 0.5, 0.35, 0.25, 0.18, 0.15,0.13 微米; 90, 65, 40, 28,20纳米 – 晶圆直径越来越大:4, 5, 6, 8, 12 英寸 – 率先用于数字IC,特别是DRAM和Flash等存储器电路 – 结果:规模越来越大,性能越来越高,单片制造成本相对越来越 低

晶圆(管芯)

芯片

设计结果:芯片版图(Layout)

• An Example

Chip Layout of Intel Pentium Pro - 5.5 million FETs

掩模版(光罩版、Mask)

版图 Layout

晶圆制造

掩模版

封装

晶圆制造

从空白晶圆(Wafer)到图案化的晶圆

版图 →管芯

Pentium III

PentiumPro

当前:超大规模集成电路(VLSI)时代

为什么采用VLSI:人们对电子系统的需要

★ 功能要求越来越复杂:电路规模 ★ 性能要求越来越优良:速度、功耗 ★ 成本相对来讲最好低一点:尺寸

由于集成电路在电子系统中的核心作用,集成电路在系统功能 、性能和成本中所起的作用是关键性的

课程参考书

(仅适用于Part 1)

中文版

《现代VLSI设计——系统芯片设计》(原书第三版)

[美]韦恩•沃尔夫 著

科学出版社

该书的前半部分

(Chap1-6)

英文版

Modern VLSI Design: System-on-Chip Design, 3th

by Wayne Wolf

绪论

1. IC:从设计、制造、封装、测试到芯片产品

2. IC设计:设计流程及其EDA工具

集成电路(IC)的发明

• 1952年5月,英国科学家G. W. A. Dummer提出了集成电路的设想。 • 1958年TI公司Clair Kilby的研究小组发明了第一块集成电路,12个元件,锗半导体

获2000年Nobel物理奖

第一块微处理器芯片

Intel公司, 1971年 4004中央处理 器(CPU)

IC的大致分类 (1)

IC

数字IC

FPGA/CPLD

SOC

射频/模拟IC 混合信号IC

数字ASIC(掩膜

混合 ASIC

)

基于门阵列

基于标准单元

基于全定制

集成电路的发展:摩尔定律

• 由Gordon Moore提出(Gordon Moore是Intel的创立者之一) • Moore’s Law:每个芯片上的晶体管数目,以指数形式增加,每18个月翻一番

摩尔定律:微处理器的发展

8080

8086

80286

80386

80486

Pentium

Itanium

Pentium IV

Layout→Die

制造(1)

• 芯片制造的大致步骤

– 掩模版(光罩版、Mask)制作 • 对每层版图都要制作一层掩模版,实际是光刻工序的次数 • 除金属层外,一般CMOS电路至少需要20层以上掩模版

– 晶圆制造(光刻)(Wafer Manufacturing)

• 制造工艺的种类

– Bipolar – MOS(NMOS、PMOS) – CMOS(当前主流工艺) – BiCMOS – 其它特殊工艺

测试(2)

• 成测(成品测试、Final Testing 、FT):芯片封装完成后的测 试,需对每个芯片进行测试 – 测试在制造、封装过程中形成的故障 – 是必须经过的过程,但对经过中测的芯片可以相对简单 – 自动测试仪ATE + 芯片自动分拣机(或称机械手)Handler

测试(3)

世界知名的测试仪器和设备

集成电路的三个关键特性(功能要求定下来的前提下)

★ 尺寸 ★ 速度 ★ 功耗

集成电路:从 Spec. 到芯片产品

设计 制造 封装测试

体现出了集成电路产业链: 设计业、制造业、封测业

集成电路:从 Spec. 到芯片产品

设计 制造 封装测试

设计结果

掩模版(光罩 版、Mask)

晶圆测试 (中测)

成品测试 (成测)

• 世界知名的制造厂(Foundry)

– 代工厂 TSMC、UMC、Charter、SMIC

– IDM Intel、Samsung、TI、ST

封装测试

掩模版

封装

封装(1)

先进行晶圆切割 (Sawing Wafer)

封装(2)

– 封装( Packaging )可以满足芯片的以下几个需要

– 给予芯片机械支撑 – 协助芯片向周围环境散热 – 保护芯片免受化学腐蚀 – 封装引脚可以提供芯片在整机中的有效焊接

– 测试在制造过程中形成的故障 – 不能测试在封装过程中形成的故障(因为此时还没有封装),所以中

测以后必须进行成测 – 可以在封装前测试出故障芯片,避免这部分故障芯片的封装费用,适

用于封装费用比较昂贵的芯片。所以,封装费用低廉的芯片可以不经 过中测 – 自动测试仪ATE(Teaster) +自动探针台ProbeStation

• Advantest(爱德万) • Teradyne(泰瑞达) • Credence(科利登) • Verigy(原Agilent 安捷伦半导体测试部门)

绪论

1. IC:从设计、制造、封装、测试到芯片产品

2. IC设计:设计流程及其EDA工具

1)数字IC设计流程 2)模拟IC设计流程 3)设计对制造和封测的影响