P型扩散电阻版图规则

p型电池发射极方块电阻单位

p型电池发射极方块电阻单位“半导体基础知识”篇之后,再次回归基础知识的学习记录。

蒸发铝膜、导电漆膜、印制电路板铝箔膜等薄膜状导电材料,衡量它们厚度的最好方法就是测试它们的方阻。

本篇学习记录主要涉及方阻的概念、意义、测量方法等。

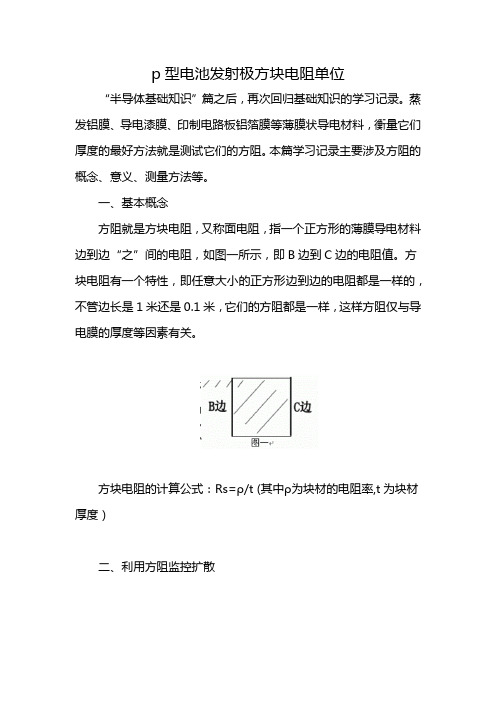

一、基本概念方阻就是方块电阻,又称面电阻,指一个正方形的薄膜导电材料边到边“之”间的电阻,如图一所示,即B边到C边的电阻值。

方块电阻有一个特性,即任意大小的正方形边到边的电阻都是一样的,不管边长是1米还是0.1米,它们的方阻都是一样,这样方阻仅与导电膜的厚度等因素有关。

方块电阻的计算公式:Rs=ρ/t (其中ρ为块材的电阻率,t为块材厚度)二、利用方阻监控扩散方块电阻是一个二级概念,真正的核心是扩散深度。

一般扩散深度会影响电性能参数,因为扩散深度无法测量,所以只能通过测电阻来大概反映扩散深度和扩散浓度。

他是一个深度和浓度,以及体材料多重作用的结果,至于其和电性能参数各值之间的线性关系,目前没有什么特定方程式,都是通过经验来控制在一定的方位,做到30-50的都有。

方阻一般只是在扩散后进行监控,监控方阻就是为了监控扩散的稳定性。

测试方阻跟最后的烧结工序的影响也是很重要的,因为结的深度也会影响你最后烧结的深度,否则有可能出现Rs的异常。

所以方阻也是烧结条件的重要指标。

一般结深则电阻小,掺杂浓度高。

电阻小了,掺杂量就高了,表面死层就会多,这样会牺牲很多电流;电阻大了,电流的收集就会比较困难;方阻要做高,是需要其他相关条件保障的,假如其他条件不满足,效率反而会降低。

一般扩散温度越高,时间越长,流量越大,方阻就越小,结就越深。

除了扩散之外,生产中的其它工序对方阻也会产生影响。

一般如果是稳定生产,方阻也是稳定的。

后道生产中,假如出现大量问题片,看症状跟方阻有可能相关的,就可以去反查工序中是否出现了问题,即使电池也是可以测试的。

但是这个只能相对参考,一般公司都会规定方阻多少到多少之间的片子可以进入流程,另外的就要返工,但是因为是抽检,谁又能保障进入流程的都是好的呢,甚至员工有可能会偷懒,好的片子坏的片子都流入流程。

扩散工艺及控制要点

扩散工艺及控制要点1.由于硅太阳能电池实际生产中均采用P型硅片,因此需要形成N型层才能得到PN结,这通常是通过在高温条件下利用磷源扩散来实现的。

这种扩散工艺包括两个过程:首先是硅片表面含磷薄膜层的沉积,然后是在含磷薄膜中的磷在高温条件下往P型硅里的扩散。

2.在高温扩散炉里,汽相的POCL3(phosphorus oxychloride)或PB r3(phosphorus tribromide)首先在表面形成P2O5(phosphorus pentoxide);然后,其中的磷在高温作用下往硅片里扩散。

3.扩散过程结束后,通常利用“四探针法”对其方块电阻进行测量以确定扩散到硅片里的磷的总量,对于丝网印刷太阳电池来说,方块电阻一般控制在40-50欧姆。

4.发射结扩散通常被认为是太阳电池制作的关键的工艺步骤。

扩散太浓,会导致短路电流降低(特别是短波长光谱效应很差,当扩散过深时,该效应还会加剧);扩散不足,会导致横向传输电阻过大,同样还会引起金属化时硅材料与丝网印刷电结之间的欧姆接触效果。

5.导致少数载流子寿命低的原因还包括扩散源的纯度、扩散炉的清洁程度、进炉之前硅片的清洁程度甚至是在热扩散过程中硅片的应力等。

6.扩散结的质量同样依赖于扩散工艺参数,如扩散的最高温度、处于最高温度的时间、升降温的快慢(直接影响硅片上的温度梯度所导致的应力和缺陷)。

当然,大量的研究表明,对于具有600mv左右开路电压的丝网印刷太阳电池,这种应力不会造成负面影响,实际上有利于多晶情况时的吸杂过程。

7.发射结扩散的质量对太阳能电池电学性能的影响反映在串联电阻从而在填充因子上:(1)光生载流子在扩散形成的N-型发射区是多数载流子,在这些电子被金属电极收集之前需要经过横向传输,传输过程中的损失依赖于N-型发射区的横向电阻;(2)正面丝网印刷金属电极与N-型发射区的电接触,为了避免形成SCHOTTKY势垒或其它接触电阻效应而得到良好的欧姆接触,要求N-型发射区的搀杂浓度要高。

新手学版图--几种电阻的画法

新手学版图--几种电阻的画法刚好Module 部门要画testkey 测试新制程对器件的影响,其中就有一部分是画不同类型的电阻。

这些电阻有:poly电阻,nwell电阻,pplus电阻,nplus电阻。

上图即为这几种电阻的画法,除poly电阻外,其他三种电阻的画法是值得推敲的。

电阻三端分别定义为force,sense和sub。

我们来分析这三种电阻。

nwell 电阻:问题1为什么force,sense端要加thinoxide和nplus?问题2:为什么要用nplus而不用pplus?Pplus电阻:问题1:为什么要画在nwell 中?问题2:为什么sub要接高电位?问题3:为什么电阻中间要用thinoxide 连接?Nplus电阻:问题1:可不可以画在nwell 中?其实以上问题的重点1是要理解thinoxide 的作用,以及nwell,p+/N+plus 在制造过程中所处的步骤。

thinoxide 可以理解为去除FOX。

nwell 在制造的前端就形成了,FOX不会对此造成影响。

而P+/N+plus会受FOX的影响,如果FOX阻挡的话,wafer上就不会形成相应的P型或N型。

重点2即是否会出现不正确的导通。

回答完这些问题之后,我们可以联想到加guardring 时的一些情况。

就p-sub/nwellCMOS 版图而言,少数载流子guardring 为nwell+nplus+thinoxide+VDD, 多数载流子guardri ng 为pplus+thi no xide+VSS 讨论当两种guardri ngth in oxide 不连续时的不同影响。

显然在thinoxide断开的地方FOX阻挡了n+/p+的形成,对于nwellguardring 在断开的地方形成nwell电阻,但对于以p型为衬底的地方而言这里就完全断开了。

由此可见,在加guardring 的时候应保持thinoxide 连续性。

《传感器技术》作业(2)

《传感器技术》作业(2)一、填空题1、沿应变片轴向的应变εx必然引起应变片电阻的相对变化,而垂直于应变片轴向的横应变εy也会引起其电阻的相对变化,这种现象成为横向效应。

这种现象的产生和影响与应变片结构有关。

为了减小由此产生的测量误差,现在一般多采用箔式应变片。

2、为了消除应变片的温度误差,可采用的温度补偿措施包括:单丝自补偿法、双丝自补偿法、桥路补偿法。

3、应变片的线性(灵敏度系数为常数)特性,只有在一定的应变限度范围内才能保持。

当试件输入的真实应变超过某一限值时,应变片的输出特性将出现非线性。

在恒温条件下,使非线性达到10%时的真实应变值,称为应变极限εlim。

它是衡量应变片测量范围和过载能力的指标。

4、应变片绝缘电阻是指已粘贴的应变片的引线与被测试件之间的电阻值。

5、应变片的选择包括:类型的选择、材料的选择、阻值的选择、尺寸的选择。

6、应变式测力传感器弹性元件即为力敏元件,它将被测力的变化转换成应变量的变化。

弹性元件的形式通常有柱式、悬臂梁式、环式等。

7、利用半导体扩散技术,将P型杂质扩散到一片N型底层上,形成一层极薄的电导P型层,装上引线接点后,即形成扩散型半导体应变片。

若在圆形硅膜上扩散出4个P型电阻构成惠斯通电桥的4个桥臂,这样的敏感器件称为固态压阻器件。

8、压阻器件本身受到温度影响后,要产生零点温度漂移和灵敏度温度漂移。

因此,必须采用温度补偿措施。

9、压阻器件的零点温度漂移是由于4个扩散电阻值及它们的温度系数不一致而造成的,一般用串、并联电阻法来补偿。

10、压阻器件的灵敏度温度漂移是由压阻系数随温度变化而引起的。

补偿灵敏度温漂,可以采用在电源回路中串联二极管的方法。

11、利用导电材料的电阻率随本身温度而变化的温度电阻效应制成的传感器,称为热电阻式传感器。

12、电位计传感器也称变阻器式传感器,其工作原理是通过改变电位计触头位置,实现将位移变化转换为电阻的变化。

13、在应用中电容式传感器有三种基本类型,即变极距型或称变间隙(δ)型、变面积(S)型和变介电常数(ε)型。

第5章 电阻版图

折弯型电阻器 注意,拐角处方块数只计算1/2

外角没有电子流过,电阻误差较大

低阻值高精度电阻的原则

如果想要得到一个阻值极低的电阻,而精度要求 很高,可以选择用金属来做。大的面积将有助于 减少delta 的影响,从而保证精度。

4.3、电阻设计的重要依据: 电流密度

➢ 对于选择电阻的宽度,电流密度是重要的。如果需要通过 电阻大量的电流,你会使用一个大的、粗的线。

表示的)

R

b

.

Lb Wb

Lb Wb

2h

.

Lh Wh

Lh Wh

2 W

c

Rc

Wc

2rs

5、实际的最小电阻尺寸:

➢ 制造商可以很好地控制中部区域(体区)的材料,但对外 部的区域,如头区或接触区的控制不太理想。因此应保持 最小体区长度为10um,这将使你的误差下降到百分之一。 如果需要一个相当精确的电阻,则要确保体区长度为10um 或更长,以使δ的影响最小化。 - “确保体区长度至少达到10um,宽度5um。” 则电阻器的最小宽度也应为5um。

宽度、长度变化分别用δW和δL表示。如假设W是 4um,而δW是0.06um,这表明实际的宽度最大是 4.06um ,最小是3.94um ,大小取决于δ表示的是过加 工还是欠加工。

15

➢ “体区误差” 和“头区误差”同样也需考虑。电阻公式改 写为:

R

b

.

Lb Wb

Lb Wb

2h

.

Lh Wh

Lh Wh

不同类型的电阻比较

Poly电阻----集成电路设计中常用的一种电阻,它 是由用制作MOSFET的Poly层来制作的电阻。多 晶硅的方块电阻-----2欧姆左右

扩散电阻----在衬底上做的,衬底是轻掺杂区,电 阻率很高,可作大电阻,但精度不高。阱电阻的 方块电阻值比较大,通常都在几百欧姆以上。

Mos2

五、实际芯片的初步认识

这 里 有 3 副 图 , 分 别 为 芯 片 的 POLY 、 METAL1和METAL2图像(METAL2图像有点 透)。后面还有提取的电路图。

图像上标出了电路图中器件的名称,可以方便 地进行对应。

POLY

METAL1

METAL2

电路图

②CMOS:

P+扩散区 (nMOS是n+)

P-阱

n+扩散区 (nMOS是注入区)

别的,nMOS和CMOS一样。

二、重合的处理: 局部重合:实线与其它,画实线, 虚线与点划线,画点划线 全部重合:加以说明

三、埋孔 埋孔即扩散区和多晶Si的接触孔。有两种。

①先刻好接触孔,然后淀积多晶Si,最后扩散,多 晶Si和扩散区直接接触;

②后刻接触孔,灌AL,把扩散层和多晶Si接起来。

n+

n+

P-Si

四、版图举例

例1:NMOS E/E 铝栅倒相器

9.4.4 MOSIC单元版图设计举例

例2:E/E 硅栅倒相器

例3:E/D 硅栅倒相器

例4:E/D 硅栅倒相器

例5:E/D 硅栅倒相器

例6:E/D 硅栅倒相器

例7:E/D 硅栅倒相器

离子注入 VDD

金属

VOUT

多晶硅

VIN 有源区

0V 接触孔

例8:自举倒相器

例9:E/D或非门

例10:E/D MOS驱动门

VDD

Vo

VSS Vi

例11:

例12:CMOS 倒相器

VIN

VDD VOUT

0V

金属 有源区 多晶硅 接触孔 阱区

例13:CMOS 与非门

VDD

GND

contact poly metal N diffusion P diffusion well

集成电路制造工艺之-扩散课件精选全文完整版

替位式扩散

➢替位式扩散:替位杂质从一个晶格位置扩散到另一个晶格位置。 如果替位杂质的近邻没有空位.则替位杂质要运动到近邻晶格位置

上,就必须通过互相换位才能实现。这种换位会引起周围晶格发生很大 的畸变,需要相当大的能量,因此只有当替位杂质的近邻晶格上出现空 位,替位式扩散才比较容易发生。

对替位杂质来说,在晶格位置上势 能相对最低,而间隙处是势能最高 位置。

间隙式扩散

➢ 间隙式杂质:存在于晶格间隙的杂质。以 间隙形式存在于硅中的杂质,主要是那些 半径较小、不容易和硅原子键合的原子。

➢ 间隙式扩散:间隙式杂质从一个间隙位 置到另一个间隙位置的运动称为间隙式 扩散。

➢ 间隙式杂质在硅晶体中的扩散运动主要 是间隙式扩散。

对间隙杂质来说,间隙位置是势能极 小位置,相邻的两个间隙之间是势能 极大位置。间隙杂质要从一个间隙位 置运动到相邻的间隙位置上,必须要 越过一个势垒,势垒高度Wi一般为0.6 ~ 1.2eV。

②空位式:由于有晶格空位,相邻原子能 移动过来。

③填隙式:在空隙中的原子挤开晶格原子 后占据其位,被挤出的原子再去挤出其他原 子。

④在空隙中的原子在晶体的原子间隙中快 速移动一段距离后,最终或占据空位,或挤 出晶格上原子占据其位。

以上几种形式主要分成两大类:①替位式 扩散。②间隙式扩散。

常见元素在硅中的扩散方式

D0为表观扩散系数,ΔE为激活能。 扩散系数由D0、ΔE及温度T决定。

上节课内容小结

1.决定氧化速率常数的两个因素:

氧化剂分压:B、B/A均与Pg成正比,那么在一定氧化条件下,通过 改变氧化剂分压可改变二氧化硅生长速率。高压氧化、低压氧化 氧化温度: B(DSiO2)、B/A(ks)均与T呈指数关系,激活能不同 2.影响氧化速率的其他因素 硅表面晶向:表面原子密度,(111)比(100)氧化速率快些

CMOS工艺器件结构

最新编辑ppt

nwell resistor 剖面图

8

二、RESISTOR

Others resistor版图和结构

普通poly resistor 版图

最新编辑ppt 扩散电阻版图

9

三、CAPACITANCE

MIM版图和结构

MIM cap 版图

最新编辑ppt

10

三、CAPACITANCE

MOM版图和结构

一、MOSFET

PMOSFET 版图和结构

Pmos 版图

最新编辑ppt

6

Pmos 剖面图

二、RESISTOR

Poly resistor 版图和结 构

Poly resistor 版图

最新编辑ppt

Poly resistor 剖面图

7

二、RESISTOR

nwell resistor 版图和 结构

nwell resistor 版图

最新编辑ppt MOM cap 版图

11

三、CAPACITANCE

VARACTOR版图和结构

VAR cap 版图

最新编辑VpAptR cap 剖面图

12

三、CAPACITANCE

MOS CAP版图和结构

MOS管做电容示意图

最新编辑ppt

13

四、DIODE

PSD/NWELL版图和结构

DIODE 版图

一、MOSFET

NMOSFET 版图和结构

Nmos 版图

最新编辑ppt

3பைடு நூலகம்

Nmos 剖面图

一、MOSFET

NMOS_NA 版图和结构

Nmos _na版图

最新编辑ppt

4

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

This mask defines the areas where all contacts are made to diffusion, poly1 and poly2.

a. Min. & Max. Contact size 0.5x0.5

b. Contact to contact Min. space 0.5

c. Active overlap contact on Active

c.1 P-active overlap contact 0.3

c.2 N-active overlap contact 0.15

d. Poly1 overlap contact on Poly1 0.3

e. Poly2 overlap contact on Poly2 for interconnect 0.3

f. Contact on Active to Poly gate space 0.4

g. No contact on Poly gate in Active area is allowed

h. No contact to field oxide is allowed.

i. Poly1 and Poly2 contact to active area space 0.4

j. Poly1 contact to Poly2 space 1.8

Note: Maximum current density is 1.5 mA/contact

Active Area (TO):

This mask defines the active areas for N and P channel devices and diffused interconnect. Sometimes it is referred as the LOCOS or thin oxide area

a. Active width for interconnect 0.5

b. Active width for Channel width

b.1 For NMOS 0.5

b.2 For PMOS 0.6

c. Spacing of Active (in the same well)

c.1 Spacing between N+ Active to N+ Active 0.8

c.2 Spacing between P+ Active to P+ Active 0.8

c.3 Spacing of N+ Active to P+ Active in Substrate outside N-well 1.0

c.4 Spacing of N+ Active to P+ Active inside N-well 1.0

Notes : (1)Minimum field oxide area 2um2

(2)Minimum active area 1um2

P+ implant area (SP):

This mask defines the areas of P channel device, P+ impurities are implanted into this region to form P channel source and drain.

a. Min. Width of P+ implant 0.8

b. Min. Space of P+ implant (merge if the space is less) 0.8

c. P+ implant enclose Active 0.5

d. P+ implant to unrelated Active space 0.5

e. Min. clearance from SP to poly gate 0.6

f. Min. extension of SP over contact 0.25

g. For Poly1 Line Resistor

g-1. Min extension of SP over poly1 line as P-type poly1 resistor 0.5

g-2. Min clearance from SP to poly1 line as N-type poly1 resistor 0.5

This mask defines the first layer Metal interconnects. Metal1 should be used for local interconnect as much as possible.

a. Metal1 width 0.6

b. Metal1 to Metal1 space

b.1 Metal1 to Metal1 space (width<10um) 0.6

b.2 Metal1 (width≥10um) to any Metal1 1.1

c.1 Metal 1 overlap over contact 0.3

c.2 When metal width equal or larger than 10um 0.8

d. The separation of two corner and a corner from a 45deg. line must satisfy the minimum spacing.

Note: 1. Maximum current density for 1M 1.5mA/um

2. Maximum current density for 2M/3M 0.8mA/um

3. Avoid 90deg. elbow for parallel metal lines. Use 135deg. bend instead.

4. Metal density, if more than 50% , please inform CSMC ; if less than 30% , please add dummy metal and follow CSMC’s another document“ Dummy Metal Rule”.

5. Minimum Isolation metal area 1.1*1.1。