版图设计规则.ppt

合集下载

版图设计实例ppt课件

分割输入器件实现四方交叉:将M3变为M3a和M3b,M4变 为M4a和M4b,就可以实现四方交叉,保证输入器件的对称 性。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

由于全部电流都要通过输入晶体管中的每一个,例如,有时整个电 流完全在M3,当差分信号关断时,M3关断M4接通,整个电流又完全在 M4,信号每摆动一次就切换一次,为了承受这一电流,在M3和M4之间 的金属线需要达到一定的宽度,采用二条金属线连接M3和M4的源极,并 且从M4b和M3b的中间向下,这样,M3导通时电流将通过M3a和M3b, 即它的两半把电流向下送到中心导线。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

4. CMOS放大器

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

1. CMOS门电路

(1) 反相器

电路图

版图1

版图2

版图1特点:多晶栅竖直排列,MOS管源区面积小,因而反相器面积也小。 版图2特点:多晶栅水平排列,MOS管漏极金属与电源、地金属线之间的 空档允许其它金属线通过,因水平尺寸较大而使面积稍大一些。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

2.MOS管并联(并联是指它们的源和源连接,漏和漏连接,各 自的栅还是独立的。) (1)栅极水平放置,节点X和Y可用金 属连线连接(图b);也可用有源区连接(图c)。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

由于全部电流都要通过输入晶体管中的每一个,例如,有时整个电 流完全在M3,当差分信号关断时,M3关断M4接通,整个电流又完全在 M4,信号每摆动一次就切换一次,为了承受这一电流,在M3和M4之间 的金属线需要达到一定的宽度,采用二条金属线连接M3和M4的源极,并 且从M4b和M3b的中间向下,这样,M3导通时电流将通过M3a和M3b, 即它的两半把电流向下送到中心导线。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

4. CMOS放大器

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

1. CMOS门电路

(1) 反相器

电路图

版图1

版图2

版图1特点:多晶栅竖直排列,MOS管源区面积小,因而反相器面积也小。 版图2特点:多晶栅水平排列,MOS管漏极金属与电源、地金属线之间的 空档允许其它金属线通过,因水平尺寸较大而使面积稍大一些。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

2.MOS管并联(并联是指它们的源和源连接,漏和漏连接,各 自的栅还是独立的。) (1)栅极水平放置,节点X和Y可用金 属连线连接(图b);也可用有源区连接(图c)。

版图设计规则

版图几何设计规则

版图几何设计规则

版图几何设计规则可看作是对光刻掩 模版制备要求. 一般来讲,设计规则反映了性能和成 品率之间可能的最好的折衷.规则越保 守,能工作的电路就越多(即成品率越 高);然而,规则越富有进取性,则电路 性能改进的可能性也越大,这种改进可 能是以牺牲成品率为代价的.

版图几何设计规则

(1)微米规则 (2)λ规则

版图几何设计规则

大部分设计规则都可以归纳入以下描 述的四种规则之一. (1)最小宽度 (2)最小间距 (3)最小包围 (4)最小延伸

版图几何设计规则

设计规则(硅栅)举例:

0.6um 2p2m CMOS

0.6um 2p2m

版图几何设计规则-N阱

定义了P沟道器件的N阱尺寸,N型杂志注入该 区域形成N-well. N-well宽度 3.0 不同电势的N-well之间的距离-4.8 N-well中用于接触的N+与阱边沿的距离-0.4 N-well距阱外的N+的距离-4.0 N-well距阱外的P+的距离-0.4 N-well距阱内的P+的距离-1.8 距划线槽的距离8.0

版图几何设计规则-接触孔

0.6

0.6

0.4

0.6

0.7

0.4

0.6

0.4

版图几何设计规则

编号 1 2 描述 金属宽度 金属间距 尺寸 0.9 0.8 防止铝条接触 保证良好导电性

版图几何设计规则-金属1

metal1宽度:0.9 Metal1之间的距离:0.8 Metal1距接触孔的距离:0.3

版图几何设计规则-多晶硅

PMOS

NMOS

0.6

0.6

0.6

0.75

0.5

版图几何设计规则

版图几何设计规则可看作是对光刻掩 模版制备要求. 一般来讲,设计规则反映了性能和成 品率之间可能的最好的折衷.规则越保 守,能工作的电路就越多(即成品率越 高);然而,规则越富有进取性,则电路 性能改进的可能性也越大,这种改进可 能是以牺牲成品率为代价的.

版图几何设计规则

(1)微米规则 (2)λ规则

版图几何设计规则

大部分设计规则都可以归纳入以下描 述的四种规则之一. (1)最小宽度 (2)最小间距 (3)最小包围 (4)最小延伸

版图几何设计规则

设计规则(硅栅)举例:

0.6um 2p2m CMOS

0.6um 2p2m

版图几何设计规则-N阱

定义了P沟道器件的N阱尺寸,N型杂志注入该 区域形成N-well. N-well宽度 3.0 不同电势的N-well之间的距离-4.8 N-well中用于接触的N+与阱边沿的距离-0.4 N-well距阱外的N+的距离-4.0 N-well距阱外的P+的距离-0.4 N-well距阱内的P+的距离-1.8 距划线槽的距离8.0

版图几何设计规则-接触孔

0.6

0.6

0.4

0.6

0.7

0.4

0.6

0.4

版图几何设计规则

编号 1 2 描述 金属宽度 金属间距 尺寸 0.9 0.8 防止铝条接触 保证良好导电性

版图几何设计规则-金属1

metal1宽度:0.9 Metal1之间的距离:0.8 Metal1距接触孔的距离:0.3

版图几何设计规则-多晶硅

PMOS

NMOS

0.6

0.6

0.6

0.75

0.5

版图设计规则

精选ppt

12

设Байду номын сангаас规则

3、最小交叠(minOverlap) 交叠有两种形式: a)一几何图形内边界到另一图形的内边界长度(overlap),

如图 (a) b)一几何图形外边界到另一图形的内边界长度(extension),

如图 (b)

精选ppt

13

TSMC_0.35μm CMOS工艺版图 各层图形之间最小交叠

精选ppt

14

设计规则举例

Metal相关的设计规则列表

编号 描 述 尺 寸

5a 金属宽度 2.5

5b 金属间距 2.0

目的与作用

保证铝线的良好 电导

防止铝条联条

精选ppt

15

设计规则举例

精选ppt

16

tf文件(Technology File)和display.drf文件

这两个文件可由厂家提供,也可由设计人员根 据design rule自已编写。

•Sizing Commands(尺寸命令)

把整个图形扩展

扩展边沿

线扩精选展ppt

26

Layer Processing(层处理命令)

•Selection Commands(选择命令)

顶点

octagon

图形

精选ppt

27

Layer Processing(层处理命令)

(NM OMS/1P-MM5O(7S8防m止O穿h通m/注sq入) T)hickVTN/VtoPpN-m=eNta/l P(1C8hmaOnhnmel/sq)

Threshold Voltage Adjust

(NMOS阈值电压调节注入)

精选ppt

6

设计规则(design rule)

版图设计规则及验证汇总

SiO2

N- Si 阱

P-S i Sub

光刻3:硅栅光刻

3#版为多晶光刻掩膜。用于制作多晶硅栅极以及 形成电路结构的多晶硅的连线和电阻。这一步是 在新生长的栅氧化层上先用CVD法沉淀多晶硅,用 该版以干法刻蚀出所需多晶硅图形。

光刻3:硅栅光刻

N- Si 阱

P-S i Sub

光刻4:P管源漏区芯片规划 根据已知的模块数量和线网连接表来估算芯片面 积,其中模块大约占用一半,另一半用来作为布 线通道。

二、版图设计过程

(三)布局 布局是指如何把各个模块合理地排布在芯片上, 怎样确定每个模块的最佳位置,以使占用芯片面 积为最小且布线结果又最好。

二、版图设计过程

二、版图设计过程

版图设计主要包括模块设计、芯片规划、布局、 布线等,是一个组合规划和巧拼图形的工作。在 一个规则形伏(一般为长方形)平面区域内不重 叠地布局多个模块(亦称部件),在各模块之间 按电路连接信息的要求逐行布线。版图设计是从 逻辑信息向几何信息的转换。

二、版图设计过程

(一)模块设计 芯片设计中最小的单位是元件,设计过程从元件, 门,基本单元,宏单元,芯片,从小到大进行。 基本单元和宏单元可视为模块。模块设计是最基 本的环节。

光刻5:N管源漏区注入光刻

N+注入

N- Si 阱

P-S i Sub

光刻6:接触孔光刻

6#版为接触孔掩膜。用来确定欧姆接触的大小和 位置。

光刻6:接触孔光刻

N- Si 阱

P-S i Sub

光刻7:金属引线光刻

7#版为金属图形(电极和连线)掩膜。用于确定集成 元器件电极引出和互连布线的位置和形状。在上 一版接触孔光刻之后,硅片表面用CVD法淀积上一 层金属膜,用该版留下所要的金属膜,实现金属层欧 姆引出和互连。

N- Si 阱

P-S i Sub

光刻3:硅栅光刻

3#版为多晶光刻掩膜。用于制作多晶硅栅极以及 形成电路结构的多晶硅的连线和电阻。这一步是 在新生长的栅氧化层上先用CVD法沉淀多晶硅,用 该版以干法刻蚀出所需多晶硅图形。

光刻3:硅栅光刻

N- Si 阱

P-S i Sub

光刻4:P管源漏区芯片规划 根据已知的模块数量和线网连接表来估算芯片面 积,其中模块大约占用一半,另一半用来作为布 线通道。

二、版图设计过程

(三)布局 布局是指如何把各个模块合理地排布在芯片上, 怎样确定每个模块的最佳位置,以使占用芯片面 积为最小且布线结果又最好。

二、版图设计过程

二、版图设计过程

版图设计主要包括模块设计、芯片规划、布局、 布线等,是一个组合规划和巧拼图形的工作。在 一个规则形伏(一般为长方形)平面区域内不重 叠地布局多个模块(亦称部件),在各模块之间 按电路连接信息的要求逐行布线。版图设计是从 逻辑信息向几何信息的转换。

二、版图设计过程

(一)模块设计 芯片设计中最小的单位是元件,设计过程从元件, 门,基本单元,宏单元,芯片,从小到大进行。 基本单元和宏单元可视为模块。模块设计是最基 本的环节。

光刻5:N管源漏区注入光刻

N+注入

N- Si 阱

P-S i Sub

光刻6:接触孔光刻

6#版为接触孔掩膜。用来确定欧姆接触的大小和 位置。

光刻6:接触孔光刻

N- Si 阱

P-S i Sub

光刻7:金属引线光刻

7#版为金属图形(电极和连线)掩膜。用于确定集成 元器件电极引出和互连布线的位置和形状。在上 一版接触孔光刻之后,硅片表面用CVD法淀积上一 层金属膜,用该版留下所要的金属膜,实现金属层欧 姆引出和互连。

数字后端版图设计ppt课件

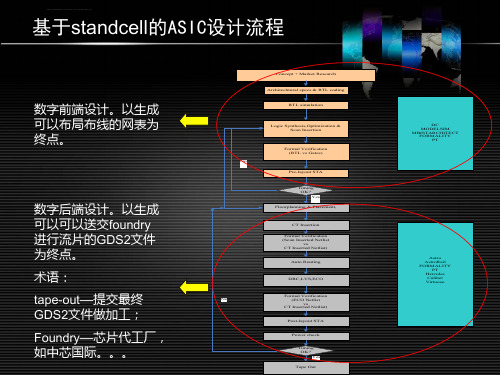

数字后端设计流程-8

布线

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

数字后端设计流程-8

布线

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

芯片中的时钟网络要驱动电路中所有的时序单元,所以 时钟源端门单元带载很多,其负载延时很大并且不平衡, 需要插入缓冲器减小负载和平衡延时。时钟网络及其上 的缓冲器构成了时钟树。一般要反复几次才可以做出一 个比较理想的时钟树。

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

数字后端设计流程-2

哪些工作要APR工具完成? 芯片布图(RAM,ROM等的摆放、芯片供电网络配置、 I/O PAD摆放) 标准单元的布局 时钟树和复位树综合 布线 DRC LVS DFM(Design For Manufacturing)

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

布图

这是一个小电路,电源 规划比较简单,对于一 个复杂的电路,还需要 横竖添加stripes,降低 IRdrop。

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

数字后端设计流程-5

布线

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

数字后端设计流程-8

布线

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

芯片中的时钟网络要驱动电路中所有的时序单元,所以 时钟源端门单元带载很多,其负载延时很大并且不平衡, 需要插入缓冲器减小负载和平衡延时。时钟网络及其上 的缓冲器构成了时钟树。一般要反复几次才可以做出一 个比较理想的时钟树。

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

数字后端设计流程-2

哪些工作要APR工具完成? 芯片布图(RAM,ROM等的摆放、芯片供电网络配置、 I/O PAD摆放) 标准单元的布局 时钟树和复位树综合 布线 DRC LVS DFM(Design For Manufacturing)

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

布图

这是一个小电路,电源 规划比较简单,对于一 个复杂的电路,还需要 横竖添加stripes,降低 IRdrop。

采用PP管及配件:根据给水设计图配 置好PP管及配 件,用 管件在 管材垂 直角切 断管材 ,边剪 边旋转 ,以保 证切口 面的圆 度,保 持熔接 部位干 净无污 物

数字后端设计流程-5

第二讲集成电路版图设计规则

- 1.5mA 最大电流密度

/um

-

- 禁止并行金属线90度拐角,用135

度拐角代替

a

c.2

b

c.1 c.2

设计规则 via

定义为两层金属之 间的连接孔

符号 尺寸

含义

12.a .7*.7 过孔最小面积

12.b 0.8 过孔间距

12.d~f - 接触孔、poly-poly电容和栅 上不能打过孔

12.g 0.4 金属1对过孔的最小覆盖

6.d 6.e 6.f 6.g

尺寸 1.2 1.0 0.5 3.2 1.5 0.8 -

含义 poly2做电容时的最小宽度 poly2做电容时的最小间距 Poly2与有源区的最小间距 做关键电容时的间距 电容底板对顶板的最小覆盖 电容Poly2对接触孔最小覆盖 Poly2不能在有源区上 Poly2不能跨过poly1边沿

– 上华0.6um DPDM CMOS工艺拓扑设计规则 – 设计规则的运用

• 版图设计准则(‘Rule’ for performance)

– 匹配 – 抗干扰 – 寄生的优化 – 可靠性

引言

• 芯片加工:从版图到裸片

制

加

版

工

是一种多层平面“印刷”和 叠加过程,但中间是否会 带来误差?

引言

一个版图的例子:

习)

VDD

15k

OUT IN 80/0.8

又试问NMOS晶体管的漏极面积和周长是多 少?

设计规则的运用

• TASK3:设计一个简单开关电容电路 (练习)

f1 IN

30/0.6 X

f2 OUT

60/0.6 2pF 6/0.6 12/0.6

又试问X点的寄生电容如何计算?

Ledit及器件版图设计ppt课件

L-EDIT的应用

Auto panning:窗口自动 平移。即当鼠标碰到版 图窗口边缘时会自动平 移窗口跟随鼠标。

Active push rubberbanding:活动推拉。 选中后绘图时不必一直 按住鼠标来绘制多边形, 只用单击起点和结束点 即可完成

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

版图设计规则

a:阱的最小宽度 b:不同电位的阱间距 c:相同电位的阱间 距 d:阱对有源区的最小覆盖 e:阱外有源区和阱的间距

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

版图设计规则

a:有源区的最小宽度 b:沟道最小宽度 c:有源区间距

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

举例:CMOS结构示意图

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

举例:CMOS结构示意图

L-edit 14.0基本的操作界面

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

L-EDIT的应用

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

Auto panning:窗口自动 平移。即当鼠标碰到版 图窗口边缘时会自动平 移窗口跟随鼠标。

Active push rubberbanding:活动推拉。 选中后绘图时不必一直 按住鼠标来绘制多边形, 只用单击起点和结束点 即可完成

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

版图设计规则

a:阱的最小宽度 b:不同电位的阱间距 c:相同电位的阱间 距 d:阱对有源区的最小覆盖 e:阱外有源区和阱的间距

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

版图设计规则

a:有源区的最小宽度 b:沟道最小宽度 c:有源区间距

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

举例:CMOS结构示意图

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

举例:CMOS结构示意图

L-edit 14.0基本的操作界面

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

L-EDIT的应用

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

火灾袭来时要迅速疏散逃生,不可蜂 拥而出 或留恋 财物, 要当机 立断, 披上浸 湿的衣 服或裹 上湿毛 毯、湿 被褥勇 敢地冲 出去

版图设计规则

3

第3页/共45页

版图设计规则

(一)、设计的类型 • Minimum Width • Exact Width • Not Exist • Spacing • Surround • Overlap • Extension • Density

4

第4页/共45页

版图设计规则

5

第5页/共45页

版图设计规则

12

第12页/共45页

版图设计规则的应用

•多晶硅条最小宽度5 um Poly minum width =5 um

• 多晶硅条最小间距5 um poly to poly spacing=5 um

• 离子注入区对有源区最 小覆盖10 um

• 铝引线孔7.5*7.5 um*um

p-select surround active =10 um n-select surround active

17

第17页/共45页

CMOS IC 版图设计技巧

1、布局要合理 (1)引出端分布是否便于使用或与其他相关电路兼容,是否 符合管壳引出线排列要求。 (2)特殊要求的单元是否安排合理,如p阱与p管漏源p+区离 远一些,使pnp,抑制Latch-up,尤其是输出级更应注意。 (3)布局是否紧凑,以节约芯片面积,一般尽可能将各单元 设计成方形。 (4)考虑到热场对器件工作的影响,应注意电路温度分布是 否合理。

①了解工艺现状,确定工艺路线

确定选用标准pn结隔离或对通隔离工艺或等平 面隔离工艺。由此确定工艺路线及光刻掩膜版的块数。

由制版和光刻工艺水平确定最小接触孔的尺寸和 光刻套刻精度。光刻工艺的分辨率,即能刻蚀图形的 最小宽度,受到掩膜分辨率、光刻胶分辨率、胶膜厚 度、横向腐蚀等多因素的限制。套刻精度与光刻机的 精度和操作人员的熟练程度关系密切。

第3页/共45页

版图设计规则

(一)、设计的类型 • Minimum Width • Exact Width • Not Exist • Spacing • Surround • Overlap • Extension • Density

4

第4页/共45页

版图设计规则

5

第5页/共45页

版图设计规则

12

第12页/共45页

版图设计规则的应用

•多晶硅条最小宽度5 um Poly minum width =5 um

• 多晶硅条最小间距5 um poly to poly spacing=5 um

• 离子注入区对有源区最 小覆盖10 um

• 铝引线孔7.5*7.5 um*um

p-select surround active =10 um n-select surround active

17

第17页/共45页

CMOS IC 版图设计技巧

1、布局要合理 (1)引出端分布是否便于使用或与其他相关电路兼容,是否 符合管壳引出线排列要求。 (2)特殊要求的单元是否安排合理,如p阱与p管漏源p+区离 远一些,使pnp,抑制Latch-up,尤其是输出级更应注意。 (3)布局是否紧凑,以节约芯片面积,一般尽可能将各单元 设计成方形。 (4)考虑到热场对器件工作的影响,应注意电路温度分布是 否合理。

①了解工艺现状,确定工艺路线

确定选用标准pn结隔离或对通隔离工艺或等平 面隔离工艺。由此确定工艺路线及光刻掩膜版的块数。

由制版和光刻工艺水平确定最小接触孔的尺寸和 光刻套刻精度。光刻工艺的分辨率,即能刻蚀图形的 最小宽度,受到掩膜分辨率、光刻胶分辨率、胶膜厚 度、横向腐蚀等多因素的限制。套刻精度与光刻机的 精度和操作人员的熟练程度关系密切。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

举例:工艺结构 •TSMC 0.35umCMOS工艺定义的全部工艺层

举例:工艺结构

•0.18um 工艺结构

Feature size L=0.18um VDD 1.8V/2.5V Deep NWELL to reduce

substrate noise MIM capacitor(1fF/um^2) 6 Metal 1 Poly Polycideresistor(7.5 Ohm/sq) NAPT/PHAPigTh=NN/P/PimCphalannntelreAsnisttio-r(59 PunchtOhrhomug/shq, 133 Ohm/sq) (NMOS/MPM1O-SM防5止(7穿8 m通O注h入m)/sq) ThickVTN/VPtNop=-mN/ePtaCl h(1a8nnmelOhThmr/essqh)old Voltage Adjust (NMOS阈值电压调 节注入)

•Logical Commands(逻辑命令)

ndiff

poly Original layer

Layer Processing(层处理命令)

•Logical Commands(逻辑命令)

原始层

poly

diff

Layer Processing(层处理命令)

•Relational Commands (关系命令)

版图概述

设计者只能根据厂家提供的设计规则进行 版图设计。严格遵守设计规则可以极大地 避免由于短路、断路造成的电路失效和容 差以及寄生效应引起的性能劣化。

版图在设计的过程中要进行定期的检查, 避免错误的积累而导致难以修改。

举例:工艺结构

以TSMC(台积电)的0.35μm CMOS工艺为例

TSMC的0.35μm沟道尺寸和对应的电源电压、 电路布局图中金属布线层及其性能参数

设计规则(design rule)

•TSMC_0.35μm CMOS工艺中各版图层的线条最小宽度

设计规则(design rule)

2、最小间距(minSep) 间距指各几何图形外边界之间的距离。

TSMC_0.35μm CMOS工艺版图 各层图形之间的最小间距

设计规则

3、最小交叠(minOverlap) 交叠有两种形式: a)一几何图形内边界到另一图形的内边界长度(overlap),

版图设计规则

版图概述

定义:版图(Layout)是集成电路设计者将设计 并模拟优化后的电路转化成的一系列几何图形, 包含了集成电路尺寸、各层拓扑定义等器件相 关的物理信息数据。

集成电路制造厂家根据这些数据来制造掩膜。 掩膜上的图形决定着芯片上器件或连接物理层

的尺寸。因此版图上的几何图形尺寸与芯片上 物理层的尺寸直接相关。

设计规则举例

tf文件(Technology File)和display.drf文件

这两个文件可由厂家提供,也可由设计人员根 据design rule自已编写。

tf文件规定了版图的层次、各层次的表示方式、 设计规则。

display.drf是一个显示文件,规定显示的颜色。

Tf & display

顶点 octagon

图形

Layer Processing(层处理命令)

•Selection Commands(选择命令)

gate = geomAnd(poly diff) sd = geomAndNot(diff poly)

Layer Processing(层处理命令)

•Selection Commands(选择命令)

定义: drcExtractRules(

bkgnd = geomBkgnd() NT = geomOr( "NT" ) ;。 TO = geomOr( "TO" ) ;有源区, GT = geomOr( "GT" ) ;多晶硅 W1 = geomOr( "W1" ) ;接触孔 A1 = geomOr( "A1" ) ;铝线

DRC(设计规则检查 Design Rule Check)

•层的概念

Original Layer 初始层 Derived Layer 衍(派)生层 Layer Processing 层处理 Geometry 几何图形

Layer Processing(层处理命令)

•层处理命令的类型

Layer Processing(层处理命令)

DRC规则文件

saveDerived 语句输出坏的接触孔图形到错 误层中。

举例: saveDerived( geomAndNot( W1 geomOr( TO GT ) ) "Contact not inside Active or Poly" ) saveDerived( geomAndNot( W1 A1 ) "Contacts not covered by Metal" ) drc( W1 width < 4.0 "Contact width < 4.0" ) drc( W1 sep < 2.0 "Contact to Contact spacing < 2.0" ) drc( TO W1 enc < 1.5 "Contact inside Active < 1.5" )

MIM:metal-insulator-metal

HDP:high-density plasma

厚的顶层金属:信号线,减少了寄 生电容和电阻干扰

设计规则(design rule)

版图几何设计规则可看作是对光刻掩模 版制备要求。光刻掩模版是用来制造集 成电路的。这些规则在生产阶段中为电 路设计师和工艺工程师提供了一种必要 的信息联系。

Layer Processing(层处理命令)

•Relational Commands (关系命令)

外切

图片有错 颠倒一下

内切

Layer Processing(层处理命令)

•Sizing Commands(尺寸命令)

把整个图形扩展

扩展边沿

线扩展

Layer Processing(层处理命令)

•Selection Commands(选择命令)

设计规则主要包括各层的最小宽度、层与层之 间的最小间距、最小交叠等。

设计规则(design rule)

1、最小宽度(minWidth) 最小宽度指封闭几何图形的内边之间的距离

在利用DRC(设计规则检查)对版图进行几何规则检查时,对于宽度低 于规则中指定的最小宽度的几何图形,计算机将给出错误提示。

•当technology file 创建后,用di于vaDDRRCC的.ru规l 则 在drcExtractRules 中定义

DRC (Design Rule Check)的命令

•DRC Function DRC函数

槽口

DRC (Design Rule Check)的命令

DRC规则文件

geomOr( )语句的目的是把括号里的层次合并起 来,也就是或的关系。

DRC规则文件

练习

Wactive = geomAnd( W1 TO ) Wpoly = geomAnd( W1 GT ) drc( Wpoly TO sep < 3.5 ) drc( Wactive GT sep < 2.0 ) drc( GT W1 enc < 1.5) drc( A1 W1 enc < 1.5)

;N阱,假设技术文件中以”NT”为名。 ;有源区,’’ ;多晶硅 ;接触孔 ;铝线

DRC规则文件

[outlayer]=drc(inlayer1 [inlayer2] function [modifiers] )

说明: outlayer表示输出层 ,如果没有定义outlayer层,出

错的信息将直接显示在出错的原来层次上。

• 版图的设计有特定的规则,规则是集成 电路制造厂家根据自已的工艺特点而制定 的。因此,不同的工艺就有不同的设计规 则。设计者只有得到了厂家提供的规则以 后,才能开始设计。

设计规则(design rule)

两种规则: (a) 以λ (lamda)为单位的设计规则—相对单位 (b) 以μ m(micron)为单位的设计规则—绝对单位 如果一种工艺的特征尺寸为S μ m,则λ =S/2 μ m, 选用λ 为单位的设计规则主要与MOS工艺的成比例 缩小有关。

如图 (a) b)一几何图形外边界到另一图形的内边界长度(extension),

如图 (b)

TSMC_0.35μm CMOS工艺版图 各层图形之间最小交叠

设计规则举例

Metal相关的设计规则列表

编号 描 述 尺 寸

5a 金属宽度 2.5

5b 金属间距 2.0

目的与作用

保证铝线的良好 电导

防止铝条联条

;接触孔

A1 = geomOr( "A1" )

;铝线

drc(GT TO (enc<2) "Poly Overhang out of Active into Field<2.0")

DRC规则文件

geomAnd()把括号内层次“与”之后再 赋给前面的新层次。

geomAndNot()是把括号内层次“与非” 之后再赋给前面的新层次。

DRC规则文件

举例:

gate = geomAnd( GT TO ) connect = geomAndNot( GT TO ) drc( connect TO

( sep < 2.0) " Field Poly to Active spacing < 2.0") drc( gate TO