第4章TTL电路半导体集成电路共14章 53页

第4章 晶体管-晶体管逻辑(TTL)电路

二、低功耗肖特基TTL(LSTTL)电路

功耗19mW,门延时3ns。

功耗仅2mW,门延时9.5ns。

两个电路的不同之处: (1)用肖特基势垒二极管D1、D2代替多发射极晶体管Q1。 (2)将Q4管的基极泄放电阻R4由接地改为接输出端Vo, 并加上SBD管D5和D6。 (3)采用高阻值电阻。

LSTTL电路的基本特点: (1)采用高阻值电阻使功耗PD 下降为标准TTL门的1/5左右。 (2)用R1、D1、D2组成以SBD为 输入管的DTL电路。因为在LSTTL 电路中,已用肖特基箝位晶体管 代替可能进入饱和状态的一般晶 体管,所以这些管子的基区超额 存储电荷减小,没有必要再用反 抽能力很强的多发射极晶体管来 加快Q2管脱离饱和。 用DTL输入方式有以下优点:

1、划分隔离区

根据隔离岛的划分原则,本电路可划分成七个隔离区。

2、基本设计条件的确定 包括采用的工艺、基本的工艺设计参数和版图设计规则。 3、各单元的图形设计 集成电路中各元器件的图形和尺寸,取决于它在集成电路中 的作用以及对其参数的要求,所有尺寸的设计要符合版图设计 规则的要求。所以在进行各单元的图形、尺寸设计前,首先要 对电路进行分析。例如,关于基区扩散电阻的设计,如第3章中 介绍的那样,当知道版图设计规则、通过电阻的电流和对电阻 的参数要求后,先确定电阻条的最小宽度,然后计算电阻的长 度。至于电阻的形状,可根据布局和布线的要求适当进行调整。 又如一般NPN晶体管的设计,当知道对其参数要求后,首先确定 图形结构,然后根据单位有效发射区周长所允许的最大电流αE 计算有效发射区总的长度,再由设计规则确定图形各部分的尺 寸和间距。

三、六管单元与非门

当输入电压大于等于0.55V时,VC2开始下降,而此 时Q5管尚未导通,对应图4.2曲线的BC段。由于电压 传输特性曲线上出现了线性区BC段,使电路的抗干扰 能力下降。在电路导通的瞬态,由于R3的存在,分走 了部分Q5管的基极驱动电流,使下降时间延长。

第4章TTL电路半导体集成电路共14章

输入信号VI

处到输出波形上升沿 50% 幅值处所需要的时

输出信号V0

间,

平均传输延迟时间tpd:

t

p

dt

P

LHt 2

P

HL

通常tPLH>tPHL,tpd越小, 电路的开关速度越高。

2019/12/19

返回22

简易TTL与非门的版图

2019/12/19

VCC

接触孔 集电区 基区 发射区 电阻 电源线

B、C的与运算

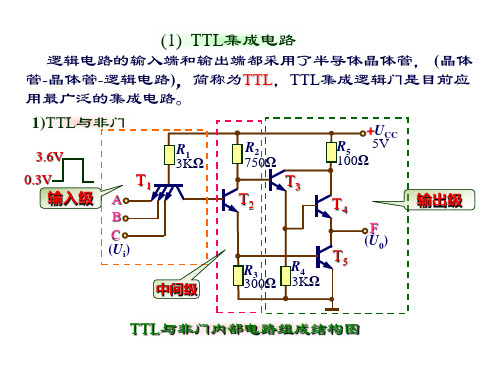

输出级:由T3、T4、T5和R4、R5组成 其中T3、T4构成复合管,与T5组成推 拉式输出结构。具有较强的负载能力

2019/12/19

30

TTL与非门工作原理

输入端至少有一个接低 电平

T1管:A端发射结导通,Vb1 = VA + Vbe1 = 1V, 其它发射结均因反偏而截 止.

VB1被嵌位在1.4V

T1管的发射结反偏,集电结正偏, 工作在反向有源区,集电极电流 是流出的,T2管的基极电流为: IB2=-IC1=IB1+bIB1≈IB1(b<0.01)

IB1=(VCC-VB1)/R1 =5V-1.4V/4K=0.9mA

∴ IB2≈0.9mA

R1 4K

VCC

R2 4K

A B C

T2管截止, VOH=VCC-IOHR2

T2管的集电结反偏,Ic1很小, 满足βIB1> Ic1,T1管深饱和,

VOCS1=0.1V,VB2=0.4V

输出高电平时电路供给负载门的电流

2019/12/19

简易TTL与非门 6

2. 输入信号全为高电平

VOH=5V VB1 =VBC1+VBE2

=0.7V+0.7V =1.4V

TTL集成电路

②输入端全部为高电平时的工作情况:

3.6V 0.3V

R1

T1 23.K1ΩV

R2 750Ω

T3

+UCC R5 5V

100Ω 显然T1处于倒 置工作状态,

3.6V A 3.6V B

1.4V T2

3.6V C (Ui)

深度饱和

由“地”经T2、 T5管的

发

R3 300Ω

T4

此时集电结做 为发射结使用。

R4

A

&

F

B

A&

B

F1

C&

D

F2

+UC “线与” 逻辑功能

RC

F 可实现

“与或非” 逻辑运算

F F1 • F2 AB • CD AB CD

上述分析可知,OC门具有“线与”功能,并且在线 与的过程中实现了输出对输入的与或非逻辑运算。OC 门还可用于数字系统接口部分的电平转换。

+12V

RC

T4

F

(U0)

T5

输出级

TTL与非门内部电路组成结构图

R1 3KΩ

R2 750Ω

+UCC R5 5V 100Ω

T1

A B C (Ui)

输入级由多发射极晶体管T1和电 阻R1组成。所谓多发射极晶体管, 可看作由多个晶体管的集电极和基

T3

T2

T4

F

(U0)

R3 300Ω

R4

T5

3KΩ

极分别并接在一起,而发射极作为逻辑门的输入端。多个发射极

A B

一个普通与非门,输出由输入 端A、B决定。

三态门控制端EN=0(有效态) EN

T R2 D1

集成电路教案

《半导体集成电路》课程教学教案课程总体介绍:教材:选用清华大学出版社出版的朱正涌编写的高等学校电子信息类规划教材《半导体集成电路》一书。

根据同学的基础情况参考了上海科技出版社张延庆,张开华编写《半导体集成电路》。

1.该教材参考教学学时为120学时。

2.本教案按教学学时数:64学时编制。

3.教学内容学时分配:第一篇半导体集成电路制造工艺与寄生效应11学时第0章绪论2学时第一章半导体集成电路基本制造工艺5学时第二章集成电路的寄生效应4学时第二篇双极型逻辑集成电路21学时第三章TTL集成电路11学时第四章TTL中大规模集成电路设计与版图设计8学时第五章ECL电路与IIL电路2学时第三篇MOS 逻辑集成电路24学时第六章MOS反相器与传输们10学时第七章MOS基本逻辑门与版图设计8学时第八章MOS存储器6学时第四篇模拟集成电路8学时第九章模拟集成电路中的元器件与基本单元8学时教案结构:课程内容;课程重点;课程难点;基本概念;基本要求。

基本概念视同学的基础可以适当删减。

:课程教案:第一篇半导体集成电路制造工艺与寄生效应11学时第0章绪论2学时第一章半导体集成电路基本制造工艺5学时第二章集成电路的寄生效应4学时绪论2学时课程内容: 认识集成电路;集成电路的定义:集成电路的应用特点;集成电路分类。

1 半导体集成电路的发展史2 集成电路发展的特点3 半导体集成电路的分类4 课程内容介绍及要求课程重点:介绍了何谓集成电路,集成电路发展过程,集成电路是如何分类的(即可分为膜集成电路.半导体集成电路和混合集成电路。

半导体集成电路)是以制造工艺分类的,以集成电路的发展史集成电路有何特点;介绍了何谓半导体集成电路,半导体集成电路的分类(即按照电路中晶体管的导电载流子状况分类,可分为双极型集成电路和单极型集成电路两种;按照电路工作性质分类,可分为数字集成电路和模拟集成电路两种),半导体集成电路的重要概念-集成度,以及半导体集成电路的优点(即体积小重量轻;技术指标先进可靠性高以及便于大批量生产和成本低等)。

详解TTL电路

详解TTL门电路一、什么是TTL门电路TTL 是一种集成电路,通过使用双极性晶体管组合来做到具有驱动能力的逻辑输出。

TTL 最重要的特性是门的输入在未连接时将为逻辑高电平。

在硬件电路中,会用到逻辑门这样的数字器件,对于这样的数字器件,从内部工艺结构来份的话主要有两个大的分支:一个是晶体管构成的,另一个是场效应管构成的。

而晶体管构成的门电路,被称为TTL门电路。

二、TTL电路工作原理TTL门电路也分很多种,比如说非门、与非门、或非门、与或非门以及OC输出的与非门。

虽然种类多,但是基本的工作原理都是类似的。

以常用的与非门电路为例对其工作原理进行介绍。

图 1 非门的TTL电路从图1中可以看出非门电路是由Q1输入级、Q2中间级以及Q3、Q4输出级组成。

1、输入级:Q1从结构上把它看成由二极管构成的,两个二极管的P结背靠背,N结分别连接输入和Q2的基极。

2、中间级:由三极管Q2和电阻R2、R4组成。

在电路的开通过程中利用Q2的放大作用,为输出管Q3和Q4提供较大的基极电流,加速了输出管的导通。

所以,中间级的作用是提高输出管的开通速度,改善电路的性能。

3、输出级:由三极管Q3、Q4、二极管D1和电阻R3组成。

从图中可以看出,输出级由三极管Q4实现逻辑非的运算。

但在输出级电路中用三极管Q3、二极管D1和R3组成的有源负载来使输出级具有较强的负载能力。

其中D1可以起到三极管be反向击穿的保护作用。

工作原理:1、当输入端Input为逻辑低电平时,电流流经R1至Input,Q1晶体管导通,此时Vb(Q2)的电压小于Vbe导通电压0.7V,Q2晶体管截止。

此时由于R2与R4的存在,使Q3导通、Q4截止,在Out上输出高电平。

由图1中输出结构可知,此时输出高电平电压将为:Vout=Vcc−Vce−V D1≈Vcc-1V。

2、当输入端Input为逻辑高电平时,Q1晶体管截止,此时电流流经R1和Q1的PN结,流向Q2的基极,Q2晶体管导通。

第14章版图设计基础(半导体集成电路共14章)讲解

AHDL

SPECTURE

逻辑图

寄存器传输级 描述 寄存器传输级 模拟与验证

综合 逻辑模拟 与验证

DC modelsim

SPICE/ SPECTURE

电路图

电路模拟 与验证

版图生成

CADENCE的Virtuso

APOLLO(自动)

版图几何设计规则和 电学规则检查

同右

网表一致性检 查和后仿真

4.PAD单元

PAD单元部分包括: (1)绑定金属线所需的 可靠连接区域 (2)ESD保护结构 (4)与内部电路相连的 接口 (3)输入、输出缓冲器

(1)绑定金属线所需的可靠连接区域

(2)ESD保护结构 ESD:ElectroStatic Discharge

输入I/O栅保护电路

其余ESD保护电路见P397

Dog Bone

接触孔 :

CON.1 最大/最小接触孔尺寸 CON.2 接触孔最小间距 CON.3 CON.5 扩散区的接触孔与边沿的距 离 多晶硅栅上的接触孔到多晶 硅栅边界的距离 0.40x0.40

CON.5 CON.2 CON.3 CON.1 CON.6 CON.5 Legend Comp Poly 2 Contact

PAD 3.13 PAD.3.14

M3

Via2

M2

via1

M1

键合点(PAD)

PAD.1 PAD.2 PAD.3.1

宽度 间距 顶层金属四周覆盖键合点距离

70 30 2.5

说明:实际版图中的pad都是有保护电路的,且厂商会 提供经过若干次实验的电路。

二、版图设计步骤(人工)

版图检查与验证

总体版图

半导体 集成电路

第4章TTL电路半导体集成电路共14章讲解

IB

IE

IC

IC=IB+IE

饱和工作区

C

B

VCES

E

截止区

C B

E

3

简易TTL与非门

与非门

A

B

C

O

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

0

VCC

R1

R2

B1

VO

A B C

B2 T1

T2

两管单元TTL与非门

2022/1/16

4

两管单元TTL与非门工作原理

VCC

R1 4K R2 4K

2022/1/16

由T6、R6和R3构成 的有源泄放电路来

代替T2射极电返阻回R3 36

TTL“与非〞门的静态特性及主要参数

2022/1/16

简易TTL与非门5

1. 输入信号中至少有一个为低电平的情况

VOL VB1 =VBE1+VOL

=1V

R1 4K

1V B1

VCC

R2 4K

IOH

VB1被嵌位在1V

IB1=(VCC-1V)/R1 =5V-1V/4K=1mA

A B C

VOL=0.3V

IC1

B2

T2管截止, VOH=VCC-IOHR2

2022/1/16

3 .6V 3 .6V 3 .6V

0 .3V

32

TTL与非门工作原理

《电工电子学》第4章 数字集成电路新

1

0

A

&

Y

0

B

C

跳转到第一页

例:

逻辑图

X &

A

B C

&

Y &

≥1

F

Z &

逻辑表 达式

X A ABC Y B ABC Z C ABC

F X Y Z A ABC B ABC C ABC

最简与或 表达式 F (A B C)(A B C ) ABC ABC

跳转到第一页

真值表

1 (A B)

AB

分配率 A+BC=(A+B)(A+C)

跳转到第一页

4.1.2 逻辑函数的表示方法

逻辑函数有3种表示形式:逻辑状态表、逻辑表达式、 逻辑图。

1、逻辑状态表

跳转到第一页

例如,要表示这样一个函数关系:当3个变量A、B、C的取值中有 偶数个1时,函数取值为1;否则,函数取值为0。此函数称为判偶 函数,可用真值表表示如下。

V4

A

FE

V5

& F

EN

符号

结论:电路的输出有高阻态、高电平和低电 平3种状态。

跳转到第一页

4.3 组合逻辑电路

4.3.1 组合逻辑电路的分析

A

&X

X AB Y BC Z CA

B

&Y

F &

F XYZ AB BC AC

C

&Z

F AB BC CA

跳转到第一页

F AB BCCA

ABC

EN

符号

②E=1时,二极管D截止,三态门的输出状态完全取决 于输入信号A的状态,电路输出与输入的逻辑关系和一 般反相器相同,即:F=A,A=0时F=1,为高电平;A =1时F=0,为低电平。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2019/11/21

4

两管单元TTL与非门工作原理

VCC

R1 4K R2 4K

B1

VO

A B C

B2 T1

T2

A B

C

R1 4K

B1

VCC

R2 4K

几个假设: 1.发射极正向压降,当晶体管正向工作时,取VbeF=0.7V,而当晶体管饱和时,

取VbeS=0.7V. 2.集电结正向饱和压降,取VbcF=0.6~0.7V。 3.晶体管饱和压降,当T1管深饱和时,因Ic几乎为零,取VceS=0.1V,其余管子取 VceS=0.3V

T1

T2

。

。 N个 。

VCC

4K

4K

VO

T1

T2

19

两管单元TTL与非门的静态特性

3. 直流功耗 P=ICC*VCC

VCC

R1 4K R2 4K

静态功耗:电路导通和截止时的功耗 B1

VO

1.空载导通电源电流 ICCL :

A B C

B2 T1

T2

ICC IL R 1IR 2V CR C 1V B 1V CR C 2 V O L2 .1 mA

VSS

23

VCC

R1

R2

B1

VO

A B C

B2 T1

T2

简易TTL与非门的缺点 1.输入抗干扰能力小 2.电路输出端负载能力弱 3.IB2太小,导通延迟改善小

四管单元与非门

2019/11/21

24

典型四管单元TTL与非门

VCC

R1

R2

R3

B1

A B C

B2 T1

T2

R5

T3

VO

T5

VCC

R1

R2

B1

VO

A B C

B2 T1

T2

2019/11/21

25

典型四管单元TTL与非门

VCC

VCC

R1

R2

R3 180

R1

R2

B1

A B C

B2 T1

T2

T3

VO

B1

VO

A B C

B2 T1

T2

T5

R4

电平移位作用

1. T2管使电路低电平噪声容限VNML提高了一个结压降,因此电 路抗干扰能力增强。

2. T3、T5构成推挽输出(又称图腾柱输出),使电路负载能力 增强。

2019/11/21

9

最大允许 电压

最小允许 电压

VOH

VOL

VIL

VOH

VIH

VOL

噪声

噪声

2019/11/21

10

"1"

高噪声容限

VIH 不定区

VIL

低噪声容限

VNMH VNML

VOH

VOL "0"

2019/11/21

Gate Input

Gate Output

VNML=VIL-VOL VNMH=VOH-VIH

Vb1 =1V,所以T2、T5截止, VC2≈Vcc=5V,

T3:微饱和状态。 T4:放大状态。 电路输出高电平为:

V O HV C 2V be3V be4

5-0.7-0.7=3.6V

2019/11/21

0 .3V 3 .6V 3 .6V

1V 5V

3 .6V

31

TTL与非门工作原理

输入端全为高电平 T1:Vb1= Vbc1+Vbe2+Vbe5 = 0.7V×3 = 2.1V 发射结反偏而集电极正偏.

VOH=5V

1.4V

B1

B2 IC1

T2管饱和,T2管的饱和电压VCES=0.3V

∴ VOL=0.3V

2019/11/21

简易TTL与非门7

T1管工作在反向放大区

假设:ßF=20, ßR=0.02

IB1=(VCC-VB1)/R1 =5V-1.4V/4K=0.9mA

-IE1=ßRIB1=0.02*0.9=0.018mA

2.空载截止电源电流 ICCH : 3.电路 平IC均C静H 态IR1功耗VC:C R 1VB1PC1.1m ICVCAC12(ICCLICCH)VCC

2019/11/21

8mW

20

两管单元TTL与非门的瞬态特性

VCC

R1

R2

Vi

B1

0 VO

A B C

B2 T1

T2

Vi

1. 延迟时间 2. 下降时间 3. 存储时间 4. 上升时间

处于反向放大状态

T2:饱和状态 T3:Vc2=Vces2+Vbe5≈1V, 使T3导通, Ve3=Vc2-Vbe3=1-0.7≈0.3V, 使T4截止。 T5:饱和状态, 因此输出为逻辑低电平 VOL=0.3V

2019/11/21

3 .6V 3 .6V 3 .6V

2.1V

0 .3V

32

TTL与非门工作原理

VB1被嵌位在1V

IB1=(VCC-1V)/R1 =5V-1V/4K=1mA

A B C

VOL=0.3V

R1 4K

1V

B1

VCC

R2 4K

IOH

IC1 0.4V B2

T2管截止, VOH=VCC-IOHR2

2019/11/21

输出高电平时电路供给负载门的电流

简易TTL与非门16

两管单元TTL与非门的静态特性-负载能力

B、C的与运算

输出级:由T3、T4、T5和R4、R5组成 其中T3、T4构成复合管,与T5组成推 拉式输出结构。具有较强的负载能力

2019/11/21

30

TTL与非门工作原理

输入端至少有一个接低 电平

T1管:A端发射结导通,Vb1 = VA + Vbe1 = 1V, 其它发射结均因反偏而截 止.

2019/11/21

0 t0 t1 t2 t3

t4 t5

td=t1-t0 tf=t2-t1 ts=t4-t3 tr=t5-t4

t t

21

平均传输延迟时间tpd

导通延迟时间tPHL :输入波形上升沿的50%幅值处到 输出波形下降沿50% 幅值处所需要的时间,

截止延迟时间tPLH:从输 入波形下降沿50% 幅值

2019/11/21

27

R1

R2

B1

A B C

B2 T1

T2

VCC

R5

电路导通时,T2、T5饱和

T3

VO T5

VO=VOL 这时,T2管的集电极和 输出之间的电位差为:

VC2-VO=VCES2+VBES5-VCES5≈VBES5=0.8V

T5和D不能同时导通

D起了电平移位的作用

2019/11/21

14

两管单元非门的噪声容限

VCC

R1

R2

B1

VO

A

B2 T1

T2

VA: 00.6V; >0.6V;

2019/11/21

0.6V

VNMH=VOH-VIH VNML=VIL-VOL VNML=0.6V-0.3V=0.3V

15

2. 负载能力

VOL=0.3V VB1 =VBE1+VOL

=0.3V+0.7V =1V

输入信号VI

处到输出波形上升沿 50% 幅值处所需要的时

输出信号V0

间,

平均传输延迟时间tpd:

t

p

dt

P

LHt 2

P

HL

通常tPLH>tPHL,tpd越小, 电路的开关速度越高。

2019/11/21

返回22

简易TTL与非门的版图

2019/11/21

VCC

接触孔 集电区 基区 发射区 电阻 电源线

VB1被嵌位在1.4V

T1管的发射结反偏,集电结正偏, 工作在反向有源区,集电极电流 是流出的,T2管的基极电流为: IB2=-IC1=IB1+bIB1≈IB1(b<0.01)

IB1=(VCC-VB1)/R1 =5V-1.4V/4K=0.9mA

∴ IB2≈0.9mA

R1 4K

VCC

R2 4K

A B C

11

Vin VDD

输入高电平 有效范围

VIH 过渡区

Vout

有效高电平输出 VOH

噪声

高电平

NMH=VOH-VIH

高噪声容 限

VIL

输入低电平 有效范围

0

NML=VIL-VOL 噪声

有效低电平输出

低噪声容限

VOL

低电平

噪声幅值+VOL<VIL

噪声幅值< VIL-VOL

噪声幅值+VIH<VOH

噪声幅值< VOH-VIH

R1 4K R2

VCC

4K

B1

VO

A B C

B2

T1 0.7V

T2

-IC1=(ßR+1)IB1=0.918=IB2 假设T2管工作在正向放大区

IB20.9mA, bF20 IC2bFIB2200.918mA

在R2上产生的压降为18mA*4K=72V

不成立

2019/11/21

8

两管单元TTL与非门的静态特性

输入端全为高电平, 输出为低电平 输入至少有一个为 低电平时,输出为高 电平 由此可见电路的输 出和输入之间满足 与非逻辑关系

F ABC

T1:反向放大状态 T2:饱和状态 T3:导通状态 TTTT4523::::截深截微止饱止饱状和状和态状态状态态 T4:放大状态 T5:截止状态