几何变换单元的设计及其FPGA实现

图形加速器中几何变换的设计与实现

高 质 量 的 图 形 显 示 以及 人 们 对 视 觉 效 果 的追 求 , 用 现有 的高 性 能 C U, 可 编程 的方 法 , 利 P 靠 已经 不 能满 足高 质量 复 杂场 景 图形实 时处理 和 显示 的要

求 。近 年 来 , 图形 处 理 器 ( P G a hc rcsig G U, rp is oes P n

a i t n o r p i s a d t tp a r ilr l n p ro ma c fg a is a c l r tr . i a e h w t n ma i fg a h c , n he i ly a cuca oe i e r n e o ph c c ee a o sTh s p p r s o is o f r S fwa e d sg de n t a o t h r le pei e sr c u e de i e nd i lme t d t e g o tia ot r e i n mo la d i d p s t e pa allpi ln tu t r , sg d a mpe n e h e merc l n

速 度 。最后将 电路 下载到 F G P A开发板 进行 了验证 。 关键 字 : 图形加速 器 ; 几何 变换 ; 流水线

The De i n a d I plm e t to sg n m e n a i n

o o e rc Tr n f r a i n i r p i c lr t r fGe m t i a s o m to G a h c Ac ee a o n

摘要: 几何变换 ( 包含旋转, 平移, 缩放 ) 单元是图形加速 器中唯一表现图形动画的基本单元, 其性能对于

整个 图形 加速 器起 着至 关重要 的作 用 。 文针对 图形加 速 器 中几何 变换 的特 性 , 出其 软件设 计模 型 , 本 提 并

fpga仿射变换

fpga仿射变换

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,其功能可以通过编程来定制。

在图像处理领域,常常使用FPGA来进行仿射变换。

仿射变换是一种几何变换,可以将一个图像映射到另一个图像上。

在FPGA中实现仿射变换需要使用到一些特定的算法和硬件资源。

首先,需要使用一些乘法器和加法器来计算图像中每个像素的变换。

这些运算需要使用到FPGA中的数字信号处理(DSP)资源。

为了提高计算效率,可以使用并行处理的策略,将多个像素的计算任务分配给不同的处理单元。

其次,需要使用到一些存储器资源来存储图像数据和变换矩阵。

在FPGA中,可以使用块RAM(BRAM)或者分布式RAM来存储这些数据。

BRAM具有较高的存储密度和较低的功耗,而分布式RAM具有较快的访问速度和较低的功耗。

最后,需要使用一些接口资源来传输图像数据和控制信号。

在FPGA中,可以使用AXI 或者PCIe等高速接口来传输数据,也可以使用SPI或I2C等低速接口来传输控制信号。

在实现仿射变换时,还需要考虑一些优化策略。

例如,可以使用查找表(LUT)来减少乘法运算的复杂度;可以使用流水线结构来提高计算效率;可以使用并行处理策略来加速计算过程。

总之,FPGA是一种非常适合实现仿射变换的硬件平台。

通过使用FPGA,可以大大提高图像处理的效率和速度,为各种应用场景提供更好的解决方案。

实验报告几何变换实验

实验报告几何变换实验实验报告:几何变换实验引言:几何变换是计算机图形学中的重要概念,它可以改变图像的形状、位置和大小。

在本次实验中,我们将通过对几何变换的实际操作,深入了解几何变换的原理和应用。

一、实验目的本次实验的主要目的是探究几何变换在图像处理中的应用,具体包括平移、旋转、缩放和翻转等几何变换操作。

通过实际操作和观察,我们将了解几何变换对图像的影响,并学习如何使用计算机编程实现这些变换。

二、实验材料和方法1. 实验材料:- 一台计算机- 图像处理软件(如Photoshop、GIMP等)- 编程软件(如Python、MATLAB等)2. 实验方法:- 步骤一:选择一张图片作为实验对象,并导入到图像处理软件中。

- 步骤二:使用图像处理软件进行平移操作,观察图像的位置变化。

- 步骤三:使用图像处理软件进行旋转操作,观察图像的旋转效果。

- 步骤四:使用图像处理软件进行缩放操作,观察图像的大小变化。

- 步骤五:使用图像处理软件进行翻转操作,观察图像的翻转效果。

- 步骤六:使用编程软件编写程序,实现上述几何变换操作,并观察结果。

三、实验结果与分析1. 平移操作:在实验中,我们发现通过平移操作,可以将图像在水平和垂直方向上进行移动。

通过调整平移的距离和方向,我们可以改变图像在画布上的位置。

这种操作常用于图像的对齐和拼接等应用中。

2. 旋转操作:旋转操作可以改变图像的角度和方向。

通过调整旋转的角度和中心点,我们可以使图像以不同的角度进行旋转。

这种操作常用于图像的矫正、仿射变换等应用中。

3. 缩放操作:缩放操作可以改变图像的大小。

通过调整缩放的比例,我们可以使图像变得更大或更小。

这种操作常用于图像的放大、缩小、裁剪等应用中。

4. 翻转操作:翻转操作可以改变图像的方向。

通过水平或垂直翻转,我们可以使图像在左右或上下方向发生镜像反转。

这种操作常用于图像的镜像处理、对称效果等应用中。

四、实验总结通过本次实验,我们深入了解了几何变换在图像处理中的应用。

OFDM调制解调及FPGA实现

OFDM(正交频分复用)是一种高效的多载波调制技术,其最大的特点是传输速率高,具有很强的抗码间干扰和信道选择性衰落能力。

OFDM最初用于高速MODEM、数字移动通信和无线调频信道上的宽带数据传输,随着IEEE802.11a协议、BRAN(Broadband Radio Access Network)和多媒体的发展,数字音频广播(DAB)、地面数字视频广播((DVB-T)和高清晰度电视((HDTV)都应用了OFDM 技术.OFDM利用离散傅立叶反变换/离散傅立叶变换(IDFT/DFT)代替多载波调制和解调,调制解调的核心是快速傅立叶运算单元,在进行蝴蝶运算时,不可避免的要进行大量的乘法运算。

由于FPGA具有强大的并行处理和计算能力,以及丰富的存储资源和逻辑运算资源,因此在FPGA器件上实现OFDM调制解调结构,具有很好的通用性和灵活性。

OFDM与系统框图OFDM的多个载波相互正交,一个信号内包含整数个载波周期,每个载波的频点和相邻载波零点重叠,这种载波间的部分重叠提高了频带利用率.OFDM每个子信道的频谱均为sinx/x形,各子信道频谱相互交叠,但在每个子信道载频的位置来自其他子信道的干扰为零,如图1所示。

OFDM系统如图2所示,OFDM系统的调制和解调分别由IFFT和FFT完成。

首先将串行输入数据d0,d1。

,d(N—1)变换成并行数据,接下来进行编码和星座图映射,得到频域数据。

经过IFFT后相当于调制到正交的N个f0,f1,。

,fN-1子载波,完成正交频分复用.接下来加入循环前缀,进行并/串转换,数/模转换,再调制到高频载波上发送。

如果是基带传输,则不需要进行载波调制。

在接收端进行相反的操作,使用N个相同的子载波进行N路解调,再将这N路解调信号并串输出,复现发送的原始信号。

经过FFT变换后的数据相当于将时域数据再转换成频域数据,即完成了OFDM信号的解调。

OFDM调制原理虽然是用N个正交的载波分别调制N路子信道码元序列,但实际中很难独立产生N个正交的载波。

fpga 频率变换 实现方法

fpga 频率变换实现方法

FPGA(现场可编程门阵列)是一种可以进行并行处理的集成电路,其频率

变换可以通过以下几种方法实现:

1. 时钟分频器:FPGA内部通常包含一些内置的时钟分频器,可以将输入的时钟信号进行分频,从而得到不同频率的输出信号。

在FPGA开发工具中,可以通过配置时钟分频器的参数来改变分频比,从而实现频率变换。

2. 时钟生成器:FPGA内部还可以生成一些高精度的时钟信号,这些时钟信号可以通过配置时钟生成器的参数来改变其频率。

在FPGA开发工具中,可以使用内建的时钟生成器来生成所需的时钟信号。

3. 数字控制振荡器(Digital Controlled Oscillator,DCO):DCO是一种数字控制的振荡器,可以通过改变控制字来改变其振荡频率。

在FPGA开发工具中,可以通过配置DCO的参数来改变其振荡频率,从而实现频率变换。

4. 查找表(LUT):FPGA内部还可以使用查找表来实现频率变换。

查找表可以根据输入的地址选择相应的输出值,从而实现不同的频率变换。

在FPGA开发工具中,可以通过配置查找表的参数来改变输出值,从而实现频率变换。

5. 硬件描述语言:在FPGA开发过程中,可以使用硬件描述语言(如Verilog或VHDL)来实现频率变换的逻辑电路。

通过编写相应的代码,可

以实现不同的频率变换功能。

在FPGA开发工具中,将代码进行编译和综合后生成相应的配置文件,然后将配置文件下载到FPGA中即可实现频率变换。

以上是FPGA实现频率变换的几种常见方法,具体实现方式可以根据实际需求和开发环境进行选择。

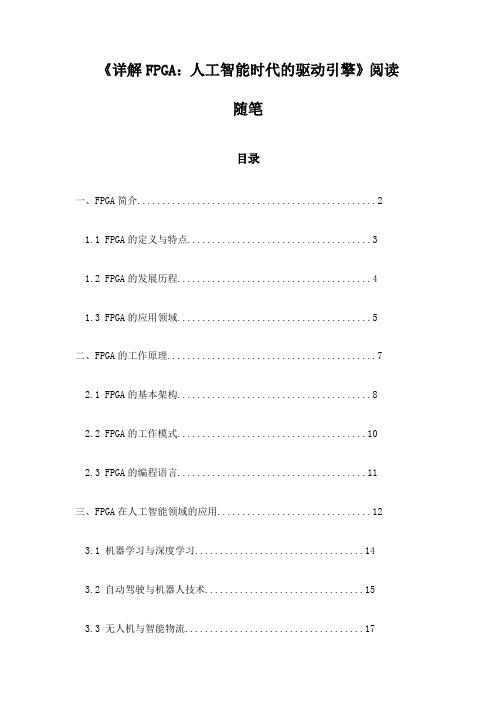

《详解FPGA:人工智能时代的驱动引擎》札记

《详解FPGA:人工智能时代的驱动引擎》阅读随笔目录一、FPGA简介 (2)1.1 FPGA的定义与特点 (3)1.2 FPGA的发展历程 (4)1.3 FPGA的应用领域 (5)二、FPGA的工作原理 (7)2.1 FPGA的基本架构 (8)2.2 FPGA的工作模式 (10)2.3 FPGA的编程语言 (11)三、FPGA在人工智能领域的应用 (12)3.1 机器学习与深度学习 (14)3.2 自动驾驶与机器人技术 (15)3.3 无人机与智能物流 (17)3.4 医疗诊断与生物信息学 (18)3.5 其他领域的FPGA应用 (20)四、FPGA的设计与优化 (22)4.1 FPGA设计流程 (23)4.2 硬件描述语言 (25)4.3 设计优化策略 (26)4.4 性能评估与测试 (28)五、FPGA的未来发展趋势 (29)5.1 技术创新与突破 (30)5.2 行业合作与生态系统建设 (32)5.3 应对挑战与机遇 (33)六、结论 (35)6.1 FPGA在人工智能时代的重要性 (36)6.2 未来展望与期许 (37)一、FPGA简介FPGA(现场可编程门阵列)是一种集成电路芯片,它允许设计师在硬件层面上实现可编程的解决方案。

与传统的专用硬件电路相比,FPGA具有更高的灵活性和可扩展性,因此在人工智能、数据中心、通信等领域得到了广泛应用。

FPGA的核心特点是可编程性。

它可以根据需要动态地重新配置内部逻辑单元,从而实现各种功能。

这种可编程性使得FPGA在应对不断变化的应用需求时具有很高的效率。

FPGA还具备低功耗、高性能、高可靠性等优点。

FPGA的发展历程可以追溯到20世纪80年代,当时Xilinx公司推出了世界上第一款商用FPGA产品。

随着技术的不断发展,FPGA的性能不断提高,功能也越来越丰富。

FPGA已经发展到了第四代,即UltraScale系列,其最大容量可达140亿个逻辑单元,支持多种编程语言和开发工具,为人工智能时代的应用提供了强大的支持。

FFT的FPGA实现

fft的fpga实现1.引言DFT及其快速算法FFT是信号处理领域的核心组成部分。

FFT算法多种多样,按数据组合方式不同一般分时域和频域,按数据抽取方式的不同又可分为基2,基4等。

各算法的优缺点视不同的制约因素而不同。

FFT的实现方法也多种多样,可以用软件实现,也可以用硬件实现,用软件在PC机或工作站上实现则计算速度很慢。

一般多结合具体系统用硬件实现。

例如用单片机或DSP实现。

但是速度仍然很慢,难以与快速的A/D器件匹配。

在雷达信号处理领域主要追求的目标是速度,即实时性的要求非常高。

针对这种快速信号处理的要求及FPGA器件的特点,本文采用的是一种基2固定几何结构的FFT算法。

采用的是Altera公司推出的最新器件Stratix来做硬件仿真。

Stratix器件是一款采用高性能结构体系的PLD器件。

它结合了强大内核性能,大存储带宽,数字信号处理(DSP)功能,高速I/O性能和模块化设计与一体的PLD。

其内嵌的DSP模块具有很高的乘法运算速度。

在用VHDL编程时可以用MegaWizard的方法指定用DSP模块生成乘法器,用这种乘法器来做蝶形,用多个蝶形来构成FFT运算级,通过循环即可实现FFT核心运算的并行化。

用Altera公司的Quartus软件做逻辑分析和波形分析。

Quartus软件具有很强的硬件仿真和逻辑分析功能,它可将用VHDL编写的硬件描述综合到FPGA中。

2.算法介绍为了说明问题的方便,下面以基2,八点FFT为例加以说明。

传统的基2变几何结构算法如下(图一):箭头上的数字代表旋转因子中的k。

图中输入采用的是按码位颠倒的顺序排放的。

输出是自然顺序。

这种结构的特点是每个蝶形的输出数据仍然放在原来的输入的数据存储单元内,这样只需要2N个存储单元(FFT中的数据是复数形式,每点需要两个单元存储)。

其缺点是不同级的同一位置蝶形的输入数据的寻址不固定,难以实现循环控制。

用FPGA编程时难以并行实现,数据处理速度慢。

fpga课程设计+综合实验方案+主要知识点

FPGA 课程设计一、实验名称。

基于FPGA技术的交通灯控制系统设计二、实验仪器。

试验箱电脑数据线三、设计目的和设计要求四、电路工作原理及设计方案五、软件工作原理与调试分频模块的设计与仿真图六、心得体会FPGA综合实验安排一、FPGA综合实验选题仔细阅读下列各设计题目的说明和设计要求,每位同学按照指定的题目完成设计。

要求通过综合性实验,进一步理解和掌握硬件描述语言(VHDL或Verilog)和TOP-DOWN的设计流程,提高对实际项目的分析和设计能力,体会FPGA项目开发的过程,熟悉实验报告的编写规范。

二、总体要求1.选定题目后,要严格按照题目要求独立完成,不可随意更改题目。

2.完成总体方案及详细方案设计,提交《设计方案》;3.FPGA课设所选题目要求采用自顶向下的全正向设计方法,并选用Verilog_HDL、VHDL语言或原理图为设计输入工具。

4.要求电路的功能仿真和FPGA后仿真验证全部正确通过,且功能仿真和后仿真建议采用第三方验证工具(Modelsim6.0),综合与布局布线工具为:Quartus II。

5.完成验证方案设计,采用第三方工具完成后仿真,提交后仿真结果报告;;6.课程设计的具体评定标准:7.完成功能和引脚定义,提交功能引脚定义图;8.完成设计电路的FPGA综合及布局布线,提交综合及布局布线报告和引脚分布报告;9.选择任意一种设计输入方式,实现项目的总体设计及各个模块的设计;10.基于FPGA开发板完成设计电路的功能测试验证,提交硬件测试结果报告;11.实际设计要能够运行,并进行验收,须经过指导老师的验收后方可通过12.设计报告要符合规范。

三、实验成绩评定实验的成绩评定以课设出勤情况(20%),选定课题的难易度、完成情况及验收情况(40%)和设计报告(40%)为依据综合评分。

要求对于选定的题目,最后完成的程序在FPGA开发平台上能够运行,而且要完成基本的功能,否则视为没有完成该题目,设计报告中只有设计代码,没有设计框图及仿真文件视为不合格。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘

要:随着计算机绘 图规模 的需要 , 借助辅助硬件资 源, 来提 高图形处理单元 ( U) GP 处理速度 的需求 越来越普遍 。

结合计算 机绘 图及 F G 的特点 , PA 本文 采用 T p o n的方法 对 G U 几何变换 单元部分 进行 了 F G o- w D P P A设 计实现 。 所有结构模块均实现 了 R L级建模 , T 并对其 中较复杂 的矩阵构造单元和矩阵乘法器模块给 出了详细的描述 。最后 借 助 电子设计 自动化工具 ( D X 整个模块进行 了验证综合 , E A) ̄ 结果 表明 , 符合 设计需求 , 该方案能很好 地完成几何 变换

S n Da h n Gu u c eg o Li

( e a t n f lcr ncS i c D p rme t eto i ce e& T c n l y , TC,Hee 3 0 6 oE n e h oo g US fi 0 2 ) 2

Ab ta t sr c :W i h e d o o u e r p is h e u r me t fu ig a ss a t a d r O e h n et e e f in y o t t e n e fc mp t rg a h c 。t er q i h e n sn s it n r wa e t n a c h fi e c f o h c

( DA) tos E o l.Th e utpo ei o dp ro ma c n w e o rec s , n shg e t r q e c a e 2 M Hz ers l r v sg o e fr n ea dl rs uc o t a di ih s e u n yc ng t1 O t o t f .

Ke wo d :g o er r n f r a i n LUT; ma rx mu t l r s s o i r a y r s e m tyta so m t ; o t i li i ; y t l a r y p e c

0 引

言

针对 几何变换 实时性 的要 求 , 文提 出如下 的 F G 本 P A 实 现方案 , 体框 图流程 如图 1 总 。

GPU eo e r n r o ua .Co iigt efa u e fc mp trg a hc n GA,t i p p rp ee t h b c m smo ea dmo ep p lr mbnn h e t rso o ue rp i dFP s hs a e rs n st e To - w to oo y d sg n mp e n ain o e mer r n f r t n i U. Al sr cu a d ls a e pD n meh d lg e in a d i lme tt fg o ty ta so mai n GP o o o l tu t r lmo ue r

d n t o e wih RTL mo es n h e d ls t eM a rx B l e d l n h a rx M u t l r d l ,a d t ek y mo u e h t i ui rmo u ea d t eM t i l p i d l r i u s d d i e mo ue a e d s s e c i e al Th nd ti . e RTL mo e f t e a c i c u e h s as e n s n h s z d wih t e ad o l c r n c d sg u o t d 1o h r h t t r a lo b e y t e i t h i f ee t o i e in a t ma i e e c

维普资讯

电

子

测

量

技

术

第3 O卷 第 1 期 2 20 0 7年 1 月 2

EL ECTRONI M EAS C UREM匮NT TE CHNOL OGY

几 何 变 换 单 元 的 设 计 及 其 F GA 实 现 P

孙大 成 郭 立

合肥 202) 3 06 ( 中国科 学技术 大学电子科 学与技 术 系

功能 , 资源耗 费低 , 最高工作频率可达 1 0MHz 2 。 关键词 :几何变换 ;查找表 ;矩阵乘 法 ;脉 动阵列 中图分类号 :T 3 2 P 3 文献标识码 :A

De in fg o er r nso m a in n ta t sg o e m ty ta f r to u i nd isFPGA m plm e t to i e n a in

几何变换 是 图形 处 理单 元 ( P 算 法 实现 中 的重 要 G U)

一

环 , 运算速 度 直 接 关 系 到 G U 的运 算 效 率 。人 们 一 其 P

影模 矩阵构造单  ̄( tx ul 0 : rB ie Ma i d

直在 寻求各种 方法来 加快 算 法速 度 , 通常 是使 用 更快 速 的 处理 器 、 利用 并 行性 和 专 门 的硬 件 结构 等 , 着数 字 电路 随 技 术 的发展 , 是 在 F G 尤其 P A方 面 的快 速 进 步 , 我 们 可 让 以尝试 另外一 条途径 。 本 文 的工 作就 是对 几何 变 换部 分 , 采用 T pD w o- o n的 方 法对 G U 几何 变 换部 分 进 行 了 F G 设 计 实现 , 为 P PA 作