×××芯片用户手册

芯驰科技芯片手册

芯驰科技芯片手册第一章:产品介绍芯驰科技芯片手册是为了向用户提供关于芯驰科技生产的芯片的详细信息和操作指南。

本手册主要涵盖了芯片的功能、性能参数、使用说明、安装和连接等方面的内容,以帮助用户更好地了解和使用芯驰科技芯片。

第二章:产品特点1.高性能:芯驰科技芯片采用先进的制造工艺,具有出色的计算能力和能效比,能够满足用户的高性能需求。

2.多功能:芯驰科技芯片集成了多种功能,如图像处理、音频处理、数据通信等,可以满足不同用户的多样化需求。

3.低功耗:芯驰科技芯片采用低功耗设计,能够有效降低能耗,延长电池寿命,为用户提供更持久的使用时间。

4.高可靠性:芯驰科技芯片经过严格的测试和质量控制流程,具有优秀的稳定性和可靠性,在各种复杂环境下都能正常运行。

第三章:技术参数1.处理器类型:芯驰科技芯片采用先进的处理器技术,可提供高速、高效的计算能力。

2.内存容量:芯驰科技芯片内置大容量内存,能够满足用户对存储空间的需求。

3.电源要求:芯驰科技芯片采用标准的电源接口,支持多种电源输入方式,可适应不同的电源环境。

4.尺寸和重量:芯驰科技芯片体积小,重量轻,便于携带和安装。

第四章:使用说明1.芯片安装:用户应按照芯驰科技芯片手册中的指导,正确安装芯片到目标设备中,并确保连接牢固。

2.芯片连接:用户应按照芯驰科技芯片手册中的说明,正确连接芯片与其他设备或接口,以确保正常的数据传输和通信。

3.芯片操作:用户应详细阅读芯驰科技芯片手册中的操作指南,并按照指南进行相应的操作,以达到所需的功能和效果。

4.注意事项:芯驰科技芯片手册中还提供了一些注意事项,用户在使用芯片时应注意这些事项,并按照要求进行操作,以确保使用安全和稳定性。

第五章:常见问题解答芯驰科技芯片手册中提供了一些常见问题和解答,用户在使用芯片时遇到问题可以参考这些解答,以帮助解决问题。

结语芯驰科技芯片手册是用户了解和使用芯驰科技芯片的重要参考资料。

本手册详细介绍了芯驰科技芯片的特点、技术参数、使用说明和常见问题解答等内容,能够帮助用户更好地了解和使用芯驰科技芯片。

v3s芯片手册

v3s芯片手册一、简介v3s芯片是一款高性能的处理器芯片,广泛应用于智能家居、物联网、工业控制等领域。

本手册旨在为用户提供v3s芯片的使用指南,帮助用户充分了解芯片功能,正确使用芯片,以达到最佳的应用效果。

二、芯片概述1.芯片结构:v3s芯片采用先进的处理器架构,拥有强大的处理能力和丰富的外设接口。

2.内存配置:芯片内部配备高速缓存内存,支持实时数据交换和处理。

3.通信接口:芯片支持多种通信协议,包括蓝牙、Wi-Fi、Zigbee 等,可实现高速数据传输和远距离通信。

4.电源管理:芯片采用高效电源管理技术,支持多种电源输入和输出模式。

三、使用步骤1.硬件连接:将v3s芯片连接至相关设备,确保连接稳定。

2.软件安装:下载并安装配套的软件开发工具包(SDK),以便进行芯片编程和调试。

3.芯片初始化:对芯片进行初始化设置,包括系统时钟、外设接口等参数。

4.程序编写:使用配套的软件开发工具包进行程序编写,实现所需功能。

5.调试与测试:对程序进行调试和测试,确保芯片正常运行。

四、编程接口v3s芯片提供了丰富的编程接口,方便用户进行程序开发。

以下是一些常用的编程接口:1.GPIO接口:用于控制芯片的外设引脚。

2.UART接口:用于串口通信。

3.I2C接口:用于实现芯片之间的数据交换。

4.SPI接口:用于高速数据传输。

5.PWM接口:用于生成指定占空比的脉冲信号。

五、常见问题及解决方法1.问题:芯片无法正常启动怎么办?解决方法:检查电源是否正常,芯片与外部设备的连接是否稳定,以及相关软件是否正确安装。

2.问题:程序运行出现异常怎么办?解决方法:检查程序代码是否正确,以及相关外设接口是否正常工作。

可以查阅相关技术文档或寻求专业人士帮助。

3.问题:芯片发热严重怎么办?解决方法:检查电源管理是否合理,是否过度使用芯片,以及是否正确散热。

可以尝试调整电源参数或改善散热条件。

六、注意事项1.确保芯片在干燥、无尘的环境中使用,避免潮湿和灰尘进入芯片内部。

宇凡微电子YF153J 8位单片机用户手册说明书

深圳宇凡微电子有限公司8-Bit Single-Chip Microcontrollers YF153J用户手册(Ver1.1)2019年12月修订目录1芯片简介 (3)1.1功能特性 (3)1.2引脚分配 (4)1.3引脚描述 (5)1.4系统框图 (6)2存储器结构 (7)2.1程序存储器区 (7)2.2数据存储区 (8)3寄存器配置 (9)3.1操作寄存器 (9)3.1.1RPAGE~R0(间接地址存储器) (9)3.1.2RPAGE~R1(TCC定时计数器) (9)3.1.3RPAGE~R2(PC程序计数器) (9)3.1.4RPAGE~R3(STATUS状态寄存器) (10)3.1.5RPAGE~R4(FSR RAM选择寄存器) (11)3.1.6RPAGE~R5(P0RT5数据寄存器) (11)3.1.7RPAGE~R6(P0RT6数据寄存器) (12)3.1.8RPAGE~R7(LVD控制寄存器) (12)3.1.9RPAGE~R8(T1控制寄存器) (12)3.1.10RPAGE~R9(PWM周期寄存器) (13)3.1.11RPAGE~RA(PWM1占空比寄存器) (13)3.1.12RPAGE~RB(PWM2占空比寄存器) (13)3.1.13RPAGE~RC(PWM3占空比寄存器) (13)3.1.14RPAGE~RD(P6端口中断唤醒使能寄存器) (14)3.1.15RPAGE~RE(CPU模式控制寄存器) (14)3.1.16RPAGE~RF(中断标志寄存器) (15)3.2控制寄存器 (16)3.2.1CONT(控制寄存器) (17)3.2.2IOPAGE~IOC5(P5端口方向控制寄存器) (18)3.2.3IOPAGE~IOC6(P6端口方向控制寄存器) (18)3.2.4IOPAGE~IOC9(端口上下拉控制寄存器) (18)3.2.5IOPAGE~IOCB(端口下拉控制寄存器) (18)3.2.6IOPAGE~IOCD(P6端口上拉控制寄存器) (19)3.2.7IOPAGE~IOCE(WDT控制寄存器) (19)3.2.8IOPAGF~IOCF(WDT唤醒及中断使能控制寄存器) (20)3.3重要说明 (20)4封装类型 (21)5封装尺寸 (22)5.114PIN封装尺寸 (22)5.28PIN封装尺寸 (24)1芯片简介1.1功能特性CPU配置●1K×14-Bit OTP ROM●48×8-Bit SRAM●5级堆栈空间●28级可编程电压检测(LVD)2.0V~4.7V,0.1V/级●8级可编程电压复位(LVR)1.2V,1.6V,1.8V,2.4V2.7V,3.3V,3.6V,3.9V●工作电流小于2mA(4MHz/5V)●工作电流30μA(32KHz/3V)●休眠电流小于1μA(休眠模式)I/O配置●2组双向IO端口:P5,P6●12个I/O引脚●唤醒端口:P6口●12个可编程上拉I/O引脚●11个可编程下拉I/O引脚●端口驱动可增强●P63(复位引脚)可配置上拉和输出●外部电压检测:P63●外部中断:P60工作电压●工作电压范围:1.8V~5.5V(0℃-70℃)2.3V~5.5V(-40℃-85℃)常温(25℃)工作电压可低至1.5V●工作温度范围:工作温度-40℃-85℃工作频率范围●外部晶振HXT,LXT●外部晶振内置电容:Disable、7PF、9PF、12.5PF●内置IRC振荡电路:8MHz/1MHz●时钟周期分频选择:2Clock,4Clock,8Clock16Clock,32Clock外围模块●8Bit实时时钟/计数器●3路共周期8Bit脉宽调制器PWM 中断源●TCC溢出中断●外部中断●输入端口状态改变产生中断●T1/PWM周期溢出中断特性●可编程WDT定时器4.5ms、18ms、72ms、288ms●内置RC振荡器供电:VDD、LDO2.1V封装类型●YF153J-DIP14;●YF153J-SOP14;●YF153J-DIP8;●YF153J-SOP8;YF153J-14PIN脚位图YF153J-8PIN脚位图序号管脚名I/O功能描述P50P50I/O(上/下拉)GPIO,可编程上下拉、高驱动P51P51I/O(上/下拉)GPIO,可编程上下拉、高驱动P52P52I/O(上/下拉)GPIO,可编程上下拉、高驱动P53P53I/O(上/下拉)GPIO,可编程上下拉、高驱动P60P60I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒EXINT I(SMT)外部中断输入端口PWM3O PWM3输出P61P61I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒PWM20PWM2输出P62P62I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒TCC I外部TCC信号源输入脚PWM10PWM1输出P63P63I/O(上拉)GPIO,可编程上拉、端口唤醒RST I(SMT)复位引脚EXVDET I(ANALOG)电压检测引脚P64P64I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒P65P65I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒P66P66I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒P67P67I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒VDD--电源VSS--地1.4系统框图2存储器结构2.1程序存储器区2.2数据存储区RPAGE\IOPAGE\Bank数据寄存器区地址R页面寄存器CTLX0页面寄存器0x00R0(间接地址存储器)保留0x01R1(TCC定时计数器)CONT(控制寄存器)0x02R2(PC程序计数器)保留0x03R3(STATUS状态寄存器)保留0x04FSR RAM选择寄存器保留0x05P0RT5数据寄存器P5方向控制寄存器0x06P0RT6数据寄存器P6方向控制寄存器0x07LVD控制寄存器保留0x08PWM控制寄存器保留0x09PWM周期寄存器端口上下拉控制寄存器0x0A PWM1占空比寄存器保留0x0B PWM2占空比寄存器端口下拉控制寄存器0x0C PWM3占空比寄存器保留0x0D输入状态变化中断使能控制器端口上拉控制寄存器0x0E CPU模式控制寄存器WDT使能控制寄存器0x0F中断标志寄存器中断使能控制寄存器地址Bank寄存器0x10~通用寄存器0x3F3寄存器配置3.1操作寄存器3.1.1RPAGE~R0(间接地址存储器)Bit7Bit6Bit5Bit4Bit3Bit2Bit1Bit0RIND<7:0>间接寻址寄存器并不是一个实际存在的寄存器,它的主要功能是作为间接寻址的指针。

vca821芯片手册

vca821芯片手册VCA821芯片是一款基于数字信号处理技术的音频编解码芯片,是当前音频处理领域中性能最为出色的一款。

它在音频编解码、音效处理、语音识别等方面具有出众的表现,吸引了众多音频处理领域的专业人士的关注和使用。

在使用VCA821芯片之前,首先需要仔细阅读其手册。

手册提供了关于芯片设计、使用、测试等方面的详细信息,帮助用户更好地了解和使用该芯片。

下面将从以下几个方面介绍VCA821芯片手册的内容。

一、芯片综述VCA821芯片手册首先对该芯片的主要特性和应用领域进行了简要介绍。

从芯片外观、功能特点、性能指标、接口等多个方面,对该芯片的整体情况进行了概括,方便用户快速了解其相关信息。

二、引脚功能VCA821芯片手册详细介绍了该芯片所有引脚的功能和定义。

所有引脚的编号及其功能被详细标注在引脚图上,方便用户理解和应用。

三、电气特性VCA821芯片手册还包含了该芯片的电气特性参数表,其中包括了直流电气特性、交流电气特性、噪声特性等多个方面的指标。

这些指标非常重要,在芯片选择、设计及测试过程中起着至关重要的作用。

四、应用电路VCA821芯片手册提供了多个典型应用电路,这些应用电路涵盖了芯片在不同领域内的应用场景。

这些应用电路不仅能够为用户提供可靠的参考方案,并且可以快速启动芯片的设计,提升芯片的应用效率。

五、使用说明VCA821芯片手册有一整套使用说明,详细介绍了芯片的使用方法和注意事项。

这些说明提供了从PCB设计、软件编程到调试的全面指导,旨在使用户能够快速上手,合理采用芯片实现所需功能。

总结来说,VCA821芯片手册提供的内容非常丰富,包含了该芯片的各方面信息,可以为用户的芯片设计、应用和测试提供全面的帮助,是一份不可多得的宝贵参考资料。

USB2XXX_Mamu使用说明

USB2XXX系列转换芯片用户手册V0.1CUSBIO TECH.目录USB2XXX系列转换芯片用户手册 (1)1、 驱动安装 (3)2、 Demo软件使用说明 (8)3、 上位机Windows API使用说明 (20)4、 使用过程中的注意事项 (21)5、 常见问题问答 (22)1、驱动安装1、1、下载驱动文件从USBIO公司网站的“在线下载”栏里下载最新的驱动程序。

连接地址是:/cn/down.htm。

对于USB2ISP、USB2I2C或USB2SPI,选择相应的“开发大礼包”下载。

解压缩到本地机器的硬盘里,待用。

USB2I2C和USB2SPI是USB2ISP的功能简化版本,可以看作是USB2ISP的子集。

USB2I2C实现USB转换I2C接口;USB2SPI实现USB转换SPI接口;USB2ISP实现USB转换SPI和I2C接口,同时还提供EPP或MEM并口,也可以当成是GPIO口来使用,具体请参考USB2ISP的数据手册。

USB2I2C(SOP28封装)、USB2SPI和USB2ISP 管脚完全兼容,所以USB2I2C和USB2SPI的相关设计也可以参考USB2ISP的数据手册。

本手册以USB2ISP_DEV开发板为例,说明USB2XXX系列转换芯片的功能。

1、2、插入USB2ISP_DEV开发板将USB2ISP_DEV开发板插入到电脑主板USB接口。

当USB2ISP_DEV开发板向外部供电时,最好插入PC机背部的主板USB口。

1、3、W indows提示发现新硬件插入USB2ISP_DEV开发板后Windows提示发现新硬件。

1、4、提示安装驱动选择【从列表或指定位置安装(高级)】选项,然后单击【下一步】按钮。

1、5、指定驱动文件的路径此处需要指定驱动文件的路径。

驱动文件就是从网站上下载解压缩后的文件。

注意:USB2ISP、USB2I2C或USB2SPI芯片2007年11月之前的产品选择DRIVER 文件夹内的驱动文件安装。

ast2620芯片手册_范文模板

ast2620芯片手册范文模板1. 引言1.1 概述本文主要介绍了AST2620芯片的手册内容和相关信息。

AST2620芯片是一款应用广泛的高性能低功耗芯片,具有出色的处理能力和多种接口功能。

该手册旨在为用户提供详细的技术规格和使用指南,帮助用户充分了解和应用AST2620芯片。

1.2 文章结构本文将按照以下四个部分来组织内容:AST2620芯片的特性、应用领域、技术规格以及结论。

在第二部分中,我们将介绍AST2620芯片作为一个整体的特性和优势。

然后,在第三部分中,我们将探讨AST2620芯片在不同领域的应用,包括工业控制、物联网和智能家居等方面。

接下来,在第四部分中,我们将详细介绍AST2620芯片的技术规格,包括处理器架构与核心数目、内存和存储容量以及接口和通信功能等方面。

最后,在结论部分,我们将总结AST2620芯片的优势和适用场景,并展望它在未来的发展前景,并提出对手册完善与扩展方面的建议。

1.3 目的本文的目的在于提供一份详细并且易于理解的AST2620芯片手册,使读者能够全面了解AST2620芯片的特性、应用领域和技术规格。

通过阅读本手册,读者将对AST2620芯片有更深入的认识,并能够更好地利用它的优势和功能。

同时,我们也希望通过展望其未来发展前景和提出建议,为用户提供更多有益的信息和参考。

2. ast2620芯片的特性:2.1 芯片介绍:ast2620芯片是一款专为嵌入式系统设计的高性能低功耗芯片。

它采用先进的制造工艺和优化的架构,具有出色的处理能力和卓越的稳定性。

它内置了多个处理器核心以及丰富的外设接口,可以满足各种复杂应用场景的需求。

2.2 高性能特性:ast2620芯片具有出色的高性能特性,其中包括:- 多核处理器: ast2620芯片内部集成了多个处理器核心,每个核心都具有独立运算和控制能力。

这样可以实现多任务并行执行,提升系统整体的处理效率。

- 高频率运行: ast2620芯片支持高频率运行,可以快速响应操作指令并进行大规模数据处理。

HM6107芯片用户手册说明书

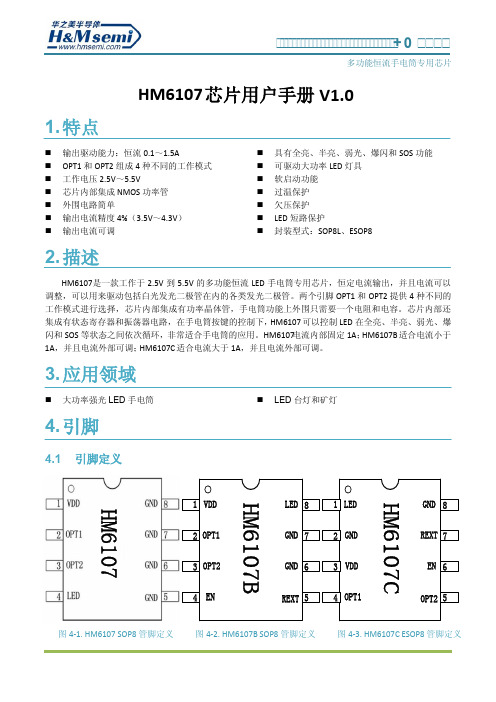

图 4-1. HM6107 SOP8 管脚定义

图 4-2. HM6107B SOP8 管脚定义

图 4-3. HM6107C ESOP8 管脚定义

4.2 SOP8 引脚描述

+0

多功能恒流手电筒专用芯片

引脚序号 引脚名称

I/O

1

VDD

O 电源

10. 封装尺寸

10.1 SOP8 封装尺寸

+0

多功能恒流手电筒专用芯片

I 模式选择 1

5

OPT2

I 模式选择 2

6

EN

I 使能端,低电平正常工作

7

REXT

I 外接电阻

8

GND

O地

注:OPTI 和 OPT2 需要接电源或者接地,EN 需要外接电源或者地。

描述

5. 结构框图

VDD 1 电源检测

+0

多功能恒流手电筒专用芯片

REF

OTP

OPT1 2 OPT2 3

EN 4 REXT 5

数字控制 模式选择

振荡器

状态控制

恒流 驱动

8 LED

7 gnd 6 gnd

6. 典型应用电路

图 5-1. HM6107结构框图

3.7V

R1 47

C1 4.7uF

1 VDD 2 OPT1 3 OPT2 4 LED

HM6107

gnd 8 gnd 7 gnd 6 gnd 5

3. 应用领域

大功率强光 LED 手电筒

4. 引脚

LED 台灯和矿灯

4.1 引脚定义

HM6107C HM6107B

HM6107

1 VDD 2 OPT1 3 OPT2 4 EN

S698PM 用户手册说明书

高性能32位多核处理器SOC芯片S698PM用户手册(Ver:4.8)珠海欧比特宇航科技股份有限公司地址: 广东省珠海市唐家东岸白沙路1号欧比特科技园邮编: 519080 电话*************传真*************网址: 修改记录版权声明珠海欧比特宇航科技股份有限公司拥有此文件的版权,并有权将其作为保密资料处理。

本文件包含由版权法保护的专有资料,版权所有,未经珠海欧比特宇航科技股份有限公司的书面同意不得将本文件的任何部分进行照相、复制、公开、转载或以其他方式散发给第三方,否则,必将追究其法律责任。

免责声明本文档仅提供阶段性信息,所含内容可根据产品的实际情况随时更新,恕不另行通知。

如因文档使用不当造成的直接或间接损失,珠海欧比特宇航科技股份有限公司不承担任何责任。

珠海欧比特宇航科技股份有限公司ZHUHAI ORBITA AEROSPACE SCIENCE & TECHNOLOGY CO. , LTD地址(Addr):广东省珠海市唐家东岸白沙路1号欧比特科技园Orbita Tech Park, 1 Baisha Road, Tangjia Dong,an, Zhuhai, Guangdong, China 邮编:519080电话(Tel):+86 756-3391979传真(Fax):+86 756-3391980网址(web):目录目录 (I)表目录 (IX)图目录 (1)1.概述 (1)1.1产品简介 (1)1.2结构组成 (2)1.3主要特征 (3)1.4产品订货信息 (5)2.芯片初始化 (6)2.1上电或复位初始化过程 (6)2.2上电或复位需初始化参数配置 (8)2.3多核软件程序启动过程 (10)3.时钟信号发生模块 (10)3.1片内时钟域 (10)3.2时钟信号发生模块 (12)4.处理器核心 (15)4.1整型单元IU (15)4.1.1 主要特性 (15)4.1.2 指令 (16)4.1.3 寄存器堆(Register File) (19)4.1.4 专用寄存器 (22)4.1.5 异常(Exception) (27)4.1.6 复位操作 (29)4.1.7 休眠模式(Power-down) (29)4.1.8 多核处理器支持 (30)4.2浮点单元(FPU)和浮点控制器(FPC) (30)4.2.1 FPU概述 (30)4.2.2 FPU功能描述 (30)4.2.3 FPC概述 (35)4.2.4 FPC的浮点寄存器文件(Floating-Point register file) (35)4.2.5 SP ARC浮点状态寄存器(FSR) (35)4.2.6 浮点异常和浮点延迟队列 (36)4.3一级缓存(L1C ACHE) (37)4.3.1 指令缓存(instration cache) (37)4.3.2 数据缓存(data cache) (38)4.3.3 缓存寄存器定义 (39)4.4存储器管理单元(MMU) (40)4.4.1 MMU控制寄存器 (41)4.4.2 MMU上下文指针寄存器 (42)4.4.3 MMU上下文寄存器 (42)4.4.4 MMU错误状态寄存器 (42)4.4.5 MMU错误地址寄存器 (43)4.4.6 MMU Flush操作 (43)4.4.7 MMU Bypass操作 (43)珠海欧比特宇航科技股份有限公司I高性能32位多核处理器SOC 芯片-S698PM 用户手册珠海欧比特宇航科技股份有限公司 II 5. 二级缓存(L2 CACHE ) (44)5.1 读操作 (44)5.2 写操作 (45)5.3 F LUSH 操作 (45)5.4 诊断接口 (45)5.5 地址映射 (46)5.6 寄存器定义 (47)5.6.1 L2C 控制寄存器 (47)5.6.2 L2C 状态寄存器 (48)5.6.3 L2C flush 寄存器 (48)5.6.4 L2C flush 寄存器 (49)5.6.5 L2C 错误状态控制寄存器 (50)5.6.6 L2C 错误地址寄存器 (51)5.6.7 L2C TAG 位校验位寄存器 (51)5.6.8 L2C 数据校验位寄存器 (51)5.6.9 L2C scrub 控制状态寄存器 (51)5.6.10 L2C scrub 延迟寄存器 (52)5.6.11 L2C 错误注入寄存器 (52)5.6.12 L2C 存储器类型范围寄存器(L2CMTRR) (52)6. 地址空间分配 (53)6.1 内部地址空间分配 (53)6.2 APB 总线地址分配 (53)6.3 AHB 总线状态寄存器 (54)6.3.1 寄存器地址分配 (54)6.3.2 AHB 状态寄存器 (55)6.3.3 AHB 出错地址寄存器 (55)7. 中断控制器 (55)7.1 中断优先级 (56)7.2 中断信号流程及中断处理过程 (56)7.3 多处理器状态监视 (57)7.4 中断分配表 (57)7.5 外部中断扩展 (58)7.6 中断寄存器 (59)7.6.1 中断级别寄存器 (60)7.6.2 中断悬挂寄存器 (60)7.6.3 中断清除寄存器 (60)7.6.4 多处理器状态寄存器 (60)7.6.5 中断广播寄存器 (61)7.6.6 中断屏蔽寄存器 (61)7.6.7 处理器中断强制寄存器 (62)7.6.8 扩展中断响应寄存器 (62)8. 通用定时器 (62)8.1 通用定时器工作原理 (63)8.2 通用定时器寄存器 (66)8.2.1 预分频器计数值寄存器 (67)8.2.2 预分频器重载计数值寄存器 (67)8.2.3 通用定时器配置寄存器 (67)8.2.4 通用定时器定时值寄存器 (67)8.2.5 通用定时器重载值寄存器 (68)8.2.6 通用定时器控制寄存器 (68)9.锁存定时器 (69)9.1锁存定时器工作原理 (69)9.2锁存定时器寄存器 (71)9.2.1 预分频器计数值寄存器 (71)9.2.2 预分频器重载计数值寄存器 (71)9.2.3 锁存定时器配置寄存器 (72)9.2.4 锁存触发中断选择寄存器 (72)9.2.5 锁存定时器定时值寄存器 (72)9.2.6 锁存定时器重载值寄存器 (73)9.2.7 锁存定时器控制寄存器 (73)9.2.8 锁存定时器锁存值寄存器 (73)10.通用输入输出接口GPIO (74)10.1GPIO的工作原理 (74)10.2GPIO寄存器 (75)10.2.1 GPIO数据输入寄存器 (76)10.2.2 GPIO数据输出寄存器 (76)10.2.3 GPIO方向寄存器 (76)10.2.4 GPIO外部中断屏蔽寄存器 (77)10.2.5 GPIO外部中断极性寄存器 (77)10.2.6 GPIO外部中断方式寄存器 (77)10.2.7 GPIO外部中断映射配置寄存器 (77)11.多功能引脚配置寄存器GPREG (78)11.1概述 (78)11.1.1 GPREG通用寄存器 (78)12. I2C总线主控制器 (79)12.1概述 (79)12.2I2C工作原理 (79)12.3I2C-MASTER寄存器 (81)12.3.1 I2C -master时钟预分频(prescale)寄存器 (81)12.3.2 I2C -master控制寄存器 (81)12.3.3 I2C-master发送寄存器 (82)12.3.4 I2C -master接收寄存器 (82)12.3.5 I2C -master命令寄存器 (82)12.3.6 I2C -master状态寄存器 (82)12.3.7 I2C-master动态滤波器寄存器 (83)13.调试支持模块DSU (83)13.1DSU简介 (83)13.2DSU工作原理 (84)13.3DSU寄存器映射表 (85)13.3.1 DSU寄存器映射表 (85)13.3.2 DSU控制寄存器 (86)13.3.3 DSU断点和单步寄存器 (87)13.3.4 DSU调试模式控制寄存器 (87)13.3.5 DSU陷阱寄存器 (87)13.3.6 DSU踪迹缓存时间标识计数器 (87)13.3.7 DSU ASI寄存器 (87)珠海欧比特宇航科技股份有限公司III高性能32位多核处理器SOC 芯片-S698PM 用户手册珠海欧比特宇航科技股份有限公司 IV 13.3.8 DSU 踪迹缓存控制寄存器 (88)13.3.9 DSU 踪迹缓存索引寄存器 (88)13.3.10 DSU 踪迹缓存过滤控制寄存器 (88)13.3.11 DSU 踪迹缓存过滤标识寄存器 (88)13.3.12 DSU 踪迹缓存断点寄存器 (88)13.3.13 DSU 命令踪迹控制寄存器 (89)13.3.14 DSU 命令计数寄存器 (89)13.3.15 AHB 观测控制寄存器 (89)13.3.16 AHB 观测点数据寄存器 (89)14. JTAG 接口控制器 ............................................................................................................................ 90 14.1 概述 ........................................................................................................................................... 90 14.2 功能说明 ................................................................................................................................... 90 14.3 寄存器说明 . (91)14.3.1 JTAG 命令/地址寄存器 (91)14.3.2 JTAG 数据寄存器 (91)15. 外部存储控制器 ............................................................................................................................. 92 15.1 存储控制器简介 ....................................................................................................................... 92 15.2 存储地址分配 ........................................................................................................................... 92 15.3 存储器控制寄存器 . (92)15.3.1 存储器寄存器地址分配 (92)15.3.2 存储器配置寄存器1(MCFG1) (92)15.3.3 存储器配置寄存器2(MCFG2) (93)15.3.4 存储器配置寄存器3(MCFG3) (94)15.3.5 DDR2 FT 配置寄存器 ........................................................................................................ 94 15.4 EDAC 控制器 . (95)15.4.1 概述 (95)15.4.2 EDAC 校验的测试方法 (95)15.4.3 EDAC 的配置 ..................................................................................................................... 96 15.5 PROM 控制器 ........................................................................................................................... 96 15.6 SRAM 控制器 ............................................................................................................................ 99 15.7 I/O 设备 .................................................................................................................................... 102 15.8 DDR2 SDRAM 控制器 .. (103)16. 遥控遥测模块TMTC ...................................................................................................................... 105 16.1 TMTC 简介 .............................................................................................................................. 105 16.2 TM-遥测编码 ........................................................................................................................... 105 16.2.1 TM 简介 ............................................................................................................................ 105 16.2.2 参考资料 .......................................................................................................................... 106 16.2.3 使用介绍 .......................................................................................................................... 107 16.2.4 启动发送 .......................................................................................................................... 108 16.2.5 发送数据后的处理 .......................................................................................................... 108 16.2.6 TM 寄存器描述 ................................................................................................................ 108 16.3 TC-遥控解码 ............................................................................................................................ 113 16.3.1 TC 简介 ............................................................................................................................. 113 16.3.2 参考资料 .......................................................................................................................... 114 16.3.3 数据传送 .......................................................................................................................... 115 16.3.4 命令链接控制字-CLCW .................................................................................................. 115 16.3.5 TC 寄存器描述 .. (115)17. SPACEWIRE 节点控制器 (119)17.1S PACEWIRE总线简介 (119)17.2S PACEWIRE节点控制器主要特征 (120)17.3S PACEWIRE节点控制器实现的功能与工作流程 (121)17.3.1 Spacewire节点控制器实现的功能 (121)17.3.2 Spacewire节点控制器工作流程 (121)17.4S PACEWIRE节点控制器结构 (122)17.5S PACEWIRE节点控制器寄存器描述 (124)17.5.1 Spacewire节点控制器寄存器地址 (124)17.5.2 Spacewire节点控制器寄存器说明 (124)18. SPI总线主控制器 (130)18.1SPI简介 (130)18.2SPI工作原理 (131)18.2.1 SPI传输协议 (131)18.2.2 SPI时钟控制 (132)18.2.3 SPI从模式控制 (133)18.2.4 SPI主模式控制 (133)18.3SPI控制寄存器描述 (133)18.3.1 SPI寄存器地址 (133)18.3.2 SPI性能寄存器 (134)18.3.3 SPI模式控制寄存器 (134)18.3.4 SPI事件寄存器 (136)18.3.5 SPI控制屏蔽寄存器 (136)18.3.6 SPI控制命令寄存器 (137)18.3.7 SPI控制传输寄存器 (137)18.3.8 SPI控制接收寄存器 (137)18.3.9 SPI slave选择寄存器 (137)19. CAN总线控制器 (138)19.1简介 (138)19.2CAN控制器主要特征 (138)19.3结构框图 (139)19.4B ASIC CAN模式寄存器 (140)19.4.1 BasicCAN模式寄存器映射 (140)19.4.2 控制寄存器 (141)19.4.3 命令寄存器 (141)19.4.4 状态寄存器 (142)19.4.5 中断寄存器 (142)19.4.6 发送缓冲寄存器 (142)19.4.7 接收缓冲寄存器 (143)19.4.8 接收过滤寄存器 (143)19.5P ELI CAN模式寄存器 (143)19.5.1 PeliCAN模式寄存器映射 (143)19.5.2 模式寄存器 (144)19.5.3 命令寄存器 (144)19.5.4 状态寄存器 (145)19.5.5 中断寄存器 (145)19.5.6 中断允许寄存器 (145)19.5.7 仲裁丢失捕捉寄存器 (146)19.5.8 错误代码捕捉寄存器 (146)19.5.9 错误报警限制寄存器 (147)19.5.10 接收错误计数器 (147)珠海欧比特宇航科技股份有限公司V高性能32位多核处理器SOC 芯片-S698PM 用户手册珠海欧比特宇航科技股份有限公司 VI 19.5.11 发送错误计数器 ............................................................................................................ 147 19.5.12 发送缓冲寄存器 ............................................................................................................ 147 19.5.13 接收缓冲寄存器 ............................................................................................................ 148 19.5.14 验收过滤寄存器 ............................................................................................................ 149 19.5.15 接收报文计数器 ............................................................................................................ 151 19.6 公共寄存器 ............................................................................................................................. 152 19.6.1 时钟分频寄存器 .............................................................................................................. 152 19.6.2 总线定时0寄存器 .......................................................................................................... 152 19.6.3 总线定时1寄存器 .......................................................................................................... 152 19.7 信号数据帧组成 (153)20. USB 主控制器 ................................................................................................................................ 154 20.1 USB 主控制器(USBHC)简介.................................................................................................. 154 20.2 USB1.1主机控制器架构 ........................................................................................................ 154 20.3 USB 主控制器(USBHC)工作原理 .......................................................................................... 155 20.4 USB(UHC)主控寄存器 ........................................................................................................... 156 20.4.1 UHC I/O 寄存器(0x802A0000 - 0x802A0100) (156)21. 通用串行接口UART ...................................................................................................................... 159 21.1 串口(UART)简介 .................................................................................................................... 159 21.2 串口(UART)工作原理 ............................................................................................................ 160 21.2.1 发送操作 .......................................................................................................................... 160 21.2.2 接收操作 .......................................................................................................................... 160 21.2.3 波特率设置 ...................................................................................................................... 161 21.2.4 自环模式 .......................................................................................................................... 161 21.2.5 FIFO 调试模式 ................................................................................................................. 161 21.2.6 中断机制 .......................................................................................................................... 161 21.3 串口寄存器 ............................................................................................................................. 162 21.3.1 UART 数据寄存器 ........................................................................................................... 162 21.3.2 UART 状态寄存器 ........................................................................................................... 162 21.3.3 UART 控制寄存器 ........................................................................................................... 163 21.3.4 UART 分频寄存器 .. (163)22. 以太网控制器 ............................................................................................................................... 163 22.1 以太网(ETHERNET )简介 ..................................................................................................... 163 22.2 以太网功能介绍 ..................................................................................................................... 164 22.3 发送DMA 通道 ...................................................................................................................... 165 22.3.1 设置发送描述符 .............................................................................................................. 165 22.3.2 启动发送 .......................................................................................................................... 165 22.3.3 发送数据后的处理 .......................................................................................................... 166 22.3.4 设置发送数据 .................................................................................................................. 166 22.4 接收DMA 通道 ...................................................................................................................... 166 22.4.1 设置接收描述符 .............................................................................................................. 166 22.4.2 启动接收 .......................................................................................................................... 167 22.4.3 接收数据后的处理 .......................................................................................................... 167 22.4.4 接收过程中AHB 错误 .................................................................................................... 167 22.4.5 接收MAC 地址 ............................................................................................................... 168 22.5 MDIO 接口 .............................................................................................................................. 168 22.6 以太网调试通信链路(EDCL) ................................................................................................ 168 22.6.1 使用介绍 .......................................................................................................................... 168 22.6.2 EDCL 协议........................................................................................................................ 169 22.7 以太网控制器寄存器 . (169)22.7.1 以太网控制寄存器 (170)22.7.2 以太网状态寄存器 (170)22.7.3 MAC地址MSB (171)22.7.4 MAC地址LSB (171)22.7.5 MDIO寄存器 (171)22.7.6 以太网发送描述符表基地址寄存器 (172)22.7.7 以太网接收描述符表基地址寄存器 (172)22.7.8 以太网EDCL IP寄存器 (172)22.7.9 以太网Hash表MSB寄存器 (172)22.7.10 以太网Hash表MSB寄存器 (172)22.7.11 EDCL MAC地址MSB (173)22.7.12 EDCL MAC地址LSB (173)22.8以太网控制器自动协商机制使用说明 (173)22.8.1 以太网模块的自动协商机制 (173)22.8.2 MDIO ctrl/status register第3位Busy信号的自动置位 (173)22.8.3 如何将Busy信号置为0 (173)22.8.4 以太网外围硬件电路配置 (174)23. DDR2存储器控制器 (174)23.1DDR2SPA简介 (174)23.2DDR2SPA操作 (175)23.2.1 概述 (175)23.2.2 DDR2控制器的初始化 (175)23.2.3 DDR2控制器对大容量存储器的支持 (177)23.2.4 DDR2控制器可配的时需参数 (177)23.2.5 DDR2控制器的刷新操作 (178)23.2.6 DDR2SDRAM控制命令 (178)23.2.7 寄存SDRAM总线 (178)23.2.8 DDR2时钟 (179)23.3DDR2纠错 (179)23.3.1 概述 (179)23.3.2 数据的传送 (179)23.3.3 校验位的访问 (179)23.4DDR2SPA寄存器列表 (180)23.4.1 DDR2SP A控制寄存器 (180)23.4.2 DDR2SP A配置寄存器2 (181)23.4.3 DDR2SP A配置寄存器3 (181)23.4.4 DDR2SP A配置寄存器4 (181)23.4.5 DDR2SP A配置寄存器5 (182)23.4.6 DDR2 FT配置寄存器 (182)23.4.7 DDR2 FT诊断地址寄存器 (182)23.4.8 DDR2 FT诊断纠错位寄存器 (182)23.4.9 DDR2 FT诊断数据寄存器 (183)23.4.10 DDR2 FT边界地址寄存器 (183)24. 1553B总线控制器 (183)24.1主要特征 (183)24.2结构描述 (184)24.3功能描述 (187)24.3.1 总线控制器(BC) (187)24.3.2 远程终端(RT) (187)珠海欧比特宇航科技股份有限公司VII24.3.3 总线监视器(BM) (188)24.4地址空间分配 (188)24.5寄存器定义及描述 (188)24.6模块工作方式描述 (209)24.6.1 BC总线控制器工作方式 (209)24.6.2 RT远程终端工作方式 (211)24.6.3 BM总线监视器工作方式 (217)24.7时序图 (219)24.8应用说明 (219)24.8.1 1Mbps外围接口 (220)24.8.2 10Mbps外围接口 (220)24.8.3 BC总线控制器应用案例 (221)24.8.4 RT远程终端应用案例 (222)24.8.5 BM总线监视器应用案例 (223)25.封装和信号定义 (224)25.1塑封球栅阵列 (224)25.1.1 塑料封装信号引脚定义 (226)25.1.2 塑料封装电源引脚定义 (238)25.2陶封柱栅阵列 (240)25.2.1 陶瓷封装信号引脚定义 (242)25.2.2 陶瓷封装电源引脚定义 (254)26.工作条件及电气特性 (255)表目录表1-1S698PM芯片产品订货信息 (5)表2-1S698PM芯片上电或复位需配置信号 (8)表3-1S698PM芯片内部时钟域 (11)表3-2S698PM芯片时钟相关的引脚信号 (11)表4-1S698PM芯片指令周期 (19)表4-2S698PM芯片的指令可以访问32个通用寄存器 (20)表4-3S698PM芯片陷阱及其优先级分配表 (28)表4-4IU内部部分寄存器复位状态 (29)表4-5FPU操作 (31)表4-6输出与延迟 (33)表4-7N A N S操作 (35)表4-8L1C ACHE寄存器列表 (39)表4-9C ACHE控制寄存器位描述 (39)表4-10IC ACHE配置寄存器位描述 (40)表4-11DC ACHE配置寄存器位描述 (40)表4-12MMU寄存器列表 (41)表4-13MMU控制寄存器 (41)表4-14MMU上下文指针寄存器 (42)表4-15MMU上下文寄存器 (42)表4-16MMU错误状态寄存器 (42)表4-17MMU错误地址寄存器 (43)表5-1S698PM芯片二级缓存相关的地址映射 (46)表5-2L2C控制寄存器 (47)表5-3L2C状态寄存器 (48)表5-4L2C FLUSH寄存器1(MEMORY ADDRESS) (48)表5-5L2C FLUSH寄存器2(SET, INDEX) (49)表5-6L2C错误状态控制寄存器 (50)表5-7错误地址寄存器 (51)表5-8TAG校验位寄存器 (51)表5-9数据校验位寄存器 (51)表5-10L2C SCRUB控制状态寄存器 (51)表5-11L2C SCRUB延迟寄存器 (52)表5-12L2C错误注入寄存器 (52)表5-13L2C存储器类型范围寄存器 (52)表6-1S698PM芯片内部地址空间分配 (53)表6-2S698PM芯片APB总线地址分配 (53)表6-3寄存器地址分配 (54)表6-4AHB状态寄存器(AHB STATUS) (55)表6-5AHB出错地址寄存器(AHB FAIL ADDR) (55)表7-1S698PM芯片的中断列表 (58)表7-2中断控制寄存器列表 (59)表7-3中断级别寄存器ILR (60)表7-4中断悬挂寄存器IPR (60)表7-5中断清除寄存器ICR (60)表7-6多处理器状态寄存器MSR (60)表7-7中断广播寄存器IBR (61)表7-8中断屏蔽寄存器IMR (61)表7-9中断强制寄存器 (62)表7-10扩展中断响应寄存器 (62)表8-1寄存器地址分配 (66)表8-2预分频器计数值寄存器(PRESCALER VALUE) (67)表8-3预分频器重载计数值寄存器(PRESCALER RELOAD VALUE) (67)表8-4通用定时器配置寄存器(TIMER CONFIG) (67)表8-5通用定时器定时值寄存器(TIMER N VALUE) (67)表8-6通用定时器重载值寄存器(TIMER N RELOAD VALUE) (68)表8-7通用定时器控制寄存器(TIMER CONTROL) (68)表9-1锁存定时器寄存器地址分配 (71)表9-2预分频器计数值寄存器(PRESCALER VALUE) (71)表9-3预分频器重载计数值寄存器(PRESCALER RELOAD VALUE) (71)表9-4锁存定时器配置寄存器(LTIMER CONFIG) (72)表9-5锁存触发中断选择寄存器(LTIMER LATCH INT SELECT) (72)表9-6锁存定时器定时值寄存器(COUNTER VALUR) (72)表9-7锁存定时器重载值寄存器(RELOD VALUR) (73)表9-8锁存定时器控制寄存器(LTIMER CONTROL) (73)表9-9锁存定时器的锁存值寄存器(LTIMER LATCH VALUE) (73)表10-1GPIO寄存器地址分配 (75)表10-2GPIO数据输入寄存器(INPUT) (76)表10-3GPIO数据输出寄存器(OUTPUT) (76)表10-4GPIO方向寄存器(DIRECTION) (76)表10-5GPIO外部中断屏蔽寄存器(INT MASK) (77)表10-6GPIO外部中断极性寄存器(INT POLA) (77)表10-7GPIO外部中断方式寄存器(EDGE) (77)表10-8GPIO外部中断映射配置寄存器N(0≤N≤7) (77)表11-1多功能引脚配置GPREG寄存器地址 (78)表11-2多功能引脚配置GPREG寄存器 (78)表12-1I2C-MASTER寄存器 (81)表12-2I2C-MASTER时钟预分频(PRESCALE)寄存器 (81)表12-3I2C-MASTER控制寄存器 (81)表12-4I2C-MASTER发送寄存器 (82)表12-5I2C-MASTER接收寄存器 (82)表12-6I2C-MASTER命令寄存器 (82)表12-7I2C-MASTER状态寄存器 (82)表12-8I2C-MASTER动态滤波器寄存器 (83)表13-1DSU寄存器映射表 (85)表13-2DSU控制寄存器 (86)表13-3DSU断点和单步寄存器 (87)表13-4DSU调试模式控制寄存器 (87)表13-5DSU陷阱寄存器 (87)表13-6DSU踪迹缓存时间标识寄存器 (87)表13-7DSU ASI寄存器 (87)表13-8DSU踪迹缓存控制寄存器 (88)表13-9DSU踪迹缓存索引寄存器 (88)表13-10DSU踪迹缓存过滤控制寄存器 (88)表13-11DSU踪迹缓存过滤标识寄存器 (88)表13-12DSU踪迹缓存断点寄存器 (88)表13-13DSU命令踪迹控制寄存器 (89)表13-14DSU命令计数寄存器 (89)表13-15AHB观测控制寄存器 (89)表13-16AHB观测点数据寄存器 (89)表14-1JTAG命令/地址寄存器 (91)表14-2JTAG数据寄存器 (91)表15-1存储器控制器地址分配表 (92)表15-2EDAC寄存器地址分配列表 (92)表15-3存储器配置寄存器1 (92)表15-4存储器配置寄存器2 (93)表15-5存储器配置寄存器3 (94)表15-6DDR2FT配置寄存器 (94)表16-1TM发送描述符字0 (107)表16-2TM发送描述符字1 (107)表16-3TM寄存器地址 (108)表16-4DMA控制寄存器 (109)表16-5DMA状态寄存器 (109)表16-6DMA长度寄存器 (109)表16-7DMA描述符指针寄存器 (109)表16-8DMA配置寄存器 (110)表16-9DMA修正寄存器 (110)表16-10外部VC控制&状态寄存器 (110)表16-11DMA外部VC描述符指针寄存器 (110)表16-12控制寄存器 (110)表16-13配置寄存器 (110)表16-14物理层寄存器 (111)表16-15编码子层寄存器 (111)表16-16添加同步标志寄存器 (112)表16-17所有帧产生寄存器 (112)表16-18主帧产生寄存器 (112)表16-19空闲帧产生寄存器 (112)表16-20副帧头/插入区寄存器0 (112)表16-21副帧头/插入区寄存器1 (113)表16-22副帧头/插入区寄存器2 (113)表16-23副帧头/插入区寄存器3 (113)表16-24操作控制域寄存器 (113)表16-25TC寄存器地址 (115)表16-26TC全局复位寄存器 (116)表16-27TC全局控制寄存器 (116)表16-28TC物理接口屏蔽寄存器 (116)表16-29TC航天器标识符寄存器 (116)表16-30TC帧接收报告寄存器 (117)表16-31TC命令链接控制字寄存器1 (117)表16-32TC命令链接控制字寄存器2 (117)表16-33TC物理接口寄存器 (118)表16-34TC控制寄存器 (118)表16-35TC状态寄存器 (118)表16-36TC地址空间寄存器 (118)表16-37TC接收读指针寄存器 (118)表16-38TC接收写指针寄存器 (119)表16-39TC中断寄存器 (119)表17-1S PACEWIRE节点控制器主要模块说明 (123)表17-2S PACEWIRE节点控制器寄存器地址 (124)表17-3SPW控制寄存器 (124)表17-4SPW状态寄存器 (125)表17-5SPW节点地址寄存器 (126)表17-6SPW时钟分频器寄存器 (126)表17-7SPW目标关键字寄存器 (126)表17-8SPW时间寄存器 (126)表17-9SPW DMA控制寄存器 (127)表17-10SPW接收最长数据包寄存器 (128)表17-11SPW发送器描述符表地址寄存器 (128)表17-12SPW接收描述符表地址寄存器 (128)表17-13SPW通道地址寄存器 (128)表17-14SPW接收描述符寄存器0 (128)表17-15SPW接收描述符寄存器1 (129)表17-16SPW发送描述符寄存器0 (129)表17-17SPW发送描述符寄存器1 (130)表17-18SPW发送描述符寄存器2 (130)表17-19SPW发送描述符寄存器3 (130)表18-1SPI寄存器地址 (133)表18-2SPI性能寄存器 (134)表18-3SPI模式控制寄存器 (134)表18-4SPI事件寄存器 (136)表18-5SPI控制屏蔽寄存器 (136)表18-6SPI控制命令寄存器 (137)表18-7SPI控制传输寄存器 (137)表18-8SPI控制接收寄存器 (137)表18-9SPI SLAVE选择寄存器 (137)表19-1B ASIC CAN偏移地址分配(基地址为:0X80200000) (140)表19-2控制寄存器(CR) (141)表19-3命令寄存器(CMR) (141)表19-4状态寄存器(SR) (142)表19-5中断寄存器(IR) (142)表19-6发送缓冲器 (142)表19-7P ELI CAN偏移地址分配 (143)表19-8模式寄存器(MOD) (144)表19-9命令寄存器(CMR) (145)表19-10状态寄存器 (145)表19-11中断寄存器(IR) (145)表19-12中断允许寄存器(IER) (146)表19-13仲裁丢失捕捉寄存器(ALC) (146)表19-14仲裁丢失捕捉寄存器(ALC) (146)表19-15错误代码说明(ALC.7:6) (146)表19-16错误代码说明(ALC.4:0) (146)表19-17发送缓冲器 (147)表19-18发送帧信息(此位段在SFF和EFF帧中相同) (147)表19-19发送标识符1(此位段在SFF帧和EFF帧中相同) (148)表19-20发送标识符2,SFF帧 (148)表19-21发送标识符2,EFF帧 (148)表19-22发送标识符3,EFF帧 (148)表19-23发送标识符4,EFF帧 (148)表19-24接收缓冲寄存器 (148)表19-25接收帧信息(此位段在SFF和EFF帧中相同) (149)表19-26接收标识符1(此位段在SFF帧和EFF帧中相同) (149)表19-27接收标识符2,SFF帧 (149)表19-28接收标识符2,EFF帧 (149)表19-29接收标识符3,EFF帧 (149)表19-30接收标识符4,EFF帧 (149)表19-31验收过滤寄存器 (150)表19-32时钟分频寄存器(CDR) (152)表19-33总线定时0寄存器(BTR0) (152)表19-34总线定时1寄存器(BTR1) (153)表20-1UHC I/O寄存器 (156)表20-2UHC I/O命令寄存器 (156)表20-3UHC I/O状态寄存器 (156)表20-4UHC I/O中断使能寄存器 (157)表20-5UHC I/O帧索引寄存器 (157)表20-6UHC I/O帧列表基地址寄存器 (157)表20-7UHC I/O起始帧修改寄存器 (157)表20-8UHC I/O端口状态与控制表寄存器 (158)表21-1UART寄存器 (162)表21-2UART数据寄存器 (162)表21-3UART状态寄存器 (162)表21-4UART控制寄存器 (163)表21-5UART分频寄存器 (163)表22-1以太网发送描述符字0 (165)表22-2以太网发送描述符字1 (165)表22-3以太网接收描述符字0 (166)表22-4以太网接收描述符字1 (167)表22-5的数据包格式 (169)表22-6EDCL接收数据包的应用协议域 (169)表22-7以太网控制器寄存器 (169)表22-8以太网控制寄存器 (170)表22-9以太网状态寄存器 (170)表22-10以太网MAC地址MSB寄存器 (171)表22-11以太网MAC地址LSB寄存器 (171)表22-12以太网MDIO寄存器 (171)表22-13以太网发送描述符表基地址寄存器 (172)表22-14以太网接收描述符表基地址寄存器 (172)表22-15以太网EDCL IP寄存器 (172)表22-16以太网H ASH表MSB寄存器 (172)表22-17以太网H ASH表MSB寄存器 (172)表22-18以太网EDCL MAC地址MSB寄存器 (173)表22-19以太网EDCL MAC地址LSB寄存器 (173)表23-1DDR2PHY的配置参考参数值 (176)表23-2DDR2PHY的配置参考参数值 (177)表23-3DDR2典型配置参考参数值 (178)表23-4DDR2SPA寄存器地址(0XFFE00000~0XFFE000FF) (180)表23-5DDR2SPA控制寄存器(DDR2SRAM CONTROL REGISTER(DDR2CFG1)) (180)表23-6DDR2SPA配置寄存器(DDR2SRAM CONFIG REGISTER2(DDR2CFG2),只读) (181)表23-7DDR2SPA配置寄存器(DDR2SRAM CONFIGURATION REGISTER3(DDR2CFG3)) (181)表23-8DDR2SPA配置寄存器(DDR2SRAM CONFIGURATION REGISTER4(DDR2CFG4)) (181)表23-9DDR2SPA配置寄存器(DDR2SRAM CONFIGURATION REGISTER5(DDR2CFG5)) (182)表23-10DDR2FT配置寄存器(DDR2FT CONFIGURATION REGISTER(DDR2FTCFG)) (182)表23-11DDR2FT诊断地址(DDR2FT DIAGNOSTIC ADDRESS(DDR2FTDA)) (182)表23-12DDR2FT诊断纠错位(DDR2FT DIAGNOSTIC CHECKBITS(DDR2FTDC)) (182)表23-13DDR2FT诊断数据(DDR2FT DIAGNOSTIC DATA(DDR2FTDD)) (183)表23-14DDR2FT边界地址寄存器(DDR2FT BOUNDARY ADDRESS REGISTER(DDR2FTBND)) (183)表24-1S698PM中1553B模块各子模块说明 (185)表24-2S698PM中1553B模块的端口信号说明 (186)表24-3S698PM中1553B模块地址空间分配 (188)表24-4S698PM中1553B模块寄存器偏移地址分配 (188)表24-5S698PM中1553B模块中断屏蔽寄存器(IMR) (189)表24-6S698PM中1553B模块BC配置寄存器1(BC-CFG1) (191)表24-7S698PM中1553B模块RT配置寄存器1(RT-CFG1) (192)表24-8S698PM中1553B模块配置寄存器2(CFG2) (193)表24-9S698PM中1553B模块启动/复位寄存器(SRR) (194)表24-10S698PM中1553B模块BC/RT命令堆栈指针寄存器(STACK_ADDR) (195)表24-11S698PM中1553B模块BM初始命令堆栈指针寄存器(INIT_STACK_ADDR) (195)表24-12S698PM中1553B模块时间标签寄存器0(TTR) (196)表24-13S698PM中1553B模块中断状态寄存器(INT_STA) (196)表24-14S698PM中1553B模块配置寄存器3(CFG3) (197)表24-15S698PM中1553B模块配置寄存器4(CFG4) (199)表24-16S698PM中1553B模块配置寄存器5(CFG5) (199)表24-17S698PM中1553B模块BM数据堆栈指针寄存器(BM_STACK_ADDR) (200)表24-18S698PM中1553B模块1M BPS/10M BPS配置寄存器(1M_10M_SEL) (200)表24-19S698PM中1553B模块BC帧时间/RT上一命令字寄存器(LAST_CMD) (200)表24-20S698PM中1553B模块RT状态字寄存器(RT_STA) (200)表24-21S698PM中1553B模块RT BIT字寄存器(RT_BIT_REG) (201)表24-22S698PM中1553B模块时间标签寄存器1(TTR1) (202)表24-23S698PM中1553B模块BC控制字(BC_CTRL) (202)表24-24S698PM中1553B模块BC命令字(BC_CMD) (203)表24-25S698PM中1553B模块BC块状态字(BC_BLK) (203)表24-26S698PM中1553B模块RT子地址控制字(RT_SUB_CTRL) (205)表24-27S698PM中1553B模块RT块状态字(RT_BLK) (206)表24-28S698PM中1553B模块BM块状态字(BM_BLK) (207)表24-29S698PM中1553B模块BC存储器地址分配(4K双口RAM) (209)表24-30S698PM中1553B模块BC消息格式 (210)表24-31S698PM中1553B模块BC消息格式(接上表) (211)表24-32S698PM中1553B模块RT存储器地址分配(4K双口RAM) (211)表24-33S698PM中1553B模块RT存储器查找表(LOOK_UP TABLE) (212)表24-34S698PM中1553B模块RT存储器非法命令地址分配表(COMMAND ILLEGALIZING TABLE) (212)表24-35S698PM中1553B模块RT存储器忙位查找表地址分配表(BUSY BIT LOOKUP TABLE) . 213表24-36S698PM中1553B模块RT存储器方式代码选择中断表 (213)表24-37S698PM中1553B模块RT存储器方式代码选择中断表地址分配表 (214)表24-38S698PM中1553B模块RT存储器方式代码数据表 (214)表24-39S698PM中1553B模块已实现的方式代码 (215)表24-40S698PM中1553B模块BM存储器地址分配 (217)表24-41S698PM中1553B模块BM子地址分配表 (218)表25-1塑料封装信号引脚定义 (226)表25-2塑料封装电源引脚定义 (238)表25-3陶瓷封装信号引脚定义 (242)表25-4陶瓷封装电源引脚定义 (254)表26-1S698PM芯片关键参数极限范围 (255)表26-2S698PM芯片直流(DC)特性参数 (256)图目录图1-1S698PM芯片结构框图 (2)图2-1S698PM芯片的复位及启动过程图 (7)图2-2S698PM芯片的复位及启动时序图 (8)图2-3S698PM芯片的多核软件程序启动过程图 (10)图3-1时钟分频结构图 (13)图4-1地址转换 (17)图4-2S698PM芯片窗口的寄存器结构 (21)图7-1S698PM芯片的中断控制器功能结构图 (57)图8-1S698PM芯片通用定时器结构图 (65)图9-1S698PM芯片锁存定时器结构图 (70)图10-1S698PM芯片GPIO结构示意图 (74)图12-1I2C MASTER结构框图 (79)图12-2I2C数据传输示意图 (80)图13-1S698PM内部DSU模块结构图 (84)图14-1 JTAG 控制器模块图 (90)图15-1 PROM 非连续读周期(0等待) (97)图15-2 PROM连续读周期(0等待) (97)图15-3 PROM读周期(3等待) (98)图15-4 PROM 写周期(0等待) (98)图15-5 PROM 写周期(3等待) (99)图15-6静态RAM非连续读周期(0等待) (99)图15-7静态RAM非连续读周期(3等待) (100)图15-8静态RAM写周期(0等待) (100)图15-9静态RAM写周期(3等待) (101)图15-10静态RAM R EAD-MODIFY-WRITE周期(0等待) (101)图15-11I/O读周期(0等待) (102)图15-12I/O写周期(0等待) (102)图15-13I/O读周期(3等待) (103)图15-14I/O写周期(3等待) (103)图15-15DDR2SDRAM读操作时序 (104)图15-16DDR2SDRAM写操作时序 (104)图16-1TM结构框图 (106)图16-2TC结构框图 (114)图17-1S PACEWIRE节点控制器功能结构框图 (123)图18-1SPI控制器结构框图 (131)图18-2SPI控制器传输字节(0X55)的所有传输模式 (132)图19-1CAN控制器结构框图 (139)图19-2信号数据帧组成 (153)图20-1基于AMBA总线的USB1.1主机控制器IP核的结构 (155)图21-1UART结构框图 (159)图22-1以太网内部结构图 (164)图23-1DDR2SPA结构图 (175)图24-1S698PM中1553B模块结构框图 (185)图24-2S698PM中1553B模块BC存储器管理 (210)图24-3S698PM中1553B模块RT单缓冲存储器管理 (216)图24-4S698PM中1553B模块RT循环缓冲存储器管理 (217)图24-5S698PM中1553B模块RT双缓冲存储器管理 (217)图24-6S698PM中1553B模块BM存储器管理 (218)图24-7S698PM中1553B模块发送波形 (219)图24-8S698PM中1553B模块接收波形 (219)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

L X Y28162用户手册2008年07月V1.0目录1芯片功能说明 (4)1.1芯片主要功能特性 (5)1.2芯片应用场合 (5)1.3芯片基本结构描述 (5)2芯片特性说明 (5)2.1芯片的封装和引脚 (5)2.2芯片最大极限值 (6)2.3芯片电气特性(VDD=5) (7)2.4开关特性(VDD=5V) (8)2.5开关特性测试电路图 (9)2.6芯片时序图 (10)2.6.1 串口时序图 (10)2.6.2 电流输出端口时序图............................................................... 错误!未定义书签。

2.6.3 控制命令时序图....................................................................... 错误!未定义书签。

3芯片功能模块描述.................................................................................... 错误!未定义书签。

3.1设置像素灰度(Setting Gray Scales of Pixels) ............................ 错误!未定义书签。

3.2数据加载时时序图(Full Timing for Data Loading) ................... 错误!未定义书签。

3.3配置加载时时序图(Full Timing for Config Loading)................ 错误!未定义书签。

3.4开路检测原理(Open-Circuit Detection Principle) (10)3.5短路检测原理(Short-Circuit Detection Principle) (10)3.6奇偶校验位(Checking Parity Bit) ............................................... 错误!未定义书签。

3.7温度错误指示(Thermal Error Flag) (10)3.8恒定电流输出(Constant Current) (10)3.9设定输出电流(Setting Output Current) (11)3.10级连输出的延迟(Delay Time of Staggered Output) (11)3.11功耗(Package Power Dissipation ) (11)3.12管脚散热(Usage of Thermal Pad) (11)3.13过热保护(Thermal Protection Function ) (12)3.14LED供电电压(LED Supply Voltage ) (12)3.15开关噪声抑制(Switching Noise Reduction) (12)3.16控制命令(Control Command)................................................. 错误!未定义书签。

4芯片寄存器描述........................................................................................ 错误!未定义书签。

4.1寄存器定义(Definition of Configuration Register) .................... 错误!未定义书签。

4.2输入输出管脚等效电路(Equivalent Circuits of Inputs and Outputs) (13)5芯片的封装 (13)图目录图1 芯片原理框图 (5)图2 与数字部分接口框图....................................................................... 错误!未定义书签。

图3 芯片引脚图.. (6)图4 芯片开关特性测试电路图 (9)图5 串口时序图 (10)图6 电流输出时序图一........................................................................... 错误!未定义书签。

图7 电流输出时序图二........................................................................... 错误!未定义书签。

图8 控制命令时序图............................................................................... 错误!未定义书签。

图9 数据载入时序全图........................................................................... 错误!未定义书签。

图10 配置载入时序全图................................................................... 错误!未定义书签。

图11 开路检测原理........................................................................... 错误!未定义书签。

图12 短路检测原理........................................................................... 错误!未定义书签。

图13 错误状态输出时序图............................................................... 错误!未定义书签。

图14 输出端口I-V特性图............................................................. 错误!未定义书签。

图15 输出端口输出电流与外置电阻R EXT关系图.......................... 错误!未定义书签。

图16 温度与占空比关系图............................................................... 错误!未定义书签。

图17 功率与环境温度关系图........................................................... 错误!未定义书签。

图18 PCB板散热布局图示 .. (12)图19 LED供电电路图示 (12)图20 输入输出端口等效电路 (13)图21 芯片封装尺寸信息 (13)图22 TSSOP-24芯片封装尺寸信息 (13)表目录表1 芯片引脚说明 (6)表2 芯片最大物理极限值 (6)表3 芯片电气特性表 (7)表4 开关特性表 (8)表5 芯片的开路状态指示定义............................................................... 错误!未定义书签。

表6 芯片的短路状态指示定义............................................................... 错误!未定义书签。

表7 芯片的开短路状态指示定义........................................................... 错误!未定义书签。

表8 控制命令列表................................................................................... 错误!未定义书签。

表9 寄存器地址表................................................................................... 错误!未定义书签。

表10 寄存器定义表........................................................................... 错误!未定义书签。

1芯片功能说明LXY28162是一款16通道内置脉冲宽度调制(PWM)的LED驱动器,SOP-24封装和TSSOP-24封装。

彩色深度为16位深度.。

LXY28162集成一个16位深度的移位寄存器将串行输入的数据转换成每个输出通道的像素灰度.。

在LXY28162的输出口,16个端口下拉输出恒定、一致的电流用于驱动宽Vf variations 的LED.。

输出电流可以流过一个外置电阻,输出电流可以配置为1024为梯度来调整LED显示的亮度。

LXY28162去除了主控制器的信号同步产生模块,只需要把数据输入至驱动器即可。

LXY28162由图形数据的亮度来驱动对应的LED。

LXY28162所有的输出通道可以建立16位彩色深度(65,536 gray scales). 每个LED的亮度可以通过芯片内置的10位D/A来调整LED为最大、最小亮度。

1.1芯片主要功能特性●封装管脚向下兼容市场主流16位恒流芯片●16路8位(256级)可独立调整的恒流输出(逐点校正)●所有通道128级电流调整(整屏亮度调整)●16位深度的智能脉冲宽度调制(W-PWM)控制●16 位开路检测和短路检测●施密特触发输入●过热检测、保护功能●恒流输出范围: 5V,5~80mA●输出电流精度:通道之间+/-1.5%,芯片之间+/-3%●最高输入频率25MHz● 3.3-5V电压工作1.2芯片应用场合●LED视频显示驱动1.3芯片基本结构描述LXY28162主要包括串行数据输入、智能(W-PWM)、恒流控制电路(含256级单通道和128级全部通道)、开短路检测、输出电流驱动等功能模块,原理框图如下图1芯片原理框图2芯片特性说明2.1芯片的封装和引脚LXY28162采用SOP-24和TSSOP-24封装,管脚定义如下图图2芯片引脚图表1芯片引脚说明管脚脚号类型功能GND 1 电源控制逻辑地和恒流源地SDI 2 施密特触发输入串行数据输入CLK 3 施密特触发输入串行移位时钟输入LE 4 施密特触发输入串行数据锁存及功能控制OUT0~15 5~20 输出恒流输入,电流为5-60mA NC 21 空脚无定义SDO 22 可控延时输输出输据输出脚,有四级延时可选10ns,20ns,30ns,或时钟下降缘R-EXT 23 控制外接一电阻控制恒流脚电流大小VDD 24 电源5V电源2.2芯片最大极限值表2芯片最大物理极限值参数符号范围单位工作电压VDD 7 V输入电压(SDI) VIN-0.4~VDD+0.4V输出电流IOUT +80 mA Sustaining Voltage at OUT Port VDS 7 V 数据、时钟频率* DCLK +25 MHz 地线电流IGND +1300 mA 功耗(On PCB, L Type PD 2.39 W参数符号范围单位Ta=25°C) S Type 1.73封装热阻(On PCB,,Ta=25°C) L Type Rth(j-a) 59.1°C/W S Type 72.4工作温度Topr -40~+85 °C储存温度Tstg -55~+150 °C2.3芯片电气特性(VDD=5)表3芯片电气特性表特性指标符号测试条件最小典型最大单位电源电压VDD - 3.3 5.0 5.5 V SustainingVoltage atOUT PortsVDS OUT0 ~ OUT15 - - VDD+0.4 V输出电流IOUT 参考电气特性测试电路 5 - 80 mA IOH SDO输出- - -6.0 mA IOL SDO 输出- - 6.0 mA输入电压高电平VIH Ta=-40~85ºC 0.7*VDD - VDD V 底电平VIL Ta=-40~85ºC GND - 0.3*VDD V输出漏电流IOH VDS=7.0V - - 0.5 μA输出电压SDO管脚VOL IOL=6.0mA - - 0.4 VVOH IOH=6.0mA 4.6 - - V通道间电流失配∆IOUT1 IOUT=10.8mAVDS=1.0VRext=910Ω - ±1.5 ±3.0 %芯片间电流失配∆IOUT2 IOUT=10.8mAVDS=1.0VRext=910Ω - ±3.0 ±6.0 %输出电流 vs. 输出电压调制%/∆VDSVDS = 1.0V 或 3.0V,Rext=460Ω@21mA- ±0.1 ±0.5 % / V输出电流 vs.输出电压调整%/dVDD VDD = 4.5V 或 5.5V - ±1.0 ±5.0 % / V LED错误检测阈值VDS,TH - - 0.15 0.20 V 下拉电阻阻值RIN(down) LE 250 500 800 KΩ电压电压关断状态IDD(off) 1 Rext=Open OUT0 ~ OUT15=Off- 11.4 12.5mA IDD(off) 2Rext=1800ΩOUT0 ~ OUT15=Off- 12.3 13.5IDD(off) 3 Rext=910Ω OUT0 ~ OUT15=Off- 13.7 15.0工作状态IDD(on) 1Rext=1800ΩOUT0 ~ OUT15=On- 14.2 15.7IDD(on) 2 Rext=910Ω OUT0 ~ OUT15=On- 16.3 18.5芯片节温TTF Junction Temperature 135 150 165 °C2.4开关特性(VDD=5V)特性指标符号测试条件最小典型最大单位建立时间SDI - DCLK↑ tSU0 1 - - nsLE↑ –DCLK↑ tSU1 1 - - nsLE↓ –DCLK↑ tSU2 5 - - ns 保持时间DCLK↑ - SDI tH0 3 - - nsDCLK↑ - LE↓ tH1 7 - - ns传输延迟时间DCLK -SDO(可选择)tPD0VDD=5.0VVIH=VDDVIL=GND5 10 20 ns15 20 30 ns25 30 40 nsDCLK 下降缘输出- GCLK –OUT8ntPD1* 75 - nsStagger Delay Time OUT8n + 1* tDL1 RL=152ΩCL=10pFC1=100nFC2=10μF--- 25 - ns OUT8n + 2 * tDL2 - 50 - ns OUT8n + 3 * tDL3 - 75 - ns OUT8n + 4 * tDL4 100 ns OUT8n + 5 * tDL5 125 ns OUT8n + 6 * tDL6 150 ns OUT8n + 7 * tDL7 175 ns脉冲宽度LE tw(L) 5 - - ns DCLK tw(DCLK) 20 - - ns GCLK tw(GCLK) 20 - - ns电流输出端上升时间 ** tOR - 10 20 ns 电流输出端下降时间**tOF - 10 20 ns 错误检测最小持续时间tEDD *** - 1 - μs * 参考电流输出时序图, 当 n=0, 1, 2, 3, 4, 5, 6, 72.5开关特性测试电路图图3芯片开关特性测试电路图2.6芯片时序图2.6.1串口时序图图4串口时序图2.7开路检测原理(Open-Circuit Detection Principle)LXY28162根据LED负载状态进行开路检测。