半导体—金属接触特性测试技术

半导体测试原理

半导体测试公司简介Integrated Device Manufacturer (IDM):半导体公司,集成了设计和制造业务。

IBM:(International Business Machines Corporation)国际商业机器公司,总部在美国纽约州阿蒙克市。

Intel:英特尔,全球最大的半导体芯片制造商,总部位于美国加利弗尼亚州圣克拉拉市。

Texas Instruments:简称TI,德州仪器,全球领先的数字信号处理与模拟技术半导体供应商。

总部位于美国得克萨斯州的达拉斯。

Samsung:三星,韩国最大的企业集团,业务涉及多个领域,主要包括半导体、移动电话、显示器、笔记本、电视机、电冰箱、空调、数码摄像机等。

STMicroelectronics:意法半导体,意大利SGS半导体公司和法国Thomson半导体合并后的新企业,公司总部设在瑞士日内瓦。

是全球第五大半导体厂商。

Strategic Outsourcing Model(战略外包模式):一种新的业务模式,使IDM厂商外包前沿的设计,同时保持工艺技术开发Motorola:摩托罗拉。

总部在美国伊利诺斯州。

是全球芯片制造、电子通讯的领导者。

ADI:(Analog Devices, Inc)亚德诺半导体技术公司,公司总部设在美国,高性能模拟集成电路(IC)制造商,产品广泛用于模拟信号和数字信号处理领域。

Fabless:是半导体集成电路行业中无生产线设计公司的简称。

专注于设计与销售应用半导体晶片,将半导体的生产制造外包给专业晶圆代工制造厂商。

一般的fabless公司至少外包百分之七十五的晶圆生产给别的代工厂。

Qualcomm:高通,公司总部在美国。

以CDMA(码分多址)数字技术为基础,开发并提供富于创意的数字无线通信产品和服务。

如今,美国高通公司正积极倡导全球快速部署3G网络、手机及应用。

Broadcom:博通,总部在美国,全球领先的有线和无线通信半导体公司。

半导体测试与分析-PPT精选文档

二探针法

用两根探针借助于电位差计量取 样品表面某两点(实际上是某两 个等位面)间的电位差U,并量出 流经样品的电流值I,即可算出 该两个等位面间的长方体的电阻 值R。精确量出探针间距L及样 品截面积S, 则样品的电阻率为

两个改进措施

1. 补偿法来测量电压,以避免探针与半导体之间 高阻接触对测量结果的影响 2. 两个端电极与被测半导体之间为欧姆接触,因 而避免了少数载流子的注入

半导体电阻率的测量与导体的电阻率测量是有区 别的

1、在金属与半导体接触的界面附近也要产生一个耗尽层。因为金属 的电子密度极高,因而这个耗尽层展宽在半导体一边。耗尽层中只有 不能自由运动的电离杂质,它们不能参与导电,因而这是一个高阻层。 同时,任何两种材料的小面积接触都会在接触处产生扩展电阻。尤其 是对金属—半导体点接触,这个扩展电阻会很大,人们常常把这两个 因接触而产生的高电阻统称为接触电阻。因此,当用欧姆表来测量半 导体时,这个巨大的接触电阻就会使结果面目全非,毫不可信。

2、功函数不同的两种金属制品在接触时也要因接触电势差而在界面

上出现一个电荷偶层,但这个空间电荷层极薄,每边只有约一个原于 层厚,远小于电子的扩散长度,因而对载流子没有阻挡作用。同时, 金属与金属的小面积接触的扩展电阻也很小。因此,上述方法对测量 金属导体的电阻率是精确的。

3、由非平衡载流子的电注入效应可以想到,如果被测半 导体是n型,那么测量电流将通过正电极向半导体注入空 穴;若被测半导体是P型则会从负电极向半导体注入电子。 这些注入的少数载流子在外电场的驱使下向另一电极漂移, 参与导电。在注入电极附近的某一范围内,载流子密度因 此而高于载流子的热平衡密度,因而测量结果不能反映材 料电阻率的真正大小。对于热平衡载流子密度较低的高阻 材料,其接触电阻更大,少子注入的影响也更加严重。

半导体测试与表征技术基础[详细讲解]

![半导体测试与表征技术基础[详细讲解]](https://img.taocdn.com/s3/m/29135caaf021dd36a32d7375a417866fb84ac01c.png)

半导体测试与表征技术基础第一章概述(编写人陆晓东)第一节半导体测试与表征技术概述主要包括:发展历史、现状和在半导体产业中的作用第二节半导体测试与表征技术分类及特点主要包括:按测试与表征技术的物理效应分类、按芯片生产流程分类及测试对象分类(性能、材料、制备、成分)等。

第三节半导体测试与表征技术的发展趋势主要包括:结合自动化和计算机技术的发展,重点论述在线测试、结果输出和数据处理功能的变化;简要介绍最新出现的各类新型测试技术。

第二章半导体工艺质量测试技术第一节杂质浓度分布测试技术(编写人:吕航)主要介绍探针法,具体包括:PN结结深测量;探针法测量半导体扩散层的薄层电阻(探针法测试电阻率的基本原理、四探针法的测试设备、样品制备及测试过程注意事项、四探针测试的应用和实例);要介绍扩展电阻测试系统,具体包括:扩展电阻测试的基本原理、扩展电阻的测试原理、扩展电阻测试系统、扩展电阻测试的样品、扩展电阻法样品的磨角、扩展电阻法样品的制备、扩展电阻测试的影响因素、扩展电阻法测量过程中应注意的问题、扩展电阻法测量浅结器件结深和杂质分布时应注意的问题、扩展电阻测试的应用和实例。

第二节少数载流子寿命测试技术(编写人:钟敏)主要介绍直流光电导衰退法、高频光电导衰退法,具体包括:非平衡载流子的产生、非平衡载流子寿命、少数载流子寿命测试的基本原理和技术、少数载流子寿命的测试。

以及其它少子寿命测试方法,如表面光电压法、少子脉冲漂移法。

第三节表面电场和空间电荷区测量(编写人:吕航)主要包括:表面电场和空间电荷区的测量,金属探针法测量PN结表面电场的分布、激光探针法测试空间电荷区的宽度;容压法测量体内空间电荷区展宽。

第四节杂质补偿度的测量(编写人:钟敏)包括:霍尔效应的基本理论、范德堡测试技术、霍尔效应的测试系统、霍尔效应测试仪的结构、霍尔效应仪的灵敏度、霍尔效应的样品和测试、霍尔效应测试的样品结构、霍尔效应测试的测准条件、霍尔效应测试步骤、霍尔效应测试的应用和实例、硅的杂质补偿度测量、znO的载流子浓度、迁移率和补偿度测量、硅超浅结中载流子浓度的深度分布测量第五节氧化物、界面陷阱电荷及氧化物完整性测量(编写人:钟敏)包括:固定氧化物陷阱和可动电荷、界面陷阱电荷、氧化物完整性测试技术等。

半导体金属沾污问题研究

半导体硅片金属微观污染机理研究进展文章来源:互联网点击数:589 录入时间:2006-4-2减小字体增大字体郑宣,程璇摘要:综述了近10年来国内外在半导体硅片金属微观污染研究领域的进展。

研究了单金属特别是铜的沉积、形成机理和动力学以及采用的研究方法和分析测试手段,包括对电化学参数和物理参数等研究。

指出了随着科学技术的不断发展,金属污染金属检测手段也得到了丰富,为金属微观污染的研究提供了有力的工具。

1引言随着ULSI技术的不断向前发展,对半导体硅的表面性质要求也越来越严格。

而且电路的集成度日益提高,单元图形的尺寸日益微化,污染物对器件的影响也愈加突出,以至于洁净表面的制备已成为制作64M和2 56Mbyte DRAM的关键技术[1,2]。

此外有超过50%成品损失率是由硅表面的污染所造成的。

硅片上的杂质一般可分为三种:分子型、离子型和原子型。

这里主要探讨原子型杂质。

原子型杂质主要是指过渡金属或贵金属原子(如Au、Ag、Cu等),它们主要来自于硅的酸性刻蚀剂中。

原子型杂质主要影响器件中少子寿命、表面的导电性、门氧化物的完整性和其它器件稳定性参数等,特别在高温或电场下,它们能够向半导体结构的本体扩散或在表面扩大分布,导致器件性能下降,产率降低。

在工业上,硅表面清洗分为干法和湿法清洗两种,前者是物理方法,后者是化学方法。

目前湿法清洗一直占主导地位,因为它对杂质和基体选择性好,可将杂质清洗至非常低的水平。

本文综述了几种典型金属在湿法清洗过程中对硅片表面产生的金属微观污染和所涉及的机理研究进展,并讨论了今后该领域的研究方向。

2 污染物的形成机理与研究半导体微电子制造过程中,金属污染浓度可达到1012 ~1013 atom/cm2。

但实际上制造16Mbyte DRAM 要求必须将硅表面金属浓度降低到1×1012 atom/cm2以下。

所以研究化学试剂HF中金属离子(主要是铜离子)在硅表面的沉积行为和污染机理具有重要的科学价值和实际意义。

半导体物理学第七章

J = J m → s + J s →m

qφns qV = A T exp(− )[exp( ) − 1] k0T k0T

∗ 2

qV = J sT [exp( ) − 1] k0T

与扩散理论得到的J-V形式上是一样的,所不同的是JsT与外加电压无 关,却是一个更强烈依赖于温度的函数。

3、镜像力和隧道效应的影响

接触电阻定义为零偏压下的微分电阻,即

∂I Rs = ∂V V =0

−1

下面估算一下以隧道电流为主时的接触电阻。讨论金属和n型半导体接触的 势垒贯穿问题。将导带底选为电势能的零点。

qN D V ( x) = − ( x − d0 )2 2ε r ε 0

电子的势垒为:

q2 ND −qV ( x) = ( x − d0 )2 2ε r ε 0

2

半导体内电场为零,因而

E ( xd ) = − dV dx

x = xd

=0

金属费米能级除以-q作为电势零点,则有 势垒区中

V (0) = −φns

dV ( x) qN D E ( xd ) = − = ( x − xd ) dx ε rε 0 1 2 V ( x) = ( xxd − x ) − φns ε rε 0 2 qN D

2、接触电势差

设想有一块金属和n型半导体, 它们有共同的真空静止能级。 假定

Wm > Ws

接触前,未平衡的能级

平衡状态的能级

q(Vs' − Vm ) = Wm − Ws Ws − Wm Vms = Vm − V = q

' s

接触电势差

紧密接触

忽略间隙 当 Vms 很小时,接触电势差绝大部分 落在空间电荷区。 金属一边的势垒高度是

为p型si半导体设计欧姆接触

为p型si半导体设计欧姆接触欧姆接触是一种电子学现象,是指当两个电极之间的接触电阻随着加入的电压增大而变小。

在半导体器件制造中,欧姆接触被广泛应用于p型和n型半导体器件的电极制作中。

本文将针对p型Si半导体的欧姆接触设计进行详细探讨。

1. 欧姆接触原理欧姆接触的原理可以通过欧姆定律来解释。

欧姆定律是指电流$I$与电压$V$之间的关系,即$I=V/R$,其中$R$为电阻。

在欧姆接触中,当两个接触金属与半导体接触时,接触电阻$R$会随着电压的升高而减小,这是因为当电压升高时,电子在金属外壳中的热运动增强,进一步促进更多电子从半导体向金属流动,从而导致接触电阻降低。

2. p型Si半导体欧姆接触设计在p型Si半导体的欧姆接触设计中,我们需要考虑以下因素:2.1 金属材料的选择选择合适的金属材料是欧姆接触设计中最关键的一步。

常用的金属材料包括Ti、Cr、Al和Au等。

Ti和Cr的粘附性强,可以很好地粘附到p型Si表面,并且它们的电学性能也比较适合制作欧姆接触。

而Al和Au的电学性能更优秀,但由于它们的粘附性不够强,需要在它们之上涂覆一层Ti或Cr来增强粘附力。

对于p型Si半导体的欧姆接触设计,建议选择Ti或Cr材料。

2.2 洁净度的保证在欧姆接触制作过程中,确保器件表面的洁净度是非常重要的。

因为器件表面的杂质和污染物会对接触电极的制造和性能产生很大影响。

需要在制作欧姆接触前,充分保证p型Si表面的洁净度。

2.3 接触面积的控制接触面积的大小会直接影响欧姆接触的电学特性。

一般来讲,接触面积越大,电流密度就越小,接触电阻就越小。

在设计欧姆接触时,需要合理控制接触面积,以达到最佳电学性能。

2.4 热处理的优化在欧姆接触制作过程中,热处理是一个非常重要的步骤。

热处理可以改善接触金属与p型Si之间的界面特性,促进更好的电子传输。

在制作欧姆接触时,需要对热处理的参数进行优化,以获得最佳的电学性能。

在设计p型Si半导体的欧姆接触时,需要考虑金属材料的选择、洁净度的保证、接触面积的控制以及热处理的优化等因素。

半导体激光器的光学特性测试

实验八半导体激光器的光学特性测试[实验目的]1、通过实验熟悉半导体激光器的光学特性。

2、掌握半导体激光器耦合、准直等光路的调节。

3、根据半导体激光器的光学特性考察其在光电子技术方面的应用。

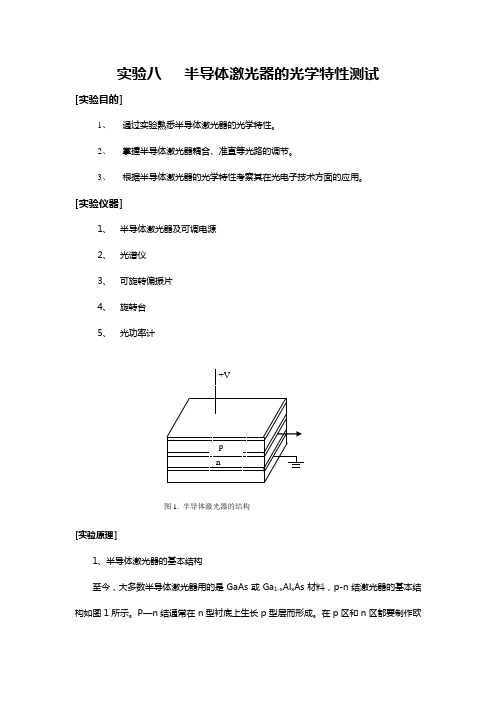

[实验仪器]1、半导体激光器及可调电源2、光谱仪3、可旋转偏振片4、旋转台5、光功率计图1. 半导体激光器的结构[实验原理]1、半导体激光器的基本结构至今,大多数半导体激光器用的是GaAs或Ga1-x Al x As材料,p-n结激光器的基本结构如图1所示。

P—n结通常在n型衬底上生长p型层而形成。

在p区和n区都要制作欧姆接触,使激励电流能够通过,这电流使结区附近的有源区内产生粒子数反转,还需要制成两个平行的端面起镜面作用,为形成激光模提供必须的光反馈。

图1中的器件是分立的激光器结构,它可以与光纤传输线连接,如果设计成更完整的多层结构,可以提供更复杂的光反馈,更适合单片集成光路。

2、半导体激光器的阈值条件:当半导体激光器加正向偏置并导通时,器件不会立即出现激光振荡。

小电流时发射光大都来自自发辐射,光谱线宽在数百唉数量级。

随着激励电流的增大,结区大量粒子数反转,发射更多的光子。

当电流超过阈值时,会出现从非受激发射到受激发射的突变。

实际上能够 观察到超过阈值电流时激光的突然发生,只要观察在光功率对激励电流曲线上斜率的急速突变,如图2所示;这是由于激光作用过程的本身具有较高量子效率的缘故。

从定量分析,激光的阈值对应于:由受激发射所增加的激光模光子数(每秒)正好等于由散射、吸收激光器的发射所损耗的光子数(每秒)。

据此,可将阈值电流作为各种材料和结构参数的函数导出一个表达式:)]1(121[8202Rn a Den J Q th +∆=ληγπ (1) 这里,Q η是内量子效率,O λ是发射光的真空波长,n 是折射率,γ∆是自发辐射线宽,e 是电子电荷,D 是光发射层的厚度,α是行波的损耗系数,L 是腔长,R 为功率反射系数。

半导体测试与表征技术基础

半导体测试与表征技术基础第一章概述(编写人陆晓东)第一节半导体测试与表征技术概述主要包括:发展历史、现状和在半导体产业中的作用第二节半导体测试与表征技术分类及特点主要包括:按测试与表征技术的物理效应分类、按芯片生产流程分类及测试对象分类(性能、材料、制备、成分)等。

第三节半导体测试与表征技术的发展趋势主要包括:结合自动化和计算机技术的发展,重点论述在线测试、结果输出和数据处理功能的变化;简要介绍最新出现的各类新型测试技术。

第二章半导体工艺质量测试技术第一节杂质浓度分布测试技术(编写人:吕航)主要介绍探针法,具体包括:PN结结深测量;探针法测量半导体扩散层的薄层电阻(探针法测试电阻率的基本原理、四探针法的测试设备、样品制备及测试过程注意事项、四探针测试的应用和实例);要介绍扩展电阻测试系统,具体包括:扩展电阻测试的基本原理、扩展电阻的测试原理、扩展电阻测试系统、扩展电阻测试的样品、扩展电阻法样品的磨角、扩展电阻法样品的制备、扩展电阻测试的影响因素、扩展电阻法测量过程中应注意的问题、扩展电阻法测量浅结器件结深和杂质分布时应注意的问题、扩展电阻测试的应用和实例。

第二节少数载流子寿命测试技术(编写人:钟敏)主要介绍直流光电导衰退法、高频光电导衰退法,具体包括:非平衡载流子的产生、非平衡载流子寿命、少数载流子寿命测试的基本原理和技术、少数载流子寿命的测试。

以及其它少子寿命测试方法,如表面光电压法、少子脉冲漂移法。

第三节表面电场和空间电荷区测量(编写人:吕航)主要包括:表面电场和空间电荷区的测量,金属探针法测量PN结表面电场的分布、激光探针法测试空间电荷区的宽度;容压法测量体内空间电荷区展宽。

第四节杂质补偿度的测量(编写人:钟敏)包括:霍尔效应的基本理论、范德堡测试技术、霍尔效应的测试系统、霍尔效应测试仪的结构、霍尔效应仪的灵敏度、霍尔效应的样品和测试、霍尔效应测试的样品结构、霍尔效应测试的测准条件、霍尔效应测试步骤、霍尔效应测试的应用和实例、硅的杂质补偿度测量、znO的载流子浓度、迁移率和补偿度测量、硅超浅结中载流子浓度的深度分布测量第五节氧化物、界面陷阱电荷及氧化物完整性测量(编写人:钟敏)包括:固定氧化物陷阱和可动电荷、界面陷阱电荷、氧化物完整性测试技术等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

W

I

由紫外光谱等方法可以测出禁带宽度,由UPS可测出导带底相对于费米能 级的位置。

半导体亲和势

欧姆接触与肖特基接触

Φm Φm- χ

Vacuum level

Φm

χ Φ

Φm- χ

Vacuum level

χ Φm

Φ Φm- χ

Vacuum level χ

Φ

Metal

Semiconductor

Metal

半导体—金属接触特性测试技术

(1)功函数 (2)半导体亲和势(能) (3)欧姆接触与肖特基接触 (4)肖特基接触势垒

功函数(work function)又称逸出功,在固体物理中 被定义成:把一个电子从固体内部刚刚移到此物 体表面所需的最少的能量。 半导体功函数:真空中静止电子的能量与半导体 费米能级的能量之差。 单位:eV/电子伏特

(1)功函数

紫外光电子能谱(UPS)

基本原理就是光电效应:

紫外光 外层价电子自由 光电子 ( 激发态分子离子)

能量关系可表示:

hv Eb Ek Er

电子结合能 电子动能

原子的反冲能量

Er

ቤተ መጻሕፍቲ ባይዱ1M

2

ma*2

紫外光电子能谱(UPS)

紫外光电子能谱(UPS)

开尔文探针法(Kelvin probe force microscopy-KPFM)

(4)肖特基接触势垒 I-V 法

(4)肖特基接触势垒

(4)肖特基接触势垒 C-V 法

(4)肖特基接触势垒 C-V 法

由

则势垒高度可由下式求出

(4)肖特基接触势垒 C-V 法

(4)肖特基接触势垒

在I-V测试中,电流依赖于界面结构,接触的横向 不均匀性使整流特性变差,而且电流中还包含热 电子发射以外的电流,这些都导致计算出来的结 果与实际偏差很大。

在C-V方法中,电容对于空间电荷区内的势垒涨 落不敏感,会屏蔽空间电荷区的边界,并且此方 法是在整个接触面上计算势垒高度的,而通过界 面的电流与势垒高度成指数关系,因此它对界面 处的势垒分布非常敏感。对于能带弯曲不均匀的 界面以及空间电荷,不同方法计算出来的势垒高 度是不同的。

(4)肖特基接触势垒 同步辐射光电子能谱法(SRXPS)

开尔文探针法(Kelvin probe force microscopy-KPFM)

不存在电子发射和收集过程,避免测量本身引起表面态的变化。 测量精度高,对样品表面无破坏。 需要高真空环境,对探针的性能有较高要求。

半导体亲和势

半导体导带底部到真空能级间的能量值,它表征材料在发生光电效应时,电 子逸出材料的难易程度。电子亲和势越小,就越容易逸出。

Au/CZT/Au

Pockels效应测试

Pt/CdT/Pt 600V

In/CdTe/Pt 600V

对于形成肖特基接触的CdTe晶体,其内电场在从阳极(In电极)到阴极(Pt 电极)显著的逐渐降低。这一现象是由于阳极的肖特基接触势垒所产生的 反向电流使得空穴注入半导体,使得正空间电荷在阳极开始聚集。

Pockels效应测试

Pockels效应是一种一次电光效应,指的是:平面偏振光沿着处 在外电场内的压电晶体的光轴传播时发生双折射现象,且两个主 折射率之差与外电场强度成正比。

Pockels效应测试

E(x, y) 1 arcsin I (x, y)

I0 (x, y)

3 n03r41d 2

Pockels效应测试

在CdZnTe(110)上得出EB和EV-C分别为11.377eV和10.639eV。所以 Au与CdZnTe (110)面的理想肖特基接触势垒ΦB, p 为0.74eV。

谢谢!

Semiconductor

Metal Semiconductor

(a)

(b)

(c)

Energy band diagram for n-type semiconductor-metal contacts: (a) Schottky contact;

(b) Ohmic contact ; (c)Injecting Ohmic contact

(4)肖特基接触势垒 同步辐射光电子能谱法(SRXPS)

以CdZnTe晶体为例,利用同步辐射光电子能谱分别测量清洁的 CdZnTe晶片和蒸Au后的晶体表面内层Cd 4d 芯能级和价带结构

费米边

The photoemission spectra of clean CdZnTe(110) surface without Au The photoemission spectra of clean CdZnTe(110) surface with Au

同步辐射光电子能谱法(SRXPS)可以直接测 算势垒高度而不受金属-半导体接触界面的缺陷以 及缺陷引起的空间电荷区变化的影响。在超高真 空条件下对晶片进行原位金属沉积,根据金属沉 积前后芯能级的偏移来计算势垒高度。接触势垒 高度的计算公式为,

B ,P E B EV C

式中,ΦB, p为接触势垒高度,EB为镀金金属后芯能 级,EV-C为芯能级与价带顶的距离。

探针的参考电极( 功函数已知) 与样品组成振动式平板电容C, 由于两电极的功函数不同而 产生的接触电势差等效为:

当探针相对样品振动时,电容C的改变就会产生位移电流:

对样品外加一补偿电压使位移电流为零,此时的补偿电压值就是样品与探针的功

函数之差。

Fig.2 Electronic energy levels of the sample and AFM tip for three cases: (a) tip and sample are separated by distance d with no electrical contact, (b) tip and sample are in electrical contact, and (c) external bias (Vdc ) is applied between tip and sample to nullify the CPD