“101”序列检测器

时序电路设计-101序列检测器

数字逻辑设计及应用课程设计报告姓名:雷蕾学号:2010012030036选课号:设计题号: 5一.设计题目:设计101序列检测器二.设计要求要求使用状态机设计一个序列检测器,检测输入数据,当输入中出现101时,输出1,否则输出为0。

不进行重复判断,即当出现10101…时,输出为00100…判断的具体流程如下:1.电路复位,进入状态S0,等待输入2.S0状态下:如果输入为0,则停留在S0,如果输入为1,则跳转到S13.S1状态下:如果输入为0,则跳转到S2,如果输入为1,则停留在S14.S2状态下:如果输入为1,则输出1,并跳转到S0,如果输入为0,则输出0,并跳转到S0检测器电路实现:时钟信号,1 bit输入待判断信号,1bit输出判断结果。

三.设计过程1.设计方案:通过使用ISE编写verilog语言,实现以下过程:1s3只有当s3接收到的输入信号为1的时候,输出才会为1,其余时候输出都为0.2.设计程序:模块文件:`timescale 10ns/1ns//////////////////////////////////////////////////////////////////////////////////// Company:// Engineer://// Create Date: 21:02:40 06/06/2012// Design Name:// Module Name: abcd// Project Name:// Target Devices:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://////////////////////////////////////////////////////////////////////////////////// module abcd(input reset,input clk,input ipt,output reg result);parameter [1:0] s0 = 2'b00, s1 = 2'b01, s2 = 2'b10;reg[1:0] state;always @ (posedge clk)beginif(reset)beginstate<=s0;result<=0;endelsebegincase(state)s0:beginif(ipt==0)beginstate<=s0;result<=0;endelse.beginstate<=s1;result<=0;endends1:beginif(ipt==0)beginstate<=s2;result<=0;endelsebeginstate<=s1;result<=0;endends2:beginif(ipt==0)beginstate<=s0;result<=0;endelsebeginstate<=s0;result<=1;endenddefault:beginstate<=s0;result<=0;endendcaseendendendmodule测试文件:`timescale 10ns / 1ps////////////////////////////////////////////////////////////////////////////// //// Company:// Engineer://// Create Date: 23:05:50 06/06/2012// Design Name: test_detector// Module Name: D:/TDDOWNLOAD/fortwo2/haha.v// Project Name: fortwo2// Target Device:// Tool versions:// Description://// Verilog Test Fixture created by ISE for module: test_detector//// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://////////////////////////////////////////////////////////////////////////////// //module haha;module test_detector();reg clk;reg reset;reg ipt;wire result;reg[20:0] indata=20'b101001110011011110110;integer i;initial clk=1;always #1 clk=~clk;initialbeginreset=1;ipt=0;#4reset=0;for(i=0;i<21;i=i+1)beginipt=indata[i];#2;end#10$stop;endabcd detector_instance(.clk(clk),.reset(reset),.ipt(ipt),.result(result));endmodule3.仿真结果四.设计结论(包括:设计结果分析、设计中遇到的问题、设计心得和体会等) 1.设计结果分析:以时钟信号的一个周期为基准,有仿真结果可看出,当输入(ipt)为连续的一个周期高一个周期的低一个周期的高(即101)时,输出(result)为高。

【免费阅读】康华光数电复习题

第二章2.1.3 用逻辑代数定律证明下列等式:(3)ECD A E D C CD A C B A A ++=++++)(解: ECD A E CD CD A ECD CD A A ECD CD A C B A A ED C CD A C B A A ++=++=++=+++=++++)()()(2.1.4 用代数法化简下列各式:(6)A BA B BA B BA B A B A BA B A B A B A BA B A B A B A =∙=+=++=∙++=∙++++2.1.5 将下列各式转换成与-或表达式:(3)CA D C D AB CA B D C C B D A B A B A C B D B C A ABBC BD AC ABBC BD AC +++=+++++=+++++=⋅+⋅=⋅⋅⋅))(())((2.1.7 利用与非门和非门实现下列函数:(3)DC B AD C B A L ⋅=++=))((2.2.3 用卡诺图法化简下列各式:(3)CB A D BCD AB D C B CD B A C B A D B C A D C B D CD B A ++++=+⋅++++)()(AB CD000111100001111011111111DC AD B D B A ⋅++= 3(7)∑∑+=)11,10,9,3,2,1()15,14,13,0(),,,(d m D C B A L ADAC B A ++=第四章4.1.1(a )试写出图所示逻辑电路的真值表。

解:逻辑电路的输出表达式为: 列出真值表如表所示。

A B C L0 0 0 10 0 1 10 1 0 10 1 1 11 0 0 01 0 1 11 1 0 11 1 1 14.2.7某足球评委会由一位教练和三位球迷组成,对裁判员的判罚进行表决。

当满足以下条件时表示同意:有三人或三人以上同意,或者有两人同意,但其中一人是教练。

序列检测器实验报告

序列检测器设计实验内容:设计一个1110010序列检测器,即检测器检测到序列1110010时,输出为1,否则输出为0。

输入信号:一个时钟输入信号clk;一个输入端x以输入序列来检测;一个输入y用来选择是检测序列1110010或是检测自己输入的序列;一个输入k(7..0)用来输入想要检测器检测的序列;输出信号:一个7位输出信号q,用来输出正在检测的7位序列;一个1位输出信号unlk,当被检测序列符合时,输出unlk为1否则为0;中间信号:再定义两个7位的中间信号a和combination;执行操作:在上升的时钟沿时候,将从x输入的序列赋给7位a,在y等于1的情况下,令中间信号combination为1110010,否则,在y等于0的情况下,令中间信号combination为从k输入的七位长序列。

最后把a的值赋给q,如果a与combination输出unlk等于1否则等于0。

(1)序列检测器语言设计:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;USE IEEE.STD_LOGIC_ARITH.ALL;entity xulie2 isport (clk,x:in std_logic;y:in std_logic;k:in std_logic_vector(7 downto 1);unlk:out std_logic;q:out std_logic_vector(7 downto 1)); end xulie2;architecture art of xulie2 issignal a:std_logic_vector(7 downto 1);signal combination: std_logic_vector(7 downto 1);beginprocess(clk)beginif clk'event and clk='1' thena<=a(6 downto 1)&x;if y='1' thencombination<="1110010";else combination<=k;end if;end if;q<=a;end process;unlk<='1' when(a=combination) else '0';end art;序列检测器波形图:其中ENDTIME=10.0us GRIDSIZE=100.0ns波形图分析:如图,选择输入端y输入为1时,q对应着输出从x输入的7位序列,如果从x输入的待检测的7位序列为1110010时,unlk为1,否则为0,当选择输入端y输入为0时,q依旧对应着输出从x输入的待检测的当前7为序列,但是只有当从x输入的7为序列与从k输入的7位序列一致时,输出端unlk才为1,否则为0。

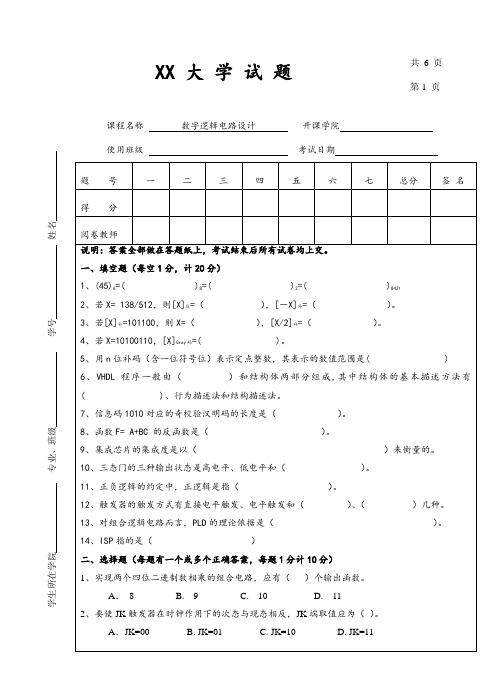

数字逻辑模拟试卷附答案

XX 大 学 试 题课程名称 数字逻辑电路设计 开课学院使用班级 考试日期苏 大 学 试题 第3 页苏大 学 试题第4 页四、根据下图波形写出其逻辑关系表达式Z=F(A,B,C) (10分)A B C Z五、分析题:某同步时序逻辑电路如图所示。

(12分)(1) 写出该电路激励函数和输出函数; (2) 画出输出矩阵和激励矩阵; (3) 画出状态表和状态图;(4)设各触发器的初态均为0,试画出下图中Q1、Q2和Z 的输出波形。

数字逻辑模拟试卷2答案一、填空题(每空1分,计20分) 1、(45)6=(35)8=(11101)2=(00101001)84212、若X= 138/512,则[X]反=(0.01000101),[-X]补=(1.10111011)。

3、若[X]补=101100,则X=(-100100),[X/2]补=(110110)。

4、若X=10100110,[X]Gray 码=(11110101)。

5、用n 位补码(含一位符号位)表示定点整数,其表示的数值范围是(-2n-1~2n-1-1)6、VHDL 程序一般由(实体)和结构体两部分组成,其中结构体的基本描述方法有(数据流描述法)、行为描述法和结构描述法。

7、信息码1010对应的奇校验汉明码的长度是(7位)。

8、函数F= A+BC 的反函数是()(C B A )。

9、集成芯片的集成度是以(等效门电路的数量)来衡量的。

10、三态门的三种输出状态是高电平、低电平和(高阻状态)。

11、正负逻辑的约定中,正逻辑是指(高电平表示1;低电平表示0)。

12、触发器的触发方式有直接电平触发、电平触发和(脉冲触发)、(边沿触发)几种。

13、对组合逻辑电路而言,PLD 的理论依据是(任何组合逻辑函数都可以用与-或式表示)。

14、ISP 指的是(在系统可编程技术)二、选择题(每题有一个或多个正确答案,每题1分计10分)1、A2、D3、B ,C4、A ,D5、A ,B ,D6、A ,B ,C7、A ,B ,C8、B9、B ,D 10、C 三、按要求化简下列函数(14分)1.用代数法求函数 F = A B + A B C + B C 的最简“与-或”表达式。

RI101检测器说明书

连接管,将连接管的另一端插入废液瓶内,不要加背压。

【警惕】 当与其它检测器并联时应把该检测器放在最后

【警惕】 如果检测器内的流动相冻结就可能会损坏仪器,如果在放置或储藏的

过程中有可能会导致流动相的冻结,则应把检测器流路中的流动相放

干。

【警惕】 当流动相中含有高浓度的盐时用完后一定要用水彻底的冲洗,否则将

9

4. 检测原理

4-1 光学系统

如图4.1所示,对于偏转式示差折光检测器,光路在通过两个装有不同液体的检测池 时发生偏转,偏转的大小与两种液体之间折光率的差异成比例。光路的偏转由光敏 元件上的位移测得,显示了折光率的不同。

图 4.1 偏转式示差折光检测器的检测原理

1. 光束 2. 样品腔 3. 参比腔 4. ns nr 时的光束 5. ns=nr 时的光束 6. 位移 7. 光敏接收元件 ns:样品腔中液体的折射率 nr:参比腔中液体的折射率

【注意】 除了仪器所附的信号线不要在信号输出终端连接任何ห้องสมุดไป่ตู้他的线。

4

【注意】 【注意】

【注意】

使用完全彻底冲洗的流动相推荐使用Shodex DEGAS在线冲洗机它具 有操作简便可连续冲洗的优点。 如果替换的流动相与原流动相不互溶,在排出旧的流动相后用与此两 个流动相均能互溶的溶剂清洗,然后再充入新的流动相。例如用氯仿 来替换水时,则先用丙酮清洗流路再充入氯仿。 当用含有机溶剂的流动相来替换含盐的流动相时,在充入含有机溶剂 的流动相之前,先用纯水再用丙酮冲洗流路。反之,当用含盐的流动 相来替换含有机溶剂的流动相时,在充入含盐流动相前应先用丙酮再 用纯水冲洗。

保证条件:

除了Showa Denko K.K.公司正式授权的代理所签署的和专门发布的书面保证书,对 于Shodex RI-101示差折光检测器的质量,性能,工艺,系统适用性,及其销路不提 供任何明示或暗示的、书面或口头的、成文或其他的担保。

使用D触发器设计一个11001序列检测器

使用D触发器设计一个11001序列检测器讨论使用D触发器设计一个11001序列检测器,讨论序列可交迭(Overlap)检测和不可交迭检测在设计上的区别,讨论分别采用Mealy机设计和采用Moore机设计的区别,讨论未用状态的处理问题。

【要求】给出电路原理图或HDL代码,要求进行仿真,并给出仿真结果。

1.原件介绍D触发器(74LS74)、“与”门(74LS08)、“或”门(74LS32)、“非”门(74LS04),集成电路引脚2.设计思路根据要求,设计的序列检测器有一个外部输入x 和一个外部输出Z 。

输入和输出的逻辑关系为:当外部输入x 第一个为"1",外部输出Z 为"0";当外部输入x 第二个为"1",外部输出Z 为"0";当外部输入第三个x 为"0",外部输出Z 为"0",当外部输入第四个x 为“0”,外部输出Z 为0,当外部输入第五个x 为“1”,输入X 0 1 1 1 0 0 1 0 1 输出Y 0 0 0 0 0 0 1 0 0要判别序列检测器是否连续接收了"11001",电路必须用不同的状态记载外部输入x 的值。

假设电路的初始状态为A ,x 输入第一个"1",检测器状态由A 装换到B ,用状态B 记载检测器接受了"11001"序列的第一个"1",这时外部输出Z=0;x 输入第二个"1",检测器状态由B 装换到C ,用状态C 记载检测器接了“11001”序列的第二个"1",外部输出Z=0;x 输入第三个"0",检测器状态由C 装换到D ,外部输出Z=0;x 输入第四个为“0”,检测器状态由D 装换到E ,外部输出Z=0;x 输入第五个为“1”,检测器状态由E 装换到F ,外部输出Z=1。

李昂“101”序列检测器

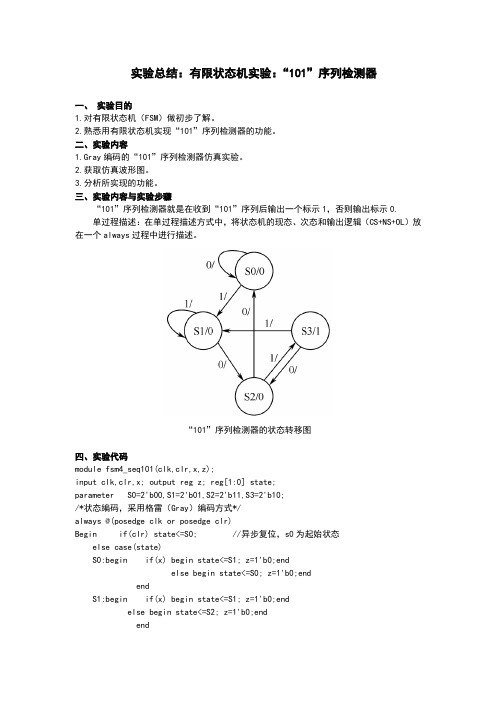

实验总结:有限状态机实验:“101”序列检测器一、实验目的1.对有限状态机(FSM)做初步了解。

2.熟悉用有限状态机实现“101”序列检测器的功能。

二、实验内容1.Gray编码的“101”序列检测器仿真实验。

2.获取仿真波形图。

3.分析所实现的功能。

三、实验内容与实验步骤“101”序列检测器就是在收到“101”序列后输出一个标示1,否则输出标示0.单过程描述:在单过程描述方式中,将状态机的现态、次态和输出逻辑(CS+NS+OL)放在一个always过程中进行描述。

“101”序列检测器的状态转移图四、实验代码module fsm4_seq101(clk,clr,x,z);input clk,clr,x; output reg z; reg[1:0] state;parameter S0=2'b00,S1=2'b01,S2=2'b11,S3=2'b10;/*状态编码,采用格雷(Gray)编码方式*/always @(posedge clk or posedge clr)Begin if(clr) state<=S0; //异步复位,s0为起始状态else case(state)S0:begin if(x) begin state<=S1; z=1'b0;endelse begin state<=S0; z=1'b0;endendS1:begin if(x) begin state<=S1; z=1'b0;endelse begin state<=S2; z=1'b0;endendS2:begin if(x) begin state<=S3; z=1'b0;endelse begin state<=S0; z=1'b0;endendS3:begin if(x) begin state<=S1; z=1'b1;endelse begin state<=S2; z=1'b1;endenddefault:begin state<=S0; z=1'b0;end /*default语句*/ endcaseendendmodule。

101序列检测器原理

101序列检测器原理你想啊,就像我们在生活里找东西一样,这个序列检测器呢,就是在一堆数字或者信号里找特定的“宝贝”,这个宝贝就是101这个序列啦。

那它到底是怎么做到的呢?这就像是一场超级有趣的寻宝游戏呢。

我们先得有个小“机关”,这个机关就是状态机啦。

状态机就像是一个有着不同状态的小机器人,它可以在不同的情况下做出不同的反应。

比如说,最开始的时候,它有个初始状态,就像是小机器人在休息,啥都还没开始找呢。

当它接收到第一个信号的时候,如果这个信号是1,那它就会进入一个新的状态,这个状态就像是小机器人开始警觉起来啦,觉得可能找到了宝贝的开头。

要是这个信号是0呢,那它就还在初始状态,就像小机器人打了个盹儿,觉得还不是时候。

然后呢,当它处于那个警觉状态的时候,如果下一个信号是0,那它就进入到一个中间状态啦,这个状态就像是小机器人在心里默默记着,已经有了个1,现在又有个0,离目标更近一步喽。

要是下一个信号是1呢,那它就得回到初始状态重新开始找啦,就像小机器人发现自己找错了路,得重新出发。

当它在中间状态的时候,如果下一个信号是1,哇塞,那就找到了101这个宝贝啦,小机器人就可以欢呼起来啦,就像我们找到了藏起来的小糖果一样开心。

要是下一个信号是0呢,那它又得回到初始状态重新开始找喽。

这个101序列检测器啊,在实际生活里用处可大啦。

比如说在数字通信里,就像是一个超级小侦探。

它能在那些乱乱的数字信号流里,把101这个特定的序列给找出来。

这就好比在一堆信件里,找到一封特别标记的信一样。

再想象一下,在电路里呢,它也像是一个聪明的小管家。

电路里有各种各样的信号在跑来跑去,101序列检测器就能把那些符合101序列的信号给挑出来,然后进行特殊的处理,就像小管家把特别的东西单独放到一个小盒子里一样。

而且哦,这个原理其实也没有那么难理解啦。

就像我们玩游戏的时候,有一定的规则,按照规则走就能达到目的。

101序列检测器也是按照它自己的小规则,在那些数字或者信号里游刃有余地找到目标。