七人表决器

七人表决器实验

3.3实验三七人表决器设计3.3.1实验目的1、掌握用QuartusII软件设计基本数字系统流程及注意事项。

2、进一步熟练掌握程序的编译、仿真、生成模块及芯片引脚号码锁定方法。

3、掌握分层设计的方法和注意事项4、在实验报告中,总结数字系统设计步骤及注意事项。

3.3.2实验内容基于QuartusII软件及VHDL语言实现七人表决器。

当参与表决的7人中有4个或4个以上赞同时,表决器输出“1”表示通过,否则输出“0”表示不通过,并显示赞成和反对的人数。

用7个开关作为表决器的7个输入变量,数码管显示人数,LED灯显示是否通过。

本实验4学时。

3.3.3实验仪器ZY11EDA13BE型实验箱。

3.3.4实验原理分析实验要求,七人表决器系统主要由两个模块构成:投票计数模块和数码管显示模块。

一、建立项目(1)新建文件夹。

路径及文件名中不可出现汉字。

(2)新建项目。

一个数字系统可以由多个模块构成,使所有模块连接在一起的总文件叫做顶层文件,只有顶层文件名可以且必须与项目名相同。

项目取名为bjq7。

(3)选择芯片二、建立文件首先,建立各个VHDL功能模块。

1.投票计数模块。

(1)新建VHDL文件编辑VHDL程序。

投票计数模块输入为七个电平开关input,输出为同意的人数agree,反对的人数disagree,是否通过指示灯y,程序清单如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity BJQ isport(input:in std_logic_vector(6downto0);七个输入开关agree:out std_logic_vector(3downto0);同意的人数disagree:out std_logic_vector(3downto0);不同意的人数y:out std_logic);是否通过标志end;architecture one of BJQ isbeginprocess(input)variable cnt:integer range0to7;variable cnt0:integer range0to7;begincnt:=0;for i in6downto0loopif input(i)='1'thencnt:=cnt+1;end if;end loop;cnt0:=7-cnt;if cnt>3then y<='0';else y<='1';end if;case cnt iswhen0=>agree<="0000";when1=>agree<="0001";when2=>agree<="0010";when3=>agree<="0011";when4=>agree<="0100";when5=>agree<="0101";when6=>agree<="0110";when7=>agree<="0111";when others=>agree<="0000";end case;case cnt0iswhen0=>disagree<="0000";when1=>disagree<="0001";when2=>disagree<="0010";when3=>disagree<="0011";when4=>disagree<="0100";when5=>disagree<="0101";when6=>disagree<="0110";when7=>disagree<="0111";when others=>disagree<="0000";end case;end process;end;程序输入完成后进行保存,名字与实体名一致BJQ。

七人表决器设计设计报告

七人表决器设计一.设计要求1. 能够完成七人表决的功能,并且直观的显示结果:决议通过显示字母P,否则显示字母E;2.能够选择显示表决双方的人数,有控制开关与显示指示灯,并且能够实时的显示反对与赞成的人数;3.能够选择是否记名,并有指示灯显示。

当选择记名时,与表决参与者相对应的指示灯亮起;4.不设置弃权的状况,超过三人同意则表示决议通过。

二.设计思路1.使用Altera的Cyclone II器件,FPGA型号为EP2C35F672C6N;开发平台为Quartus II 8.02.使用6个拨动开关用以进行表决,开关闭合时表示同意,断开时表示不同意;3.使用6个LED用以显示表决的个人结果,用以显示记名时的情况。

LED亮起表示表决人同意,否则表示不同意;4.使用一个七段数码管用以显示表决结果,通过显示P,否则显示E;另外使用两个数码管用以分别显示同意与不同意的人数;5.使用两个拨动开关控制是否记名,是否显示表决的人数结果;6.其他电路按需要搭建。

三.硬件系统组成框图注释:set:选择是否记名set1:选择是否显示投票人数及比例xin[0:6]:表决输入,分别是七个拨动开关sel:输出指示是否记名投票sel1:输出指示是否显示投票人数及比例xout[0:6]:译码用数码管输出表决是否通过xout0[0:6]:译码用数码管输出同意的人数(set1=1)xout1[0:6]:译码用数码管输出不同意同意的人数(set1=1)xout2[0:6]:译码用七个LED输出记名结果设计HDL源程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity biao isport (set, set1: in std_logic ; ----控制按键xin: in std_logic_vector ( 6 downto 0 ); ----按键输入表决sel,sel2: out std_logic; -------控制指示灯xout,xout0,xout1,xout2 : out std_logic_vector ( 6 downto 0 )); ----xout显示结果,xout0显示否决的人数,xout1赞成的人数,xout2 LED输出end entity ;architecture bev of biao isbeginprocess ( xin ,set,set1)variable j: integer :=0;beginj:=0;for i in 0 to 6 loop ------统计同意的个数if xin(i)='1' thenj:=j+1;end if;end loop;if (set='1') then -------是否记名投票sel<='1';xout2<=xin; -------记名投票elsesel<='0';xout2<="0000000";end if;if j>3 then ------判决是否表决通过并输出结果xout<="0001100"; ----数码管显示Pelse xout<="0000110"; -----数码管显示Eend if;if set1='1' then ------是否显示表决比例sel2<='1'; ------显示指示灯亮并且译码输出同意与不同意的数目case j is ------显示赞成的人数when 0 =>xout1<="1000000";when 1 =>xout1<="1111001";when 2 =>xout1<="0100100";when 3 =>xout1<="0110000";when 4 =>xout1<="0011001";when 5 =>xout1<="0010010";when 6 =>xout1<="0000010";when 7 =>xout1<="1111000";when others =>xout1<="XXXXXXX";end case;case j is ------显示不赞成的人数when 7 =>xout0<="1000000";when 6 =>xout0<="1111001";when 5 =>xout0<="0100100";when 4 =>xout0<="0110000";when 3 =>xout0<="0011001";when 2 =>xout0<="0010010";when 1 =>xout0<="0000010";when 0 =>xout0<="1111000";when others =>xout0<="XXXXXXX";end case;else ------不显示表决比例sel2<='0';xout0<="1111111"; ----不显示数字xout1<="1111111";end if;end process;end architecture bev;四.DE2平台仿真1.在Quartus中打开已经建好的工程文件;2.按要求选择设备并且分配管脚,重新编译,连接实验板的电源线与下载线,下载程序文件3.分别拨动开关sw0到sw6,看是否能够满足基本要求;在分别拨动sw16,sw17,看是否能够按要求显示表决人数结果与对应的LED灯是否正常亮与灭。

7人表决器设计设计任务书

引导文3

7人表决器设计任务书

姓名

页 数:

一、项目描述

1、项目工作要求(任务书)

请根据要求设计7人表决器,要求如下:

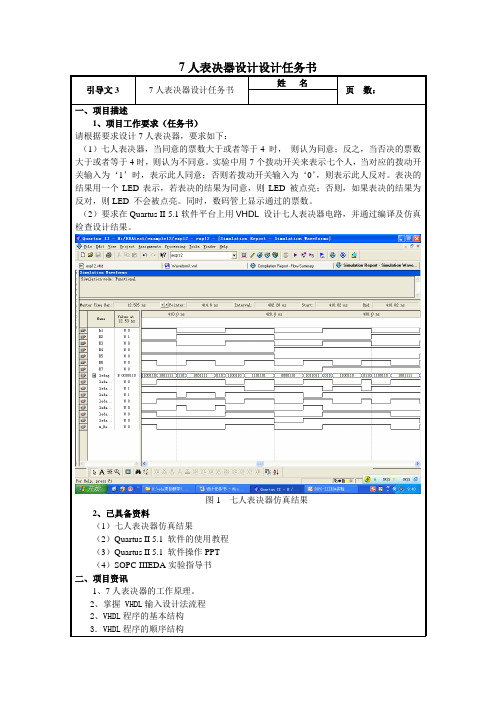

(1)七人表决器,当同意的票数大于或者等于4时,则认为同意;反之,当否决的票数大于或者等于4时,则认为不同意。实验中用7个拨动开关来表示七个人,当对应的拨动开关输入为‘1’时,表示此人同意;否则若拨动开关输入为‘0’,则表示此人反对。表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。同时,数码管上显示通过的票数。

(2)要求在Quartus II5.1软件平台上用VHDL设计七人表决器电路,并通过编译及仿真检查设计结果。

图1七人表决器仿真结果

2、已具备资料

(1)七人表决器仿真结果

(2)Quartus II5.1软件的使用教程

(3)Quartus II5.1软件操作PPT

(4)SOPC-IIIEDA实验指导书

二、项目资讯

4、整理相关资料,列表说明项目资料及资料来源,注明存档情况。

项目名称

项目资料名称

资料来源

存档备注

5、成品上交资料备注。

项目名称

上交资料名称

七、备注(需要注明的内容)

指导老师评语:

项目完成人签字: 日期: 年 月 日

指导老师签字: 日期: 年 月 日

辅助设备

备注

四、项目决策

1、分小组讨论,分析阐述各自的设计方案和设计电路。

2、老师指导确定最终设计方案和设计电路。

3、每组选派一位成员阐述设计方案。

五、项目实施

1、设计前的准备工作具体有哪些?

2、Quartus IIVHDL设计时要注意哪些事项?

实验2七人表决器概要

1

ZY11EDA13BE实验箱简介

2

1. 实验箱俯视图

3

本实验箱采用先进的主板+适配板+扩展板的灵活 结构,并采用ALTERA公司ACEX系列3万门的 FPGA器件EP1K30QC208-2为核心处理芯片。提 供1968个寄存器,24576个存储位,30000个典型门 ,因此EP1K30非常适合于构建复杂逻辑功能和存 储功能。

8

电源的打开顺序是:先打开交流开关,再打开直流开关, 最后打开各个模块的控制开关。电源关掉的顺序刚 好相反。

9

4用配置/编程模块,可以使 用本模块对ALTERA、LATTICE、XILINX等国际著名P LD公司的几乎所有isp器件或FPGA/CPLD器件进行编程 下载并且能自动识别目标器件。

43

3)锁定后重新编译;

引脚重新定义后必须再通过编译器 “Compile”对文件重新进行编译,以 便将引脚信息编入下载文件中。此时 回到原来的设计文件“7vote.gdf”上 的输入输出信号旁都标有其对应的管 脚号。

44

编程下载

1)将25针下载电缆线一端插入LPT1(打印 机口即并行口),另一端连接到实验箱主板 系统的通用编程模块DB25接口,再用十针连 接线一端插入该模块JTAG下载接口固定不变, 另一端连接到主板系统的配置模块中目标芯 片的下载接口,打开系统主板电源。

4

2. 核心芯片俯视图

5

EP1K30包含一个嵌入式阵列来完成存储功能, 一个逻辑阵列来完成通用逻辑功能和众多的引 脚从而使其可以作为接口与系统组件有效连接。 做实验时切记不要用手触摸核心芯片A,静电可 能会损坏此贴片芯片。

6

3. 电源模块

7

电源模块包括3个开关,7个电压输出插孔。其 中交流开关用于打开从220V交流电源接入的内部 变压器,为实验箱提供基本工作电源。打开交流 开关,电源指示灯PL0亮,实验箱进入待机状态。 按钮开关APW1用于打开主板中模块工作电源,按 下APW1后,电源指示灯PL1亮,实验箱进入工作 状态,为系统提供+5V,+3.3V,+2.5V,+1.8V电源 。 按钮开关APW2用于打开+12V,-12V电源,按 下APW2后,电源指示灯PL2、PL3亮。

数电—七人多路表决器

(1)电路状态转换图:(4)七人表决器电路设计:六.设计源程序与电路图绘制(1)或门的设计源程序:--or2_1.vhdLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY or2_1 ISPORT(A,B:IN STD_LOGIC;C:OUT STD_LOGIC);END ENTITY or2_1; ARCHITECTURE art1 OF or2_1 IS BEGINC<=A Or B;END ARCHITECTURE art1;(2)半加器的设计源程序:--h_adder.vhdLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY h_adder ISPORT(A,B:IN STD_LOGIC;SO,CO:OUT STD_LOGIC); END ENTITY h_adder; ARCHITECTURE art2 OF h_adder IS BEGINSO<=NOT(A XOR(NOT B));CO<=A AND B;END ARCHITECTURE art2;电路图:(3)全加器的设计源代码:--f_adder.vhdLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY f_adder ISPORT(AIN,BIN,CIN:IN STD_LOGIC;SUM,COUT:OUT STD_LOGIC); END ENTITY f_adder; ARCHITECTURE art3 OF f_adder IS COMPONENT h_adder ISPORT(A,B:IN STD_LOGIC;SO,CO:OUT STD_LOGIC); END COMPONENT h_adder; COMPONENT or2_1 ISPORT(A,B:IN STD_LOGIC;C:OUT STD_LOGIC);END COMPONENT or2_1;SIGNAL S1,S2,S3:STD_LOGIC;BEGINU1:h_adder PORT MAP(A=>AIN,B=>BIN,CO=>S1,SO=>S2);U2:h_adder PORT MAP(A=>S2,B=>CIN,CO=>S3,SO=>SUM); U3:or2_1 PORT MAP(A=>S1,B=>S3,C=>COUT);END ARCHITECTURE art3;电路图:(4)七人表决器设计电路:七.电路仿真仿真波形图:引脚锁定:。

七人表决器实验报告

七人表决器实验报告七人表决器实验报告引言:在日常生活中,我们经常会遇到需要做决策的情况。

而在集体决策中,如何快速、公正地达成共识成为了一个重要的问题。

为了解决这一问题,我们进行了七人表决器的实验。

本实验旨在探索七人表决器在集体决策中的效果和影响因素。

实验设计:我们邀请了七位志愿者参与实验,每个人都具有不同的背景和观点。

在实验开始前,我们向每位参与者提供了相同的决策问题,并要求他们独立思考并给出自己的答案。

然后,我们将七人表决器放置在桌面上,并告知参与者如何使用。

在每次决策中,参与者需要将自己的决策结果输入到表决器中,然后等待其他人完成决策。

当所有参与者完成决策后,表决器会自动计算出最终的决策结果。

实验结果:通过观察实验过程和分析实验数据,我们得出了以下结论:1. 影响决策结果的因素:参与者的个人观点、决策顺序以及决策权重等因素都可能影响最终的决策结果。

在实验中,我们发现当个人观点相差较大时,决策结果往往会偏向于多数人的意见。

而当个人观点相似或相同时,决策结果则更容易达成一致。

2. 决策效率的提升:相比于传统的集体讨论和投票方式,七人表决器在决策效率上具有明显的优势。

参与者只需输入自己的决策结果,无需进行冗长的讨论和辩论过程,从而节省了时间和精力。

3. 决策公正性的保障:七人表决器在一定程度上保障了决策的公正性。

由于每个参与者的决策权重相等,没有任何一方能够主导决策结果。

这种平等的决策机制能够避免个别参与者的意见被忽视或压制,从而提高了决策的公正性。

讨论:尽管七人表决器在决策效率和公正性方面具有优势,但仍存在一些潜在的问题和限制。

首先,由于每个参与者只能输入一个决策结果,可能无法充分体现个体的多样性和复杂性。

其次,决策结果可能受到决策顺序的影响,先行决策者的意见可能会对后续决策者产生影响。

此外,表决器本身的设计和算法也可能存在一定的偏差,需要进一步优化和改进。

结论:通过本次实验,我们初步探索了七人表决器在集体决策中的应用。

七人表决器——精选推荐

七人表决器一:实验目的1.掌握用VHDL硬件描述语言做数字电路综合和设计的方法。

2.熟练掌握程序的编译,仿真,生成模块及引脚号码锁定方法并下载到目标芯片。

二:实验仪器ZY11EDA12BE三:实验要求设计一个七人表决电路,当参与表决的7人中有4人或4人以上赞同时,表决器输出“1”表示通过,否则输出“0”表示不通过。

实验时,可用7个电平开关作为表决器的7个输入变量,输入“1”表示表决者“赞同”输入“0”表示表决者“不赞同”。

可在上述电路的基础上,增加数码管显示功能,显示赞同和不赞同的票数。

四:实验原理根据设计任务要求,实验电路如上图,其中key表示七个输入cp为输入脉冲,result为表决结果显示,seg[6。

0]为送数码管显示结果,sel为选择要显示的数码管其vhdl语言编写后连接,程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity biaojue isport (cp:in std_logic;key_in:in std_logic_vector(6 downto 0);result:out std_logic;seg_out:out std_logic_vector(6 downto 0);sel:out std_logic_vector(2 downto 0));end biaojue;architecture arc of biaojue issignal sum:std_logic_vector(3 downto 0);signal seg1,seg0:std_logic_vector(6 downto 0);signal sel1: std_logic_vector(2 downto 0);beginprocessvariable sum1:std_logic_vector(3 downto 0);beginsum1:="0000";for i in 0 to 6 loopif key_in(i)='1' thensum1:=sum1+"0001";elsesum1:=sum1;end if;end loop;sum<=sum1;if sum(2)='1' thenresult<='1';elseresult<='0';end if;case sum iswhen "0000"=>seg1<="0111111";seg0<="0000111";when "0001"=>seg1<="0000110";seg0<="1111101";when "0010"=>seg1<="1011011";seg0<="1101101";when "0011"=>seg1<="1001111";seg0<="1100110";when "0100"=>seg1<="1100110";seg0<="1001111";when "0101"=>seg1<="1101101";seg0<="1011011";when "0110"=>seg1<="1111101";seg0<="0000110";when"0111"=> seg1<="0000111";seg0<="0111111";when others=>seg1<="0000000";seg0<="0000000"; end case;end process;process(cp)beginif(cp'event and cp='1') thenif sel1<="001"thensel1<="000";else sel1<=sel1+"001";end if;end if;end process;sel<=sel1;process(cp)beginif(cp'event and cp='1')then--sel<=sel1;if sel1="001"thenseg_out<=seg0;--sel<=sel1;elsif sel1="000" thenseg_out<=seg1;--sel<=sel1;end if;end if;end process;end arc;五:管脚锁定输入:1.掌握了用vhdl语言常用的设计方法,原理图和vhdl语言硬件描述法2.理解动态扫描电路的基本原理并实现七:参考资料《EDA技术习题与实践》《EDA与数字系统设计》。

EDA 七人表决器设计

EDA 课程设计报告书课题名称 七人表决器设计姓 名学 号 院、系、部 电气系专 业 电气工程及其自动化指导教师2010年 7 月3日※※※※※※※※※ ※※ ※※ ※※ ※※※※※※※※※2007级EDA课程设计七人表决器设计一、设计目的1.熟悉Quartus II软件的使用。

2.熟悉七人表决器的工作原理3.熟悉EDA开发的基本流程。

二、设计要求表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器由七个人来投票,当同意的票数大于或者等于4人时,则认为同意;反之,当否决的票数大于或者等于4人时,则认为不同意。

实验中用7个拨挡开关来表示七个人,当对应的拨挡开关输入为‘1’时,表示此人同意;否则若拨挡开关输入为‘0’时,则表示此人反对。

表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

同时用七段显示数码管来显示同意的人数。

三、电路及连线设计管脚分配:实验符号对应附录符号管脚K1 K1 PIN_74K2 K2 PIN_73K3 K3 PIN_38K4 K4 PIN_39K5 K5 PIN_44K6 K6 PIN_45K7 K7 PIN_46A A 62B B 61C C 60D D 59E E 58F F 57G G 56m_Result D1_1 PIN_215四、使用说明本设计就是利用EDA/SOPC-II+实验箱中的拨挡开关模块和LED模块来实现一个简单的七人表决器的功能。

拨挡开关模块中的K1~K7表示七个人,当拨挡开关输入为‘1’时,表示对应的人投同意票,否则当拨挡开关输入为‘0’时,表示对应的人投反对票;LED模块中D1_1表示七人表决的结果,当D1_1点亮时,表示一致同意,否则当D1_1熄灭时,表示一致反对。

五、流程图设计六、程序设计如下:library ieee;use ieee.std_logic_1164.all;USE IEEE.STD_LOGIC_UNSIGNED.ALL;entity biao isport ( reset : in std_logic ;xin: in std_logic_vector ( 6 downto 0 );sel: out std_logic;xout : out std_logic_vector ( 6 downto 0 );xout1 : out std_logic_vector ( 6 downto 0 ));end entity ;architecture bev of biao isbeginprocess ( xin )variable j: integer :=0;beginj:=0;for i in 0 to 6 loopif xin(i)='1' thenj:=j+1;end if;end loop;case j iswhen 0 => xout1 <= "1000000" ;when 1 => xout1 <= "1111001" ;when 2 => xout1 <= "0100100" ;when 3 => xout1<= "0110000" ;when 4 => xout1 <= "0011001" ;when 5 => xout1 <= "0010010" ;when 6 => xout1 <= "0000010" ;when 7 => xout1 <= "1111000" ;when others => null;end case;if j>3 thenxout<="1110011";sel<='1';else xout<="1111001";sel<='0';end if;end process;end architecture bev;七、设计总结:通过这段时间的EDA课程设计,我更加熟练的掌握了EDA开发的基本流程,熟练的使用Quartus II软件进行编程,在大家的努力之下,我们完成了七人表决器的相关设计,在此我要感谢我的组员和在EDA设计中给于我们很多帮助的老师们。

文档 - 副本单片机七人表决器

单片机又称单片微控制器,它不是完成某一个逻辑功能的芯片,而是把一个计算机系统集成到一个芯片上,它体积小,质量轻,价格便宜,为学习、应用和开发提供了便利条件。

近几年来,开发推出单片机的公司很多,各种高性能单片机芯片市场也异常活跃,新技术不断采用,更加是单片机的种类、性能及应用领域不断扩大和提高,单片机已经在各个领域受到广泛应用。

本题就是基于单片机的一个七人表决器设计。

本题以AT89C52单片机为主控芯片,与LED显示灯、开关、七段数码管等共同构成七人表决器。

使用单片机可以使整个系统结构灵活,构成简单,且功能可以扩展或者裁减。

而且现在单片机已经很便宜,整个系统构成成本也不高。

在现实会议中使用电子表决器表决,可以使表决结果更加精确,表决效率大大提高,而且更能体现评为们的意志。

表决器设有赞成、反对开关,开始表决后,只要主持人按结果现实按键,结果就能实时显示出来。

在单片机的教学中,这也是一个很好的案例。

七人表决器包括C51单片机运行程序、表决器电路设计、按键设定、LED显示等模块。

关键词:表决器,单片机,KEIL,proteus仿真。

Single-chip microcomputer and says monolithic micro controller, it is not a complete a logical function chips, but put a computer system integration to a chip, it is small, light quality, the price is cheap, for learning, application and development provides the convenience. In recent years, the development of single chip company launched many, all kinds of high performance microprocessor chip market is very active, new technology is constantly, even more is the single chip microcomputer type, performance and application field to expand and improve, microcontroller has been widely applied in all fields.Ontology based on single chip computer is one of the seven Voter design. Subject to the microcontroller of AT89C52 main control chip, and LED display lights, switch, seven period of digital tube to form a Voter seven people. Using single chip can make the whole system flexible structure, a simple, and function can expand or cuts. And now microcontroller is cheap, the whole system construction cost is not high also.In reality Voter use electronic voting in the meeting, can make the voting results more accurate, voting efficiency greatly improved, and more can reflect the will of the as. Voter has agreed, against switch, began after a vote, as long as the host the buttons in reality, the results can real-time display. In the teaching of the single chip microcomputer, this is also a very good case. Seven people Voter including C51 operation procedures, Voter circuit design, key setting, LED display, and other modules.Keywords:Voter System,singlechip,simulation目录1 前言 (1)2 设计目的与任务 (2)2.1设计目的 (2)2.2设计任务要求 (2)3 方案 (3)3.1方案 (3)3.1.1 方案一 (3)3.1.2 方案二 (4)3.2方案论证 (5)4 设计具体 (6)4.1硬件设计 (6)4.2软件设计 (7)5 说明 (9)6 总结 (11)致谢 (12)参考文献 (13)1 前言此处加入本课题的意义等内容……在计算机出现以前,有不少能工巧匠做出了不少精巧的机械。

实验一七人表决器(1)

第三章数字电路与数字系统设计实验实验一七人表决器一、实验目的1 .初步了解VHDL语言。

2 .学会用行为描述方式来设计电路。

二、实验原理用七个开关作为表决器的7个输入变量,输入变量为逻辑“1”时表示表决者“赞同”;输入变量为“0”时,表示表决者“不赞同”。

输出逻辑“1”时,表示表决“通过”;输出逻辑“0”时,表示表决“不通过”。

当表决器的七个输入变量中有4个以上(含4个)为“1”时,则表决器输出为“1”;否则为“0”。

七人表决器设计方案很多,比如用多个全加器采用组合电路实现。

用VHDL语言设计七人表决器时,也有多种选择。

常见的VHDL语言描述方式有行为描述、寄存器传输(RTL)描述、结构描述以及这几种描述在一起的混合描述。

我们可以用结构描述的方式用多个全加器来实现电路,也可以用行为描述。

采用行为描述时,可用一变量来表示选举通过的总人数。

当选举人大于或等于4时为通过,绿灯亮;反之不通过时,黄灯亮。

描述时,只须检查每一个输入的状态(通过为“1”不通过为“0”)并将这些状态值相加,判断状态值和即可选择输出。

三、实验内容1.用VHDL语言设计上述电路。

2.下载并验证结果。

四、设计提示1.初次接触VHDL语言应注意语言程序的基本结构,数据类型及运算操作符。

2.了解变量和信号的区别。

3.了解进程内部顺序执行语句及进程外部并行执行语句的区别。

五、实验报告要求1.写出七人表决器的VHDL语言设计源程序。

2.书写实验报告时要结构合理,层次分明,在分析叙述时注意语言的流畅。

实验二格雷码变换电路一、实验目的1.用组合电路设计4位格雷码/二进制变换电路。

2.了解进程内部CASE语句的使用及用VHDL语言设计门级电路的方法。

二、实验原理用VHDL语言描述4位格雷码/二进制码变换电路有两种设计方法,即方程输入、状态选择方程。

1)方程输入法4位格雷码/二进制码的转换表如下表所示。

由此转换表(真值表)可以求得每个输出方程为:B3=G3;B2=!G3G2+G3!G2;B1=!G3!G2G1+!G3G2!G1+G3!G2!G1;B0=!G3!G2!G1G0+!G3!G2G1!G0+!G3G2G1G0+!G3G2!G1!G0+G3G2!G1G0+G3G2G1!G0+G3!G2G1G0+G3!G2!G1!G0;考虑实验时观察方便,每个输出均受一个EN信号控制;EN=0时,4个输出为0;EN=1时,4个输出由上式决定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.设计任务 2.设计分析 3.系统框图 4.模块说明 5.编程,下载,测试

任务:实用表决系统设计

要求:在实用表决器系统中,每个表决者 都有三种选择:分别是同意、反对和弃权。 将所有表决结果进行累计,得出同意、反 对和弃权票的总数,当同意票数大于反对 票数,表决通过,否则不通过,同时在数 码管上显示同意、反对和弃权票的总数。

开始

按键输入表决器

绿色LED亮 Y 同意数>反对数 N 红色LED亮

LED显示同意 LED显示反

人数

对人数

LED显示弃权 人数

模块说明

• 扫描是将投票结果统计出来,根据结果分别

驱动电路是数码管显示数字

• 判断模块用来比较同意与不同意人数,根据

判断,使相应的LED亮

1.VHDL语言(略)

2.测试:K9~K15为ON时,表 示同意,K17~K23为ON时,表示反对。当同 意票数大于反对票数,表决通过,实验箱输出 指示OUT1亮;当反对票大于同意票数,表决

设计分析

• 实用表决器系统设计,首先要判断表决者是投的

同意票、反对票还是弃权票,然后累计表决结果 (同意、反对和弃权票的总数),接下来比较同 意票数和反对票数的大小,当同意票数大于半数, 表决通过,否则不通过,因此需要一个判断并累 计表决的子系统。又因为任务还要求在数码管上 显示同意、反对和弃权票的总数,因此,需要动 态扫描子系统和7段-BCD译码子系统。最后得出实 用表决系统(7人)的结构框图E END