DDR时序学习笔记

ddr时序

DDR 内存既然叫做双倍速率SDRAM(Dual date rate SDRSM),就是说是SDRAM的升级换代产品。

从技术上分析,DDR SDRAM最重要的改变是在界面数据传输上,其在时钟信号上升缘与下降缘时各传输一次数据,这使得DDR的数据传输速率为传统SDRAM的两倍。

那么大家就应该知道了,我们所说的DDR400,DDR333,DDR266,他们的工作频率其实仅为那些数值的一半,也就是说DDR400工作频率为200MHz。

FSB与内存频率的关系首先请大家看看表一:FSB(Front Side Bus:前端总线)和内存比率与内存实际运行频率的关系。

FSB/MEM比率实际运行频率1/01200MHz1/02100MHz2/03133MHz3/04150MHz3/05120MHz5/06166MHz7/10140MHz9/10180MHz对于大多数玩家来说,FSB和内存同步,即1:1(DFI 用1/01表示)是使性能最佳的选择。

而其他的设置都是异步的。

同步后,内存的实际运行频率是FSBx2,所以,DDR400的内存和200MHz的FSB正好同步。

如果你的FSB为240MHz,则同步后,内存的实际运行频率为240MHz x 2 = 480MHz。

表2更详尽列出了FSB与不同速度的DDR内存之间正确的设置关系强烈建议采用1:1的FSB与内存同步的设置,这样可以完全发挥内存带宽的优势。

Command Per Clock(CPC)可选的设置:Auto,Enable(1T),Disable(2T)。

Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。

由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。

这个参数的含义就是指在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令,单位是时钟周期。

DDR的原理和时序

DDR的原理和时序DDR(Double Data Rate Synchronous Dynamic Random Access Memory)是一种现代计算机内存技术,广泛应用于各类数码设备和计算机系统中。

DDR内存具有高速度、高数据吞吐量和低功耗等优点,是一种非常重要的内存技术。

首先是内存芯片,DDR内存使用DRAM(Dynamic Random Access Memory)作为存储单元。

DRAM是一种具有高集成度和低功耗的存储技术。

内存芯片上由一系列DRM单元阵列组成,每个单元包含一个存储电容和一个访问电路。

其次是集成电路。

集成电路是连接主板和内存芯片的桥梁。

它包括DDR内存控制器和电源电路,用于控制内存芯片的读写操作和提供电源供电。

第三是总线。

DDR内存通过总线与主板连接,实现与中央处理器(CPU)的数据交换。

总线上有多条信号线,用于传输地址、数据和控制信号。

这些信号线采用差分信号传输方式,以提高抗干扰能力和传输速度。

最后是控制器。

DDR内存控制器位于集成电路内部,负责控制内存读写操作、地址和数据传输等。

控制器根据CPU的指令和数据请求,对内存芯片进行控制和管理,确保数据的准确传输和存储。

DDR的时序是指在读写操作中各个信号的时间顺序和延迟要求。

首先是写时序。

写时序包括命令在写操作中经过的各个阶段的时序和延迟要求。

主要包括:地址输入时间(tAW),即写命令之前地址信号的稳定时间;写命令输入时间(tCW),即写命令发出后,数据输入稳定所需时间;写命令保持时间(tCWH),即写命令的有效保持时间。

其次是读时序。

读时序包括读操作中各个阶段的时序和延迟要求。

主要包括:地址输入时间(tAR),即读命令之前地址信号的稳定时间;读命令输入时间(tCR),即读命令发出后,数据输出稳定所需时间;读命令保持时间(tRDH),即读命令的有效保持时间。

此外,DDR还有一些其他时序参数,如预充电时间(tRP)和对内存控制器和内存芯片之间的信号延迟时间(tDQSS和tDQSQ)。

内存的工作原理及时序介绍

内存的工作原理及时序介绍时序及相关概念以下我把时序分为两部分,只是为了下文介绍起来作为归类,非官方分类方法。

第一时序:CL-tRCD-tRP-tRAS-CR,就是我们常说的5个主要时序。

第二时序:(包含所有XMP时序)在讲时序之前,我想先让大家明白一些概念。

内存时钟信号是方波,DDR内存在时钟信号上升和下降时各进行一次数据传输,所以会有等效两倍传输率的关系。

例如DDR3-1333的实际工作频率是666.7MHz,每秒传输数据666.7*2=1333百万次,即1333MT/s,也就是我们说的等效频率1333MHz,再由每条内存位宽是64bit,那么它的带宽就是:1333MT/s*64bit/8(8bit是一字节)=10667MB/s。

所谓时序,就是内存的时钟周期数值,脉冲信号经过上升再下降,到下一次上升之前叫做一个时钟周期,随着内存频率提升,这个周期会变短。

例如CL9的意思就是CL这个操作的时间是9个时钟周期。

另外还要搞清楚一些基本术语:Cell:颗粒中的一个数据存储单元叫做一个Cell,由一个电容和一个N沟道MOSFET组成。

Bank:8bit的内存颗粒,一个颗粒叫做一个bank,4bit的颗粒,正反两个颗粒合起来叫做一个bank。

一根内存是64bit,如果是单面就是8个8bit颗粒,如果是双面,那就是16个4bit的颗粒分别在两面,不算ECC颗粒。

Rank:内存PCB的一面所有颗粒叫做一个rank,目前在Unbuffered台式机内存上,通常一面是8个颗粒,所以单面内存就是1个rank,8个bank,双面内存就是2个rank,8个bank。

Bank与rank的定义是SPD信息的一部分,在AIDA64中SPD一栏可以看到。

DIMM:指一条可传输64bit数据的内存PCB,也就是内存颗粒的载体,算上ECC芯片,一条DIMM PCB最多可以容纳18个芯片。

第一时序CAS Latency(CL):CAS即Column Address Strobe,列地址信号,它定义了在读取命令发出后到数据读出到IO接口的间隔时间。

DDR工作原理与时序(详细且准确版----以DDR3为例)

DDR工作原理与时序(详细且准确版----以DDR3为例)2015-07-08 by mbmlccking168一、内存工作流程首先,我们先了解一下内存的大体结构工作流程,这样会比较容量理解这些参数在其中所起到的作用。

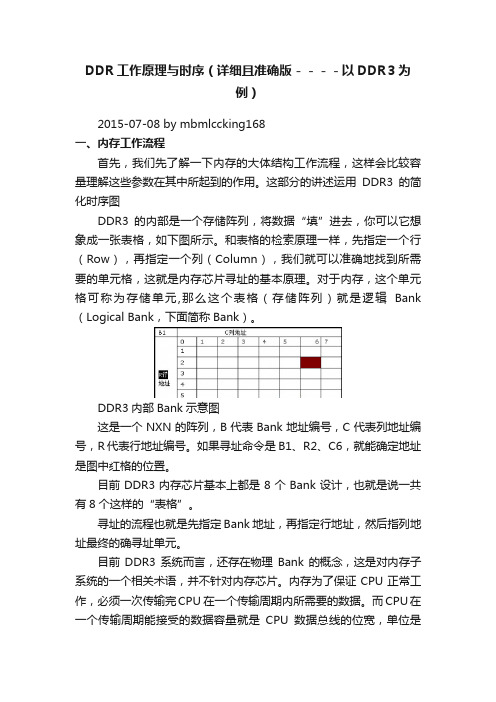

这部分的讲述运用DDR3的简化时序图DDR3的内部是一个存储阵列,将数据“填”进去,你可以它想象成一张表格,如下图所示。

和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。

对于内存,这个单元格可称为存储单元,那么这个表格(存储阵列)就是逻辑Bank (Logical Bank,下面简称Bank)。

DDR3内部Bank示意图这是一个NXN的阵列,B代表Bank地址编号,C代表列地址编号,R代表行地址编号。

如果寻址命令是B1、R2、C6,就能确定地址是图中红格的位置。

目前DDR3内存芯片基本上都是8个Bank设计,也就是说一共有8个这样的“表格”。

寻址的流程也就是先指定Bank地址,再指定行地址,然后指列地址最终的确寻址单元。

目前DDR3系统而言,还存在物理Bank的概念,这是对内存子系统的一个相关术语,并不针对内存芯片。

内存为了保证CPU正常工作,必须一次传输完CPU 在一个传输周期内所需要的数据。

而CPU在一个传输周期能接受的数据容量就是CPU数据总线的位宽,单位是bit(位)。

控制内存与CPU之间数据交换的北桥芯片也因此将内存总线的数据位宽等同于CPU数据总线的位宽,这个位宽就称为物理Bank (Physical Bank,有的资料称之为Rank)的位宽。

目前这个位宽基本为64bit。

在实际工作中,Bank地址与相应的行地址是同时发出的,此时这个命令称之为“行激活”(Row Active)。

在此之后,将发送列地址寻址命令与具体的操作命令(是读还是写),这两个命令也是同时发出的,所以一般都会以“读/写命令”来表示列寻址。

内存时序参数详解

内存时序参数详解内存时序参数是指与内存控制器及内存之间的时间关系的参数,这些参数是由SDRAM系统的设计者设定的,其目的是使控制器可以正确读写SDRAM,也就是执行正确的读写操作。

主要参数如下:1. 主频:指的是CPU的时钟频率,也是内存控制器的时钟频率,它决定了SDRAM的读写时序和速度。

2. CAS延迟(CAS Latency):CAS延迟指SDRAM从受到激活请求开始至内部地址信号被接受完毕的最短时间,即CPU发出激活请求开始到实际内存传输数据延迟的时间,它占据检测时间的最长比例。

一般认为,该时序参数越小越好,可以提高内存的读取速度。

3. RAS延迟(RAS Latency):RAS延迟指受到激活请求后,SDRAM 准备要接受内存地址和读写数据信号之间的最短时间,即CPU发出激活请求后到内存实际传输数据之间的延迟时间,RAS延迟比CAS延迟低,但又不能太低,因为CAS延迟在一定范围内取值比RAS延迟更重要。

4. RAS Precharge(RAS Precharge):RAS Precharge指执行一个操作(比如某一特定的读写操作)后,把SDRAM复位为可以再次接受新的操作的最短时间,如果我们对RAS Precharge时间太长,则对总系统的存取效率影响较大,因此要尽可能的将这个参数设置较短,以提高存取效率。

5. 预取(Pre-charge):Pre-charge时间是每次内存操作结束后,从正在传输数据的某一页中,切换到下一页并等待内部地址信号的最短的时间,它是RAS to CAS的时间,Pre-charge是对RAS Precharge的扩展,Pre-charge时间一般比RAS Precharge时间长,其取值应根据实际应用来确定。

6. 传输时间(Transfer time):Transfer time指的是地址/控制线CAS之后,从SDRAM收发数据的传输时间,除了地址延迟以外,它也包括传输延迟,它取决于内存传输速度(每秒传输几字节),以及内存容量。

ddr 时序参数

ddr 时序参数DDR(Double Data Rate)时序参数是指DDR存储器的时序特性,包括时钟速度、时钟周期、数据传输速率等。

DDR时序参数的优化是提高DDR存储器性能的关键。

本文将从时钟速度、时钟周期和数据传输速率三个方面介绍DDR时序参数的优化方法。

一、时钟速度时钟速度是DDR存储器工作频率的表征,通常以MHz为单位。

提高时钟速度可以加快DDR存储器的数据传输速率,从而提高系统的整体性能。

然而,时钟速度的提高也会带来一些问题,比如信号完整性的降低和功耗的增加。

为了克服这些问题,可以采取以下优化方法:1. 选择高质量的时钟发生器和时钟信号线,确保时钟信号的稳定性和准确性。

2. 使用低延迟的时钟布线技术,减小时钟信号的传输延迟。

3. 合理设计时钟分配网络,避免时钟偏移和时钟抖动。

二、时钟周期时钟周期是DDR存储器时序参数中的另一个重要指标,它表示数据在一个时钟周期内的传输时间。

时钟周期越短,数据传输速率越高。

为了优化时钟周期,可以采取以下方法:1. 减小时钟延迟:通过优化时钟信号的传输路径和布线方式,减小时钟信号的传输延迟。

2. 优化时钟分配:合理设计时钟分配网络,避免时钟偏移和时钟抖动,确保时钟信号的稳定传输。

3. 优化时钟缓冲:选择合适的时钟缓冲器,减小时钟信号的驱动能力,以提高时钟信号的传输速度。

三、数据传输速率数据传输速率是DDR存储器的重要性能指标,它表示DDR存储器单位时间内能传输的数据量。

提高数据传输速率可以提高系统的数据处理能力。

为了优化数据传输速率,可以采取以下方法:1. 提高总线带宽:通过增加数据总线的宽度,提高数据传输的并行性,从而提高数据传输速率。

2. 优化数据线布局:合理布置数据线,减小数据线的长度和电容负载,降低传输延迟和功耗。

3. 优化数据驱动电路:选择高速、低功耗的数据驱动电路,提高数据传输速率的同时降低功耗。

DDR时序参数的优化是提高DDR存储器性能的关键。

了解电脑内存的频率和时序参数

了解电脑内存的频率和时序参数在学习和了解电脑内存的时候,频率和时序参数是两个非常重要的概念。

了解这些参数可以帮助我们选择适合自己需求的内存产品,并且能够提升电脑的运行效率。

本文将介绍电脑内存频率和时序参数的基本知识,并解释它们对电脑性能的影响。

一、内存频率内存频率指的是内存模块每秒钟运行的数据传输速度,也被称为时钟速度。

一般而言,内存频率越高,数据传输速度越快,电脑的响应速度和运行效率也会更高。

内存频率的单位是赫兹(Hz),常见的内存频率有标准频率和超频频率两种。

标准频率是内存模块官方推荐的数据传输速度,超频频率是用户通过提高内存电压和频率进行的人为增加内存性能的操作。

需要注意的是,在超频的情况下,内存的稳定性和寿命可能会受到一定程度的影响,因此超频时需谨慎操作。

二、时序参数时序参数是指内存在不同操作之间所需的时间间隔,它们代表了内存模块的工作效率和响应能力。

常见的时序参数包括CAS延迟、传输延迟和命令延迟等。

1. CAS延迟CAS(Column Address Strobe)延迟是指内存模块在接收到读写指令之后,需要多少个时钟周期才能够提供所需的数据。

CAS延迟越低,内存的读写速度越快,电脑的响应速度也会相应提高。

2. 传输延迟传输延迟是指内存模块在传输数据之前所需的时间延迟,也被称为TRCD(RAS to CAS Delay)。

传输延迟越低,内存模块的数据传输速度越快,对于电脑运行速度的提升也会更显著。

3. 命令延迟命令延迟是指内存模块接收到读写指令后,开始执行读写操作所需的时间延迟,也被称为TRP(Row Precharge Delay)。

命令延迟越低,内存模块的响应速度越快,电脑的运行效率也会有所提升。

三、频率和时序的关系内存频率和时序参数是相互影响的,它们之间的关系决定了内存的整体性能表现。

一般而言,较高的内存频率可以提高内存模块的最大数据传输速度,而较低的时序参数可以减少内存模块的读写延迟。

ddr工作原理与时序

ddr工作原理与时序

DDR(Double Data Rate双倍数据速率)是一种现代的动态随

机存取存储器(DRAM)的接口标准,它具有高带宽、高存

储密度和低功耗等特点。

DDR内部工作原理和时序如下:

工作原理:

1. 内存芯片初始时处于“等待指令”的状态,等待控制器发送读写指令。

2. 控制器向内存芯片发送读或写指令,并同时传输地址信息。

3. 内存芯片接收到指令和地址后,开始进行操作(读取或写入数据),并将结果通过数据线传输给控制器。

时序:

1. 内存芯片上电复位后,需要一定的初始化时间来使其进入正常工作状态。

这个时间称为Power On Reset(POR)时间。

2. 初始化完成后,内存芯片开始从控制器接收和发送数据。

DDR在每个时钟周期内进行一次数据传输,一个时钟周期称

为一个Bus Clock周期。

3. 周期开始时,控制器向内存芯片发送指令,同时传输地址信息。

这个阶段称为命令和地址传输阶段(Command/Address Transfer Phase)。

4. 在下一个时钟周期,内存芯片进行操作(读取或写入数据),并将结果通过数据线传输给控制器。

这个阶段称为数据传输阶段(Data Transfer Phase)。

5. 所有数据传输完成后,内存芯片等待下一次指令。

DDR的主要特点是在一个Bus Clock周期内进行两次数据传输,

即上升沿和下降沿都传输一次数据,从而达到双倍数据速率的效果。

同时,DDR还采用了预取和乱序传输等技术来提高数据传输效率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

高速先生前几期的自媒体文章里多次提到了时序,并且也写了很多时序方面的文章,这些文章都从不同的角度对时序的概念进行了阐述。

作者读完之后深受启发,这里,作者也把自己对时序的理解表达出来,供网友们参考。

接触到时序概念,是从学习DDR布线开始的。

作者以前只知道一个差分对里面的

两根线需要等长,等长的原因是保证P和N两根线上传输的信号同时到达接收端,这样就不会有共模信号的出现。

然而,在DDR实际布线中,难点在于各组信号间的线长匹配。

我们知道,DDR的四组信号之中,地址/命令/控制信号都是参考时钟信号的,数据信号参考DQS。

具体来说,就是要这些信号波形的相对位置之间存在一定的约束。

时钟与地址/命令,控制之间的波形位置对应关系如下,如下图1:

图1

从图1可以看出,理想情况下,地址/命令,控制信号的波形边沿应该和时钟信号

的下降沿对齐,这样才能保证时钟信号的上升沿在地址/命令信号的中间位置,只有这样,信号传输到接收端为建立时间和保持时间留足裕量。

图一中的灰色窗口就是不确定区域,也是我们在设计的时候需要考虑的,一般我们可以通过查看芯片的Datesheet来查阅Prelaunch的最小值与最大值,这个是芯片本身的参数,与布线无关。

说了这么多,系统在工作的时候,时钟与地址/控制信号波形之间的位置关系到底是什么样的呢?让

给我们来看看下图2

图2

上图2中,绿色的是时钟信号波形,紫色的是地址信号。

可以看到,地址/命令,控制信号并不像时钟信号那样是周期性的,但它的位宽是时钟周期的整数倍,信号边沿都是要和时钟信号的下降沿对齐的,如果不能对齐,至少在时钟信号下降沿附近。

同样的,数据信号是参考DQS的,DQS又是参考时钟信号的,它们之间的位置关系如下图所示,图3是时钟信号与DQS之间的时序关系;图4是DQS与DQ之间的时序关系。

图3

图4

从上图可以看出,理想情况下,DQS的波形边沿与时钟信号的边沿是应该对齐的。

对于数据信号来说,由于是DDR,双倍数据速率,时钟波形的上升沿和下降沿都能触发数据,为保证这一点,必须保证DQS信号波形边沿在DQ波形的中间位置。

芯片工作时,这些相对位置都会出现一定的偏移,这些偏移量是芯片本身的属性,相关延时参数在芯片手册上可以查找。

理论联系实际,我们还是来看看芯片在实际工作的时候,这几组信号之间的相对位置是不是我们上面说的那样。

图5

上图中红色波形时DQS信号,黄色是数据信号,可见,数据信号在翻转的时候,边沿基本上都在DQS脉冲的中间位置,这也保证了接收端在读取信号的时候有充足的建立时间与保持时间。

综上所述,本篇文章定性的介绍了一下DDR各组信号之间的时序关系,没有做定量计算。

在实际的时序仿真中,重点在于能够在芯片手册上找到这些时序参数,并理解这些时序参数的含义。

最后通过评估建立时间与保持时间的裕量来判定系统时序是否符合要求。

上篇文章说道,时序就是为了维持数据信号与其参考时钟信号之间的相对位置,保证在时钟上升沿或者下降沿附近的数据能够维持稳定,这样数据就能被有效的读取。

怎么让这些时序关系在系统运行中有效的实现呢?设计中,是通过定义时序参数来实现的,下面就来看看这些时序参数的具体含义。

这里作者按照自己的理解把时序参数分成了三类,一类是用来描述驱动端的,一类是用来描述接收端的,还有一类是用来描述传输通道的。

对于驱动端,描述它的时序参数是Tco,Tco是指时钟触发开始到有效数据输出的器件内部所有延时的总和。

这个参数描述了最开始信号从芯片出来的时候,时钟与数据之间的一个位置关系。

对于源同步时序,不是直接用Tco来定义的,而是使用Tvb和Tva,如下图1

图1

图1中,Tvb指的是在驱动端,时钟上升沿之前(before)数据的有效时间;Tva

指的是时钟上升沿之后,数据的有效时间。

这些参数在驱动芯片手册上可以查到。

对于接收端,主要是建立时间和保持时间,这两个时序参数是时序分析中提到最多的两个参数,如下图2所示:

图2

看图2,有没有觉得和图1很相似呢,它们都是以时钟信号为参考。

对于接收端来说,数据在时钟信号上升沿之前的有效时间称为建立时间,在时钟上升沿之后的叫保持时间。

和驱动端对比,它们的叫法不一样罢了,定义方式都是相似的。

时序分析的最终目的就是要保证数据被接收端有效的读取,所以我们在评估一个系统的时序是否满足要求,是通过评估建立时间和保持时间的裕量来实现的。

对于传输通道来说,是通过飞行时间来描述的。

飞行时间包括最大飞行时间和最小飞行时间。

最大最小飞行时间和传输线的长度有关,也和负载的轻重有关,负载较重会导致上升时间变缓,定义方式如下图3

在理解这些时序参数的含义之后,就可以进行时序裕量的计算了。

这里以数据信号为例进行说明,我们知道,DDR总线中,数据信号是参考DQS的,在写方向:

Data信号从驱动到接收总的延时为:Tdata=Tco_data+Tflt_data (1)

DQS信号从驱动到接收总的延时为:Tstrobe=Tco_strobe+Tflt_strobe+Tdelay (2)

式中:Tco和Tflt分别代表数据、选通信号在器件的内部延迟和信号传输的飞行时间;Tdelay是指数据信号和选通信号之间的延迟,由系统内延时器件决定。

建立时序裕量的公式为:Tsetup_margin=Tstrobe-Tdata-Tsetup(3)

把式(1)和式(2)带入得式(3)得:

Tsetup_margin=Tco_strobe+Tflt_strobe+Tdelay- (Tco_data+Tflt_data)-Tsetup(4)

式中:Tsetup表示接收数据端数据的建立时间,从器件手册上获取;将数据和Strobe

信号在器件内的延时差异定义为Tvb,其值从器件手册上获取;

Tvb=Tco_strobe+Tdelay-Tco_data (5)将PCB走线引起的延时差异,定义为Tpcb_skew:Tpcb_skew= Tflt_data- Tflt_strobe(6)将式(5)和式(6)带入式(4),这样可以得到一个简单的建立时间裕量方程:

Tsetup_margin=Tvb-Tsetup- (Tflt_data(max)-Tflt_strobe(min))(7)

使用同样的方法分析,保持时间裕量:

Thold_margin=(Tco_strobe+Tflt_strobe+Tdelay)-(Tco_data+Tflt_data)-Thold(9)

同样定义:

Tva=Tco_strobe+Tdelay-Tco_data(10)

Tpcb_skew=Tflt_data-Tflt_strobe(11)

Thold_margin=Tva-Thold+(Tflt_data(min)-Tflt_strobe(max))(12)

综上所述,我们可以看出,对于DDR的时序来说,影响时序裕量的关键因素是驱动芯片的Tva与Tvb,以及接收端的建立时间与保持时间。

我们布线可以控制的只是数据与选通时钟之间的长度差值。

数据线与数据选通线长度的差值有正负之分,从(7)和(9)式可以看出,建立时间很保持时间与Tpcb_skew之间的关系,在增大建立时间的时候必然会牺牲保持时间。

所以在布线的时候,数据与数据选通即DQ与同组的DQS 之间应该保持严格的等长,这样可以减少Tpcb_skew,增大建立时间裕量。

时序问题是很复杂的,文中分析的情况没有考虑Jitter与串扰。

我们也很少会手动计算一个系统的时序关系,一般会借助软件分析。

本文只是学习时序仿真的一个入门,感兴趣的网友,让我们一起查阅更多的资料,进行更加深入的学习吧!。