MB9054X 评估板用户手册

恩智浦MIMXRT1060 1064评估板硬件用户指南说明书

NXP Semiconductors Document identifier: MIMXRT10601064EKBHUG User's Guide Rev. 0, 06/2020MIMXRT1060/1064 Evaluation Kit Board Hardware User's GuideContentsChapter 1 Introduction (3)1.1 Board overview (3)1.2 MIMXRT1060/1064 EVK contents (4)1.3 MIMXRT1060/1064 EVK board revision history (4)Chapter 2 Specifications (5)2.1 i.MX RT1060/1064 processor (7)2.2 Boot mode configurations (7)2.3 Power tree (8)2.4 SDRAM memory (11)2.5 SD card slot (11)2.6 Hyper flash (11)2.7 QSPI flash (11)2.8 Ethernet connector (12)2.9 USB PHY connector (12)2.10 Audio input/output connector (12)2.11 OpenSDA circuit (DAP-Link) (12)2.12 JTAG connector (12)2.13 Arduino expansion port (13)2.14 Camera module connector (14)2.15 User interface switch (14)2.16 Sensor (15)2.17 User interface LED indicator (15)2.18 LCD interface (15)Chapter 3 PCB information (16)Chapter 4 EVK design files (17)Chapter 5 EVK contents (18)Chapter 1IntroductionThis document describes MIMXRT1060/1064 Evaluation Kit (EVK) based on the i.MX RT1060/1064 processor from NXP Semiconductor. The document includes system setup, debugging, and provides detailed information on the overall design and usage of the EVK board from a hardware system.1.1Board overviewThis EVK board is a platform designed to showcase the commonly used features of the i.MX RT1060/1064 Processor in a small, low-cost package. The MIMXRT1060/1064 EVK board is an entry level development board that familiarizes the developer to the processor before investing on resources for specific designs.The features of the MIMXRT1060/1064 EVK board are listed in Board features.The features of the MIMXRT1060/1064 EVK board are listed in Table 1.Table 1.Board featuresProcessor NXP Processor MIMXRT1062DVL6AMIMXRT1064DVL6ADRAM Memory SDRAM 256 Mbit, 166 MHz IS42S16160J-6BLIDCDC MPS MP2144GJLDO UNION UM1550S-18UM1750S-00Mass Storage TF Card Slot64 Mbit Quad SPI flash512 Mbit Hyper flashDisplay Interface LCD connectorEthernet10/100 Mbit/s Ethernet connector. PHY chip: KSZ8081RNBUSB USB 2.0 OTG connectorUSB 2.0 host connectorAudio Connector 3.5 mm audio stereo headphone jackBoard-mounted microphoneLeft and right speaker out connectorsS/PDIF interface (unpopulated )Power Connector 5 V DC-jackDebug Connector JTAG 20-pin connector (SWD by default)OpenSDA with DAP-LinkSensor FXOS8700CQ: 6-Axis Ecompass (3-Axis Mag, 3-Axis Accel)(Some boards are unpopulated)Table continues on the next page...IntroductionTable 1.Board features (continued)Camera CMOS sensor interfaceCAN CAN bus connectorUser Interface Button ON/OFF, POR Reset, Reset, USER buttonLED Indicator Power Status, Reset, OpenSDA, USER LEDExpansion Port Arduino interfacePCB 3.937 inch x 5.9055 inch (10 cm x 15 cm), 4-layer board1.2MIMXRT1060/1064 EVK contentsThe MIMXRT1060/1064 EVK contains the following items:•MIMXRT1060/1064 EVK board•USB cable (Micro B)•Camera1.3MIMXRT1060/1064 EVK board revision historyEVK: Mass ProductChapter 2SpecificationsThis section provides detailed information about the electrical design and practical considerations of the EVK board. The document describes each block shown in Block diagram.The document describes each block shown in Figure 1.Figure 1.Block diagramThe overview of the MIMXRT1060 EVK board is shown in Figure 2 and Figure 3.Figure 2.Overview of the MIMXRT1060 EVK board (Front side)Figure 3.Overview of the MIMXRT1060 EVK board (Back side)2.1i.MX RT1060/1064 processorThe i.MX RT1060/1064 is a new processor family featuring NXP advanced implementation of the Arm Cortex-M7 Core. It provides high CPU performance and best real-time response. i.MX RT1060/1064 provides various memory interfaces, including SDRAM, Raw NAND flash, NOR flash, SD/eMMC, Quad SPI, HyperBus, and a wide range of other interfaces for connecting peripherals, such as WLAN, Bluetooth™, GPS, displays, and camera sensors. i.MX RT1060/1064 has rich audio and video features, including LCD display, basic 2D graphics, camera interface, S/PDIF, and I2S audio interface.The i.MX RT1060/1064 applications processor can be used in areas such as industrial HMI, IoT, motor control, and home appliances. The flexibility of the architecture enables it to be used in a wide variety of other general embedded applications too. The i.MX RT processor provides all interfaces necessary to connect peripherals such as WLAN, Bluetooth™, GPS, camera sensors, and multiple displays.The more detail information about i.MX RT1060/1064 can be found in the Datasheet and Reference Manual.2.2Boot mode configurationsThe device has four boot modes (one is reserved for NXP use). The boot mode is selected based on the binary value stored in the internal BOOT_MODE register.Switch (SW7-3 and SW7-4) is used to select the boot mode on the MIMXRT1060/1064 EVK board.Table 2.Boot mode pin settingsBOOT_MODE[1:0] (SW7-3 SW7-4)BOOT TypeTable continues on the next page...Table 2.Boot mode pin settings (continued)00Boot From Fuses 01Serial Downloader 10Internal Boot 11ReservedTypically, the internal boot is selected for normal boot, which is configured by external BOOT_CFG GPIOs. Table 3 shows the typical Boot Mode and Boot Device settings.Table 3.Typical boot mode and boot device settings for RT1060SW7-1SW7-2SW7-3SW7-4Boot Device OFF ON ON OFF Hyper flash OFFOFF ON OFF QSPI flash ONOFFONOFFSD cardFor more information about boot mode configuration, see the System Boot chapter of the MIMXRT1060 Reference Manual .For more information about MIMXRT1060 EVK boot device selection and configuration, see the main board schematic .Table 4.Typical boot mode and boot device settings for RT1064SW7-1SW7-2SW7-3SW7-4Boot Device OFF OFF ON OFF QSPI flash ONOFFONOFFSD card2.3Power treeA DC 5 V external power supply is used to supply the MIMXRT1060/1064 EVK board at J2, and a slide switch SW1 is used to turn the Power ON/OFF. J41 and J9 is used to supply the EVK board.Table 5 lists different J1 jumper settings for different power supply.Table 5.Jumper settings for power supply Power Supply J1 Setting J21-2J93-4J415-6The power tree is shown in the following figure.Figure 4.Power treeThe power control logic of the MIMXRT1060/1064 EVK board is shown in the Figure 5.•SNVS is powered first and then PMIC_REQ_ON is switched on to enable external DC/DC to power up other power domains.•ON/OFF button is used to switch ON/OFF PMIC_REQ_ON to control power modes.•RESET button and WDOG output are used to reset the system power.Figure 5.Power control diagramThe power rails on the board are shown in Table 6.Table 6.Power railsTable continues on the next page...Table 6.Power rails (continued)2.4SDRAM memory256 Mbit, 166 MHz SDRAM (IS42S16160J-6BLI) is used on the EVK board.2.5SD card slotThere is an SD card slot (J39) on the MIMXRT1060/1064 EVK board. J39 is the Micro SD slot for USDHC1 interface. To boot from the SD card, the boot device switch (SW7) settings should be: ON, OFF, ON, OFF, as shown in Typical boot mode and boot device settings.2.6Hyper flashOn the MIMXRT1060/1064 EVK board, there is one 512 Mbit hyper flash device. To boot from the Hyper Flash, the boot device switch (SW7) settings should be: OFF, ON, ON, OFF, as shown in Table 3. By default, this hyper flash is disabled on the EVK. To enable the onboard hyper flash, update the following settings.1.Weld resistors: R356, R361 - R366.2.Removed 0Ωresistors: R153 - R158.The boot from hyper flash only supports RT1060.2.7QSPI flashA 64 Mbit QSPI flash is used on the MIMXRT1060/1064 EVK board. If the developer wants to boot from the QSPI flash, the boot device switch (SW7) settings should be: OFF, OFF, ON, OFF, as shown in Table 3. The QSPI flash is the default onboard flash.The boot from QSPI flash only supports RT1060.2.8Ethernet connectorThere are two Ethernet Mac controllers in the MIMXRT1060/1064 processor. The Ethernet subsystem of the MIMXRT1060/1064 EVK board is provided by the KSZ8081RNB 10/100 M Ethernet Transceiver (U16) and an RJ45 (J19) with integrated magnetic.2.9USB PHY connectorMIMXRT1060/1064 contains two integrated USB 2.0 PHYs capable of connecting USB host/device systems at:•USB low-speed (LS) rate of 1.5 Mbits/s•USB full-speed (FS) rate of 12 Mbits/s•USB 2.0 high-speed (HS) rate of 480 Mbits/s2.10Audio input/output connectorThe audio codec used on the MIMXRT1060/1064 EVK board is Wolfson’s low power, high-quality stereo codec, WM8960. The MIMXRT1060/1064 EVK board includes:•one headphone interface (J12)•one onboard MIC (P1)•two speaker interfaces (J16, J17)•S/PDIF interface (J14 and J18, DNP).J12 is a 3.5 mm audio-stereo headphone jack, which supports jack detect.2.11OpenSDA circuit (DAP-Link)The OpenSDA circuit (CMSIS–DAP) is an open-standard serial and debug adapter. It bridges serial and debug communications between a USB host and an embedded target processor.CMSIS-DAP features a mass storage device (MSD) bootloader, which provides a quick and easy mechanism for loading different CMSIS-DAP applications such as flash programmers, run-control debug interfaces, serial-to-USB converters, and more.Two or more CMSIS-DAP applications can run simultaneously. For example, run-control debug application and serial-to-USB converter run in parallel to provide a virtual COM communication interface while allowing code debugging via CMSIS-DAP with single USB connection.For the MIMXRT1060/1064 EVK board, J41 is the connector between the USB host and the RT1060/1064. To update the Open SDA firmaware, press the SW8 and Power on the board. There is a disk named "MAINTENANCE". Drag/drop the new firmware to the "MAINTENANCE" and re-power the board. The firmware is updated.2.12JTAG connectorJ21 is a standard 20-pin/2.54 mm box header connector JTAG. The pin definitions are shown in Figure 6. It supports SWD by default.Figure 6.JTAG pin definitions2.13Arduino expansion portJ22 – J25 is defined as Arduino interface. Table 7 lists the pin definitions of Arduino interface. Table 7.Arduino Interface pin definitionsJ22J23UART_RX/D0A0/ADC0UART_TX/D1A1/ADC1D2/INT0A2/ADC2D3/INT1/PWM/OC2B A3/ADC3D4/T0/XCK A4/ADC4/SDAD5/TI/PWM A5/ADC5/SCLD6/AIN0/PWM/OC0AD7/AIN1/PWMJ24J25D8/CLKO/ICP1NCD9/OC1A/PWM IOREFD10/SPI_CS RESETD11/OC2A/PWM/SPI_MOSI 3.3 VD12/SPI_MISO 5 VD13/SPI_CLK GNDGND GNDAREFD14/I2C_SDAD15/I2C_SCL2.14Camera module connectori.MX RT1060/1064 supports one parallel CSI (Camera Sensor Interface). There is a camera module connector (J35) on the MIMXRT1060/1064 EVK board. The CA031C based on OV7725 and CA111C based on MT9M114 are used directly.J35 supports both MT9M114 and OV7725 camera module, but 3.3 V is a violation to MT9M114 spec 3.1 V. Itproved fine for evaluation/demo with 3.3 V supply, but in product design, it is recommended to adjust DCDC outputor add level shifter.2.15User interface switchThere are four user interface switches on the MIMXRT1060/1064 EVK board.•Power switch•ON/OFF button•Reset button•USER button2.15.1Power switchSW1 is a slide switch to control the power of the MIMXRT1060/1064 EVK board when the power supply is from J2.•Sliding the switch to the ON position connects the 5 V power supply to the evaluation board main power system.•Sliding the switch to the OFF position immediately removes all power from the board.2.15.2ON/OFF buttonSW2 is the ON/OFF button for MIMXRT1060/1064 EVK board. A short pressing in OFF mode causes the internal power management state machine to change state to ON. In ON mode, a short pressing generates an interrupt as a software-controllable power-down. An approximate 5 seconds or more pressing causes a forced OFF. However, you can disconnect both the boot mode inputs.2.15.3Reset buttonThere are two Reset buttons on the EVK board. SW3 is the power-on reset button. Pressing SW3 in the power on state forces to reset the system power except SNVS domain. The processor immediately turns off and reinitiates a boot cycle from the processor power off state. SW9 is a reset button.2.15.4USER buttonSW8 is a USER button (GPIO5-00). Pressing the USER button can produce changes in high and low levels.2.16SensorU32 on the EVK board is a 6-Axis Ecompass (3-Axis Mag, 3-Axis Accel) sensor FXOS8700CQ. The Ecompass is connected to i.MX RT1060/1064 I2C1 port.The sensor is not populated on some boards.2.17User interface LED indicatorThere are four LED status indicators on the EVK board.The functions of these LEDs include:•Main Power Supply (D3)—Green: DC 5 V main supply is normal.—Red: J2 input voltage is over 5.6 V.—Off: Board is not powered.•Reset RED LED (D21)•OpenSDA LED (D20)•USER LED (D18)2.18LCD interfaceThe enhanced Liquid Crystal Display Interface (eLCDIF) is a general-purpose display controller.The eLCDIF block supports the following:•Displays that support moving pictures and require the RGB interface mode (DOTCLK interface).The eLCDIF provides fully programmable functionality to supported interfaces:•Bus master interface to source frame buffer data for display refresh.•8/16/18/24/32 bit LCD data bus support available depending on I/O MUX options.•Programmable timing and parameters for DOTCLK LCD interfaces.To use the LCD, NXP provides an optional LCD module RK043FN02H-CT. RK043FN02H-CT has a 4.3 inches touch screen and supports a resolution of up to 480*3(RGB)*272. This module contains two FPC cables. The LCD interface is connected to J8 (A1-A40) and the CPT interface can be connected to J8 (B1-B6). You can purchase LCD modules from .PCB informationThe MIMXRT1060/1064 EVK board is uses the standard 4-layer technology. The material used is FR-4. The PCB stack-up information is shown in Table 8.Table 8.Board stack-up informationEVK design filesYou can download, the schematics, layout files, and gerber files (including Silkscreen) from /MIMXRT1060-EVK.EVK contentsThe following table lists the contents on the evaluation kit.Table 9.EVK contentsItem DescriptionEVK board EVK board with processor, memory, interfaces and so on. USB cable USB cable (Micro-B to Standard-A).Camera CA111C based on MT9M114.Power adapter, micro-SD card, and LCD module are not standard parts of the evaluation kit.How To Reach Us Home Page: Web Support: /support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including “typicals,” must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: / SalesTermsandConditions.While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer’s applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C‑5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C‑Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and word marks and the Power and logos and related marks are trademarks and service marks licensed by .© NXP B.V. 2020.All rights reserved.For more information, please visit: Forsalesofficeaddresses,pleasesendanemailto:**********************Date of release: 06/2020Document identifier: MIMXRT10601064EKBHUG。

NB7NPQ1004MMTGEVB评估板用户手册说明书

NB7NPQ1004MMTGEVB NB7NPQ1004MMTGEVB Evaluation Board User's ManualIntroductionThe NB7NPQ1004MMTGEVB evaluation board was developed to provide a convenient platform to quickly verify the operation of the NB7NPQ1004M redriver in a USB type −A system environment.This evaluation board manual contains:•Information on the NB7NPQ1004M Evaluation Board •Board Schematics •Bill of MaterialsFeatures•Accommodates the Functional Evaluation of the Device•Acts as a Reference Design that can Easily be Modified for Active Cables, UFP (Upstream Facing Port), DFP (Downstream Facing Port), and DRP (Dual Role Port) Applications•Type −A Plug and Receptacle to Easily Place in the Existing System Environment•On Board Control Pins for Adjusting Settings without Compromising Form FactorPart DescriptionThe NB7NPQ1004M is a 3.3 V quad channel, linear redriver for USB 3.1 applications that supports both 5 and 10 Gbps data rates.Signal integrity degrades from PCB traces and transmission cables which may cause inter symbol interference (ISI). The NB7NPQ1004M compensates for these losses by engaging varying levels of equalization at the input receiver. The output transmitter circuitry provides user selectable flat gain settings to create the best eye openings for the outgoing data signals. The flexibility of this part allows it to fit into many system applications.After power up, the NB7NPQ1004M periodically checks both of the TX output pairs of each port for a 50 W termination for a Super Speed USB receiver. When the receiver is detected on either channel of a port, the internal RX termination will be enabled of that respective channel. The port becomes active once both TX outputs have detected 50 W termination, and the NB7NPQ1004M is set to perform the redriver function. Port AB (channels A & B) and port CD (channels C & D) are independent of each other.This manual should be used in conjunction with the device datasheet NB7NPQ1004M which contains full technical details on the devicespecifications and operation.EVAL BOARD USER’S MANUALFigure 1. NB7NPQ1004M Demo Board(Top View)BOARD MAP AND FUNCTIONAL SUMMARYJumper J75 to J82: These are forEQ/FG Gain control (H/F/R/L). Refer Datasheet for Pin setting andassociated EQ and FGJumper J83 to J84: These are EN Pin Jumpers for each the Channel A/B and C/D. Connecting to thelow will disable the ChannelVcc and GND Pins: These Pins can be used to Power the 1004 Device directly with 3.3 V supply and tomeasure the device currentCh C & DCh C & DCh A & BCh A & BResistor R2, R17, (R18, R19 on the Bottom Side):These are 0 W that connects to the USB 2.0 data line.These can be removed to ensure that only SuperSpeed data lines are active+Figure 2. NB7NPQ1004M Evaluation Board(Top View)Jumper J15: This Jumper enables the LDO when High. When Jumperis Low, the LDO is ShutdownJumper J14: This Jumper connects the 5 V USB Bus to theInput of the LDO3.3 V LDONB7NPQ1004MCh C & DCh C & DCh A & BCh A & BFigure 3. NB7NPQ1004M Evaluation Board(Bottom View)Jumper J13: This Jumperconnects the 3.3 V LDO Output tothe VCC of the 1004 DeviceSelect Power SourceThe NB7NPQ1004MMTGEVB has the flexibility to be powered through USB’s VBUS, or an external power supply. Table 1 and Figure 4 describe the jumper settings for each of the configuration.Monitoring Current / PowerThere are two easy ways to monitor the current consumed by the redriver. If you are using an external power supply, you can simply use the current meter commonly found on the power supplies. If you would like to use a current probe, simply solder the probe between the VCC pin and the power supply. This will allow monitoring of the NB7PQ1004M’s current consumption.USB 2.0 Data LinesThe USB 2.0 lines can be disconnected by removing the 0 W resistors R2, R17, R18 and R19 on the D+ and D− lines.This is useful if you cannot easily tell whether the downstream facing port has acknowledged a Super Speed(+) connection with the inserted loss, or if it stepped down to High Speed data rates. When a receiver is detected through RxDetect, the DFP will initialize link training. It will send a test signal out at the highest data rate and expect to see the same signal sent back by the UFP. If the signals do not match due to ISI (or any other connection issues) then it will drop down the data rate to USB 2.0 speeds.On Windows machines, an easy way to tell that a Super Speed connection was not established is to look for a pop up in the task bar letting the user know that “This device can perform faster”. A disk benchmarking tool like Crystal Disk Mark that lets you test read and write speeds to a peripheralstorage can also be used.USB 5 V VBUSLDO 5 V InputLDO5 V OutputJ14J13VCC Test Pt.GND Test Pt.LDO3.3 VFigure 4. Power Source SelectionTable 1. SELECTING A POWER SOURCEUSB VBUS Place jumper on J14 and J13EXTERNAL SUPPLY Open J14 and connect a positive lead of an external supply to VCC and apply 3.3 V.Ensure that GND is connected to ground and that current limit is set to 300 mA.COMPLETE BOARD SCHEMATICS Figure 5. RE−DriverFigure 6. NB7NPQ1004M USB Type−A EvaluationBoard Schematics Figure 7. Power Supply SectionTEST POINTGNDTEST POINT1J13EQATXn1TXp1RXn1RXp1RXp2RXn2TXp2TXn2 RXp2RXn2TXp2TXn2TXn1TXp1RXn1RXp1BILL OF MATERIALSTable 2. BILL OF MATERIALSSl. No.Qty Description Reference Manufacturer Manufacturer PN 11USB 3.1 Redriver U4ON Semiconductor NB7NPQ1004M21 3.3 V Voltage Regulator U3ON Semiconductor NCP3335ADM330R2GGSB4111312HR 32USB Type−A Receptacle CN1_B, CN2_A AmphenolCommercial ProductsGSB416445CHR42 USB Type−A Plug CN1_A, CN2_B AmphenolCommercial Products52Capacitor 1 m F (0603)C21, C22 Samsung CL10A105KA5LNNC 68Capacitor 0.220 m F (0402)C4, C8, C15, C18, C23,TDK C1005X5R1C22M050BBC24, C25, C26TDK C1005X5R1C334K050BB 78Capacitor 0.33 m F (0402)C27, C28, C29, C30,C38, C39, C40, C4181Blue LED D1Rohm Semiconductor SMLE12BC7TT86 911Header, 0.100”J75 to J84, J15Amphenol FCI68001−203HLF 107Header, 0.100”J13, J14Amphenol FCI 77311−118−02LF 114Resistor 0.0 W (0402)R2, R17, R18, R19 YAGEO RC0402JA−070RLPanasonic ERJ−2RKF6802X 128Resistor 68 k W (0402)R3, R8, R9, R10, R11,R12, R13138Resistor 200 k W (0402)R20 to R23, R28 to R31Panasonic ERJ−2RKF2003X 141Resistor 1 k W (0402)R7Panasonic ERJ−2RKF1001X 152TEST POINT TP1, TP2 Keystone5016ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed atON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.PUBLICATION ORDERING INFORMATION。

VSC8584芯片评估板用户指南说明书

VSC8584User Guide VSC8584 Evaluation BoardJanuary 2014Contents1Revision History (1)1.1Revision 1.0 (1)2Introduction (2)3General Description (3)3.1Key Features (3)3.1.1Copper Port RJ45 Connections (3)3.1.2SGMII/QSGMII MAC SMA (3)3.1.3Switch Block Control (3)3.1.4Zarlink ZL30343 SyncE G.8262/SETS (3)3.1.5External 1588 Clock Option (4)3.1.6External RefClk Option (4)3.1.71588 Daisy-Chain SPI Time-Stamping Connection (4)3.1.8Network Interface Microcontroller Card (5)4Quick Start (6)4.1Connecting the Power Supply (6)4.2PC Software Installation (6)4.3Connecting to the Board to the PC (6)4.3.1Changing the IP Address of the Board (6)4.4Using the Control Software (7)4.4.1CAT5 to SGMII with Clause 37 AutoNeg Enabled (7)4.4.2Board Initialization and Running PGY Scripts (8)4.4.3Copper Media Operation (1000BASE-T) (9)4.4.4Fiber Media Operation (1000BASE-X) (10)4.4.5Fiber Media Operation (100BASE-FX) (10)4.5Useful Registers (10)4.5.1Ethernet Packet Generator (10)4.5.2Copper PHY Error Counters (10)4.5.3Fiber PHY Error Counters (10)4.5.4Configuring 1588 Daisy-Chain SPI Time-Stamping (11)5Additional Information (12)1Revision HistoryThe revision history describes the changes that were implemented in this document. The changes arelisted by revision, starting with the most current publication.1.1Revision 1.0Revision 1.0 of this datasheet was published in January 2014. This was the first publication of thedocument.2IntroductionThe VSC8584 device is a low-power, quad-port Gigabit Ethernet transceiver with four SerDes interfacesfor quad-port dual media capability. It also includes an integrated quad port I2C multiplexer (MUX) tocontrol SFPs or PoE modules. The VSC8584 supports IEEE 802.1AE 128/256-bit MACsec protocols tomeet the security requirements for protecting data traversing Ethernet LANs, and also includes Vitesse’spatent-pending distributed timing technology VeriTime™ that delivers the industry’s most accurate IEEE1588v2 timing implementation. The VSC8584 device offers a seamless integration between IEEE 1588v2and the MACsec engine with no loss of precision. The VSC8584 also supports a ring resiliency featurethat allows a 1000BASE-T connected PHY port to switch between master and slave timing withouthaving to interrupt the 1000BASE-T link.This document describes the architecture and usage of the VSC8584 Evaluation Board (VSC8584EV). TheVSC8584EV may be used to evaluate a family of devices which include VSC8584. These devices vary withrespect to the number of ports, supported interfaces, and available features. This document specificallyThe Quick Startaddresses the VSC8584 device. section describes how to bring-up the evaluation boardalong with install and run the graphical user interface (GUI), used to control the evaluation board.Figure 1 • VSC8584EV Evaluation BoardThe following reference documents provide additional information about the operation of the VSC8584evaluation board.https:///products/product.php?number=VSC8564VSC8564 Datasheet ()VSC8582 Datasheet ()https:///products/product.php?number=VSC8582https:///products/product.php?number=VSC8575VSC8575 Datasheet ()VSC8584 Datasheet ()https:///products/product.php?number=VSC8584IEEE1588v2 and SyncE – Applications and Operation Using Vitesse’s Synchronization Solution/products/download.php?fid=4767&number=VSC8574()https:///products/product.php?number=VSC8584VSC8584 GUI ()3General DescriptionThe evaluation board in Figure 1 provides the user a way to evaluate the VSC8584 device in multipleconfigurations. Four RJ-45 connectors are provided for copper media interfaces. The four SFP cagesallow for evaluation of the fiber media interconnects. The MAC interface is provided via SMAconnectors.For access to all of the features of the device, an external microcontroller is used to configure the on-board clock chip via a two-wire serial bus and the VSC8584 via the MDIO bus. The graphical userinterface (GUI) enables the user to access the registers.The evaluation board uses a Zarlink device to synthesize a 125 MHz reference clock signal from a 20MHz crystal which serves as the REFCLK input.3.1Key Features3.1.1Copper Port RJ45 ConnectionsPHY Ports 2 and 3 use UDE RTA 1648BAK1A with integrated magnetic while PHY Ports 0 and 1 usegeneric RJ45 connectors with discrete Pulse H5008 magnetics.3.1.2SGMII/QSGMII MAC SMASGMII SMA connections are provided for all PHYs while the QSGMII SMA connection is available only onPHY0.3.1.3Switch Block ControlSet the SW1 switch as shown in the figure below.Figure 2 • SW1 Switch Control3.1.4Zarlink ZL30343 SyncE G.8262/SETSThe Zarlink ZL30343 is initialized by default to provide a 125 MHz differential LVPECL clock to VSC8584REFCLK inputs. (Note: the ZL30343 can be programmed to provide LVDS differential clock in conjunctionwith an LVDS termination provided for REFCLK, please refer to the Zarlink manual for programming itsoutput drive).Also, the ZL30343 can support synchronization with the VSC8584 PHY recovered clock for SyncEoperation. The ZL30343 is initialized to lock a recovered clock output if one is enabled and availablefrom the VSC8584 PHY. If no recovered clock signal is available, then the ZL30343 will select the crystaloscillator (U16) as default reference source for holdover operation. ZL30343 will indicate locked versusholdover status by driving LED D33 or D34. See the Zarlink documentation for more discussionconcerning its operation. See the VSC8584 datasheet for configuring recovered clock output pinbehavior.Please ensure three-way resistive connections R19 and R22 are appropriately connected to feedback theVSC8584’s recovered clock outputs into the ZL30343 device, if synchronization to a recovered clocksource is desired.3.1.5External 1588 Clock OptionThe user may choose to provide an external 1588 REFCLK via SMA connections to J65 and J66. Zero ohmjumpers may need to be removed and or installed to connect via these clock inputs. The board is builtwith connections for external 1588 REFCLK, unless otherwise indicated in documentation accompanyingthe specific board delivered.3.1.6External RefClk OptionThe user may choose to provide an external PHY REFCLK via SMA connections to J21 and J23. Zero ohmjumpers may need to be removed and or installed to connect via these clock inputs. As per section 2.1.4,and unless otherwise indicated in documentation accompanying the specific board, the board is builtwith a REFCLK connection driven by the ZL30343, instead of using an external REFCLK source.3.1.71588 Daisy-Chain SPI Time-Stamping ConnectionThe VSC8584 device enables daisy-chaining multiple devices to reduce the number of pins required totransmit time stamping information to system ASICs gathering IEEE 1588 time stamps. For users withtwo or more 8584EV boards, the following single-ended connections shown below are required fromthe master device to slave device:J75 pin 6 to J77 pin 6 (1588_SPI_CLK output → input)J75 pin 4 to J77 pin 4 (1588_SPI_CS ouput → input)J75 pin 2 to J77 pin 2 (1588_SPI_MISO output → 1588_SPI_MOSI input)See section 3.5.4 for register programming to enable this interface.Recommendation: for SPI daisy chaining use a Molex 10 pin ribbon cable with one-to-one connectionsFigure 3 • 1588 Daisy-Chain SPI InterconnectOnce enabled along with proper initialization of the 1588 IP block, time-stamped 1588 traffic in theegress direction will generate a similar sequence on the serialized timestamp daisy-chain as shown inthe following illustration. See the VSC8584 datasheet section about Serial Time Stamp Output Internfacefor a more detailed functional description.Figure 4 • 1588 Daisy-Chain SPI Traffic Pattern (PHY port 3 egress)3.1.8Network Interface Microcontroller CardA “Rabbit” microcontroller card is included to facilitate a software interface to the registers on theVSC8584. The controller card has a hard coded static IP address. Refer to the label on the card for thevalue. This address is required by the user to initiate communications via the board and the GUI.Note: The factory programmed Rabbit board IP address is 10.9.70.193.1. 2. 3. 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 4Quick Start This section shows the quick start for the VSC8584.4.1Connecting the Power SupplyThe evaluation board uses 5 VDC to power the on-board regulators creating the 3.3 V, 2.5 V, and 1.0 V rails which drive the devices as well as modules. The evaluation board can be powered up using the power pack which provides the 5 VDC. Simply plug the AC adaptor into a wall socket and the barrel end into J67 (see the upper right corner of Figure 1). Immediately the user should see several LEDs turn on.4.2PC Software InstallationDownload the ZIP file to the PC’s root directory, normally C:\.Extract to C:\Double-click the icon to launch the GUI (It is acceptable to drag the icon to the desktop)4.3Connecting to the Board to the PCThe Rabbit board can interface with a PC either through a direct connection to the PC or if configured properly through a local area network. The latter option requires the user to configure the Rabbit’s IP address so as to properly reside on the user’s network.The IP address of the board should be written on the Rabbit network interface daughter board card. The default value should be 10.9.70.193. Use this IP address to initially access the board for operation or to change its IP address.4.3.1Changing the IP Address of the BoardDetermine and write down the new unique IP address you wish to change the board to.Directly connect an Ethernet cable from a PC to the Rabbit board.: Some older PCs do not support auto-crossover on the Ethernet connection so a cross-over NOTE cable may be unch a DOS command window by clicking on the Start->Run button and typing “cmd”.Within the DOS command window type "Telnet."In Telnet, connect to the Rabbit board’s address using the open command by typing “open 10.9.70.^XXX”.10.9.70.xxx where xxx is the value on your board from the factory (typically 193).You should have a prompt and be able to type help to get a list of commands available on the Rabbit.a) If you are unable to connect, then most likely you will need to change the IP address of the connected PC to have the first 3 octets similar to the board by following the subsequent steps.b) On the PC under Windows -> Control Panel ->Network Connections -> Local Area Connection, right mouse-click for properties. Under the General tab highlight Internet Protocol (TCP/IP) and click on Properties. From there enter the new PC IP address such as 10.9.70.yyy where yyy is a unique value and NOT the same as the Rabbit board. Once complete, return to step mand the board to change its IP address to the new one by typing into Telnet now connected to the board the command: set ip <new IP address> <Enter> where <new IP address> is in the form xxx.xxx.xxx.xxx. Once you hit <Enter> the IP address will be changed and the Rabbit will save the value and reboot which may take approximately 1 minute. The Telnet session will disconnect from the board.Change your PC IP address to the same IP network as the Rabbit board.Telnet to the Rabbit e the following commands to complete configuration of the Rabbit board:a) set netmask xxx.xxx.xxx.xxx b) set gateway xxx.xxx.xxx.xxx c) save env Please record and inform Microsemi of the new IP address of the board when you return so that Microsemi can connect to and reconfigure the board.Re-label the Rabbit board with the new IP.4.4Using the Control Software4.4.1CAT5 to SGMII with Clause 37 AutoNeg EnabledConnect the VSC8584EV Rabbit microcontroller RJ-45 directly to the PC or through a network switch ifproperly configured. Apply 5 VDC to the EVB.Launch the GUI by double-clicking the GUI shortcut located in C:\ViperGUI_4_67 or on the desktop if ithas been moved there. The GUI connection window shown in the following figure should appear.Figure 5 • GUI Connection WindowTo make a connection to the EVB, click “Rabbit” and enter the IP address of the EVB, then click on"Connect." The display next to the IP address window should change to "Connected." If it does not,check the IP address, or your network configuration until connection with the EVB can be successfullyestablished.Double-click on “MII Registers” and the window shown in Figure 6 should appear:Figure 6 • MII Registers GUI WindowBe sure the device is up and running by reading MII Register 0. It should read back 0 × 1040. Readingback all 0’s or all 1’s indicates a problem. A checked box means the bit is set to “1,” if unchecked it is“0.”4.4.2Board Initialization and Running PGY ScriptsOnce the evaluation board connectivity has been established and confirmed, the PHY should beinitialized. Initialization can be accomplished by running an init-script sequence, such as performed bythe pre- and post-reset functions of the PHY API standalone app.While the init-script sequence may not required for specific operational modes, an init-script sequenceis highly recommended to ensure correct performance over the greatest set of user scenarios for thePHY. After initialization is performed, refer to the PHY Datasheet section on Configuring of the PHY andPHY Interfaces for the desired application.In order to execute an init-script, double-click on “Run PHY Script” within the GUI Connection Windowto launch the Run PHY Script window as shown in Figure 7. This enables a user to load a script toconfigure the device rather than navigating through Registers pages. Click “Load” button, browse to adesired script file via the pop-up panel, finally click “Run” button. After execution is completed, youshould see read-back values in decimal as shown in the following figure.The script syntax is command, phy address (in decimal), register address (in decimal), and registercontent (in either hexadecimal or decimal).1. 2. 3. 4. 5. 6. content (in either hexadecimal or decimal).Figure 7 • Run PHY Script GUI Window (after script is loaded)Figure 8 • Run PHY Script GUI Window (after script is loaded)4.4.3Copper Media Operation (1000BASE-T)A single register write and some external coax cables enables 1G Ethernet traffic to be received by the VSC8584 RJ-45 port, routed through the VSC8584 and externally via coax loopback cables through the SGMII interface and transmitted back to the traffic source on the same copper port. First configure the SerDes in SGMII mode by writing to Micro page 18’d. This is a global setting and does not need to be applied per port.Steps for external SGMII loopback:Set up the copper traffic source (i.e., IXIA or Smartbits)Connect an Ethernet cable to an RJ-45 Port 0.Connect two matched coax cables, J1 - J4 and J2 - J5.Write using the "Micro Page Registers" window: 18'd 0 × 80F0When "Micro Page" 18'd is read back, bit 15 will clear.Linkup bit is in MII Reg 1, bit 2 (MII 1.2), read twice to update.Traffic should be the following:Steps for SGMI forwarding port 0 ↔ port 1:1. 2. 3. 4. 5. 6. 1. 2. 3. 4. 5. 6. 1. 2. 3. 4. 5. 6. Steps for SGMI forwarding port 0 ↔ port 1:Set up the Copper traffic source (i.e., IXIA or Smartbits)Connect an Ethernet cable to an RJ-45 Port 0.Connect two matched coax cables as follows:J1 <TDIN0+> to J6 <RXDOUT1+>J2 <TDIN0-> to J7 <RXDOUT1→J5 <RXDOUT0-> to J10 <TXDIN1→J4 <RXDOUT0+> to J9 <TXDIN1+>Write using the "Micro Page Registers" window: 18'd 0 × 80F0.When “Micro Page” 18’d is read back, bit 15 will clear.Linkup bit is in MII Reg 1, bit 2 (MII 1.2), read twice to update4.4.4Fiber Media Operation (1000BASE-X)Follow all steps in section 3.4.2 with fiber media connection to (IXIA) and add the following steps.Write using the “Micro Page Registers” window: 18’d 0 × 8FC1. (Global)When “Micro Page” 18’d is read back, bit 15 will clear.Write “MII Register” (PHY 0) 23’d 0 × 0204 (Sets Media Mode)Write “MII Register” (PHY0) 0’d 0 × 9040 (SW Reset for media mode setting to have effect)Write “Extended MII Register” (PHY0) 19’d 0 × 0001 (Flip SIGDET polarity if necessary)Write “MII Register” (PHY0) 0’d 0 × 0004 (Disable Auto Neg if necessary)Traffic should be flowing.4.4.5Fiber Media Operation (100BASE-FX)Follow all steps in section 3.4.2 with fiber media connection to (IXIA) and add the following steps.Write using the “Micro Page Registers” window: 18’d 0x8FD1. (Global)When “Micro Page” 18’d is read back, bit 15 will clear.Write “MII Register” (PHY 0) 23’d 0x0304 (Sets Media Mode)Write “MII Register” (PHY0) 0’d 0x9040 (SW Reset for media mode setting to have effect)Write “Extended MII Register” (PHY0) 19’d 0x0001 (Flip SIGDET polarity if necessary)Write “MII Register” (PHY0) 0’d 0x0004 (Disable Auto Neg if necessary)Traffic should be flowing.4.5Useful Registers 4.5.1Ethernet Packet GeneratorExtMII 29E is the Ethernet Packet Generator register. Refer to datasheet for configuration options.A Good CRC packet counter is in ExtMII 18.13:0. A read of the register reads back the good CRC packets and then clears the register so the subsequent reads will be 0 if no traffic has been received. If traffic has been received since the last read, bit 15 will be set.4.5.2Copper PHY Error CountersIdle errors = MII 10.7:0RX errors = MII 19.7:0False carrier = MII 20.7:0Disconnects = MII 21.7:0CRC errors = ExtMII 23.7:04.5.3Fiber PHY Error CountersGood RX CRC packets = Ext3MII 28.13:0Bad RX CRC packets = Ext3MII 29.7:0Good TX CRC packets = Ext3MII 21.13:0Bad TX CRC packets = Ext3MII 22.7:04.5.4Configuring 1588 Daisy-Chain SPI Time-StampingFor Master VSC8584EV, run these instructions for each port 0-3, as indicated by the “phy” variablebelow:smiwrite phy 31 4smiwrite phy 17 133smiwrite phy 18 0smiwrite phy 16 45088smiwrite phy 17 133smiwrite phy 18 0smiwrite phy 16 47136smiwrite phy 31 0Note:the accesses above can be pasted into a text file and loaded via the customer GUI “Run PHY Script” feature, after substituting the desired port number 0-3 for “phy”above.For Slave VSC8584EV, run the same instructions listed above for Master VSC8584EV for each port 0-3.Then, run the following write only on port 0:smiwrite 0 31 4smiwrite 0 26 0 × c0f7smiwrite 0 31 05Additional InformationFor any additional information or questions regarding the devices mentioned in this document, contactyour local sales representative.Microsemi HeadquartersOne Enterprise, Aliso Viejo,CA 92656 USAWithin the USA: +1 (800) 713-4113Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996Email:***************************© Microsemi. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www. .VPPD-03500。

芯通芯片评估板用户指南 UG-553说明书

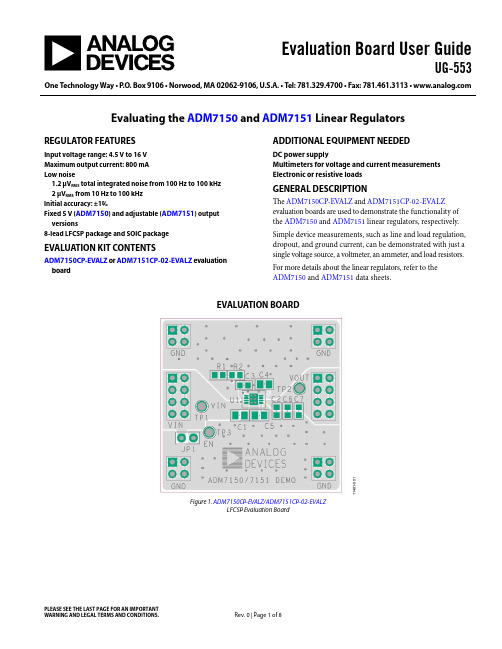

Evaluation Board User GuideUG-553One Technology Way • P .O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • Evaluating the ADM7150 and ADM7151 Linear RegulatorsPLEASE SEE THE LAST PAGE FOR AN IMPORTANT WARNING AND LEGAL TERMS AND CONDITIONS.Rev. 0 | Page 1 of 8REGULATOR FEATURESInput voltage range: 4.5 V to 16 V Maximum output current: 800 mA Low noise1.2 µV RMS total integrated noise from 100 Hz to 100 kHz 2 µV RMS from 10 Hz to 100 kHz Initial accuracy: ±1%Fixed 5 V (ADM7150) and adjustable (ADM7151) output versions8-lead LFCSP package and SOIC packageEVALUATION KIT CONTENTSADM7150CP-EVALZ or ADM7151CP-02-EVALZ evaluation boardADDITIONAL EQUIPMENT NEEDEDDC power supplyMultimeters for voltage and current measurements Electronic or resistive loadsGENERAL DESCRIPTIONThe ADM7150CP-EV AL Z and ADM7151CP-02-EV AL Z evaluation boards are used to demonstrate the functionality of the ADM7150 and ADM7151 linear regulators, respectively. Simple device measurements, such as line and load regulation, dropout, and ground current, can be demonstrated with just a single voltage source, a voltmeter, an ammeter, and load resistors. For more details about the linear regulators, refer to theADM7150 and ADM7151 data sheets.EVALUATION BOARD11481-001Figure 1. ADM7150CP-EVALZ /ADM7151CP-02-EVALZLFCSP Evaluation BoardUG-553Evaluation Board User GuideRev. 0 | Page 2 of 8TABLE OF CONTENTSRegulator Features ............................................................................ 1 Evaluation Kit Contents ................................................................... 1 Additional Equipment Needed ....................................................... 1 General Description ......................................................................... 1 Evaluation Board .............................................................................. 1 Revision History ............................................................................... 2 Evaluation Board Hardware ............................................................ 3 Evaluation Board Configurations .............................................. 3 Output Voltage Measurements ....................................................... 4 Line Regulation ..............................................................................4 Load Regulation ............................................................................5 Dropout Voltage ............................................................................5 Ground Current Measurements ......................................................6 Ground Current Consumption ...................................................6 Schematic ............................................................................................7 Ordering Information .......................................................................8 Bill of Materials (8)REVISION HISTORY11/13—Revision 0: Initial VersionEvaluation Board User GuideUG-553Rev. 0 | Page 3 of 8EVALUATION BOARD HARDWAREEVALUATION BOARD CONFIGURATIONSThe evaluation boards arrive supplied with differentcomponents depending on which version is ordered. Components common to both versions are C1, C2, R3, J1, and J2.Resistors R1 and R2 are used for the ADM7151 adjustable output option. The output voltage is set byV OUT = 1.5 V × (1 + R1/R2).Table 1. Evaluation Board Hardware ComponentsComponent FunctionDescriptionU11 Linear regulator ADM7150ACPZ-5 or ADM7151ACPZ-02 linear regulator. C1 Input capacitor 10 μF input bypass capacitor.C2 Output capacitor 10 μF output capacitor. Required for stability and transient performance. C3 V REF capacitor 1 μF V REF bypass capacitor. C4 BYP capacitor 1 μF bypass capacitor.C5V REG capacitor 10 μF V REG bypass capacitor. C6 and C7 Output capacitor Optional output capacitors.R1 Output divider Sets output voltage with R2 in adjustable option. Short R1 for fixed output voltages. R2 Output divider Sets output voltage with R1 in adjustable option. JP1Jumper Jumper. Connects EN to VIN for automatic startup.1Component varies depending on the evaluation board ordered.UG-553Evaluation Board User GuideRev. 0 | Page 4 of 8OUTPUT VOLTAGE MEASUREMENTSFigure 2. Output Voltage Measurement, LFCSPFigure 2 shows how the evaluation board can be connected to a voltage source and a voltmeter for basic output voltage accuracy measurements. A resistor can be used as the load for the regulator.Ensure that the resistor has a power rating adequate to handle the power expected to be dissipated across it. An electronic load can also be used as an alternative. Ensure that the voltage source can supply enough current for the expected load levels. Use the following steps to connect to a voltage source and voltmeter:1. Connect the negative terminal (−) of the voltage source toone of the GND pads on the evaluation board.2. Connect the positive terminal (+) of the voltage source tothe VIN pad of the evaluation board.3. Connect a load between the VOUT pad and one of theGND pads.4. Connect the negative terminal (−) of the voltmeter to oneof the GND pads.5. Connect the positive terminal (+) of the voltmeter to theVOUT pad. The voltage source can now be turned on. If JP1 is inserted (connecting EN to VIN for automatic startup), the regulator powers up.If the load current is large, the user needs to connect the voltmeter as close as possible to the output capacitor to reduce the effects of IR drops.LINE REGULATIONFor line regulation measurements, the regulator’s output is monitored while its input is varied. For good line regulation, the output must change as little as possible with varying input levels. To ensure that the device is not in dropout during this measurement, V IN must be varied between V OUTNOM + 1.5 V (or 4.5 V , whichever is greater) and V INMAX . For example, for an ADM7150 with fixed 5 V output, V IN needs to be variedbetween 6.5 V and 16 V . This measurement can be repeated under different load conditions. Figure 3 shows the typical line regu-lation performance of an ADM7150 with fixed 5 V output.V O U T (V )V IN (V)16121410864.954.964.974.984.995.005.015.025.035.045.0511481-006Figure 3. Output Voltage vs. Input VoltageEvaluation Board User GuideUG-553Rev. 0 | Page 5 of 8LOAD REGULATIONFor load regulation measurements, the regulator’s output is monitored while the load is varied. For good load regulation, the output must change as little as possible with varying loads. The input voltage must be held constant during this measurement. The load current can be varied from 0 mA to 800 mA. Figure 4 shows the typical load regulation performance of an ADM7150 with fixed 5 V output for an input voltage of 6.5 V .V O U T (V )I LOAD (mA)10001001014.954.964.974.984.995.005.015.025.035.045.0511481-007Figure 4. Output Voltage vs. Load CurrentDROPOUT VOLTAGEDropout voltage can be measured using the configuration shown in Figure 2. Dropout voltage is defined as the input-to-output voltage differential when the input voltage is set to the nominal output voltage. This applies only for output voltages greater than 4.5 V . Dropout voltage increases with larger loads. For more accurate measurements, a second voltmeter can be used to monitor the input voltage across the input capacitor. The input supply voltage may need to be adjusted to account for IR drops, especially if large load currents are used. Figure 5 shows a typical curve of dropout voltage measurements with different load currents.D R O P O U T V O L T A GE (m V )I LOAD (mA)100010010170060050040030020010011481-008Figure 5. Dropout Voltage vs. Load CurrentUG-553Evaluation Board User GuideRev. 0 | Page 6 of 8GROUND CURRENT MEASUREMENTS11481-009Figure 6. Ground Current Measurement, LFCSPFigure 6 shows how the evaluation board can be connected to a voltage source and an ammeter for ground currentmeasurements. A resistor can be used as the load for theregulator. Ensure that the resistor has a power rating adequate to handle the power expected to be dissipated across it. An electronic load can be used as an alternative. Ensure that the voltage source used can supply enough current for the expected load levels.Use the following steps to connect to a voltage source and ammeter:1. Connect the positive terminal (+) of the voltage source tothe VIN pad on the evaluation board.2. Connect the positive terminal (+) of the ammeter to one ofthe GND pads of the evaluation board.3. Connect the negative terminal (−) of the ammeter to thenegative (−) terminal of the voltage source.4. Connect a load between the negative (−) terminal of thevoltage source and the VOUT pad of the evaluation board. The voltage source can now be turned on. If JP1 is inserted (connecting EN to VIN for automatic startup), the regulator powers up.GROUND CURRENT CONSUMPTIONGround current measurements can determine how much current the regulator’s internal circuits are consuming while the circuits perform the regulation function. To be efficient, the regulator needs to consume as little current as possible. Typically, the regulator uses the maximum current when supplying its largest load level (800 mA). Figure 7 shows the typical ground current consumption for various load levels at an input voltage of 6.5 V for an output voltage of 5 V .G R O U N D C U R R E N T (m A )I LOAD (mA)10001001011234567891011481-011Figure 7. Ground Current vs. Load CurrentWhen the device is disabled (EN = GND), the ground current drops to less than 1 µA.Evaluation Board User GuideUG-553Rev. 0 | Page 7 of 8SCHEMATICC311481-003UG-553Evaluation Board User GuideRev. 0 | Page 8 of 8ORDERING INFORMATIONBILL OF MATERIALSTable 2.Quantity Reference Designator DescriptionManufacturer/Vendor Vendor Part Number 1 U1 ADM7150ACPZ-5 or ADM7151ACPZ-02 Analog Devices, Inc. ADM7150ACPZ-5 or ADM7151ACPZ-02 3 C1, C2, C5 Capacitor, MLCC, 10 μF, 25 V, 0805, X5R Murata (or equivalent) GRM216R61E106KA12 2 C3, C4 Capacitor, MLCC, 1 μF, 25 V, 0805, X5R Murata (or equivalent)GRM216R61E105KA12 1 JP1 Header, single, STR, 2 pins Sullins Connector Solutions PEC02SAAN 1R1, R2Resistor, 1%, 0603 caseVishay DaleCRCW0603xxxxFESD CautionESD (electrostatic discharge) sensitive device . Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.Legal Terms and ConditionsBy using the evaluation board discussed herein (together with any tools, components documentation or support materials, the “Evaluation Board”), you are agreeing to be bound by the terms and conditions set forth below (“Agreement”) unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you (“Customer”) and Analog Devices, Inc. (“ADI”), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term “Third Party” includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY . This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. L IMITATION OF L IABIL ITY . THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED “AS IS” AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALL Y DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPL IED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A P ARTICUL AR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER’S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI’S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS ($100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed. ©2013 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. UG11481-0-11/13(0)。

Richtek RT9054 双通道低噪声低掉电电源说明书

RT9054®©Copyright 2017 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.Ordering InformationGeneral DescriptionThe RT9054 is a dual channel, low noise, and low dropout regulator sourcing up to 300mA at each channel. The range of output voltage is from 1.2V to 3.5V by operating from 2.5V to 5.5V input.The RT9054 offers 3% accuracy, extremely low dropout voltage (240mV @ 300mA), and extremely low ground current, only 27μA per LDO. The shutdown current is near zero current which is suitable for battery-power devices.Other features include current limiting, over temperature and output short circuit protection.The RT9054 is short circuit thermal folded back protected.The IC lowers its OTP trip point from 165°C to 110°C when output short circuit occurs (V OUT < 0.4V) providing maximum safety to end users.The RT9054 can operate stably with very small ceramic output capacitors, reducing required board space and component cost. The RT9054 is available in fixed output voltages in the WDFN-6L 1.6x1.6 packages.Portable Power Management 300mA Dual LDO RegulatorFeatures●Wide Operating Voltage Ranges : 2.5V to 5.5V ●Low-Noise for RF Application●No Noise Bypass Capacitor Required ●Fast Response in Line/Load Transient ●TTL-Logic-Controlled Shutdown Input ●Low Temperature Coefficient●Dual LDO Outputs (300mA/300mA)●Ultra-low Quiescent Current 27μA/LDO ●High Output Accuracy 3%●Short Circuit Protection●Thermal Shutdown Protection ●Current Limit Protection●Short Circuit Thermal Folded Back Protection ●Tiny 6-Lead WDFN Packages●RoHS Compliant and Halogen FreeApplications●CDMA/GSM Cellular Handsets ●Battery-Powered Equipment●Laptop, Palmtops, Notebook Computers ●Hand-Held Instruments ●PCMCIA Cards●Portable Information AppliancesMarking InformationFor marking information, contact our sales representative directly or through a Richtek distributor located in your area.VOUT2 > VOUT1 is RecommendedNote :Richtek products are :❝ RoHS compliant and compatible with the current require-ments of IPC/JEDEC J-STD-020.❝ Suitable for use in SnPb or Pb-free soldering processes.RT9054©Copyright 2017 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.Typical Application CircuitPin ConfigurationV OUT2V OUT1VIN EN2VOUT1GNDVOUT2EN1(TOP VIEW)WDFN-6L 1.6x1.6RT9054©Copyright 2017 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.Functional Block DiagramVOUT1VINGNDVOUT2GNDRT9054©Copyright 2017 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.Electrical Characteristics(V IN = V OUTx + 1V, V ENx = V IN , C IN = 1μF, C OUT = 4.7μF, T A = 25°C, unless otherwise specified.)Recommended Operating Conditions (Note 4)●Supply Input Voltage ------------------------------------------------------------------------------------------------------2.5V to 5.5V ●Enable Input Voltage ------------------------------------------------------------------------------------------------------0V to 5.5V●Junction T emperature Range --------------------------------------------------------------------------------------------−40°C to 125°C ●Ambient T emperature Range --------------------------------------------------------------------------------------------−40°C to 85°CAbsolute Maximum Ratings (Note 1)●Supply Input Voltage ------------------------------------------------------------------------------------------------------−0.3V to 7V ●Other I/O Pin Voltages ---------------------------------------------------------------------------------------------------−0.3V to 7V ●Power Dissipation, P D @ T A = 25°CWDFN-6L 1.6x1.6---------------------------------------------------------------------------------------------------------0.571W ●Package Thermal Resistance (Note 2)-----------------------------------------------------------------------------WDFN-6L 1.6x1.6, θJA ----------------------------------------------------------------------------------------------------175°C/W ●Junction T emperature -----------------------------------------------------------------------------------------------------150°C ●Lead Temperature (Soldering, 10 sec.)-------------------------------------------------------------------------------260°C●Storage T emperature Range --------------------------------------------------------------------------------------------−65°C to 150°C ●ESD Susceptibility (Note 3)HBM (Human Body Mode)----------------------------------------------------------------------------------------------2kV MM (Machine Mode)------------------------------------------------------------------------------------------------------200VRT9054©Copyright 2017 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.Note 1. Stresses beyond those listed “Absolute Maximum Ratings ” may cause permanent damage to the device. These arestress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.Note 2. θJA is measured at T A = 25°C on a low effective thermal conductivity single-layer test board per JEDEC 51-3. θJC ismeasured at the exposed pad of the package.Note 3. Devices are ESD sensitive. Handling precaution recommended.Note 4. The device is not guaranteed to function outside its operating conditions.Note 5. The dropout voltage is defined as V IN -V OUT , which is measured when V OUT is V OUT(NORMAL) − 100mV.Note 6. It is guaranteed by design.RT9054©Copyright 2017 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.Typical Operating CharacteristicsOutput Voltage vs. Temperature1.71.751.81.851.9-50-25255075100125Temperature O u t p u t V o l t a g e (V )(°C)Output Voltage vs. Temperature3.23.253.33.353.4-50-25255075100125Temperature O u t p u t V o l ta g e (V )(°C)RT9054-GS, Both I LOAD = 1mA V IN = 3.8V to 4.8VV IN (V)Time (100μs/Div)V OUT1(10mV/Div)4.83.8V OUT2(10mV/Div)Quiescent Current vs. Temperature5055606570-50-25255075100125Temperature Q u i e s c e n t C u r r e n t (u A )(°C)Power On from V INTime (10μs/Div)RT9054-FM, V EN1 = V EN2 = 1.5V Both I LOAD = 10mAV IN (5V/Div)V OUT2(2V/Div)V OUT1(1V/Div)Dropout Voltage vs. Load Current050100150200250300350050100150200250300Load Current (mA)D r o p o u t V o l ta g e (m V )RT9054©Copyright 2017 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.RT9054-GS, Both I LOAD = 100mA V IN= 3.8V to 4.8VV IN (V)Time (100μs/Div)V OUT1(10mV/Div)4.83.8V OUT2(10mV/Div)RT9054-GS, Both I LOAD = 10mA V IN = 3.8V to 4.8VV IN (V)V OUT1(10mV/Div)4.83.8VOUT2(10mV/Div)Time (100μs/Div)RT9054-GS, Both I LOAD = 50mA V IN = 3.8V to 4.8VV IN (V)Time (100μs/Div)V OUT1(10mV/Div)4.83.8V OUT2(10mV/Div)Time (250μs/Div)I OUT(50mA/Div)V OUT2(20mV/Div)V OUT1(20mV/Div)RT9054-GS, I LOAD = 10mA to 50mA V IN = V EN = 4.3VLoad Transient ResponseTime (250μs/Div)I OUT(100mA/Div)V OUT2(20mV/Div)V OUT1(20mV/Div)RT9054-GS, I LOAD = 10mA to 100mA V IN = V EN = 4.3VPower On from ENTime (5μs/Div)RT9054-FM, V IN = 5V I OUT1 = I OUT2 = 50mA(5V/Div)(1V/Div)V EN1 = V EN2V OUT1V OUT2RT9054©Copyright 2017 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.-80-60-40-2020101001000100001000001000000Frequency(Hz)P S R R (d B )1M100k 10k 1k NoiseTime (10ms/Div)RT9054-GS, No LOADV IN = V ENx = 4.5V(By battery)N o i s e (μV /D i v )150100500-50-100-150NoiseTime (10ms/Div)RT9054-GS, I LOAD = 50mA V IN = V ENx = 4.5V(By battery)N o i s e (μV /D i v )3002001000-100-200-300EN Pin Shutdown ResponseTime (50μs/Div)RT9054-FM, V IN = 5V I OUT1 = I OUT2 = 50mA(5V/Div)(1V/Div)V EN1 = V EN2V OUT1V OUT2V EN1(2V/Div)(1V/Div)V EN1V OUT1V OUT2EN1 Pin Shutdown ResponseV EN2V EN2(2V/Div)Time (10ms/Div)EN2 Pin Shutdown Response(1V/Div)V EN1V OUT1V OUT2V EN2V EN1(2V/Div)V EN2(2V/Div)Time (10ms/Div)RT9054©Copyright 2017 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.Application InformationLike any low-dropout regulator, the external capacitors used with the RT9054 must be carefully selected for regulator stability and performance. Using a capacitor value is >1μF on the RT9054 input, and the amount of capacitance can be increased without limit. The input capacitor must be located at a distance of not more than 0.5 inch from the input pin of the IC and returned to a clean analog ground.Any good quality ceramic or tantalum can be used for this capacitor. The capacitor with larger value and lower ESR (equivalent series resistance) provides better PSRR and line-transient response.The output capacitor must meet both requirements for minimum amount of capacitance and ESR in all LDO applications. The RT9054 is designed specifically to work with low ESR ceramic output capacitor under space-saving and performance consideration. Using a ceramic capacitor with value at least 4.7μF and ESR is > 20m Ω on the RT9054 output ensures stability. The RT9054 still works well with output capacitor of other types due to the wide stable ESR range. Figure 1. shows the curves of allowable ESR range as a function of load current for various output capacitor values. Output capacitor of larger capacitance can reduce noise and improve load transient response,stability, and PSRR. The output capacitor should be located not more than 0.5 inch from the VOUT pin of the RT9054and returned to a clean analog ground.Figure 1. Stable Cout ESR RangeThermal ConsiderationsThermal protection limits power dissipation in RT9054.When the operation junction temperature exceeds 170°C,the OTP circuit starts the thermal shutdown function and turns the pass element off. The pass element turns on again after the junction temperature cools by 40°C. The RT9054 lowers its OTP trip level from 170°C to 110°C when output short circuit occurs (V OUT < 0.4V) as shown in Figure 2. It limits the IC case temperature to under 100°C and provides maximum safety to customer while output short circuit occurs.For continuous operation, do not exceed absolute maximum operation junction temperature 125°C. The power dissipation definition in device is :P D = (V IN -V OUT ) x I OUT + V IN x I QThe maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow and temperature difference between junction to ambient. The maximum power dissipation can be calculated by the following formula :P D(MAX) = (T J(MAX) − T A ) /θJAwhere T J(MAX) is the maximum operation junction temperature, T A is the ambient temperature and θJA is the junction to ambient thermal resistance.Figure 2. Short Circuit Thermal Folded Back Protectionwhen Output Short Circuit Occurs (Patent)V OUT Short to GNDV OUTI OUTT SDRegion of Stable C OUT ESR vs. Load Current0.0010.010.111010050100150200250300Load Current (mA)R e g i o n o f S t a b l e C O U TE S R (Ω)R e g i o n o f S t a b l e C O U T E S R (Ω)RT9054©Copyright 2017 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.For recommended operating conditions specification of the IC, the maximum junction temperature is 125°C. The junction to ambient thermal resistance ( θJA is layout dependent ) for WDFN-8L 1.6x1.6 is 175°C/W on the standard JEDEC 51-3 single-layer thermal test board. The maximum power dissipation at T A = 25°C can be calculated by the following formula :P D(MAX) = ( 125°C − 25°C ) / (175°C/W) = 0.571W for WDFN-6L 1.6x1.6 packagesThe maximum power dissipation depends on the operating ambient temperature for fixed T J(MAX) and thermal resistance θJA . For the IC packages, the Figure 3 of de-rating curves allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.Figure 3. Derating Curve of Maximum Power Dissipation00.10.20.30.40.50.60.70.80.910255075100125Ambient Temperature (°C)P o w e r D i s s i p a t i o n (W )W-Type 6L DFN 1.6x1.6 PackageRichtek Technology Corporation5F, No. 20, Taiyuen Street, Chupei CityHsinchu, Taiwan, R.O.C.Tel: (8863)5526789Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.DS9054-04 July 11。

庞力泰(M4)评估板说明书

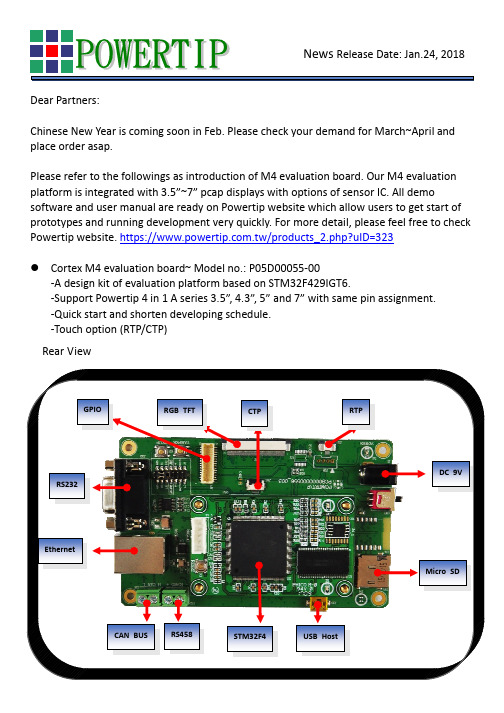

3) User Manual- Please download user manual on Powertip website. https:///products_2.php?uID=323#userm

4) TFT- 4 in 1 A series is available for both Sitronix OGS and Hycon GG types. Please refer to price list for the models with border and borderless CTP. https:///products_2.php?uID=323#tftd

CPU Memory Display

Interface Power Input

RISC Processor

On Board RAM On Board ROM External Storage

Resolution Touch Panel

USB COM Port CAN BUS

Alarm Ethernet

GPIO

RGB TFT

CTP

RTP

RS232

DC 9V

Ethernet

Micro SD

CAN BUS

RS458

STMThe M4 evaluation board is an all-in-one embedded solution with features indicated below.

RTC GPIO DC

Cortex-M4 -- STM32F429IGT6 (180MHz)

8MB SDRAM 16MB SPI Flash 1x Micro SD (under 32G) Up to 1024 RGB x 768 Projected Capacitive Touch 1x USB2.0 Host 1x RS485 or RS232

麦克西姆maxq1004评估板说明书