FPGA VHDL 简易波形发生器 简易信号发生器 EDA课设

采用EDA技术的波形发生器设计

学号:常州大学毕业设计(论文)(2012届)题目学生学院专业班级校内指导教师专业技术职务校外指导老师专业技术职务二○一二年六月采用EDA技术的波形发生器设计摘要:本课题设计了一种采用VHDL硬件描述语言描述并用FPGA实现的正弦波发生器。

本课题的研究结合了FPGA控制、LCD字符显示、DAC芯片驱动等相关知识,运用VHDL语言描述了一个具有幅度可控、频率可调和失真较小的正弦波发生器。

设计平台为Altera公司的Quartus II 8.0软件,采用Altera公司的Cyclone系列FPGA实现。

本设计中的DAC模块采用TLC5620集成芯片来实现,以此来简化设计,并达到本课题的精度要求。

本文详细介绍了正弦波发生器的设计过程,包括系统软件方案设计、系统硬件方案设计、芯片选型、编译仿真平台选择、功能模块划分、时钟分频模块设计、主控模块设计、按键去抖模块设计、TLC5620驱动模块设计和LCD显示模块等部分的设计与实现,对深入研究EDA技术和波形发生器具有重大的意义。

关键词:EDA;FPGA;VHDL;正弦波发生器Waveform Generator Design Using EDA TechnologyAbstract:This paper designs a sine wave generator using FPGA and VHDL language. The research of this paper is a combination of the FPGA controller, the LCD display, the DAC chip drivers and other related knowledge. We use the VHDL language to describe controllable amplitude, frequency adjustable sine wave generator. The design platform is Altera Quartus II 8.0 software and Altera's Cyclone series FPGA chip. In order to simplify the design and achieve the accuracy requirements of this subject, the design of the DAC module uses the TLC5620 chip.This paper describes the design process of the sine wave generator, including system software design, system hardware design, chip selection, the choice of the compile and simulation platform, the clock frequency module design, the main control module design, key debounce module design, the TLC5620 drive module design and the LCD display module design. The design and realization give me a good chance to understand the EDA technologies and waveform generator.Key words:EDA; FPGA; VHDL; Sine Wave Generator目录1引言 (1)1.1研究背景 (1)1.2波形发生器的现状 (1)1.3本文结构及内容安排 (2)2EDA开发技术概述 (3)2.1EDA技术的含义 (3)2.2EDA的工程设计流程 (3)2.3Quartus II 8.0简介 (4)3方案设计与比较 (5)3.1系统功能要求 (5)3.2系统框图 (5)3.3软件方案分析与比较 (5)3.3.1波形函数方案 (5)3.3.2波形ROM方案 (6)3.3.3方案比较 (6)3.4硬件方案设计 (6)3.4.1设计平台与仿真工具选择 (6)3.4.2芯片选择方案 (7)4FPGA的介绍 (9)4.1FPGA的简介 (9)4.1.1背景 (9)4.1.2FPGA与单片机的区别 (10)4.1.3电路设计中FPGA的应用 (11)4.1.4产品设计 (11)4.1.5系统级应用 (11)5系统设计 (12)5.1系统组成及工作原理 (12)6FPGA实现与仿真 (13)6.1顶层模块图 (13)6.2模块详细设计 (13)6.2.1主控模块 (13)6.2.2时钟分频模块 (15)6.2.3按键去抖模块 (16)6.2.4波形存储模块 (17)6.2.5TLC5620驱动模块 (18)6.2.6LCD显示模块 (19)6.3FPGA的实现功能 (19)7结论 (21)参考文献 (22)致谢 (23)附录 (24)1引言1.1研究背景随着现代化集成电路和计算机技术的不断飞跃发展,使得电子产品的设计在市场上的应用更为广泛,而且其实现方法的选择也变得越来越多。

基于VHDL语言信号发生器的设计.EDA课程设计

基于VHDL语言信号发生器的设计1、设计目的1) 掌握使用EDA工具设计信号发生器系统的设计思路和设计方法,体会使用EDA综合过程中电路设计方法和设计思路的不同,理解层次化设计理念。

2) 熟悉在Quartus II环境中,用文本输入方式与原理图输入方式完成电路的设计,同时掌握使用这两种方式相结合的EDA设计思路。

3) 通过这一部分的学习,对VHDL语言的设计方法进行进一步的学习,对其相关语言设计规范进行更深层次的掌握,能够更加熟练的做一些编程设计2、设计的主要内容和要求通过使用VHDL语言及Quartus II软件,设计多功能信号发生器的每个模块,将正弦波模块,方波模块,三角波模块,阶梯波模块创建相应的元件符号,同时设计好4选1数据选择器模块,再通过原理图输入方式,将各个模块组合起来,设计成一个完整的多种信号发生器电路,同时将各个模块单独进行仿真,设计各个模块的仿真波形,最后进行总原理图电路仿真,设计该信号发生器的总的仿真波形。

信号发生器:体现在它能自动的实现四种波形的转换。

根据题目的分析与整体构思可知,要完成设计任务必须完成以下要求:1、设计好用于波形切换的四路数据选择器selector4_1;2、设计好用于总电路设计的各个信号输出模块;3、设计好数模(D/A)转换器。

3、整体设计方案基本设计方案:在现有单一信号发生器的基础上,加上其它信号模块,通过组合与设计,用数模转换器(D/A)将选中的信号源发出的信号由数字信号转换为模拟信号,再用示波器显示出来,其信号发生器的结构框图如图3.1所示。

信号发生器由各个单一信号模块组合而成,其中信号产生模块将产生所需的各种信号,信号发生器的控制模块可以用数据选择器实现,用4选1数据选择器实现对四种信号的选择。

最后将波形数据送入D/A转换器,将数字信号转换为模拟信号输出。

用示波器测试D/A转换器的输出,可以观测到4种信号的输出。

时钟信号信号产生信号控制D/A转换输出信号选择信号图3.1信号发生器结构框图通过查找资料把各类信号模块的程序输入到Quartus Ⅱ中进行运行仿真,每一步都要慎重小心,错误难免的,还需要通过课本和资料一一更正。

EDA课程设计(信号发生器)

课程设计报告2010 ~ 2011 学年第一学期设计题目:基于FPGA可调信号发生器学院:专业:课程名称: EDA原理与应用学生姓名:时间: 2011年1月指导教师:目录一、系统总体设计---------------------------------------------------------------------2二、系统功能模块设计---------------------------------------------------------------21、矩阵键盘模块------------------------------------------------------------32、频率显示模块-----------------------------------------------------------113、波形数据ROM初始化数据文件设计--------------------------------134、频率、幅度改变模块--------------------------------------------------145、DA转化模块-----------------------------------------------------------186、示波器检测-------------------------------------------------------------18三、结束语---------------------------------------------------------------------------191、矩阵键盘模块:矩阵键盘又称为行列式键盘,它是用4条I/O线作为行线,4条I/O线作为列线组成的键盘。

在行线和列线的每一个交叉点上,设置一个按键,这样键盘中按键的个数是4×4个。

这种行列式键盘结构能够有效地提高系统中I/O口的利用率。

EDA毕业论文(设计)--基于FPGA的波形发生器设计 光学测试课程设计 模版+附件(程序,图片等)

摘要各种各样的信号是通信领域的重要组成部分,其中正弦波、三角波和方波等是较为常见的信号。

在科学研究及教学实验中常常需要这几种信号的发生装置。

为了实验、研究方便,研制一种灵活适用、功能齐全、使用方便的信号源是十分必要的。

本次关于产生三角波或其它任意波形的设计方案,不仅在理论和实践上都能满足实验的要求,而且具有很强的可行性。

该信号源的特点是:体积小、价格低廉、性能稳定、实现方便、功能齐全。

关键词:正弦波;三角波;FPGA;ABSTRACTVarious signal is an important part of telecommunication field, including sine wave, triangle wave and square-wave etc is more common signal. In scientific research and teaching experiment often need this several signal generator. In order to test, research is convenient, develop a flexible application, complete functions, use convenient source is very necessary.This about produce triangle wave andotner different kinds of waves of design scheme, not only in theory and in practice can satisfy experiment requirement, and has a strong feasibility. The signal features are: small volume, price cheap and stable performance and achieve convenient, complete function.Keywords: sine wave;Triangle wave;FPGA;目录摘要 01.前言 (2)2.FPGA工作原理 (3)3.FPGA基本特点 (4)4.系统设计 (5)4.1设计要求 (5)4.2总体设计方案 (5)4.2.1方案比较 (5)4.2.2系统组成及工作原理 (6)5.单元电路设计 (8)5.1输入模块设计 (8)5.2波形发生模块的设计 (8)5.3关于D/A转换模块的设计 (9)5.4滤波电路模块的设计 (10)6.软件设计与仿真 (11)6.1软件设计思路 (11)6.2系统仿真 (11)7.系统测试 (13)7.1测试使用的仪器 (13)7.2测试方法 (13)7.3指标测试和测试结果 (13)8.设计总结 (14)参考文献 (15)附录 (16)1.前言波形发生器是信号源的一种,它是具有信号源所具有的特点,更因它高的性能优势而备受人们青睐。

波形发生器课程设计vhdl

波形发生器课程设计vhdl一、教学目标本课程旨在通过学习VHDL(硬件描述语言),让学生掌握波形发生器的设计与仿真。

通过本课程的学习,学生应能理解VHDL的基本语法和编程技巧,能够运用VHDL设计简单的数字电路,特别是波形发生器。

此外,通过课程实践,培养学生分析问题、解决问题的能力,以及团队合作和沟通交流的能力。

具体来说,知识目标包括:1.掌握VHDL的基本语法和编程技巧。

2.理解波形发生器的工作原理和设计方法。

技能目标包括:1.能够运用VHDL设计简单的数字电路。

2.能够独立完成波形发生器的设计与仿真。

情感态度价值观目标包括:1.培养学生的创新意识和实践能力。

2.培养学生团队合作和沟通交流的能力。

二、教学内容本课程的教学内容主要包括VHDL基本语法、数字电路设计方法和波形发生器的设计与仿真。

1.VHDL基本语法:包括数据类型、信号声明、实体和架构、过程和函数、线网和赋值语句等。

2.数字电路设计方法:包括组合逻辑电路、时序逻辑电路和触发器的设计方法。

3.波形发生器的设计与仿真:包括正弦波、方波、三角波等波形发生器的设计方法,以及相应的仿真测试。

三、教学方法为了提高学生的学习兴趣和主动性,本课程将采用多种教学方法,包括讲授法、案例分析法、实验法和讨论法等。

1.讲授法:用于讲解VHDL基本语法和数字电路设计方法。

2.案例分析法:通过分析实际案例,让学生学会波形发生器的设计与仿真。

3.实验法:让学生动手实践,独立完成波形发生器的设计与仿真。

4.讨论法:在课堂上引导学生进行思考和讨论,培养团队合作和沟通交流的能力。

四、教学资源为了支持教学内容和教学方法的实施,丰富学生的学习体验,我们将选择和准备以下教学资源:1.教材:《数字电路设计与VHDL编程》等。

2.参考书:《VHDL完全学习手册》、《数字电路与逻辑设计》等。

3.多媒体资料:包括PPT课件、教学视频、在线课程等。

4.实验设备:计算机、VHDL仿真软件(如ModelSim)、示波器等。

课题设计 基于FPGA的多功能波形发生器的设计

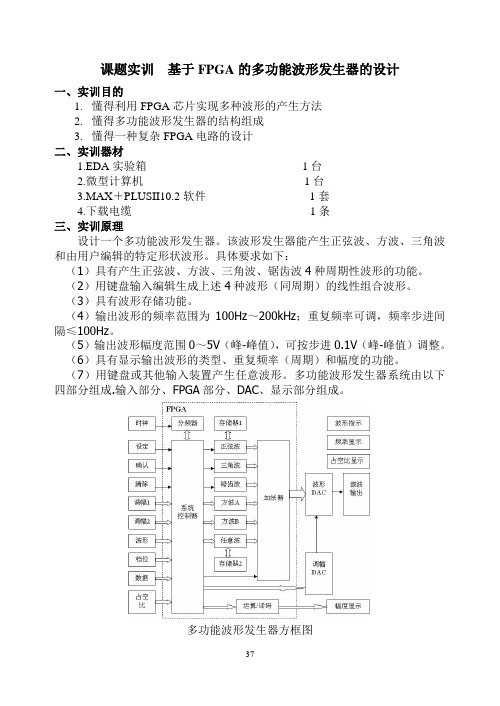

课题实训基于FPGA的多功能波形发生器的设计一、实训目的1.懂得利用FPGA芯片实现多种波形的产生方法2.懂得多功能波形发生器的结构组成3.懂得一种复杂FPGA电路的设计二、实训器材1.EDA实验箱1台2.微型计算机1台3.MAX+PLUSII10.2软件1套4.下载电缆1条三、实训原理设计一个多功能波形发生器。

该波形发生器能产生正弦波、方波、三角波和由用户编辑的特定形状波形。

具体要求如下:(1)具有产生正弦波、方波、三角波、锯齿波4种周期性波形的功能。

(2)用键盘输入编辑生成上述4种波形(同周期)的线性组合波形。

(3)具有波形存储功能。

(4)输出波形的频率范围为100Hz~200kHz;重复频率可调,频率步进间隔≤100Hz。

(5)输出波形幅度范围0~5V(峰-峰值),可按步进0.1V(峰-峰值)调整。

(6)具有显示输出波形的类型、重复频率(周期)和幅度的功能。

(7)用键盘或其他输入装置产生任意波形。

多功能波形发生器系统由以下四部分组成.输入部分、FPGA部分、DAC、显示部分组成。

多功能波形发生器方框图四、设计程序(参考程序)--功能:实现4种常见波形正弦、三角、锯齿、方波(A、B)的频率、幅度可控输出(方波--A的占空比也是可控的),可以存储任意波形特征数据并能重现该波形,还可完成--各种波形的线形叠加输出。

--说明:SSS(前三位)和SW信号控制4种常见波形种哪种波形输出。

4种波形的频率、--幅度(基准幅度A)的调节均是通过up、down、set按键和4个BCD码置入器以及一--个置入档位控制信号(ss)完成的(AMP的调节范围是0~5V,调节量阶为1/51V)。

--其中方波的幅度还可通过u0、d0调节输出数据的归一化幅值(AMP0)进行进一步--细调(调节量阶为1/(51*255)V)。

方波A的占空比通过zu、zp按键调节(调节--量阶1/64*T)。

系统采用内部存储器——RAM实现任意输入波形的存储,程序只支--持键盘式波形特征参数置入存储,posting 为进入任意波置入(set)、清除(clr)状态--控制信号,SSS控制存储波形的输出。

eda课程信号发生器课程设计

eda课程信号发生器课程设计一、课程目标知识目标:1. 学生能理解EDA课程中信号发生器的原理与功能,掌握相关电子元件的工作特性。

2. 学生能够掌握信号发生器的分类、特点及应用场景,了解各类信号发生器的优缺点。

3. 学生能够运用所学知识,分析并设计简单的信号发生器电路。

技能目标:1. 学生能够熟练运用EDA软件进行信号发生器电路的设计、仿真与调试。

2. 学生能够独立完成信号发生器的硬件搭建,并进行基本的性能测试。

3. 学生能够通过实际操作,提高动手实践能力,培养解决实际问题的能力。

情感态度价值观目标:1. 学生能够培养对电子工程的兴趣,激发创新意识,形成主动学习的习惯。

2. 学生能够培养团队协作精神,学会与他人沟通交流,共同解决问题。

3. 学生能够认识到信号发生器在现代社会中的重要作用,增强社会责任感和使命感。

本课程针对高年级学生,在分析课程性质、学生特点和教学要求的基础上,明确以上课程目标。

通过分解目标为具体的学习成果,使学生在掌握专业知识的同时,提高实践操作能力和团队协作能力,培养良好的情感态度价值观。

为后续的教学设计和评估提供明确的方向。

二、教学内容本章节教学内容依据课程目标,紧密结合教材,确保科学性和系统性。

主要内容包括:1. 信号发生器原理与分类:讲解信号发生器的基本原理、功能及分类,重点介绍函数发生器、脉冲发生器等常见类型的工作原理及应用。

2. 电子元件特性分析:分析常用电子元件(如运放、晶体管、二极管等)在信号发生器中的作用,掌握其工作特性。

3. 信号发生器电路设计:根据实际需求,设计不同类型的信号发生器电路,分析电路性能,优化设计方案。

4. EDA软件应用:教授学生如何使用EDA软件进行信号发生器电路的设计、仿真与调试,提高实际操作能力。

5. 硬件搭建与性能测试:指导学生搭建信号发生器硬件电路,进行基本性能测试,分析测试结果,找出问题并解决。

教学内容安排如下:1. 第1周:信号发生器原理与分类,电子元件特性分析。

EDA课程设计基于FPGA的任意波形发生器

EDA课程设计__基于FPGA的任意波形发生器学院:通信与电子工程学院摘要本文要紧探讨了应用FPGA灵活可重复编程和方便在系统重构的特性,以Verilog HDL为设计语言,运用QuarrtusII软件,将硬件功能以软件设计来描述,提高了产品的集成度,缩短开发周期。

所设计的波形发生器可产生正弦波(sina_wave)、锯齿波(swat_wave)、矩形波(squr_wave)、三角波(trig_wave)四种信号,能够实现信号的转换而且频率可调;关键字:任意波形发生器 FPGA Verilog HDL QuartusIIAbstractThis paper explored the application of flexible and reprogrammable FPGA and convenience features in the system reconfiguration to Verilog HDL design language, the hardware functions to software design to describe and improve the integration of products and shorten the development cycle. Waveform generator designed to produce sine wave (sina_wave), ramp (swat_wave), rectangular wave (squr_wave), triangular wave (trig_wave) four signals, to achieve signal conversion and frequency adjustable;Keywords: Arbitrary Waveform Generator FPGA Verilog HDL QuartusII目录摘要 (I)ABSTRACT (II)目录 (III)第 1章绪论 (1)概述 (1)任意波形发生器的功能 (1)国内外进展现状 (2)第2章波形发生器的大体理论 (4)FPGA简介 (4)Verilog语言简介 (4)Verilog语言概述 (4)VerilogHDL大体结构 (5)Q uarrtusII概述 (6)第3章方案设计 (8)系统介绍 (8)波形发生器各个模块设计 (9)Wave_gen 模块 (9)波形数据存储 ROM 模块 (9)第4章波形发生器软件仿真 (11)设计平台及仿真工具 (11)仿真进程 (11)结论 (14)附录 (16)第 1章绪论概述波形发生器是一种经常使用的信号源,普遍应用于电子电路,自动操纵系统,教学实验等领域,目前利用显现了大量能够产生多种波形且性能稳固的任意波形发生器,但大多数方案都是基于串行或并行总线进行数据的传输,这种方案尽管本钱较低,但系统的实时性较差,难以知足复杂波形的大数据量的传输要求。

《EDA(VHDL)课程设计》任务书

3.四组数字智力抢答器的VHDL设计(每班1-30号的双号选择)

系统设计要求是:

(1)设计制作一个可容纳四组参赛者的数字智力抢答器,每组设置一个抢答按钮供抢答者使用。

(1)主、支干道各设有一个绿、黄、红指示灯,两个显示数码管。

(2)主干道处于常允许通行状态,而支干道有车来才允许通行。

(3)当主、支道均有车时,两者交替允许通行,主干道每次放行45s,支干道每次放行25s,在每次由亮绿灯变成亮红灯的转换过程中,要亮5s的黄灯作为过渡,并进行减计时显示。

设计的基本要求

3.输入、输出接口说明

4.报告中有分频器、定时器相关模块的功能仿真和时序仿真结果。

5.编写内容充实、完整和规范的课程设计报告书。

6.课程设计报告要求校对仔细,无错字,A4纸打印,左侧装订。

主要参考文献

[1]谭会生,张昌凡.EDA技术及应用.西安:西安电子科技大学出版社,2006,12.

[2]潘松,黄继业.EDA技术实用教程.北京:科学出版社,2008,8.

2.99分钟定时器的VHDL设计(每班1-30号的单号选择)

任务要求:具有整体清零(reset)功能,定时99分钟。以秒速度递增至99分钟停止,启动报警(cout)5秒钟。具有置位(cn)控制,即cn高电平时,clk脉冲上升沿到来,计数加一;cn低电平时,置位结束,进入倒计时阶段,以秒速度使输出计数减一至零结束,并同时报警(cout)5秒钟。

为了防止雷同,建议每班1-4号设计2.5分频,5-8号设计3.5分频,9-12号设计4.5分频,13-16号设计5.5分频,17-20号设计6.5分频,21-24号设计7.5分频,25-28设计8.5分频,29-32设计9.5分频,33-36设计10.5分频,37-40号设计11.5分频,41-44号设计12.5分频计数器。

EDA课程设计的信号发生器

重庆大学城市科技学院电气信息学院EDA课程设计报告课程题目函数信号发生器指导教师专业组员学号日期一摘要EDA技术作为现代电子设计的核心,它依赖于功能强大的计算机,在EDA 工具软件平台上,对以硬件描述语言HDL为系统逻辑描述手段完成的设计文件,自动的完成设计文件,自动的完成逻辑编译,逻辑化简,逻辑分割,逻辑综合,结构综合(布局布线),以及逻辑优化和仿真测试,直到完成既定的电子线路系统功能。

随着基于FPGA的EDA技术的发展和应用领域不断的扩大与深入,EDA技术在电子信息、通信、自动控制及计算机应用等领域的重要性日益突出。

随着技术市场与人才市场对EDA技术的需求不断提高,产品的市场效率和技术要求也将会影响到教学与科研。

本设计是一个基于VHDL的采用自顶向下设计方法实现的多功能函数信号发生器,该设计方法具有外围电路简单,程序修改灵活和调试容易等特点,并通过计算机仿真和实验证明了设计的正确性。

关键词:FPGA 信号发生器 VHDL 自顶向下二题目分析1、设计目的设计一个信号发生器,用于产生正弦波、方波、三角波、锯齿波信号2、设计要求设计一个信号发生器(1).能产生正弦波、方波、三角波、锯齿波。

(2).能够选择输出不同的波形。

(3).能够调节输出波形的频率。

三硬件电路设计由题目分析可知,要完成整体设计,可通过QuartusⅡ设计出以下各个模块的原理图:1)分频器的原理图2)地址发生器的原理图3)正弦波发生器的原理图4)方波信号发生器的原理图5)锯齿波信号发生器的原理图6)三角波信号发生器的原理图7)四选一选择器原理图其中各波形数据存储ROM的HEX数据文件分别如下各图所示:图3.9 正弦波数据图3.10 方波数据图3.11 锯齿波数据图3.12 三角波数据经过对设计要求的仔细分析与思考,把以上各模块根据其功能和设计思路设计出总的系统原理图如图3.13所示:图3.13 系统综合原理图对整个系统进行硬件测试的引脚设定锁定如图3.14所示,测试时采用的是GW48-EDA系统的电路模式6.图3.14 引脚锁定图四程序设计(1)数控分频器的程序设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DVF ISPORT( DIN: IN STD_LOGIC_VECTOR(7 DOWNTO 0);CLK: IN STD_LOGIC;FOUT:OUT STD_LOGIC);END DVF;ARCHITECTURE behav of DVF ISSIGNAL FULL: STD_LOGIC;BEGINP_REG: PROCESS(CLK)VARIABLE CNT8:STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINIF CLK'EVENT AND CLK='1' THENIF CNT8="11111111" THENCNT8:=DIN;FULL<='1';ELSE CNT8:=CNT8+1;FULL<='0';END IF;END IF;END PROCESS P_REG;P_DIV:PROCESS(FULL)VARIABLE CNT2:STD_LOGIC;BEGINIF FULL'EVENT AND FULL='1' THENCNT2:=NOT CNT2;IF CNT2='1' THEN FOUT<='1'; ELSE FOUT<='0'; END IF;END IF;END PROCESS P_DIV;END behav;(2)地址发生器的程序设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT6B ISPORT (CLK,RST,EN : IN STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR(5 DOWNTO 0));END CNT6B;ARCHITECTURE behav OF CNT6B ISSIGNAL CQI : STD_LOGIC_VECTOR(5 DOWNTO 0);BEGINPROCESS(CLK, RST, EN)BEGINIF RST = '1' THEN CQI <= (OTHERS =>'0') ; --计数器异步复位ELSIF CLK'EVENT AND CLK='1' THEN --检测时钟上升沿IF EN = '1' THEN CQI <= CQI + 1;END IF;END IF;END PROCESS;DOUT<=CQI;END behav;(3)四选一选择器的程序设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY MUL41 ISPORT(A,B,C,D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);S1,S0:IN STD_LOGIC;Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY MUL41;ARCHITECTURE ONE OF MUL41 ISSIGNAL S:STD_LOGIC_VECTOR(1 DOWNTO 0);BEGINS<= S1 & S0;WITH S SELECTY<= A WHEN "00" ,B WHEN "01" ,C WHEN "10" ,D WHEN "11" ,"ZZZZZZZZ" WHEN OTHERS;END;(4)其余各波形数据存储ROM的设计可以利用MegaWizard Plug-In Manager定制信号数据ROM宏功能块,并将其相应的波形数据加载与定制的ROM中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

简易信号发生器1引言信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

它能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波等,在电路实验和设备检测中具有十分广泛的用途。

例如在通信、广播、电视系统中,都需要射频(高频)发射,这里的射频波就是载波,把音频(低频)、视频信号或脉冲信号运载出去,就需要能够产生高频的振荡器。

在工业、农业、生物医学等领域内,如高频感应加热、熔炼、淬火、超声诊断、核磁共振成像等,都需要功率或大或小、频率或高或低的信号发生器。

本设计采用FPGA来设计制作多功能信号发生器。

该信号发生器可以产生锯齿波、三角波、方波等波形。

2 FPGA简介FPGA(Field-Programmable Gate Array)即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

与传统们阵列和掩模可编程门阵列(MPGA)相比,FPGA具有很多的优点,传统门阵列可以用来设计任何电路,但是只能在工厂中一次性编程,而且还需要针对该电路的特定的掩模。

FPGA是标准通用器件。

使用其代替MPGA,可以将设计时间由几个月缩短至几小时,并且使设计更加简单,从而减少了错误修改和设计指标变更的花费。

FPGA器件在结构上,由逻辑功能块排列为阵列,它的结构可以分为三个部分:可编程快CLB(Configurable Logic Blocks)、可编程I/O模块IOB(Input Block)和可编程内部连线PI(Programmable Interconnect)。

CL B在器件中排列为阵列,周围有环形内部连线,IOB 分布在四周的管脚上。

FPGA也存在缺点,FPGA中,每个可编程的点都有电阻和电容。

电阻和电容的使用减慢了信号的传输速度,所以FPGA的速度比传统门阵列要低,而且,FPGA中互联延迟是不可预测的。

FPGA的基本特点主要有:一、采用FPGA设计ASIC电路,用户不需要投片生产,就能得到合用的芯片。

二、FPGA可做其它全定制或半定制ASIC电路的中试样片。

三、FPGA内部有丰富的触发器和I/O引脚。

四、FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

五、FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TT L电平兼容。

使用FPGA时,可以根据不同的配置模式,采用不同的编程方式。

加电时,FPGA芯片将EPROM中数据读入片内编程RAM中,配置完成后,FPGA进入工作状态。

掉电后,FPGA恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。

FPGA的编程无须专用的FPGA编程器,只须用通用的EPROM、PROM编程器即可。

当需要修改FPGA功能时,只需换一片EPROM即可。

这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。

因此,FPGA的使用非常灵活。

FPGA有多种配置模式:并行主模式为一片FPGA 加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理器对其编程。

3 VHDL & Verilog简介VHDL(Very High Speed Integrated Circuit Hardware Description Language,超高速集成电路硬件描述语言)是一种用来描述数字系统行为和结构的硬件描述语言,被广泛的运用于描述和仿真各种数字系统,小到几个门,大到许多复杂集成电路相连的系统。

VHDL诞生于1982年,是由美国国防部开发的一种快速设计电路的工具,目前已经成为IEEE(The Institute of Electrical and Electronics Engineers)的一种工业标准硬件描述语言。

相比传统的电路系统的设计方法,VHDL具有多层次描述系统硬件功能的能力,支持自顶向下(Top to Down)和基于库(Library Based)的设计的特点,因此设计者可以不必了解硬件结构。

从系统设计入手,在顶层进行系统方框图的划分和结构设计,在方框图一级用VHDL对电路的行为进行描述,并进行仿真和纠错,然后在系统一级进行验证,最后再用逻辑综合优化工具生成具体的门级逻辑电路的网表,下载到具体的FPGA器件中去,从而实现可编程的专用集成电路(ASIC)的设计。

Verilog也是一种流行的硬件描述语言,他是由工业界开发的,1984年,Verilog作为一种私用的硬件描述语言,由Gateway Design Automation公司给出,1988年,Synopsis公司为Verilog开发了综合工具。

1995年,Verilog成为IEEE的一个标准。

Verilog 适合算法级,寄存器级,逻辑级,门级和版图级等各个层次的设计和描述。

VHDL的语法是基于ADA语言的,而Verilog的语法是基于C语言的。

由于是基于C 语言,所以它更容易掌握,但是VHDL语言在设计和描述大型系统时具有突出优势。

目前两种语言各占一半市场份额,两种语言都可以满足数字系统设计者的需求。

本设计中采用VHDL语言进行设计。

4 设计工具简介本次设计是基于Altera公司的QuartusII软件。

Quartus II 是Altera公司的综合性PLD开发软件,支持原理图、VHDL、VerilogHDL 以及AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

QuartusII支持Altera的IP核,包含了LPM/MegaFuction宏功能模块库,使用它,可以简化设计的复杂性,加快设计速度。

QuartusII平台支持一个工作组环境下的设计要求,其中包括支持基于Internet的协作设计。

此外,QuartusII通过和DSP Builder工具与Matlab/SIMULINK相结合,可以方便地实现各种DSP应用系统;支持Altera的片上可编程系统开发,集系统级设计、嵌入式软件设计、可编程逻辑设计于一体,是一种综性的开发平台。

5 系统设计基于VHDL语言设计一个多功能信号发生器,通过选择输入信号,可以输出递增锯齿波、递减锯齿波、三角波、方波等四种信号。

信号发生器的控制模块可以选用数据选择器实现,4种信号的数据选择可以使用4选1数据选择器实现。

5.1 VHDL程序语言基本设计一个VHDL语言的设计程序描述的是一个电路单元,这个电路单元可以是一个门电路,或者是一个计数器,也可以是一个CPU,一般情况下,一个完整的VHDL语言程序至少包括实体、结构体和程序包三个部分。

实体给出电路单元的外部输入输出接口信号和引用信息,结构体给出了电路单元的内部结构和信号的行为特点,程序包定义在设计结构体和实体中将用到的常数、数据类型、子程序和设计好的电路单元等。

第一部分是程序包,程序包是用VHDL语言编写的共享文件,定义在设计结构体和实体中将要用到的常数、数据类型、子程序和设计好的电路单元等,放在文件目录名称为IEEE 的程序包库中。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;第二部分是程序的实体,定义电路单元的输入/输出引脚名称。

程序的实体名称可以任意取,但必须与VHDL程序的文件名称相同。

实体的标示符是ENTITY,实体以ENTITY 开头,以END结束。

ENTITY fulladder ISPORT(a,b,Ci:in std_logic;Co,s: out std_logic_vector(7 downto 0));END fulladder;其中,定义了a,b, Ci为输入信号引脚,定义Co,s为输出信号引脚。

第三部分是程序的结构体,具体描述电路的内部结构和逻辑功能。

结构体有三种描述方式,分别是行为(BEHA VIOR)描述方式、数据流(DATAFLOW)描述方式和结构描述方式。

其中数据流描述方式又被称为寄存器(RTL)描述方式。

结构体以表示ARCHITECHTURE开头,以END结尾。

结构体的名称可以任取。

architecture behav of fulladder isBEGINs<=a xor b xor Ci;Co<=(a and b)or(a and Ci)or(b and Ci);END fulladder上面程序段中结构体的描述方式属于程序流描述方式。

以上三段程序是一个完整的VHDL 程序段,实现的功能是一位全加器。

5.2 波形发生器设计采用DDS 技术可以很方便地产生各种高质量的波形。

DDS 技术是从相位概念出发之结合成所需要波形的一种频率合成技术。

以正弦波为例,首先要按照一定的采样点数将正弦波形一个周期的数据信息存于ROM 表中,表中包含着一个周期正弦波的数字幅度信息,每个地址对应正弦波中0到360度范围内的一个相位点的幅度值,查找表时即是把输入的地址相位信息映射成正弦波幅度的数字量信号,通过设置的输出端口输出。

在实物设计中,可以使用D/A 接口来实现波形信号的输出。

为简化设计过程,本设计并未采用DDS 技术,而是采用描点输出的方式,实现波形发生器的设计。

程序中设置一个波形的起始点,经过比较、计算得出波形的其他数值,将这些点依次连续输出,从而实现波形的仿真。

以递增锯齿波为例,首先定义初始点为 tmp=“00000000”;在时钟上升沿到来时,执行tmp<=tmp+1;语句,同时将tmp 输出,当 tmp=“11111111”;时,将tmp 值清零,执行下一个循环。

在本设计中,采用QuartusII 软件仿真,所以可以通过波形文件直观的反映出输出的数字量的变化情况,以达到波形输出的仿真。

设计中分别对四种波形进行编程,编译无误后,封装生成模块文件,以供在后面的顶层电路设计中使用。

图5-1 四种波形封装图块本设计中设置了四种波形,分别是递增锯齿波、递减锯齿波、三角波、方波。

四种波形通过一个4选1数据选择器来实现选择性输出。

5.3 四选一数据选择器设计可以采用集成四选一数据选择器CT54153/CT74153,也可以使用软件编程生成模块的方式实现数据四选一的功能。

在本设计中采用后者,程序中,为每一种波形分配一个通道,并为之赋予一唯一的代码,当在sel端输入不同的代码时,被选中的通道打开,响应的波形发生模块产生波形。