内存芯片封装

芯片封装类型图鉴

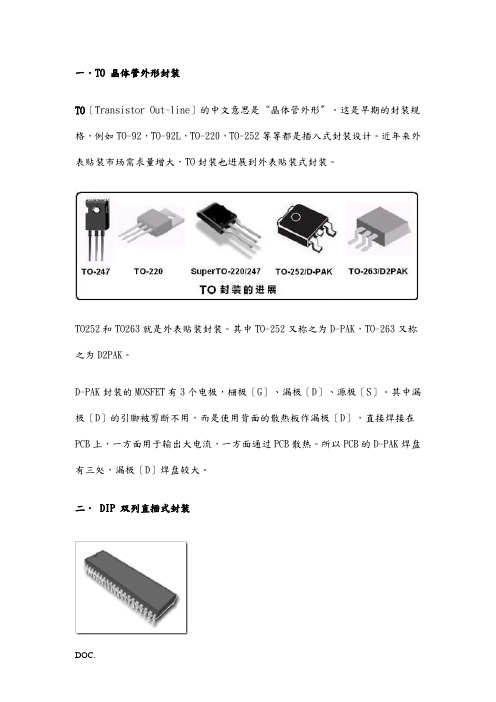

一.TO 晶体管外形封装TO〔Transistor Out-line〕的中文意思是“晶体管外形〞。

这是早期的封装规格,例如TO-92,TO-92L,TO-220,TO-252等等都是插入式封装设计。

近年来外表贴装市场需求量增大,TO封装也进展到外表贴装式封装。

TO252和TO263就是外表贴装封装。

其中TO-252又称之为D-PAK,TO-263又称之为D2PAK。

D-PAK封装的MOSFET有3个电极,栅极〔G〕、漏极〔D〕、源极〔S〕。

其中漏极〔D〕的引脚被剪断不用,而是使用背面的散热板作漏极〔D〕,直接焊接在PCB上,一方面用于输出大电流,一方面通过PCB散热。

所以PCB的D-PAK焊盘有三处,漏极〔D〕焊盘较大。

二. DIP 双列直插式封装DIP(DualIn-line Package)是指采用双列直插形式封装的集成电路芯片,绝大多数中小规模集成电路(IC)均采用这种封装形式,其引脚数一般不超过100个。

封装材料有塑料和陶瓷两种。

采用DIP封装的CPU芯片有两排引脚,使用时,需要插入到具有DIP结构的芯片插座上。

当然,也可以直接插在有一样焊孔数和几何排列的电路板上进展焊接。

DIP封装结构形式有:多层陶瓷双列直插式DIP,单层陶瓷双列直插式DIP,引线框架式DIP〔含玻璃陶瓷封接式,塑料包封结构式,陶瓷低熔玻璃封装式〕等。

DIP封装具有以下特点:1.适合在PCB (印刷电路板)上穿孔焊接,操作方便。

2.比TO型封装易于对PCB布线。

3.芯片面积与封装面积之间的比值较大,故体积也较大。

以采用40根I/O引脚塑料双列直插式封装(PDIP)的CPU为例,其芯片面积/封装面积=(3×3)/(15.24×50)=1:86,离1相差很远。

〔PS:衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。

如果封装尺寸远比芯片大,说明封装效率很低,占去了很多有效安装面积。

芯片封装类型图解

芯片封装类型图解本文介绍了常见的集成电路封装形式,包括BGA、CPGA、FBGA、JLCC、LDCC、LQFP100L、PCDIP、PLCC、PPGA、PQFP、TQFP100L、TSBGA217L、TSOP、CSP、SIP、ZIP、S-DIP、SK-DIP、PGA、SOP、MSP和QFP等。

SIP是单列直插式封装,引脚在芯片单侧排列,与DIP基本相同。

ZIP是Z型引脚直插式封装,引脚比SIP粗短些,节距等特征也与DIP基本相同。

S-DIP是收缩双列直插式封装,引脚在芯片两侧排列,引脚节距为1.778mm,芯片集成度高于DIP。

SK-DIP是窄型双列直插式封装,除了芯片的宽度是DIP的1/2以外,其它特征与DIP相同。

PGA是针栅阵列插入式封装,封装底面垂直阵列布置引脚插脚,插脚节距为2.54mm或1.27mm,插脚数可多达数百脚,用于高速的且大规模和超大规模集成电路。

SOP是小外型封装,表面贴装型封装的一种,引脚端子从封装的两个侧面引出,字母L状,引脚节距为1.27mm。

MSP是微方型封装,表面贴装型封装的一种,又叫QFI等,引脚端子从封装的四个侧面引出,呈I字形向下方延伸,没有向外突出的部分,实装占用面积小,引脚节距为1.27mm。

QFP是四方扁平封装,表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈L字形,引脚节距为1.0mm、0.8mm、0.65mm、0.5mm、0.4mm、0.3mm,引脚可达300脚以上。

SVP是一种表面安装型垂直封装,其引脚端子从封装的一个侧面引出,中间部位弯成直角并与PCB键合,适用于垂直安装,实装占有面积很小。

其引脚节距为0.65mm和0.5mm。

LCCC是一种无引线陶瓷封装载体,其四个侧面都设有电极焊盘而无引脚,适用于高速、高频集成电路封装。

PLCC是一种无引线塑料封装载体,适用于高速、高频集成电路封装,是一种塑料封装的LCC。

SOJ是一种小外形J引脚封装,其引脚端子从封装的两个侧面引出,呈J字形,引脚节距为1.27mm。

CM8501、CM8501A主板内存供电控制芯片

CM8501/CM8501ACM8501、CM8501A 是主板中常用的内存供电控制芯片,输出电流为1.5A 。

两者在封装形式上有所区别: CM8501采用PSOP-16封装,CM8501A 采用PSOP-8封装。

CM8501A 的内部电路框图SDAGNDVCCQVCCA4321振荡器锯齿波发生器100K100Km比较器SQo误差放大器-RQ++c-.20PFx过热保护i56 f 78VFBPGNDVLPVDDnaCM8501的内部电路框图AGSENVIN/2 SDiNCNCNC VCCAAGND87654321c h振荡器.锯齿波发生器w100KwSQ- 比较器wRQ误差放大器++-100K20PF过热保护9 10 1112131415 16NC VCCQ VFB NC PGND VL PVDD NCCM8501的针脚封装图 CM8501A 的针脚封装图1VCCANC 16 1VCCAPVDD 8 2NCPVDD152VCCQVL 73NCVL143AGNDPGND64 NCPGND134SDVFB55 AGND NC 126 SD VFB 117 VIN/2VCCQ10 8 AGSENNC9CM8501/CM8501A 的引脚功能m引脚号o封装 16-PSOP 封装 8-PSOP引脚名称引脚功能c11VCCA供电电压输入端16、12、9、4、3、2-NC空脚53AGND 模拟电路接地端.64SD 低电平时正常工作,使能控制端7-VIN/2输入电压的 1/2 基准电压输出端x8-AGSENi基准电压接地端102VCCQ 外部基准电压驱动输出f115VFB 电压反馈输入136PGND 接地端na14 7VL 输出电压值等于基准电压,电压输出158PVDD负载供电电压iCM8501A 的典型应用电路图hVCCVDDC1 100uf/6.3V1 12R2 R4C82c11k 1k10uf/6.3V.J1JP1R12 2JUMPER100kTP1 PWR/IND11 C3 U24C2 105470CM-431BNCSK121331w wL13.3uH16151413 1211109D2 N CP V D DV LP G N D N C V F BV C C Q N CwSK12JP32 C7 C611 A G S E N2104220uf/6.3VV C C AC A G N DV I N /23N CN CS DJ2U1VTTCM8501 123456781VCC12R6C4105J3C9VREF-OUT5R1VDD1022C5104 21JP2JUMPERR3JP4100k2 1ON/OFF SWR5CM8501的典型应用电路图VCCVDDC1 100uf/6.3V112R2 R4 C8211k1k 10uf/6.3VJP1 R122J1JUMPER100kTP1 PWR/IND11 C3 U24 C2 105470CM-431BNCSK121331L13.3uH1514131211109D2 N CP V D DV LP G N DN CV F BV C C QN CSK12JP32 C7 C611 A G S E N2104220uf/6.3V A G N DV I N /23N CN C N CS DJ2U1mVTTCM850178234561VCC12 C4 105R6J3 C9oVREF-OUT5R1VDDC510221042 1JP2R3JUMPERcJP4 100k21ON/OFF SWR5.xifnaic hw.ww。

芯片封装介绍

一、什么叫封装封装,就是指把硅片上的电路管脚,用导线接引到外部接头处,以便与其它器件连接.封装形式是指安装半导体集成电路芯片用的外壳。

它不仅起着安装、固定、密封、保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件相连接,从而实现内部芯片与外部电路的连接。

因为芯片必须与外界隔离,以防止空气中的杂质对芯片电路的腐蚀而造成电气性能下降。

另一方面,封装后的芯片也更便于安装和运输。

由于封装技术的好坏还直接影响到芯片自身性能的发挥和与之连接的PCB(印制电路板)的设计和制造,因此它是至关重要的。

衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。

封装时主要考虑的因素:1、芯片面积与封装面积之比为提高封装效率,尽量接近1:1;2、引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性能;3、基于散热的要求,封装越薄越好。

封装主要分为DIP双列直插和SMD贴片封装两种。

从结构方面,封装经历了最早期的晶体管TO(如TO-89、TO92)封装发展到了双列直插封装,随后由PHILIP 公司开发出了SOP小外型封装,以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP (薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

从材料介质方面,包括金属、陶瓷、塑料、塑料,目前很多高强度工作条件需求的电路如军工和宇航级别仍有大量的金属封装。

封装大致经过了如下发展进程:结构方面:TO->DIP->PLCC->QFP->BGA ->CSP;材料方面:金属、陶瓷->陶瓷、塑料->塑料;引脚形状:长引线直插->短引线或无引线贴装->球状凸点;装配方式:通孔插装->表面组装->直接安装二、具体的封装形式1、 SOP/SOIC封装SOP是英文Small Outline Package 的缩写,即小外形封装。

CSP

CSP封装产品工艺流程 1 、柔性基片CSP产品的封装工艺流程

2、硬质基片CSP产品的封装工艺流程

3 、引线框架CSP产品的封装工艺流程

4、 圆片级CSP产品的封装工艺流程

5 、叠层CSP产品的封装工艺流程

开发CSP封装产品技术问题 1、CSP产品的标准化问题

2、CSP产品的封装技术问题

目录

CSP封装概况封装形式

CSP封装产品特点①体积小。

②输入/输出端数可以很多。

③电性能好。

④热性能好。

⑤CSP不仅体积小,而且重量轻。

⑥CSP电路

⑦CSP产品

CSP封装分类1、柔性基片CSP

2、硬质基片CSP

3、引线框架CSP

4、圆片级CSP

5、叠层CSP

CSP封装产品工艺流程1 、柔性基片CSP产品的封装工艺流程

CSP内部的芯片与封装外壳布线间的互连线的长度比QFP或BGA短得多,因而寄生参数小,信号传输延迟时间短,有利于改善电路的高频性能。

④热性能好。

CSP很薄,芯片产生的热可以很短的通道传到外界。通过空气对流或安装散热器的办法可以对芯片Байду номын сангаас行有效的散热。

⑤CSP不仅体积小,而且重量轻。

它的重量是相同引线数的QFP的五分之一以下,比BGA的少得更多。这对于航空、航天,以及对重量有严格要求的产品应是极为有利的

引线框架CSP产品的封装工艺与传统的塑封工艺完全相同,只是使用的引线框架要小一些,也要薄一些。因此,对操作就有一些特别的要求,以免造成框架变形。引线框架CSP产品的封装工艺流程如下: 圆片→减薄、划片→芯片键合→引线键合→模塑包封→电镀→切筛、引线成型→测试→筛选→激光打标

芯片封装类型图解

集成电路封装形式介绍(图解)BGA BGFP132 CLCCCPGA DIP EBGA 680LFBGA FDIP FQFP 100LJLCC BGA160L LCCLDCC LGA LQFPLQFP100L Metal Qual100L PBGA217LPCDIP PLCC PPGAPQFP QFP SBA 192LTQFP100L TSBGA217L TSOPCSPSIP:单列直插式封装.该类型的引脚在芯片单侧排列,引脚节距等特征和DIP基本相同.ZIP:Z型引脚直插式封装.该类型的引脚也在芯片单侧排列,只是引脚比SIP粗短些,节距等特征也和DIP基本相同.S-DIP:收缩双列直插式封装.该类型的引脚在芯片两侧排列,引脚节距为1.778mm,芯片集成度高于DIP.SK-DIP:窄型双列直插式封装.除了芯片的宽度是DIP的1/2以外,其它特征和DIP相同.PGA:针栅阵列插入式封装.封装底面垂直阵列布置引脚插脚,如同针栅.插脚节距为2.54mm或1.27mm,插脚数可多达数百脚.用于高速的且大规模和超大规模集成电路.SOP:小外型封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,字母L状.引脚节距为1.27mm.MSP:微方型封装.表面贴装型封装的一种,又叫QFI等,引脚端子从封装的四个侧面引出,呈I字形向下方延伸,没有向外突出的部分,实装占用面积小,引脚节距为1.27mm.QFP:四方扁平封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈L字形,引脚节距为1.0mm,0.8mm,0.65mm,0.5mm,0.4mm,0.3mm,引脚可达300脚以上.SVP:表面安装型垂直封装.表面贴装型封装的一种,引脚端子从封装的一个侧面引出,引脚在中间部位弯成直角,弯曲引脚的端部和PCB键合,为垂直安装的封装.实装占有面积很小.引脚节距为0.65mm,0.5mm.LCCC:无引线陶瓷封装载体.在陶瓷基板的四个侧面都设有电极焊盘而无引脚的表面贴装型封装.用于高速,高频集成电路封装.PLCC:无引线塑料封装载体.一种塑料封装的LCC.也用于高速,高频集成电路封装.SOJ:小外形J引脚封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈J字形,引脚节距为1.27mm.BGA:球栅阵列封装.表面贴装型封装的一种,在PCB的背面布置二维阵列的球形端子,而不采用针脚引脚.焊球的节距通常为1.5mm,1.0mm,0.8mm,和PGA相比,不会出现针脚变形问题.CSP:芯片级封装.一种超小型表面贴装型封装,其引脚也是球形端子,节距为0.8mm,0.65mm,0.5mm等.TCP:带载封装.在形成布线的绝缘带上搭载裸芯片,并和布线相连接的封装.和其他表面贴装型封装相比,芯片更薄,引脚节距更小,达0.25mm,而引脚数可达500针以上.介绍:1 基本元件类型Basic Component Type盒形片状元件(电阻和电容)Box Type Solder ComponentResistor and Capacitor小型晶体管三极管及二极管SOTSmall Outline TransistorTransistor and Diodeelf类元件Melf type Component [Cylinder]Sop元件Small outline package小外形封装TSop元件Thin Sop薄形封装SOJ元件Small Outline J-lead Package 具有丁形引线的小外形封装QFP元件Quad Flat Package方形扁平封装PLCC元件Plastic Leaded Chip Carrier 塑料有引线芯片载体BGABall Grid Array 球脚陈列封装球栅陈列封装CSPChip Size Package芯片尺寸封装2特殊元件类型Special Component Type钽电容( Tantalium Capacitor)铝电解电容(Aalminum Electrolytic Capacitor )可变电阻( Variable Resistor )针栅陈列封装BGABin Grid Array连接器ConnectorIC卡连接器IC Card Connector附BGA 封装的种类APBGAPlastic BGA塑料BGABCBGACeramic BGA陶瓷BGACCCGACeramic Column Grid Array陶瓷柱栅陈列DTBGATape Automated BGA载带自动键合BGAEMBGA微小BGA注芯片的封装技术已经历了好几代的变迁从DIPQFPPGABGA到CSP再到MCM技术指标一代比一代先进包括芯片面积和封装面积之比越来越接近于1适用频率越来越高耐温性能越来越好引脚数增多引脚间距减少重量减少可靠性提高使用更加方便等(MCMMulti Chip Model 多芯片组件)英汉缩语对照SMTSurface Mount Technology 表面贴装技术SMDSurface Mounting Devices 表面安装器件SMBSurface Mounting Printed Circuit Board 表面安装印刷板DIP Dual-In-Line Package 双列直插式组件THTThough Hole Mounting Technology插装技术PCB Printed Circuit Board 印刷电路板SMC Surface Mounting Components表面安装零件PQFP Plastic Quad Flat Package 塑料方形扁平封装SOIC Small Scale Integrated Circuit小外形集成电路LSI Large Scale Integration 大规模集成注意芯片封装图鉴封装大致经过了如下发展进程:结构方面:DIP封装(70年代)->SMT工艺(80年代 LCCC/PLCC/SOP/QFP)->BGA封装(90年代)->面向未来的工艺(CSP/MCM)材料方面:金属、陶瓷->陶瓷、塑料->塑料;引脚形状:长引线直插->短引线或无引线贴装->球状凸点;装配方式:通孔插装->表面组装->直接安装一.TO 晶体管外形封装TO(Transistor Out-line)的中文意思是“晶体管外形”。

3D DRAM封装技术的应用

3D DRAM封装技术的应用作者:Biao Cai、Vipinchandra Patel、Edmund D. Blackshear,IBM服务器系统的需求推动了3D DRAM技术的进展。

新一代技术提供了形状因子(即几何尺寸和形状)、电气和功率性能方面的优势。

同时也带来了更为复杂的设计、新的装配技术和失效机理。

最佳的3D DRAM技术是由这种优势、成本、入市时间和可靠性的综合权衡决定的。

本文详尽分析了用于DDR2、DDR3和未来服务器存储系统的最佳3D DRAM技术的特征。

TSV(硅通孔)DRAM阵列堆叠有望带来超级的功率性能,这可能是意义重大的市场推动力。

文中还论述了对这一未来技术的权衡和工艺发展趋势。

服务器系统的需求推动3D DRAM技术服务器系统存储量至少每代增长2X。

系统空间体积配置限制了存储器插座/模块的总数,因此要求增长存储器模块密度。

近几年来,“下一代芯片缩小”减缓和成本交叉点在模块密度增长要求和DRAM芯片密度增长之间产生了差距,并且正在扩大(图1),为3D DRAM技术创造了应用空间。

DDR2 3D封装技术DDR2存储器原来是用BGA单片封装。

有互为竞争的二种DDR2 3D技术:BGA堆叠(叠层封装)和引线键合芯片堆叠。

二者均是2005年左右在IBM服务器平台中引入的。

BGA堆叠(叠层封装)在IBM服务器平台中采用了几种BGA堆叠设计(图2)。

这些设计有一个共同点,即封装独立的DRAM芯片。

没有芯片级老化功能时,单一封装可实现堆叠工艺前的老化,这对维持堆叠封装良率非常重要。

当新一代DRAM芯片良率仍处于上升阶段时,缺乏KGD(已知好芯片)对堆叠封装良率来说是一个问题。

BGA堆叠提供了这一问题的解决途径。

到200 4年,一些封装分包公司已开发了BGA堆叠技术。

采用第三方BGA堆叠服务,存储器供应商获得了“入市时间”的优势。

良率和入市时间的优势是BGA堆叠技术的首要市场推动因素。

Low Profile是市场的重要推动因素对于高密度DDR2存储模块,常要热/冷却增强措施(图3)。

芯片常见的封装方式

芯片常见的封装方式芯片是现代电子技术的基石,它们被广泛应用于各种设备中。

然而,芯片制造并不是一件容易的事情,需要经过多个步骤,其中一个重要的步骤就是芯片封装。

芯片封装是将芯片包裹在一个外壳中,以保护芯片并方便使用。

本文将介绍芯片常见的封装方式。

一、DIP封装DIP封装是最早的芯片封装方式之一,DIP全称为Dual In-line Package,即双列直插封装。

DIP封装最大的特点是封装简单、易于制造,但它的封装密度低,只能封装少量的芯片引脚。

DIP 封装通常用于一些低端的芯片或模拟电路。

二、SOP封装SOP封装是Small Outline Package的缩写,即小外形封装。

SOP封装是DIP封装的升级版,它的封装密度比DIP更高,可以封装更多的芯片引脚。

SOP封装通常用于一些中端的芯片,如微控制器、存储器等。

三、QFP封装QFP封装是Quad Flat Package的缩写,即四面扁平封装。

QFP 封装的引脚排列呈矩形,四面扁平,与芯片本身平行。

QFP封装的引脚密度很高,可以封装数百个引脚,因此QFP封装通常用于高端的芯片,如DSP、FPGA等。

四、BGA封装BGA封装是Ball Grid Array的缩写,即球栅阵列封装。

BGA封装是一种新型的芯片封装方式,它的引脚不再是直插式,而是通过一些小球连接到芯片的表面。

BGA封装的引脚密度非常高,可以封装数千个引脚。

BGA封装的优点是封装密度高、信号传输速度快、散热效果好,因此BGA封装通常用于高性能的芯片,如CPU、GPU 等。

五、CSP封装CSP封装是Chip Scale Package的缩写,即芯片尺寸封装。

CSP封装是一种非常小型化的芯片封装方式,它的封装尺寸与芯片本身相当,因此可以将芯片封装得非常小。

CSP封装的优点是封装尺寸小、引脚密度高、信号传输速度快,因此CSP封装通常用于移动设备、智能卡等小型化的设备。

综上所述,芯片封装是芯片制造过程中非常重要的一环,不同的封装方式适用于不同的芯片。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

内存芯片封装

内存颗粒的封装方式最常见的有SOJ、TSOP II、Tiny-BGA、BLP、uBGA等封

装,而未来趋势则将向CSP发展。

SOJ封装方式是指内存芯片的两边有一排小的J形引脚,直接黏着在印刷电路

板的表面上。

它是一种

表面装配的打孔封装技术,针脚的形状就像字母"J",山此而得名。

SOJ封装一般应用在EDO DRAMo

TinyBGA英文全称为Tiny Ball Grid Array (小型球栅阵列封装),属于是

BGA封装技术的一个分支。

是Kingmax公司于1998年8月开发成功的,其芯片面

积与封装面积之比不小于1:1. 14,可以使内存在体积不变的悄况下内存容量提高2

〜3倍,与TS0P封装产品相比,其具有更小的体积、更好的散热性能和电

性能。

采用TinyBGA封装技术的内存产品在相同容量1W况下体积只有TS0P封装的1/3。

TS0P封装内存的引脚是山芯片四周引出的,而TinyBGA则是山芯片中心方向引出。

这种方式有效地缩短了信号的传导距离,

信号传输线的长度仅是传统的TS0P技术的1/4,因此信号的衰减也随之减少。

这样不仅大幅提升了芯片的

抗干扰、抗噪性能,而且提高了电性能。

采用TinyBGA封装芯片可抗高达

300MHz的外频,而采用传统TSOP封装技术最高只可抗150MHz的外频。

TinyBGA封

装的内存其疗度也更薄(封装高度小于0.8mm),从金属基板到散热体的有效散热

路径仅有0・36mm。

因此,TinyBGA内存拥有更高的热传导效率,非常适用于长时间运行的系统,稳定性极佳。

樵风(ALUKA)金条的内存颗粒采用特殊的BLP封装方式,该封装技术在传统封装技术的基础上采用一

种逆向电路,山底部直接伸出引脚,其优点就是能节省约90%电路,使封装尺寸电阻及芯片表面温度大幅

下降。

和传统的TSOP封装的内存颗粒相比,其芯片面积与填充装面积之比大

于1: 1.1,明显要小很多,不仅高度和面积极小,而且电气特性得到了进一步的

提高,制造成本也不高,BLP封装与KINGMAX的TINY-BGA封装比较相似,BLP的封装技术使得电阻值大幅下降,芯片温度也大幅下降,可稳定工作的频率更高。

*古屯-的72线SlUHrtff 条

SIMM 模块包括了一个或多个RAM 芯片,这些芯片在一块小的集成电路板上,利 用电路板上的引脚与计

算机的主板相连接。

因为用户需要对内存进行扩展,只需要加入一些新的SIMM 就可以了。

SIMM 根据内存颗粒分布可以分为单面内存和双面内存,一般的容量为 1、4、16MB 的SIMM 内存都是单面的,更大的容量

的SIMM 内存是双面的。

30线SIMM 内存条出现较早,根据当时的技术需要,只 支持8位的数据传输,如要支持32位就必须要有四条30线SIMM 内存条。

这种内 存条多用在386或早期的486主板上。

72线SIMM 内存条可支持32位的数据传 输,在586主板基本上都提供的是72线SIMM 内存插槽。

需要注意的是,Pentium 处理器的数据传输是64位的,现在采用Intel 的Triton 或Triton ?芯片组的586 主板需要成对的使用这种内存条:而采用SIS 芯片组的586主板山于SIS 芯片采用 了一些特殊的技术,能够使用单条的72线内存条。

■ KINCMJUC : KINCMAX 巳 KINfrMAX ; KlllOMaX

'*>L ¥ cr*U

rill I. V biX

I f

占 / 「 冷 •# •事

I KIHCMAK 加 KIHCMAH 二 KIMCMAX R KU

f m 圣

• •曲 __ •豪

«1^ ■ * - ・'・'""■■ "一^cL**"* • rr

L.: ■・丨-■ i 一

代••… 二^^・一 ・

多

回

冗!

二

DIMM模块是U前最常见的内存模块,它是也可以说是两个SIMM。

它是包括有

一个或多个RAM芯片在一个小的集成电路板上,利用这块电路板上的一些引脚可以直接和il•算机主板相连接。

一个DIMM有168引脚,这种内存条支持64位的数据传

输。

DIMM 是U 前我们使用的内存的主要封装形式,比如SDRAM 、DDR SDRAM 、 RDRAM,其中SDRAM 具有168线引脚并且提供了 64bit 数据寻址能力。

DIMM 的工作 电压一般是3. 3v 或者5v,

并且分为unbuffered 和buffered 两种。

而SIMM 和DIMM 内存之间不仅仅是引 脚数U 的不同,另外在电气

特性、封装特点上都有明显的差别,特别是它们的芯片之间的差别相当的大。

因为按照原来内存制造方法,

制造这种内存的时候是不需要把64个芯片组装在一起构成一个64bit 的模块 的,得益于今年来生产工艺的

提高和改进,现在的高密度DRAM 芯片可以具有不止一个Din 和Dout 信号引 脚,并且可以根据不同的需要

在DRAM 芯片上制造4、8、16、32或者64条数据引脚。

在Pentium 级以上的 处理器是64位总线,使用这样的内存更能发挥处理器的性能。

■ 忌 眾 M 二Trrr 二

U TSOP 内存封装技术的一个典型特征就是在封装芯片的周B 做出引脚,如SDRAM 内存的集成电路两侧都有引脚,SGRAM 内存的集成电路四面都有引脚。

TSOP 适合用 SMT 技术(表面安装技术)在PCB (印制电路板)上安装布线。

TSOP 封装外形尺寸 k I 11 U X T?' 第 Jtz 打 KI

<

时,寄生参数(电流大幅度变化时,引起输出电压扰动)减小,适合高频应用,操作比较方便,可靠性也比较高。

改进的TSOP技术口前广泛应用于SDRAM内存的制

造上,不少知名内存制造商如三星、现代、Kingston等U前都在釆用这项技术进

行内存封装。

不过,TSOP封装方式中,内存芯片是通过芯片引脚焊接在PCB板上的,焊点和PCB板的接触面积较小,使得芯片向PCB办传热就相对困难。

而且

TSOP封装方式的内存在超过150MHz后,会产品较大的信号干扰和电磁干

扰。

SD

CSP作为新一代的芯片封装技术,在BGA、TSOP的基础上,它的性能乂有了革

命性的提升。

CSP,全称为Chip Scale Pack-age,即芯片尺寸封装的意思。

作为新一代的芯

片封装技术,在BGA、TSOP的基础上,CSP的性能乂有了革命性的提升。

CSP封装

可以让芯片面积与封装面积之比超过1?1. 14,

已经相当接近1?1的理想1W况,绝对尺寸也仅有32平方毫米,约为普通的BGA 的1/3,仅仅相当于TSOP内存芯片面积的1/6。

与BGA封装相比,同等空间下CSP

封装可以将存储容量提高3倍。

CSP封装内存不但体积小,同时也更薄,其金属基板到散热体的最有效散热路径仅有0. 2毫米,大大提高了内存芯片在长时

间运行后的可第J性。

与BGA、TOSP相比CSP封装的电气性能和可靠性也有相当大的提高。

并且,在相同的

芯片面积下CSP所能达到的引脚数明显要比TSOP、BGA引脚数多得多,这样它可支持I/O端口的数U就增

加了很多。

此外,CSP封装内存芯片的中心引脚形式有效缩短了信号的传导距离,其衰减随之减少,芯片

的抗干扰、抗噪性能也能得到大幅提升,这也使得CSP的存取时间比BGA改善

15% 〜20%。