卷积码实验报告

无线通信技术实验一卷积码

实验二:卷积码一、实验仪器:PC两台、USRP两台二、实验目的:1、了解grc仿真中的信号处理模块、流程图以及使用方法2、了解卷积码的基本原理3、了解GunRadio实现信道编码的方法4、了解不同SNR对于误码率的影响5、了解卷积码对误码率的影响6、了解不同的卷积码对于误码率的影响三、实验要求:1.了解Grc的基本操作方法,要求仿真的流程中信道编码部分使用卷积编码2.通过单机实验和GnuRadio+USRP的实验两种实验方式进行仿真3.搭建有信道编码与无信道编码的Grc仿真模型4.比较上述两种情况下的误码率,并且分析结果5.比较不同的卷积码对于误码率的影响,并且分析结果。

四、实验原理:卷积码将k个信息比特编码成n个比特,但k和n通常很小,特别适合以串行形式进行传输,时延小。

与分组码不同,卷积码编码后的n个码元不仅与当前段的k个信息有关,还与前面的N-1段信息有关,编码过程中互相关联的码元个数为nN。

卷积码的纠错性能随N的增加而增大,而差错率随N的增加而指数下降。

卷积码的纠错能力不仅与约束长度有关,还与采用的译码方式有关。

GRC提供译码方式是维特比译码,它是卷积码译码方式中非常经典的以及广泛使用的一种译码方式。

该实验可以考察编码前后数据有什么变化,译码后能不能恢复原来数据,通过Number Sink考察加噪声后误比特率怎么样,对性能有什么提高,并且划出BER图形。

下面为卷积码的一般流程:五、实验步骤及分析:1、单机实验:单机实验分成(2,1,3)码、无信道编码、(2,1,8)码三个部分进行。

(一)实验流程图:首先,我们利用(2,1,3)卷积码进行信道编码,用DPSK进行调制,来进行单机实验,最终设计的流程图和参数如下图所示:先是Vector Source,即信源,设置的数据是1,0,0,1,1。

然后是Throttle限流模块。

接下来是Packed to Unpacked模块,将pack成byte或short型的数据以unpacked型的数据输出。

卷积实验报告

新乡学院实验报告实验内容及步骤1、按1.3节用设置“信号A组”的输出为指数衰减信号(模式二,信号A组的信号输出指示灯为000000),并经放大器缓冲输出;1、按1.3节用按键2使使对应的“信号B组”产生270Hz信号(模式二,信号B组的信号输出指示灯为000101),并经放大器缓冲输出。

2、卷积输出:用短路线将A缓冲信号连接到乘法器的一端S,将信号源1KHz接到乘法器1的输入端X,示波器同时观察这两个信号(会观察到这两个信号在发生相对移动);并将乘法器1的输出端接低通滤波器(300~3400Hz)输入端,最后并观察滤波器的输出y。

3、验证卷积器的交换率:)(*)()(*)(1221tftftftf=。

在上例中,交换乘法器的两个输入,观察滤波器的输出y,并与上一步进行比较。

4、验证卷积器的分配率:)(*)()(*)()]()([*)(3121321tftftftftftftf+=+(1)用短路线将信号A、B组两信号通过加法器相加,并将加法器的输出与乘法器1的S端相连将,将标准信号源1KHz信号连接到乘法器1的输入端X;并将乘法器1的输出端接低通滤波器(300~3400Hz)输入端,最后并观察滤波器的输出y。

(2)用短路线将信号A、B组两信号分别与乘法器1、2的S端相连,将标准信号源1KHz信号分别连接到乘法器1、2的输入端X,同时将两乘法器的结果经加法器相加,观察加法器的输出。

(3)比较上两步测量结果。

注意事项1.要注意示波器的表笔要接地。

2.函数信号发生器为模式2。

3.正确连接实验电路。

实验数据︵现象︶记录及结果处理(不够可附页)。

【报告】卷积码实验报告

【报告】卷积码实验报告一、实验目的本次卷积码实验的主要目的是深入理解卷积码的编码与译码原理,掌握其在数字通信系统中的应用,并通过实际实验操作和结果分析,评估卷积码的纠错性能和对通信质量的改善效果。

二、实验原理(一)卷积码的基本概念卷积码是一种有记忆的非分组码,它将输入的信息序列经过特定的编码器生成输出的码序列。

卷积码的编码过程不仅取决于当前输入的信息位,还与之前的若干个信息位有关。

(二)编码原理卷积码的编码器通常由若干个移位寄存器和模 2 加法器组成。

输入的信息位在时钟的控制下依次进入移位寄存器,同时与寄存器中的内容进行模 2 加法运算,生成输出的编码位。

(三)译码原理卷积码的译码方法有多种,常见的有维特比译码算法。

维特比译码算法基于最大似然准则,通过在码的网格图上寻找最有可能的路径来实现译码。

三、实验环境与设备本次实验在计算机上进行,使用了以下软件和工具:1、 MATLAB 编程环境,用于实现卷积码的编码、传输和译码过程,并进行性能分析。

2、通信系统仿真工具,用于构建通信系统模型,模拟信号的传输和接收。

四、实验步骤(一)编码实现1、在 MATLAB 中定义卷积码的编码器结构,包括移位寄存器的数量和连接方式,以及模 2 加法器的位置。

2、编写编码函数,输入信息序列,按照编码器的工作原理生成编码后的序列。

(二)信道传输1、模拟加性高斯白噪声信道,设置不同的信噪比条件。

2、将编码后的序列通过信道传输,引入噪声干扰。

(三)译码实现1、使用维特比译码算法对接收序列进行译码。

2、编写译码函数,输入接收序列和信道参数,输出译码后的信息序列。

(四)性能评估1、计算误码率,即错误译码的比特数与总传输比特数的比值。

2、绘制误码率曲线,分析卷积码在不同信噪比条件下的纠错性能。

五、实验结果与分析(一)不同卷积码参数对性能的影响1、改变卷积码的约束长度,观察其对纠错性能的影响。

结果表明,约束长度越长,卷积码的纠错能力越强,但编码效率会有所降低。

缩短卷积码MATLAB仿真实训实习报告

缩短卷积码MATLAB仿真实训实习报告缩短卷积码MATLAB仿真实训实习报告(一)摘要现代通信系统的信道编码中几乎毫无例外的采用了先进的编码方式:卷积编码,如:码分多址通信系统CDMA,数字蜂窝通信系统GSM,数字集群通信系统TETRA等等,在差错控制中,卷积码表现出了优秀的纠错能力。

但是优秀的纠错能力是以降低频道利用率为代价。

在功能完备的通信系统中有许多使命不同的逻辑信道.不同的逻辑信道因为任务不同,对应的差错控制能力与频道利用率的要求是不一样的,有两种实现的方法:构建不同的卷积码或者应用同一个卷积码但是运用不同的缩短方案以适应不同的传输数码率,自然也有着相应的纠错能力和频带利用率。

在先进的数字集群系统中就是用的第二种方案,实践证明,删除型缩短卷积码的性能与最好的卷积码可以做到相当接近。

关键词:信道编码、缩短卷积码、纠错能力(二)缩短卷积码基本原理本实训目的是要构建一个具有卷积、解卷积和打孔、插零功能以及相应的传输环境的仿真系统来对各类卷积码进行缩短卷积码的仿真研究,得到相同频带利用率下不同打孔图形的差错控制能力定量结果。

用相同的生成多项式构建的维特比译码器和不同的压缩图形卷积码都可以在原打孔图形位置上嵌入填充的码元后进行译码。

仿真采用具有缩短卷积码和调制功能的仿真系统,用BernoulliRandomBinary产生每帧2码元的随机二进制码,进入卷积编码器后变成每帧6码元的二进制码流,再经过Puncture(打孔)模块后,变为删去选择码元后剩下的码元数,在调制和解调过程中,数据帧的大小不变,通过InsertZero(插零)模块在原来删去码元的位置插入码元0,解卷积,恢复每帧2码元。

Puncture模块中的打孔矢量应与输入信号具有相同的帧长度,而且要与InsertZero模块中的插零矢量相同,矢量(vector)中的0就是打掉马远的位置,也是在解卷积之前插入0的位置,1是保留码元的位置,而矢量的长度与0的数目以及卷积码的结构共同决定了编码效率。

通信原理实验19卷积码的编解码实验

通信原理实验19卷积码的编解码实验实验十九卷积码的编解码实验实验内容1. 熟悉卷积码编码实验2.熟悉卷积码译码实验一、实验目的1.了解卷积码的基本概念和原理2.加深对卷积码的编解码过程的理解3. 学习通过CPLD编程实现卷积码编译码实验二、实验电路工作原理卷积码又称连环码,是1955年提出来的一种纠错码,它和分组码有明显的区别,但在编码器复杂度相同的情况下, 卷积码的性能优于分组码,因此卷积码几乎被应用在所有无线通信的标准之中, 如GSM, IS95和CDMA 2000 的标准中。

1.卷积码编码方法:卷积码通常记作( n0 , k0 , m) ,它将k0 个信息比特编为n0 个比特, 其编码效率为k0/ n0 , m为约束长度。

( n0 , k0 , m )卷积码可用k0 个输入、n0 个输出、输入存储为m的线性有限状态移位寄存器及模2 加法计数器来实现。

实验中所选(2 ,1 ,6) 卷积编码器上图所示,其子生成元为: g(1 ,1) ( D) = 1 , g(1 ,2) ( D) = 1 + D2 + D5 +D6 , 生成矩阵G( D) = (1 ,1 + D2 + D5 + D6) 。

设输入信息序列M = (1111) ,即M( D) = 1 + D + D2 + D3 ,则编码器的输出C( D) =M( D) ·G( D) ,即:C( D) = (1+D+D2+D3)·(1,1+D2+D5+D6)=(1+D+D2+D3 ,1+D+D2+D3+D2+D3+D4+D5+D5+D6+D7+D8 +D6+D7+D8+D9)= (1+D+D2+D3 ,1+D+D4+D9)=(11)+(11)D+(10)D2+(10)D3+(01)D4+(00)D5+(00)D6+(00)D7+(0 0)D8+(01)D9+?因此,编码器输出序列为11111010010000000001。

2.卷积码编码算法process(clk,clr)beginif(clr='1')thenif(clk'event and clk='1')thentemp(0)<=datain;temp(1)<=temp(0);temp(2)<=temp(1);temp(3)<=temp(2);temp(4)<=temp(3);end if;else temp<="00000";end if;end process;y2j<= (datain xor temp(2) xor temp(3) xor temp(4));y1j<=datain;3.大数逻辑解码器大数逻辑解码器是卷积码代数解码最主要的解码方法, 既可用于纠随机错误, 又可用于纠突发错误,但要求卷积码是自正交码或可正交码。

卷积码实验报告

卷积码实验报告篇一:卷积码实验报告实验五信道编解码()本章目标掌握数字频带传输系统调制解调的仿真过程掌握数字频带传输系统误码率仿真分析方法 5.1实验目的1. 使用MATLAB进行卷积码编/译码器的仿真。

2. 熟练掌握MATLAB软件、语句。

3. 了解卷积码编/译码器的原理、知识。

5.2实验要求1. 编写源程序、准备测试数据。

2. 在 MATLAB环境下完成程序的编辑、编译、运行,获得程序结果。

如果结果有误,应找出原因,并设法更正之。

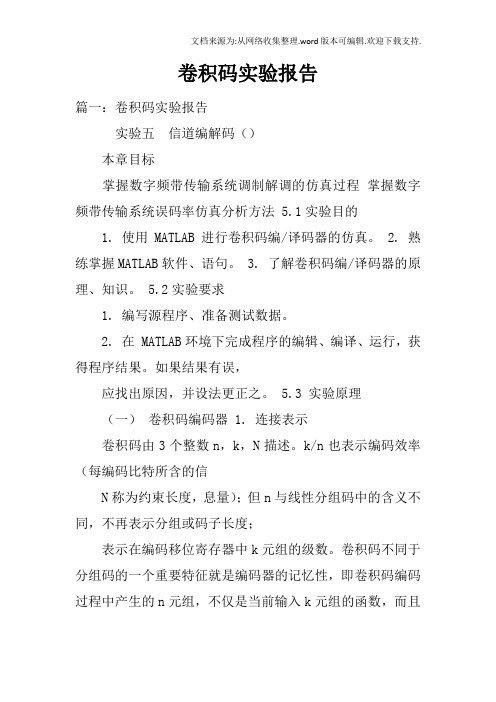

5.3 实验原理(一)卷积码编码器 1. 连接表示卷积码由3个整数n,k,N描述。

k/n也表示编码效率(每编码比特所含的信N称为约束长度,息量);但n与线性分组码中的含义不同,不再表示分组或码子长度;表示在编码移位寄存器中k元组的级数。

卷积码不同于分组码的一个重要特征就是编码器的记忆性,即卷积码编码过程中产生的n元组,不仅是当前输入k元组的函数,而且还是前面N?1个输入k元组的函数。

实际情况下,n和k经常取较小的值,而通过N的变化来控制编码的能力和复杂性。

下面以图1中的卷积码编码器为例介绍卷积码编码器。

该图表示一个约束长度K?3的(2,1)卷积译码器,模2加法器的数目为n?2,因此,编码效率k/n?1/2。

在每个输入比特时间上,1位信息比特移入寄存器最左端的一级,同时将寄存器中原有比特均右移一级,接着便交替采样两个模2加法器,得到的码元就是与该输入比特相对应的分支字。

对每一个输入信号比特都重复上述采样过程。

图1卷积码编码器(编码效率1/2,K?3)用于描述反馈移位寄存器实现循环码时所使用的生成多项式也可用户描述卷积码编码器的连接。

应用n个生成多项式描述编码的移位寄存器与模2加法器的连接方式,n个生成多项式分别对应n个模2加法器,每个生成多项式不超过K?1阶。

仍以图1中的编码器为例,用生成多项式g1(X)代表上方连接,g2(X)代表下方连接,则有:g1(X)?1?X?X2g2(X)?1?X2多项式中的最低阶项对应于寄存器的输入级。

卷积算法实验报告程序

一、实验目的通过本次实验,加深对卷积算法的理解,掌握离散时间系统中的卷积运算方法,并学会使用MATLAB进行卷积运算的仿真。

二、实验原理卷积是一种线性时不变(LTI)系统的数学运算,用于描述系统输入信号与系统冲激响应的卷积结果。

在离散时间系统中,卷积运算可以表示为:\[ y[n] = \sum_{k=-\infty}^{\infty} x[k]h[n-k] \]其中,\( y[n] \) 是系统的输出信号,\( x[k] \) 是系统的输入信号,\( h[n] \) 是系统的冲激响应,\( n \) 是时间变量。

MATLAB提供了`conv`函数来进行卷积运算,其语法为:\[ y = conv(x, h) \]其中,\( x \) 和 \( h \) 分别是输入信号和冲激响应的向量。

三、实验内容1. 创建输入信号和冲激响应使用MATLAB创建一个简单的输入信号 \( x[n] \) 和一个冲激响应 \( h[n] \)。

```matlab% 创建输入信号 x[n] = cos(2pi0.5n)n = 0:100;x = cos(2pi0.5n);% 创建冲激响应 h[n] = u[n] - u[n-10]h = [ones(1,10), zeros(1,90)];```2. 进行卷积运算使用`conv`函数进行卷积运算,并绘制输入信号、冲激响应和输出信号的图形。

```matlab% 进行卷积运算y = conv(x, h);% 绘制图形figure;subplot(3,1,1);stem(n, x);title('输入信号 x[n]');subplot(3,1,2);stem(n, h);title('冲激响应 h[n]');subplot(3,1,3);stem(n, y);title('输出信号 y[n]');```3. 分析卷积结果分析卷积结果,观察输出信号的特性,并与理论预期进行对比。

卷积码实验报告

卷积码实验报告篇一:卷积码实验报告实验五信道编解码()本章目标掌握数字频带传输系统调制解调的仿真过程掌握数字频带传输系统误码率仿真分析方法 5.1实验目的1. 使用MATLAB进行卷积码编/译码器的仿真。

2. 熟练掌握MATLAB软件、语句。

3. 了解卷积码编/译码器的原理、知识。

5.2实验要求1. 编写源程序、准备测试数据。

2. 在 MATLAB环境下完成程序的编辑、编译、运行,获得程序结果。

如果结果有误,应找出原因,并设法更正之。

5.3 实验原理(一)卷积码编码器 1. 连接表示卷积码由3个整数n,k,N描述。

k/n也表示编码效率(每编码比特所含的信N称为约束长度,息量);但n与线性分组码中的含义不同,不再表示分组或码子长度;表示在编码移位寄存器中k元组的级数。

卷积码不同于分组码的一个重要特征就是编码器的记忆性,即卷积码编码过程中产生的n元组,不仅是当前输入k元组的函数,而且还是前面N?1个输入k元组的函数。

实际情况下,n和k经常取较小的值,而通过N的变化来控制编码的能力和复杂性。

下面以图1中的卷积码编码器为例介绍卷积码编码器。

该图表示一个约束长度K?3的(2,1)卷积译码器,模2加法器的数目为n?2,因此,编码效率k/n?1/2。

在每个输入比特时间上,1位信息比特移入寄存器最左端的一级,同时将寄存器中原有比特均右移一级,接着便交替采样两个模2加法器,得到的码元就是与该输入比特相对应的分支字。

对每一个输入信号比特都重复上述采样过程。

图1卷积码编码器(编码效率1/2,K?3)用于描述反馈移位寄存器实现循环码时所使用的生成多项式也可用户描述卷积码编码器的连接。

应用n个生成多项式描述编码的移位寄存器与模2加法器的连接方式,n个生成多项式分别对应n个模2加法器,每个生成多项式不超过K?1阶。

仍以图1中的编码器为例,用生成多项式g1(X)代表上方连接,g2(X)代表下方连接,则有:g1(X)?1?X?X2g2(X)?1?X2多项式中的最低阶项对应于寄存器的输入级。

卷积编码实验报告

实验名称:___ 卷积编码_______1、使用MATLAB进行卷积编码的代码编写、运行、仿真等操作;2、熟练掌握MATLAB软件语句;3、理解并掌握卷积编码的原理知识。

二、实验原理卷积码是由Elias于1955 年提出的,是一种非分组码,通常它更适用于前向纠错法,因为其性能对于许多实际情况常优于分组码,而且设备较简单。

卷积码的结构与分组码的结构有很大的不同。

具体地说,卷积码并不是将信息序列分成不同的分组后进行编码,而是将连续的信息比特序列映射为连续的编码器输出符号。

卷积码在编码过程中,将一个码组中r 个监督码与信息码元的相关性从本码组扩展到以前若干段时刻的码组,在译码时不仅从此时刻收到的码组中提取译码信息,而且还可从与监督码相关的各码组中提取有用的译码信息。

这种映射是高度结构化的,使得卷积码的译码方法与分组译码所采用的方法完全不同。

可以验证的是在同样复杂度情况下,卷积码的编码增益要大于分组码的编码增益。

对于某个特定的应用,采用分组码还是卷积码哪一种更好则取决于这一应用的具体情况和进行比较时可用的技术。

(一)卷积编码的图形表示卷积码的编码器是由一个有k 个输人位,n 个输出位,且有m 个移位寄存器构成的有限状态的有记忆系统,其原理如图1所示。

图1 卷积码编码器的原理图描述这类时序网络的方法很多,它大致可分为两大类型:解析表示法与图形表示法。

在解析法中又可分为离散卷积法、生成矩阵法、码多项式法等;在图形表示法中也可分为状态图法、树图法和网络图法等。

图2给出的是一个生成编码速率为1/2 卷积码的移位寄存器电路。

输人比特在时钟触发下从左边移人到电路中,每输入一位,分别去两个模2加法器的输出值并复用就得到编码器的输出。

对这一编码,每输入一比特就产生两个输出符号,故编码效率为1/2。

可以看出,每个特定的输入比特不仅影响本时间间隔内的编码器输出,同时还影响紧接着的下两个输入比特时间间隔的编码器输出。

卷积编码由移位寄存器的阶数、输出的数量(即模2加法器的个数)和移位寄存器与模2 加法器间的连接所决定。

实验九 (2,1,5)卷积码编码译码技术

实验九 (2,1,5)卷积码编码译码技术一、实验目的1、掌握(2,1,5)卷积码编码译码技术2、了解纠错编码原理。

二、实验内容1、(2,1,5)卷积码编码。

2、(2,1,5)卷积码译码。

三、预备知识1、纠错编码原理。

2、(2,1,5)卷积码的工作原理。

四、实验原理卷积码是将发送的信息序列通过一个线性的,有限状态的移位寄存器而产生的编码。

通常卷积码的编码器由K级(每级K比特)的移位寄存器和n个线性代数函数发生器(这里是模2加法器)组成。

若以(n,k,m)来描述卷积码,其中k为每次输入到卷积编码器的bit数,n 为每个k元组码字对应的卷积码输出n元组码字,m为编码存储度,也就是卷积编码器的k元组的级数,称m+1= K为编码约束度m称为约束长度。

卷积码将k 元组输入码元编成n元组输出码元,但k和n通常很小,特别适合以串行形式进行传输,时延小。

与分组码不同,卷积码编码生成的n元组元不仅与当前输入的k元组有关,还与前面m-1个输入的k元组有关,编码过程中互相关联的码元个数为n*m。

卷积码的纠错性能随m的增加而增大,而差错率随N的增加而指数下降。

在编码器复杂性相同的情况下,卷积码的性能优于分组码。

编码器随着信息序列不断输入,编码器就不断从一个状态转移到另一个状态并同时输出相应的码序列,所以图3所示状态图可以简单直观的描述编码器的编码过程。

因此通过状态图很容易给出输入信息序列的编码结果,假定输入序列为110100,首先从零状态开始即图示a状态,由于输入信息为“1”,所以下一状态为b并输出“11”,继续输入信息“1”,由图知下一状态为d、输出“01”……其它输入信息依次类推,按照状态转移路径a->b->d->c->b->c->a输出其对应的编码结果“110101001011”。

译码方法⒈代数代数译码是将卷积码的一个编码约束长度的码段看作是[n0(m+1),k0(m+1)]线性分组码,每次根据(m+1)分支长接收数字,对相应的最早的那个分支上的信息数字进行估计,然后向前推进一个分支。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

苏州科技大学天平学院电子与信息工程学院信道编码课程设计报告课设名称卷积码编译及译码仿真学生姓名圣鑫学号1430119232同组人周妍智专业班级通信1422指导教师潘欣欲一、实验名称基于MAATLAB的卷积码编码及译码仿真二、实验目的卷积码就是一种性能优越的信道编码。

它的编码器与译码器都比较容易实现,同时它具有较强的纠错能力。

随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。

本实验简明地介绍了卷积码的编码原理与Viterbi译码原理。

并在SIMULINK模块设计中,完成了对卷积码的编码与译码以及误比特统计整个过程的模块仿真。

最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。

经过仿真与实测,并对测试结果作了分析。

三、实验原理1、卷积码编码原理卷积码就是一种性能优越的信道编码,它的编码器与解码器都比较易于实现,同时还具有较强的纠错能力,这使得它的使用越来越广泛。

卷积码一般表示为(n,k,K)的形式,即将 k个信息比特编码为 n 个比特的码组,K 为编码约束长度,说明编码过程中相互约束的码段个数。

卷积码编码后的 n 各码元不经与当前组的 k 个信息比特有关,还与前 K-1 个输入组的信息比特有关。

编码过程中相互关联的码元有 K*n 个。

R=k/n 就是编码效率。

编码效率与约束长度就是衡量卷积码的两个重要参数。

典型的卷积码一般选 n,k 较小,K 值可取较大(>10),但以获得简单而高性能的卷积码。

卷积码的编码描述方式有很多种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述,树图描述,网格图描述等。

2、卷积码Viterbi译码原理卷积码概率译码的基本思路就是:以接收码流为基础,逐个计算它与其她所有可能出现的、连续的网格图路径的距离,选出其中可能性最大的一条作为译码估值输出。

概率最大在大多数场合可解释为距离最小,这种最小距离译码体现的正就是最大似然的准则。

卷积码的最大似然译码与分组码的最大似然译码在原理上就是一样的,但实现方法上略有不同。

主要区别在于:分组码就是孤立地求解单个码组的相似度,而卷积码就是求码字序列之间的相似度。

基于网格图搜索的译码就是实现最大似然判决的重要方法与途径。

用格图描述时,由于路径的汇聚消除了树状图中的多余度,译码过程中只需考虑整个路径集合中那些使似然函数最大的路径。

如果在某一点上发现某条路径已不可能获得最大对数似然函数,就放弃这条路径,然后在剩下的“幸存”路径中重新选择路径。

这样一直进行到最后第 L 级(L 为发送序列的长度)。

由于这种方法较早地丢弃了那些不可能的路径,从而减轻了译码的工作量,Viterbi 译码正就是基于这种想法。

对于(n, k, K )卷积码,其网格图中共 2kL 种状态。

由网格图的前 K-1 条连续支路构成的路径互不相交,即最初 2k_1 条路径各不相同,当接收到第 K 条支路时,每条路径都有 2 条支路延伸到第 K 级上,而第 K 级上的每两条支路又都汇聚在一个节点上。

在Viterbi译码算法中,把汇聚在每个节点上的两条路径的对数似然函数累加值进行比较,然后把具有较大对数似然函数累加值的路径保存下来,而丢弃另一条路径,经挑选后第 K 级只留下2K条幸存路径。

选出的路径同它们的对数似然函数的累加值将一起被存储起来。

由于每个节点引出两条支路,因此以后各级中路径的延伸都增大一倍,但比较它们的似然函数累加值后,丢弃一半,结果留存下来的路径总数保持常数。

由此可见,上述译码过程中的基本操作就是,“加-比-选”,即每级求出对数似然函数的累加值,然后两两比较后作出选择。

有时会出现两条路径的对数似然函数累加值相等的情形,在这种情况下可以任意选择其中一条作为“幸存”路径。

卷积码的编码器从全零状态出发,最后又回到全零状态时所输出的码序列,称为结尾卷积码。

因此,当序列发送完毕后,要在网格图的终结处加上(K-1)个己知的信息作为结束信息。

在结束信息到来时,由于每一状态中只有与已知发送信息相符的那条支路被延伸,因而在每级比较后,幸存路径减少一半。

因此,在接收到(K-1)个己知信息后,在整个网格图中就只有唯一的一条幸存路径保留下来,这就就是译码所得的路径。

也就就是说,在己知接收到的序列的情况下,这条译码路径与发送序列就是最相似的。

3、MATLAB 仿真在本次实验中,主要就是利用SIMULINK仿真模块对卷积码的编码及viterbi 译码的全过程进行了设计,SIMULINK仿真框图如下:图1卷积码的SIMULINK仿真框图基本设计思路就是:先由Bernoulli Binary Generator(贝努利二进制序列产生器)产生一个0,1等概序列,经过Convolutional Encoder(卷积编码器)对输入的二进制序列进行卷积编码,并用BPSK调制方式调制信号。

加入信道噪声(高斯白噪声)后再经过BPSK解调制后送入Viterbi Decoder(Viterbi译码器)进行硬判决译码。

最后经过Error Rate Calculation(误码统计)后由Display(显示)输出。

然后通过Selector(数据选通器)将结果输出到To workspace(工作区间)。

该结果将由m文件中的程序调用以绘制不同信噪比及其她参数下系统误码率曲线。

四、实验结果1、不同的约束长度对卷积码误码率的影响对于码率一定的卷积码,当约束长度N 发生变化时,系统的误码性能也会随之发生变化, 本实验中以码率R = 1/2的(2,1,3)与(2,1,7)卷积码为例展开分析。

仿真所用所用程序如下:x=0:5;y=x;for i=1:length(x)SNR=x(i);sim('juanjima');y(i)=mean(BitErrorRate);endsemilogy(x,y,’r’);hold on;for i=1:length(x)SNR=x(i);sim('juanjima2');y(i)=mean(BitErrorRate);endsemilogy(x,y,’g’);xlabel('SNR')ylabel('BitErrorRate')仿真结果:图2约束长度对卷积码性能的影响结果分析:对于码率一定的卷积码,当约束长度N 发生变化时,系统的误码性能也会随之发生变化, 我们以码率R = 1/ 2的(2 ,1 ,3)与(2,1,7) 卷积码为例展开分析。

上面的曲线就是(2,1,3)卷积码的误码性能曲线。

下面的曲线就是(2,1,7)卷积码的误码性能曲线。

从图4-4中的误比特率曲线可以清楚地瞧到,随着约束长度的逐渐增加,系统的误比特率明显降低,所以说当码率一定时,增加约束长度可以降低系统的误比特率,但就是随着约束长度的增加,译码设备的复杂性也会随之增加,所以对于码率为1/ 2 的卷积码,我们在选取约束长度时一般为3~9 。

2、回溯长度对卷积码性能的影响以(2,1,7)卷积码为例。

将译码模块中的Traceback depth分别设置为20,35,50并在一个图中画出这三种方式下的误码性能曲线。

仿真所用程序如下:x= 0:5;y=x;for i=1:length(x)SNR=x(i);sim('juanjima');y(i)=mean(BitErrorRate);endsemilogy(x,y,’r’);hold on;for i=1:length(x)SNR=x(i);sim('juanjima2');y(i)=mean(BitErrorRate);endsemilogy(x,y,’g’);hold on;for i=1:length(x)SNR=x(i);sim('juanjima3');y(i)=mean(BitErrorRate); endsemilogy(x,y,’b’);xlabel('SNR')ylabel('BitErrorRate')仿真结果:图3 回溯长度对卷积码性能的影响从上到下的三条曲线分别就是Traceback depth为20,35,50。

可以瞧出:回溯长度在Viterbi 译码过程中一个很重要的参数,她决定了译码延迟,随着她的不断变化,误码性能也随误比特率曲线可以清楚地瞧到,当回溯长度一定时,随着信道噪声的逐渐提高,系统的误比特率逐渐降低;当回溯长度逐渐增加,系统的误比特率随之逐渐降低,当回溯程度τ增加一定程度时,误比特率数值趋于稳定。

3.不同码率对误比特率的影响以码率为1/2的(2,1,3)卷积码与码率为1/3的(3,1,3)码为例。

它们的trellis结构分别就是poly2trellis(3,[6 7])与poly2trellis(3,[1 6 5])。

仿真所用程序:x=0:5;y=x;for i=1:length(x)SNR=x(i);sim('juanjima');y(i)=mean(BitErrorRate); endsemilogy(x,y,’r’);hold on;for i=1:length(x)SNR=x(i);sim('juanjima2');y(i)=mean(BitErrorRate); endsemilogy(x,y,’b’);xlabel('SNR')ylabel('BitErrorRate'图4 码率对卷积码性能的影响结果分析:从图中可以瞧出,当码率一定时,随着信道信噪比的提高,系统误比特率逐渐降低。

当改变码率时,在信噪比一定的条件下,码率越高,误比特率越高。

5.不同信道对viterbi译码性能的影响在这个部分主要考虑的就是二进制对称信道与高斯白噪声信道对于viterbi 译码性能的影响。

采用的就是(2,1,7)卷积码。

仿真所用程序:x=0:5;y=x;for i=1:length(x)SNR=x(i);sim('juanjima');y(i)=mean(BitErrorRate); endsemilogy(x,y,’r’); semilogy(x,y,’b’);xlabel('SNR')ylabel('BitErrorRate')仿真结果:图5二进制对称信道下的仿真结果图6高斯白噪声信道下的仿真结果结果分析:高斯白噪声信道中,Viterbi译码随着信道的信噪比提升,误比特率越低,信道的可信度与纠错能力很高,而在二进制对称信道中,随着信道的误码率提升,viterbi译码的误比特率也会提升,当二进制对称信道的误码率高到一定程度时,Viterbi译码几乎会丧失纠错能力。