模可变计数器设计Verilog语言

实验六 Verilog设计分频器计数器电路答案

实验六Verilog设计分频器/计数器电路一、实验目的1、进一步掌握最基本时序电路的实现方法;2、学习分频器/计数器时序电路程序的编写方法;3、进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为4个clock周期的低电平,4个clock周期的高电平),文件命名为fenpinqi10。

v.2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为coute r10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5。

v。

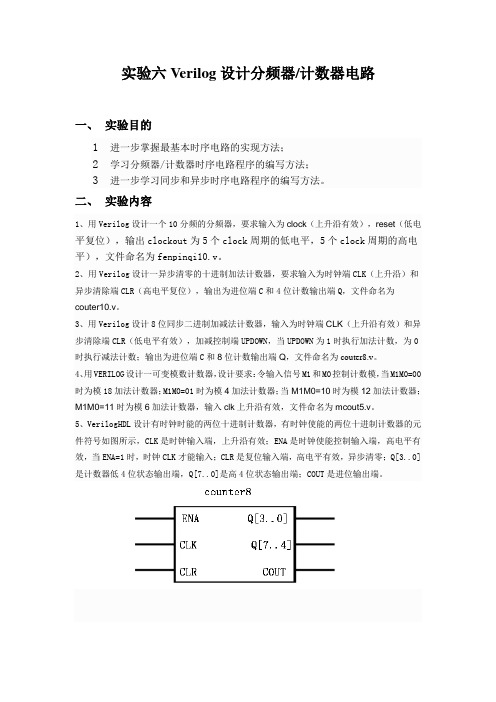

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3.。

0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端.三、实验步骤实验一:分频器1、建立工程2、创建Verilog HDL文件3、输入10分频器程序代码并保存4、进行综合编译5、新建波形文件6、导入引脚7、设置信号源并保存8、生成网表9、功能仿真10、仿真结果分析由仿真结果可以看出clockout输出5个clock周期的低电平和5个clock的高电平达到10分频的效果,设计正确。

计数器(1):Verilog常用写法

计数器(1):Verilog常⽤写法 计数器是⾮常基本的使⽤,没有计数器就⽆法处理时序。

我在学习时发现市⾯上有⼏种不同的计数器写法,⾮常有趣,在此记录下来:⼀、时序逻辑和组合逻辑彻底分开1.代码1//======================================================================2// --- 名称 : Count_13// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-105// --- 描述 : 模10计数器,0到10循环累加6//======================================================================78module Count_19 (10input clk ,11input rst_n ,12output reg [ 3:0] cnt13 );1415//----------------------------------------------------------------------16//-- 组合电路17//----------------------------------------------------------------------18reg [ 3:0] cnt_n ;1920always @(*)begin21if(cnt == 4'd9)22 cnt_n = 4'd0;23else24 cnt_n = cnt + 1'b1;25end2627//----------------------------------------------------------------------28//-- 时序电路29//----------------------------------------------------------------------30always @(posedge clk or negedge rst_n)begin31if(!rst_n)32 cnt <= 4'b0;33else34 cnt <= cnt_n;35end3637endmodule3839/*40//----------------------------------------------------------------------41//-- 组合电路也可以这样写42//----------------------------------------------------------------------43wire [ 3:0] cnt_n ;4445assign cnt_n = (cnt==4'd9)? 4'd0 : cnt+1'b1;4647*/2.写法1的RTL视图3.写法2的RTL视图⼆、最常见的写法1.代码1//======================================================================2// --- 名称 : Count_23// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-105// --- 描述 : 模10计数器,0到10循环累加6//======================================================================78module Count_29 (10input clk ,11input rst_n ,12output reg [ 3:0] cnt13 );1415always @(posedge clk or negedge rst_n)begin16if(!rst_n)17 cnt <= 4'd0;18else if(cnt==4'd9)19 cnt <= 4'd0;20else21 cnt <= cnt + 1'b1;22end23242526endmodule2.RTL视图三.代码⽚段写法1.代码1//====================================================================== 2// --- 名称 : Count_33// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-105// --- 描述 : 模10计数器,0到10循环累加6//====================================================================== 78module Count_39//---------------------<端⼝声明>---------------------------------------10 (11input clk ,12input rst_n ,13output reg [ 3:0] cnt14 );15//---------------------<信号定义>---------------------------------------16wire add_cnt ;17wire end_cnt ;1819//----------------------------------------------------------------------20//-- 0-9计数21//----------------------------------------------------------------------22always @(posedge clk or negedge rst_n)begin23if(!rst_n)24 cnt <= 'd0;25else if(add_cnt)begin26if(end_cnt)27 cnt <= 'd0;28else29 cnt <= cnt + 1'b1;30end31else32 cnt <= cnt;33end3435assign add_cnt = 1;36assign end_cnt = add_cnt && cnt==10-1;3738394041endmodule2.RTL视图四、⾃减计数器(较少⽤到)1.代码1//====================================================================== 2// --- 名称 : Count_43// --- 作者 : xianyu_FPGA4// --- ⽇期 : 2018-12-195// --- 描述 : 模10⾃减计数器,10到0循环累减6//====================================================================== 78module Count_49//---------------------<端⼝声明>---------------------------------------10 (11input clk ,12input rst_n ,13output reg [ 3:0] cnt14 );15//---------------------<参数定义>---------------------------------------16parameter CNT_MAX = 10 ;1718//----------------------------------------------------------------------19//-- 10到0循环累减20//----------------------------------------------------------------------21always @(posedge clk or negedge rst_n)begin22if(!rst_n) begin23 cnt <= 0;24end25else if(cnt==0) begin26 cnt <= CNT_MAX;27end28else begin29 cnt <= cnt - 1;30end31end323334endmodule2.RTL视图3.仿真波形五、新学到的⼀种⾮常简洁的计数器 本以为计数器就是这样了,近来学习开源骚客《SDRAM那些事⼉》系列教程,⼜发现⼀种新的写法,对于特定功能的实现上⾮常简洁。

实验六Verilog设计分频器计数器电路

实验六Verilog设计分频器/计数器电路一、实验目的1进一步掌握最基本时序电路的实现方法;2学习分频器/计数器时序电路程序的编写方法;3进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为5个clock周期的低电平,5个clock周期的高电平),文件命名为fenpinqi10.v。

2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为couter10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5.v。

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3..0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端。

三、实验步骤:第一个实验:1、打开QuartusII,新建一个工程f_fenpinq10yjq2、新建一个Verilog HDL文件3、输入程序:module fenpinqi10(clk,reset,clkout);input clk,reset;output clkout;reg clkout;reg[2:0] cnt;always @(posedge clk , negedge reset)beginif(!reset)begin clkout<=0;cnt<=0;endelse if(cnt==4)begin cnt<=0;clkout<=~clkout;endelse cnt<=cnt+1;endendmodule4、设置顶层实体名(点settings>general >下拉选fenpinqi10)5、编译6、执行file>Create/Update>Create Symbol Files for Current Flie为VHDI设计文件生成原件符号7、建立波形文件8、导入引脚9、仿真结果如下:总结:仿真结果与实验一的题意相符,所以仿真正确。

计数器的VHDL设计与实现

期刊论文—EDA课程设计题目:计数器的VHDL设计与实现学生姓名:李雷学生学号:09专业班级:计算机科学与技术0902班指导老师:方恺晴计数器的VHDL设计与实现摘要:介绍了各种基本计数器的组成及其工作原理,重点研究了可变模计数器的设计与实现,在对现有的可变模计数器的研究基础上,在Quartus 开发环境中,用VHDL语言设计一种功能更加强大的可变模计数器,它具有清零、置数、使能控制、可逆计数和可变模等功能,并且对传统的可变模计数器的计数失控问题进行研究,最终设计出一种没有计数失控缺陷的可变模计数器,并通过波形仿真和EPF10K20TI144—4系列实验箱,验证了其各项设计功能。

结果表明该设计正确.功能完整。

运行稳定.关键词:VHDL;计数器;可变模计数;可逆计数VHDL Design and Realization of CounterAbstract:This paper analyzes all kinds of basic counter and its working principle, focus on the counter variable mode of design and implementation。

In the environment of Quartus based on research of the existing module—alterable counter,a module—alterable counter with more functions,such as clear,set,enable control,reversible count,module—alterable count and so on,which is designedwith VHDL.By researching the problem of losing control existed in traditional module—alterable counter。

verilog循环变量

Verilog中的循环变量:理解其用途与用法Verilog是一种硬件描述语言,广泛应用于数字电路设计和模拟。

在编写复杂的Verilog代码时,循环变量起着非常重要的作用。

本文将详细介绍Verilog中的循环变量及其用法。

一、循环变量的定义在Verilog中,循环变量是一个可变的计数器,通常用于控制循环结构。

它可以是一个整数或一个枚举类型的成员。

循环变量用于循环语句(如for、while和repeat)中,帮助控制循环次数。

二、循环变量的分类Verilog中的循环变量可分为两类:私有循环变量和公共循环变量。

1.私有循环变量:这类循环变量仅在其定义的模块中有效。

它们通常在模块内部使用,用于控制特定模块的循环结构。

2.公共循环变量:这类循环变量可以在多个模块之间共享。

它们通常在模块之间传递数据和控制信号,以协调多个模块之间的操作。

三、循环变量的使用方法在Verilog中,使用循环变量需要注意以下几点:1.定义循环变量:在使用循环变量之前,需要先定义它。

可以使用localparam或parameter关键字定义循环变量,并指定其初始值和范围。

例如:module my_module;parameter COUNT = 10; // 定义一个名为COUNT的参数,初始值为10...endmodule2.控制循环结构:将循环变量与循环语句一起使用,以控制循环次数。

例如:verilog复制代码module my_module;parameter COUNT = 10;reg [3:0] i; // 定义一个4位的寄存器i作为循环变量...always @(posedge clk) beginfor (i = 0; i < COUNT; i = i+1) begin// 在这里编写需要重复执行的代码endendendmodule在这个例子中,for循环将重复执行代码块,直到循环变量i的值达到参数COUNT的值为止。

verilog数字系统设计教程

verilog数字系统设计教程Verilog数字系统设计教程作者:XXX引言:数字系统设计是现代电子工程中非常重要的一部分。

Verilog作为一种硬件描述语言,提供了一种方便且专业的方法来设计和描述数字系统。

本教程旨在为初学者提供关于Verilog数字系统设计的详细介绍和指导。

1. Verilog简介Verilog作为一种硬件描述语言,用于描述数字系统的功能、结构和时序行为。

它类似于C语言,但更专注于硬件级别。

Verilog可以用于设计各种数字系统,例如处理器、嵌入式系统、通信设备等。

2. Verilog基本语法2.1 模块定义Verilog的基本单位是模块。

模块是数字系统的基本组成部分,可以看作是一个独立的功能单元。

模块可以包含输入、输出、内部信号以及其它子模块等。

2.2 信号声明在Verilog中,可以声明各种类型的信号,包括输入信号、输出信号和内部信号等。

信号声明定义了信号的类型、宽度和方向。

3. Verilog建模3.1 组合逻辑建模组合逻辑是数字系统中最基本的部分。

Verilog提供了各种组合逻辑建模的方法,包括逻辑运算、选择结构和多路复用器等。

3.2 时序逻辑建模时序逻辑是数字系统中需要考虑时序关系的部分。

Verilog提供了时序逻辑建模的方法,包括触发器、计数器和时序控制等。

4. Verilog仿真4.1 仿真器介绍仿真器是用于验证数字系统设计的工具。

Verilog可以与各种仿真器配合使用,用于验证设计的正确性和性能。

4.2 仿真流程仿真流程包括编写测试平台和测试用例、编译和仿真等步骤。

本节将介绍基本的仿真流程和相关技巧。

5. Verilog综合5.1 综合概述综合是将Verilog代码转换为逻辑门级描述的过程。

综合器通过将Verilog代码映射到实际的硬件库中,生成能够实现指定功能的逻辑电路。

5.2 综合流程综合流程包括综合前的优化和综合本身两个阶段。

本节将介绍综合的基本流程和主要考虑因素。

基于Verilog的任意模长可加减计数器设计

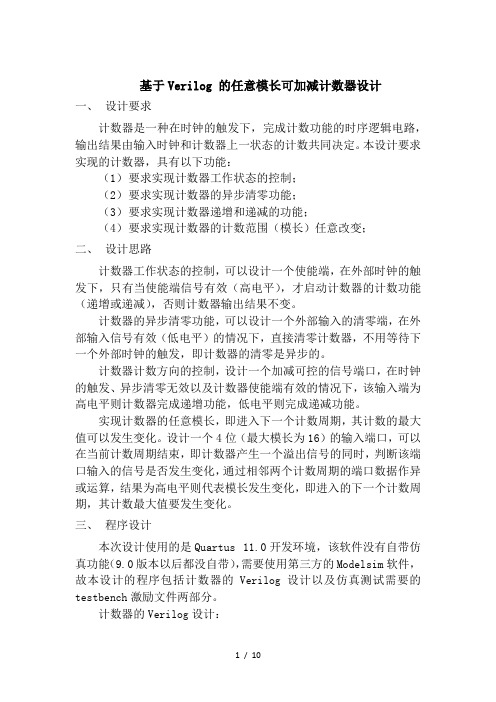

基于Verilog 的任意模长可加减计数器设计一、设计要求计数器是一种在时钟的触发下,完成计数功能的时序逻辑电路,输出结果由输入时钟和计数器上一状态的计数共同决定。

本设计要求实现的计数器,具有以下功能:(1)要求实现计数器工作状态的控制;(2)要求实现计数器的异步清零功能;(3)要求实现计数器递增和递减的功能;(4)要求实现计数器的计数范围(模长)任意改变;二、设计思路计数器工作状态的控制,可以设计一个使能端,在外部时钟的触发下,只有当使能端信号有效(高电平),才启动计数器的计数功能(递增或递减),否则计数器输出结果不变。

计数器的异步清零功能,可以设计一个外部输入的清零端,在外部输入信号有效(低电平)的情况下,直接清零计数器,不用等待下一个外部时钟的触发,即计数器的清零是异步的。

计数器计数方向的控制,设计一个加减可控的信号端口,在时钟的触发、异步清零无效以及计数器使能端有效的情况下,该输入端为高电平则计数器完成递增功能,低电平则完成递减功能。

实现计数器的任意模长,即进入下一个计数周期,其计数的最大值可以发生变化。

设计一个4位(最大模长为16)的输入端口,可以在当前计数周期结束,即计数器产生一个溢出信号的同时,判断该端口输入的信号是否发生变化,通过相邻两个计数周期的端口数据作异或运算,结果为高电平则代表模长发生变化,即进入的下一个计数周期,其计数最大值要发生变化。

三、程序设计本次设计使用的是Quartus 11.0开发环境,该软件没有自带仿真功能(9.0版本以后都没自带),需要使用第三方的Modelsim软件,故本设计的程序包括计数器的Verilog设计以及仿真测试需要的testbench激励文件两部分。

计数器的Verilog设计:module Prj(clk,rst_input,en,add_sub,data_input,full,data_output);input clk; // 外部时钟input rst_input; // 外部清零(异步)input en; // 计数使能input add_sub; // 计数方向input [3:0] data_input; // 计数器模长输入output reg full; // 计完当前模长output [3:0] data_output; // 计数器输出reg [3:0] current_counter;// 当前计数值(输出)reg update_length_en; // 改变模长的使能信号// 当前计数周期与上个计数周期的模长输入reg [3:0] current_clk_data_input,last_clk_data_in put;reg [3:0] counter_length; // 下个计数周期的模长reg [1:0] k;always @(posedge clk,negedge rst_input) beginif(!rst_input) // 异步清零beginfull=0;current_counter=0;endelse if(en) // 计数使能beginif(add_sub) // 加法器beginif(current_counter<(counter_length-1))begincurrent_counter=current_counter+1;full=0;endelse// 加法器计数完产生full脉冲以触发// 判断下个计数周期的模长是否变化begincurrent_counter=0;full=1; //full输出endendelse // 减法器beginif(current_counter>0)begincurrent_counter=current_counter-1;full=0;endelse // 减法器计数完begincurrent_counter=counter_length-1;full=1;endendendend//驱动当前计数输出assign data_output=current_counter;initialbegink=1; // k=1 表示启动计数器的第一个计数周期endalways @(posedge full) // 加法器/减法器完成当前周期计数// 计完当前周期(即full有效)才更新beginlast_clk_data_input<=data_input; // 上个周期的模长current_clk_data_input=data_input;//当前周期的模长update_length_en<=last_clk_data_input^current_clk_data_input;// update_length_en为更新计数器模长的使能端,// 异或运算使能端为0代表模长变化 1不变k=k+1; // k的初值为1,k变化说明计数模长更改过了if(k==2'd3)k=2;endalways @(posedge clk)beginif(update_length_en) // 使能有效计数模长变化counter_length=current_clk_data_input;elsebeginif(k>=2)// 下个周期计数器模长不变(保持上次更改的)counter_length=last_clk_data_input;if(k==1)// 整个计数器系统,最初的模长(一次没更改过)counter_length=data_input;endendendmodule测试激励文件testbench:`timescale 1 ps/ 1 psmodule Prj_vlg_tst();reg add_sub;reg clk;reg [3:0] data_input;reg en;reg rst_input;wire [3:0] data_output;wire full;Prj i1 (.add_sub(add_sub),.clk(clk),.data_input(data_input),.data_output(data_output),.en(en),.full(full),.rst_input(rst_input));parameter clk_period=10; // 时钟周期initial // 初始化使能端、清零端和时钟信号beginen=1;rst_input=1;clk=1;#(46*clk_period) en=0;#(3*clk_period) en=1;#(4*clk_period) rst_input=0;#(2*clk_period) rst_input=1;endalways #(clk_period/2) clk=~clk;initialbegin// 计数器模长分别为6 4 5 3// 左边为上一模长持续的时钟个数data_input=4'b0110;#(22*clk_period) data_input=4'b0100;#(12*clk_period) data_input=4'b0101;#(12*clk_period) data_input=4'b0011;#(5*clk_period);endinitialbegin// 计数器计数方向的改变// 左边为递增递减持续的时钟个数add_sub=1;#(9*clk_period) add_sub=0;#(10*clk_period) add_sub=1;#(13*clk_period) add_sub=0;#(4*clk_period) add_sub=1;endendmodule四、仿真结果如图1所示,最开始计数器输入的模长data_input为6,在计数方向控制端add_sub为高电平的情况下,可以从0计数到5,在add_sub为低电平的情况下,可以实现计数器的递减;当计数器模长data_input变为4的时候,先计完当前周期的模长(0到5),才开始模长为4的计数(0到3)。

verilog多模块编程实例

Verilog多模块编程实例1. 介绍Verilog是一种硬件描述语言,被广泛应用于数字电路设计。

Verilog具有模块化设计的特点,可以将一个大型的电路设计分解成多个小模块,然后逐个实现和调试。

本文将介绍Verilog多模块编程的实例,以帮助读者了解如何使用Verilog进行模块化设计。

2. 模块化设计的优势模块化设计是一种将大型系统分解成多个小模块的设计方法。

在Verilog中,模块化设计有以下几个优势:- 提高代码可读性:通过将大型系统分解成多个小模块,可以提高代码的可读性和可维护性。

- 便于调试:每个小模块相对独立,可以单独调试和测试,提高了系统的可靠性和稳定性。

- 提高复用性:将功能相似的代码封装成模块,可以提高代码的复用性,减少代码冗余。

3. 多模块编程实例接下来,我们将通过一个简单的数字电路设计来演示Verilog多模块编程的实例。

假设我们要设计一个4位全加器电路,首先我们需要实现一个单位全加器模块,然后将四个单元全加器模块连接成一个4位全加器模块。

3.1 单位全加器模块我们定义一个单位全加器模块,代码如下:```verilogmodule Adder_unit (input a, b, cin,output sum, cout);assign {cout, sum} = a + b + cin;endmodule```在单位全加器模块中,我们定义了三个输入信号a、b、cin和两个输出信号sum、cout。

其中,sum表示相加的结果,cout表示进位。

在模块内部,我们通过assign语句实现了全加器的功能。

3.2 4位全加器模块接下来,我们将四个单位全加器模块连接成一个4位全加器模块,代码如下:```verilogmodule Adder_4bit (input [3:0] a, b,input cin,output [3:0] sum,output cout);Adder_unit U0(.a(a[0]), .b(b[0]), .cin(cin), .sum(sum[0]), .cout(cout0));Adder_unit U1(.a(a[1]), .b(b[1]), .cin(cout0), .sum(sum[1]), .cout(cout1)); Adder_unit U2(.a(a[2]), .b(b[2]), .cin(cout1), .sum(sum[2]), .cout(cout2)); Adder_unit U3(.a(a[3]), .b(b[3]), .cin(cout2), .sum(sum[3]), .cout(cout));endmodule```在4位全加器模块中,我们首先定义了四个输入信号a、b和一个输入信号cin,以及四个输出信号sum和一个输出信号cout。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

模可变计数器设计V e r i l o g语言Document serial number【NL89WT-NY98YT-NC8CB-NNUUT-NUT108】模可变计数器设计(一)实验目的1、进一步熟悉实验装置和QuartusⅡ软件的使用;2、进一步熟悉和掌握EDA设计流程;3、学习简单组合、时序电路的EDA设计;4、学习计数器中二进制码到BCD码的转换技巧;5、学习实验装置上数码管的输出方法。

(二)设计要求完成设计、仿真、调试、下载、硬件测试等环节,在EDA实验装置上实现模可变计数器功能,具体要求如下:1、设置一个按键控制改变模值,按键按下时模为10-99之间(具体数值自行确定)的数,没按下时模为100-199之间(具体数值自行确定)的数;2、计数结果用三位数码管十进制显示。

(三)主要仪器设备3、微机1台4、QuartusII集成开发软件1套5、EDA实验装置1套(四)实验步骤主要有三个模块1:一个模20和模119的计数器2:数码管的显示3:BCD的调整源程序:module count (clk,m,en,rst,a,sel,SG,d);input clk,m,en,rst;output [7:0] SG;output [2:0] sel;output a;(* synthesis, keep *) reg clk1;(* synthesis, keep *) wire [3:0] gw,sw,bw;/*(* synthesis, keep *) */reg [3:0]a;reg [11:0] q;reg [11:0] model;reg [7:0] cnt,SG;reg [2:0] sel;reg [0:0]d;output [0:0]d;always @(posedge clk)begin cnt=cnt+1;if (cnt==200) begin clk1=1'b1; cnt=0; endelse clk1=1'b0; //200分频,CLK为数码管扫描频率,CLK1为计数频率 if (sel<2) sel=sel+1; else sel=0; end //sel为数码管选择always @(sel) begincase (sel)0: a=bw; //0数码管为百位1: a=sw; //1数码管为十位2: a=gw; //2数码管为个位default: a=0;endcasecase (a)0:SG<=8'b00111111; 1:SG<=8'b00000110;2:SG<=8'b01011011; 3:SG<=8'b01001111;4:SG<=8'b01100110; 5:SG<=8'b01101101;6:SG<=8'b01111101; 7:SG<=8'b00000111;8:SG<=8'b01111111; 9:SG<=8'b01101111; //8段译码值endcase endalways @(m)if (m) model=12'b000000100000; //模值20assign gw=q[3:0];assign sw=q[7:4];assign bw=q[11:8];always @(posedge clk1,negedge rst)beginif (!rst) q=0;else if (en)beginif (q<model)beginif (gw==9) begin q=q+7; if (sw==9) q=q+96; end //BCD调整 else q=q+1;endelse q=0;endendalways @(q)if(q<model) d<=0;else d<=1;endmodule波形仿真:Clk1是计数频率,每来一个clk1信号q计数一次如图所示:rst=1有效时开始计数 clk为扫描频率sel=0时数码管显示百位a=0sel=1时数码管显示十位a=1sel=2时数码管显示个位a=3m=1 模20计数器m=0 模119计数器管脚分配:SG[0] PIN_F13SG[1] PIN_F14SG[2] PIN_F15SG[3] PIN_E15SG[4] PIN_F16SG[5] PIN_F17SG[6] PIN_E18SG[7] PIN_F18clk PIN_C13en PIN_H8m PIN_J9rst PIN_C5sel[0] PIN_G18sel[1] PIN_G17sel[2] PIN_G16d[0] PIN_G13(五)实验心得本实验主要是三大模块的编写,第一次的实验在老师给的参考代码下进行的,不过错误依然很多,主要有几个重点药掌握,一是首先要编写出能够计数的模块,用m来控制模值的变化m=1时模值为20 m=0时模值为119;二是计数模块都是二进制计数的,而要在数码管上显示计数的话就必须进行BCD调整,并且q是一个是十二位的寄存器,通过把gw=q[3:0]; sw=q[7:4]; bw=q[11:8]赋值的方法;一个个的显示在数码管上,由于clk的频率比较快,所以可以看到三位数码管显示的值,我觉得管脚分配也是比较关键的!一开始我就把个位和百位显示的值搞反了序列信号发生和检测器设计(一)实验目的1、进一步熟悉EDA实验装置和QuartusⅡ软件的使用方法;2、学习有限状态机法进行数字系统设计;3、学习使用原理图输入法进行设计。

(二)设计要求完成设计、仿真、调试、下载、硬件测试等环节,在EDA实验装置上实现一个串行序列信号发生器和一个序列信号检测器的功能,具体要求如下:1、再设计一个序列信号检测器,检测上述序列信号,若检测到串行序列“11101”则输出为“1”,否则输出为“0”;(三)主要仪器设备1、微机1台2、QuartusII集成开发软件1套3、EDA实验装置1套(四)实验步骤主要两部分1:序列信号发生器设置q[0]<=q[15];Q<=q[15];q[15:1]<=q[14:0] ;通过循环移位串行输出2:序列信号检测器状转移态图一共有六个状态分别为S = 5'd00000,A = 5'd00001,B = 5'd00011,C = 5'd00110,D = 5'd01101,E = 5'd11010;源程序:module xulie(clk,rst,z,Q,led); input clk,rst;output Q,z;output [4:0] led;reg [4:0] led;reg [4:0] state;reg Q,z;reg [4:0] a;reg [15:0] q;parameter S = 5'd00000,A = 5'd00001,B = 5'd00011,C = 5'd00110,D = 5'd01101,E = 5'd11010;always @(posedge clk)beginif(rst==0) beginendelse beginq[0]<=q[15];Q<=q[15];q[15:1]<=q[14:0] ;endendalways @(posedge clk)beginif(state==D && Q==1)begin z<=1;led<=5'b11101;endelse begin z<=0;led<=5'b00000;end endalways @(posedge clk or negedge rst) if(!rst)beginstate<=S;endelsecasex(state)S: if(Q==1)state<=A;else state<=S;A: if (Q==1)state<=B;else state<= S;B: if (Q==1)state<=C;else state<=S;C: if(Q==0)state<=D;else state<=C;D: if(Q==1)state<=E;else state<=S;E: if(Q==0)state<=S;else state<=A;default: state<=S;endcaseendmodule波形仿真当rst=1是序列信号发生器循环发出当检测到11101是z=1输出高电平,并且同时使11101序列显示在五个led灯上(五)实验心得做实验之前准备了很多,实验时还是出现了很多问题,一开始序列信号发生器在第一个周期之后就会多出一个0即输出0,原因在于Q<=q[15]; q[15:1]<=q[14:0] ;q[0]<=Q;因为q[0]<=Q需要一个时钟的上升沿才能执行,所以就会多输出一个0;其次状态转移图也是关键,需要记忆六个不同的状态;做这个实验让我学到了casex的一些用法;进一步了解编写verilog语言。